27 26 25

Изобретение относится к вычислительной технике, может быть использовано пои построении надежных арифметических устройств, а также при создании специализированных векторных вычислительных машин и является усовершенствованием известного сумматора последовательного действия по авт. св. № 1488789.

Цель изобретения - повышение достоверности суммирования за счет обеспечения контроля входных и выходных кодов с иррациональным основанием 2

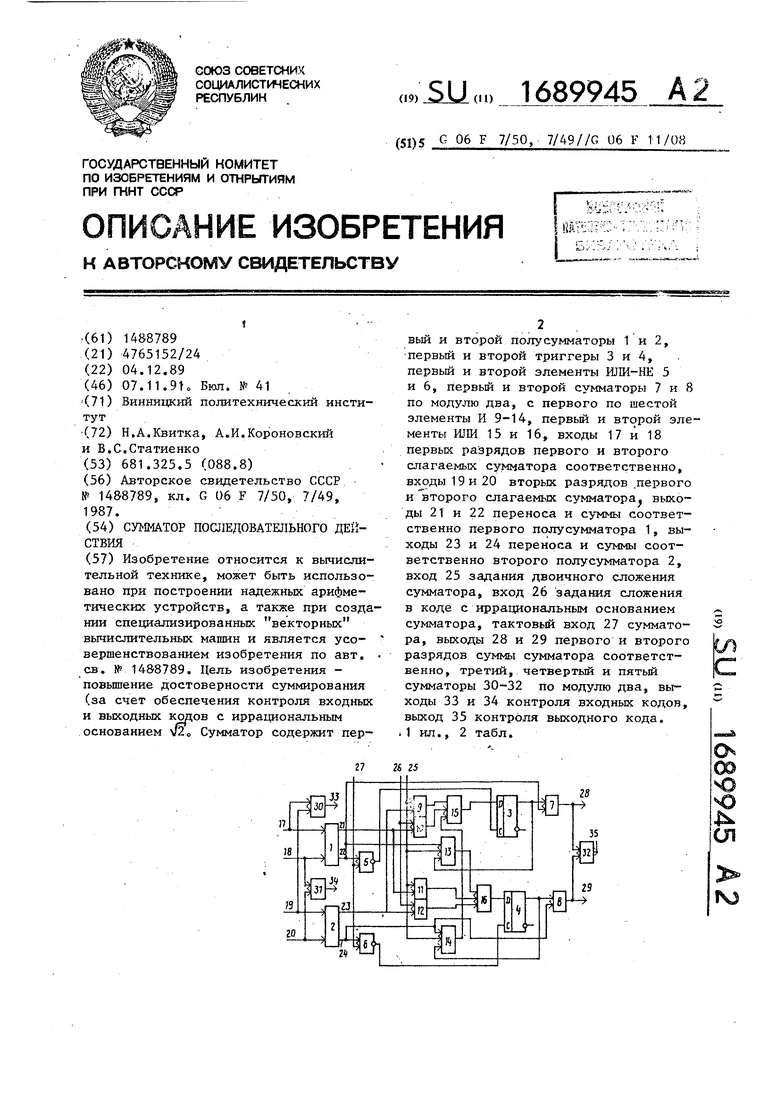

На чертеже представлена схема сум™ матора последовательного действия.

Сумматор содержит первый 1 и второй 2 полусумматоры, первый 3 и второй 4 триггеры, первый 5 и второй 6 элементы ИЛИ-НЕ, первый 7 и второй 8 сумматоры по модулю два, элементы И первый 15 и второй 16 элемен ты ИЛИ; входы первых разрядов первого 17 и второго 18 слагаемых сумматора,, яходы вторых разрядов первого 19 и второго 20 слагаемых сумматора,, выхо ,цы переноса 21 и сумгфг 22 первого потусумматора 1, выходы переноса 23 у с/ммы 24 второго полусумматора 2, пход 25 задания двоичного сложения сумматора,, вход 26 задания сложения в коде с иррациональным основанием сумматора, тактовый вход 27 сумматора выходы первого 28 и второго 29 разрядов суммы сумматора, третий 30, четвертый 31 и пятый 32 сумматоры по модулю дваj выходы 33 и 34 контро ля зходных кодов, выход 35 контроля выходного кода

Первые входы первого 1 и второго / подусумматоров соединены с входами 17 и 19 параллельного приема двух младших разрядов первого операнда, а вторые входы - с входами 18 и 20 ,параллельного приема двух младших разрядов второго операнда, выход 22 суммы полусумматора. 1 соединен с пер-- вым входом первого сумматора 7 по модулю дваг вторым входом пятого элемента И 13 и вторым входом первого ИЛИ-НЕ 5, выход которого поступает ча вход разрешения приема первого триггера 3, выход суммы 24 полусумматора 2 соединен с первым входом второго сумматора 8 по модулю два, вторым входом шестого элемента И 14 ч вторым входом второго элемента ИЛИ-НЕ 6, выход которого поступает на вход разрешения приема второго

триггера 4, первые входы о 5 и второго 6 элементов ИЛИ-ЧЕ подключаются к тактовому входу 27 с мкатора, выходы элементов И 9,10 и 14 подключены через первый элемент ИЛИ 15 к информационному входу первого триггера 3, выход которого поступает на второй вход первого сумматора 7

по модулю два, чей выход соединен с выходом 28 сумматора, а выходы элементов И 11-13 через второй элемент ИЛИ 16 подключены к информацион- ному входу второго триггера 4, выход

5 которого поступает на второй вход второго сумматора 8 по модулю два, чей выход соединен с выходом 29 сумматора, первые входы элементов 9,11, 13 и 14 подключены к входу 20 задания

0 двоичного сложения сумматора, вторые входы элементов 9, 115 13 и 14 подклю чены соответственно к выходу 23 переноса второго полусумматора 2 и второму входу четвертого элемента

Ь И 12s к выходу 21 переноса первого полусумматора 1 и второму входу второго элемента И 105 третьи входы пятого 13 и шестого 1 элементов подключены соответственно к выходам

0 первого 3 и второго 4 триггеров,

первые входы второго 10 и четвертого 12 элементов II - к входу 26 задания сложения в кеде с иррациональным о с нов я ггем«

,, Кроме того, первые и вторые входы третьего 30 и четвертого 31 сумматоров по модулю два подсоединены соот - ветственно к входам 17 и 19 первых н вторых разрядов первого слагаемого

У сумматора и входам 18 и 20 первых и вторых разрядов второго слагаемого сумматора, а первый и второй входы лчтого сумматора 32 по модулю два соединены с выходами 28 и 29 первого

j t и второго разрядов суммы сумматора соответственно 0

В системе счисления с основанием Y2 слагаемые числа А и В изобралакиг п следующим образом

((2)п- +an.2(-f)/-ft + .... + ьа,(т12|)+а0()0+а.4(-12Аа.в()в + ...+а-т($Гт;.(1)

В-ЬгмС-ф - +lWi2 r . ,,+Ъ (4J2) + -Ь0(-{2) +Ъи(тЕ +Ь-(Т -к ,0,+

W(2)-M.(2)

Веса разрядов кода с основанием s/2 составляют последовательность тепеней основания

...16 f2,l6,8l2,8,4 11,4,2 1(2,2, -{Т 1 i 1 чПГ

i-. j.. i. 1. 12. 1 2 2 4 4 8 8

.(3)

a,2

Ґ

п-е

J- ,

+ Ца;21/2; (4) is-m

П-2

+

---m

(5)

Ъ

Из выражения (3) следует, что чет ные степени являются весами разрядов двоичного кода, а нечетные - весами двоичного кода, умноженными на ifl С учетом этого выражения (1) и (2) можно записать п-

A-fiT

jsflH

n-

В i7XZtx2 j--m+

где a-,a: ,bj ,Ь ,Ј JO, 1J и являются цифрами двоично-кодированной системы счисления с основанием д2, a i, j для n+m разрядных чисел принимают значения

,-m+3, . .-3,-1,1,3,5 , ...,

,m+2, . .-4,-2,0,2,4, .. п-2) .

Первые члены формул (4) и (5) составляют суммы печатных разрядов кода, а вторые члены - суммы четных разрядов кода с основанием чПГ. Несмотря на то, что члены выражений (4) и (5) объединены общим основанием, они независимы одно от другого, а это позволяет осуществить одновременную независимую параллельную техническую реализацию операции сложения четных и нечетных разрядов операндов, представленных в кодах с основанием 1(27 и таким образом увеличить быстродействие сумматора. В основу работы сумматора последовательного действия положено сложение двух младших ( первого и второго) одноименных разрядов в двоичной системе счисления с иррациональным основанием |2, которое выполняется согласно табл.1 и 2.

Если в качестве разрешенных кодовых комбинаций в двоично-кодированной системе счисления с основанием - у2 для кодирования чисел использовать лишь те, которые содержат четное количество единиц, при этом единицы в разрешенной кодовой комбинации расположены парами, то слагаемые (4) и (5) принимают вид

(6)

А dT+1)) aj2J;

Г$

1 89945

В

о

(-17+о/ ь;

(7)

10

15

20

5

i-Ј

30

/

й

Предлагаемое кодирование позволяет довольно просто осуществить контроль на нечетность как входных кодов, так и производить текущий контроль выполнения операции суммирования. Признаком искажения кодовой комбинации является нечетность единиц в паре разрядов комбинации. Код позволяет обнаружить все однократные ошибки0

Сумматор может работать в двух режимах: в режиме сложения операндов, представленных в коде с основанием J2, и в режиме суммирования при двоичном представлении операндов. Первый режим обеспечивается подачей единичного сигнала на вход 26 режима работы, а второй - подачей единичного сигнала на вход 25 режима работы.

Последовательный сумматор в режиме сложения чисел в коде с иррациональ- 25 ным основанием $2 работает следующим образом.

Триггеры 3 и 4 перед началом работы устанавливаются в состояние О. В каждом такте суммирования на входы 17 и 19 сумматора подаются два разряда (начиная с младшего и следующего за младшим) первого операнда, а на входы 18 и 20 - соответствующие разряды второго операнда, причем на входы 17 и 19 сумматора поступают 35 одноименные разряды четных весов с иррациональным основанием |2, а на входы 18 и 20 - одноименные разряды нечетных весов кода с иррациональным основанием 2. При этом достоверной информацией присутствующей на входах

17,19 и 18, 20, является информация 11, 00, 00, 11, 11, 11, 00, 00. В случае, если на входах 17, 19 или/и

18,20 присутствуют комбинации 10, 01, 01; 01, 10; 10, 01 ;1(), то на выходах 33 и/или 34 сумматоров 30 и/или 31 по модулю два возникают единичные потенциалы, сигнализирующие

о прекращении операции сложения. Та- кьм образом, осуществляется контроль входных кодов.

Сложение одноименных достоверных разрядов происходит одновременно и для четных разрядов осуществляется по табл.1, а для нечетных - по табл.2. На вход 26 выбора режима работы поступает единичный сигнал. Параллельно с выхода 21 переноса по45

50

усумматора 1 через элементы И 10 ШШ 15 и с выхода 23 переноса полу- сумматора 2 через элементы К 12 и ЛИ 16 поступают соответственно на г информационный вход триггера 3 сигнал переноса в следующий разряд четного веса кодаэ на информационный вход Триггера 4 сигнал переноса в следуюий разряд нечетного веса кода. Если ю на входы сумматора поданы одинаковые е значения разрядов слагаемых (00 или I1)э то сигнал на выходе суммы полусумматоров 1 и 2 разрешит прохождение тактового импульса соответственно 15 через элемент ИЛИ-НЕ 5 на тактовьй вход триггера 3, которьй осуществит запись значения переноса в триггер 3S я через элемент ИЛИ-НЕ 6 на тактовьй вход триггера 4. которьй осуществит 20 запись значения переноса в триггер 4« Если значения разрядов слагаемых различны$ то триггеры 3 и 4 сохраняют .предыдущие состояния. На выходы 28 и 29 сумматора поступает сумма по 25 модулю два, значение поразрядной суммы и переноса, полученного в предыдущем разряде„ Если n+m число разрядов кодов слагаемых, то в,последнем

хШ-tn ,N30

(.--- + 1; такте работы сумматора на

го информационные входы поступают нулевые коды, а на выходе сумматора - сигналы,, соответствующие состоянию Триггерао Если сумматор, при сложении 35

работает без сбоев, то при любом Такте на выходах 28 и 29 первого и Второго разрядов суммы сумматора Всегда должны присутствовать сигналы 11 или 00.40

Появление на выходах 28 и 29 сиг- налое 01 или 10 свидетельствует о нарушении работы сумматора. Такое состояние подтверждается наличием единичного сигнала на выходе 35 сум- 45 матора 32 по модулю два. Дальнейшее Суммирование прекращаемся. В этом состоит контроль выходных кодов при сложении операндов, представленных ,$ коде с основанием 2.

Особенности работы сумматора в режиме суммирования при двоичном представлении операндов в следующем , Режим обеспечивается подачей единичного сигнала на вход 25. Два одноразрядных сумматора объединены в схему параллельного двоичного двухразрядно- ,о сумматора с последовательным пере-- tiocoM в отличие от режима сложения

50

55

0

5

0

5

0

5

операндов, представленных с основанием {2, где два одноразря/Пюгх суь,г.гора объединялись в схему параллельного двоичного двухразрядного сумматора с параллельным переносом. е

Запоминанием переноса с выхода 21 при сложении младшего из двух разрядов, поступающих на соответствующие входы 17 и 18 первого полусумматора 1, осуществляется не на триггере 3, входящем в первый одноразрядный сумматор, как в режиме сложения операндов, представленных в коде с основанием J2, а на триггере 4 второго одноразрядного сумматора, и запоминание переноса с выхода 23 при сложении старшего из двух разрядов, поступающих на соответствующие входы 19 и 20 второго полусумматора 25 осуществляется на триггере 3 первого одноразрядного сумматора.

Значение одноразрядной суммы в каждом такте снимается поочередно с выходов сумматора,, во всех нечетных тактах работы (первом, третьим и т.д. т,д.) - с выхода 285 во всех четных тактах работы - с выхода 29.

П р и м е р. Реализация операции сложения при двоичном представлении операндов. Пусть

А 0 1 101

В 0 0 0 1 1

На .-рвом такте сложения на входах 19 и 20 отсутствует информация, на входы 17 и 18 поступают два единичных сигнала„ Так как первоначально триггеры 3 и 4 установлены в нулевые состояния, то значение одноразрядной суммы на выходе 28 нулевоеt образованный в результате сложения перенос на выходе 21 поступает через элементы И 11 и ШШ 16 на информационный триггера 4 и, поскольку на выходе 2 полусумматора 2 присутствует нулевой сигнал, разрешающий прохождение тактового импульса на синхровыход триггера 4, единица переноса записывается в триггер 4.

На втором такте сложения на входы 19 и 20 поступают соответственно О и 1, на входах 17 и 18 информация отсутствует. Учитывая перенос, записанный в триггере 4, на выходе 29 получают нулевое значение суммы. На этом такте суммирования единичные сигналы с выхода триггера 4 и выхода 24 суммы полусумматора 2 совместно с единичным значением сигнала на выходе 25 поступают на входы элемента И 14, с выхода которого через элемен ИЛИ 15 поступают на информационный вход триггера 3, и данным тактовым импульсом, поступающим на тактовый вход триггера 3, запоминаются в нем,

На третьем такте сложения на входах 19 и 20 информация отсутствует, на входы 17 и 18 подаются соответственно 1 и О, значение суммы на выходе 22 полусумматора 1 - 1, значение аер .носа на выходе 21 - О Учитывая единицу, записанную на предыдущем такте работы в триггере 3, на входах первого 7 сумматора по модулю два присутствует две единицы, что обеспечивает получение на выходе 28 нулевого значения суммы и запись 1 через элемент И 13 и ИЛИ 16 в триггер 4.

На четвертом такте сложения на входах 19 и 20 присутствуют сигналы соответственно О и 1, на входах 17 и 18 информация отсутствует, значение суммы на выходе 21 - О, на выходе 22 - 1, которая совместно с записанной в триггере 4 на предыдущем такте, поступает на вход

5

0

5

раза меньше) то это позволяет повысить быстродействие сумматора в данном режиме почти в два раза. Формула изобретения

Сумматор последовательного действия по авт.св. № 1488789, отличающийся тем, что, с целью повышения достоверности суммирования, в него дополнительно введены третий, четвертый, пятый сумматоры по модулю два, причем первые входы третьего и четвертого сумматоров по модулю два подсоединены к входам первых разрядов первого и второго слагаемых сумматора соответственно, вторые входы третьего и четвертого сумматоров по модулю два соединены с входами вторых разрядов первого и второго слагаемых сумматора соответственно, выходы первого и второго разрядов суммы сумматора подсоединены соответ- .ственно к первому и второму входам пятого сумматора по модулю два, выходы третьего и четвертого сумматоров по модулю два являются выходами контроля входных кодов сумматора, а выход пятого сумматора по модулю два - вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

| Сумматор избыточного кода | 1987 |

|

SU1476460A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

Изобретение относится к вычислительной технике, может быть использовано при построении надежных арифметических устройств, а также при создании специализированных векторных вычислительных машин и является усо- вершенствованием изобретения по авт. св. № 1488789. Цель изобретения - повышение достоверности суммирования (за счет обеспечения контроля входных и выходных кодов с иррациональным основанием vZ0 Сумматор содержит первый и второй полусумматоры 1 и 2, первый и второй триггеры 3 и 4, первый и второй элементы ИЛИ-НЕ 5 и 6, первый и второй сумматоры 7 и 8 по модулю два, с первого по шестой элементы И 9-14, первый и второй элементы ИЛИ 15 и 16, входы 17 и 18 первых разрядов первого и второго слагаемых сумматора соответственно, входы 19 и 20 вторых разрядов первого и второго слагаемых сумматора выходы 21 и 22 переноса и суммы соответственно первого полусумматора 1, выходы 23 и 24 переноса и суммы соответственно второго полусумматора 2, вход 25 задания двоичного сложения сумматора, вход 26 задания сложения в коде с иррациональным основанием сумматора, тактовый вход 27 сумматора, выходы 28 и 29 первого и второго разрядов суммы сумматора соответственно, третий, четвертый и пятый сумматоры 30-32 по модулю два, выходы 33 и 34 контроля входных кодов, выход 35 контроля выходного кода. .1 ил., 2 табл. а

сумматора 8 по модулю два и обеспечи- 30 Х°Д°М контроля выходного кода сумма35

вает появление нулевого значения тора, суммы на выходе 29, а также запись единицы аналогично процессу, указанному на предыдущем такте, в триггер 3.

На пятом такте сложения на входе 17 - О, на входе 18 - О, на входах 19 и 20 информация отсутствует. На выходе суммы 22 - О, на выходе 21 - О, на первый вход сумматора 7 по модулю два поступает с выхода Q триггера 3 единица, записанная на предыдущем такте суммирования, что ведет к формированию 1 на выходе 28.

В связи с тем, что при сложении n+m-разрядных двоичных чисел выпол- 45 .няется (n+m + 1)(тн-1) суммирований, а при сложении (n+in) -разрядных кодов с иррациональным основанием

iJ2(--r- +1) суммирований (т.е. в два 250 .

Таблица 1

Таблица2

Таблица 1

35

Q

Таблица2

| Авторское свидетельство СССР № 1488789, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-07—Публикация

1989-12-04—Подача