Изобретение относится к вычислительной технике и микроэлектронике и предназначено для систем контроля, применяемых в автоматике и вычислительной технике.

Цель изобретения - расширение области применения сумматора по модулю три за счет возможности использования неприводимых значений операндов.

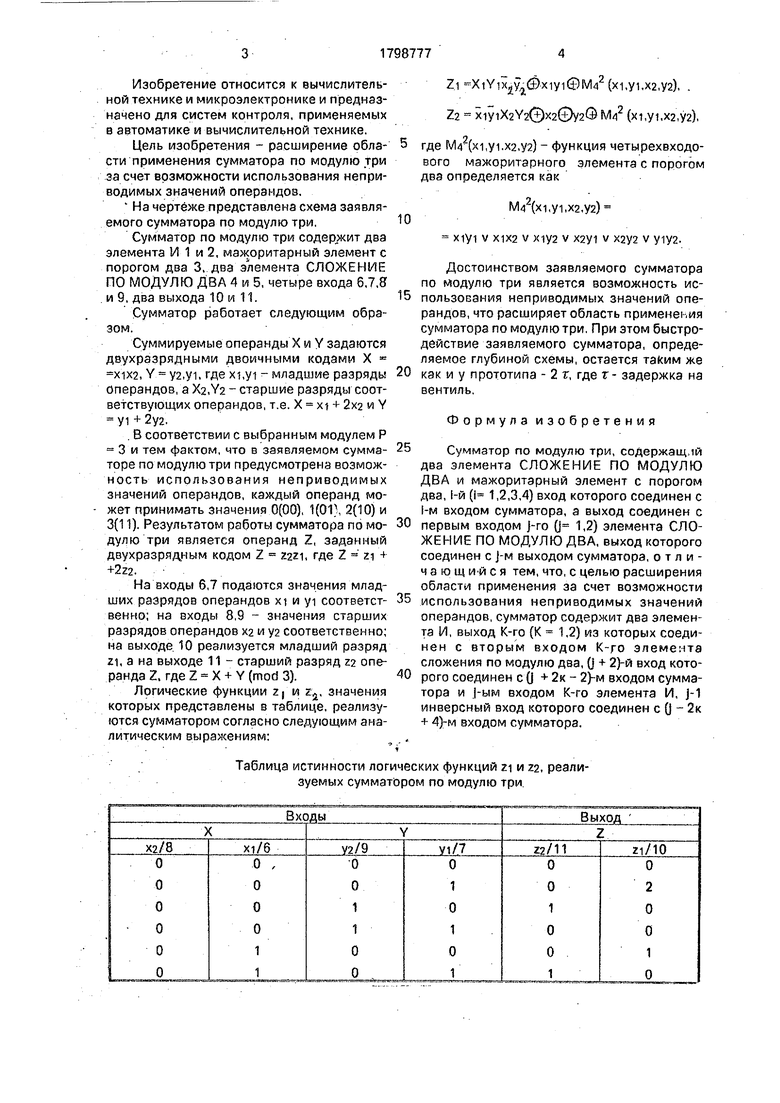

На чертеже представлена схема заявляемого сумматора по модулю три.

Сумматор по модулю три содержит два

элемента И 1 и 2, мажоритарный элемент с

порогом два 3, два элемента СЛОЖЕНИЕ

ПО МОДУЛЮ ДВА 4 и 5, четыре входа 6,7.8

. и 9, два выхода 10 и 11.

Сумматор работает следующим образом.

Суммируемые операнды X и У задаются двухразрядными двоичными кодами X xix2, Y у2,у1, где xi,yt - младшие разряды операндов, а Х2, Уг - старшие разряды соответствующих операндов, т.е. X xi + 2x2 и Y

У1 + 2уа.

. В соответствии с выбранным модулем Р 3 и тем фактом, что в заявляемом сумматоре по модулю три предусмотрена возможность использования неприводимых значений операндов, каждый операнд может принимать значения 0(00), 1(01), 2(10) и 3(11). Результатом работы сумматора по модулю три является операнд Z, заданный двухразрядным кодом Z 2221, где Z zi +

+2Z2.

На входы 6,7 подаются значения младших разрядов операндов xi и yi соответственно; на входы 8,9 - значения старших разрядов операндов ха и у2 соответственно; на выходе 10 реализуется младший разряд zi, а на выходе 11 - старший разряд za операнда Z, где Z X + Y (mod 3).

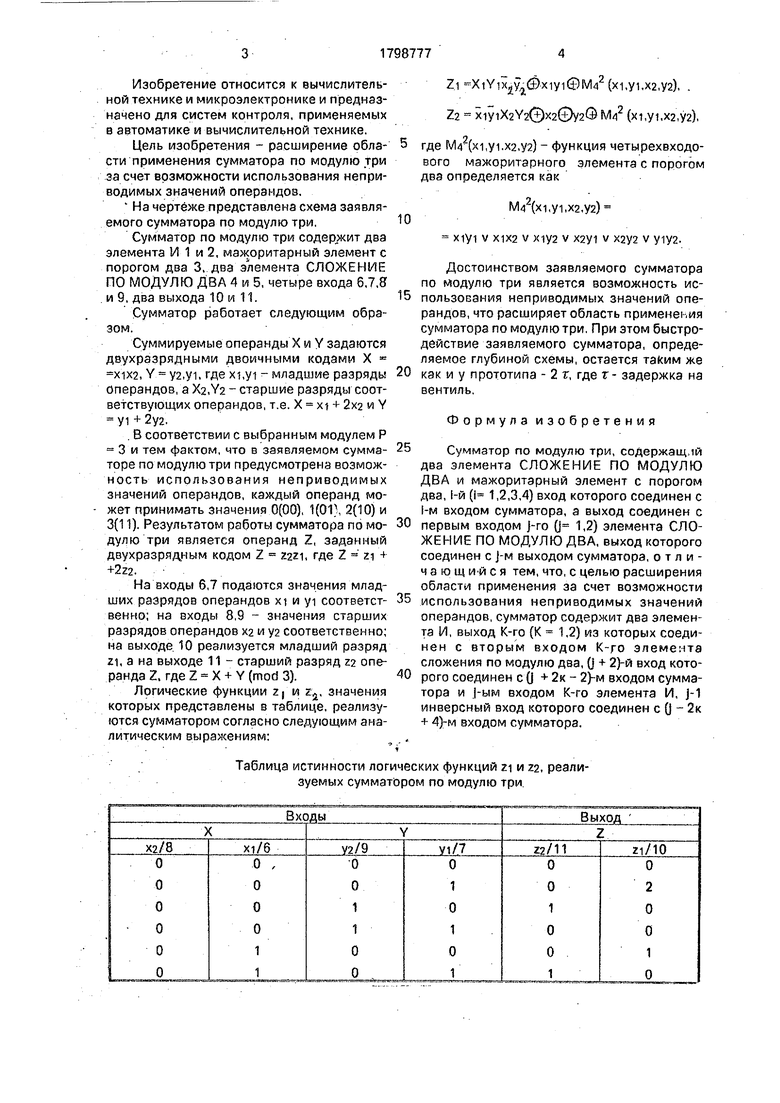

Логические функции z( и z4, значения которых представлены в таблице, реализуются сумматором согласно следующим аналитическим выражениям:

Zi -XiYix1ya©xiyi©M42(xi,yi,X2,y2), .

Z2 XiyiX2Y2(+)x2©y2® (Х1,у1,Х2,У2),

где M42(xi,yi.X2,y2) - функция четырехвходо- вого мажоритарного элемента с порогом два определяется как

10

М4 (Х1,У1,Х2,У2):

Х1У1 V Х1Х2 V Х1У2 V Х2У1 V Х2У2 V У1У2.

Достоинством заявляемого сумматора по модулю три является возможность использования неприводимых значений операндов, что расширяет область применения сумматора по модулю три. При этом быстродействие заявляемого сумматора, определяемое глубиной схемы, остается таким же

как и у прототипа -2т, где т- задержка на вентиль.

Формула изобретения

Сумматор по модулю три, содержащий два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА и мажоритарный элемент с порогом два, 1-й (1 1,2,3,4) вход которого соединен с 1-м входом сумматора, а выход соединен с

первым входом j-ro (j 1,2) элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, выход которого соединен с j-м выходом сумматора, о т л и - ч а ю щ И й с я тем, что, с целью расширения области применения за счет возможности

использования неприводимых значений операндов, сумматор содержит два элемента И, выход К-ro (К 1,2) из которых соединен с вторым входом К-ro элемента сложения по модулю два, (J + 2}-й вход которого соединен с 0 + 2к - 2)-м входом сумматора и |-ым входом К-го элемента И, j-1 инверсный вход которого соединен с 0 2к + 4)м входом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1991 |

|

SU1830528A1 |

| Устройство для сложения по модулю три | 1991 |

|

SU1827671A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| Одноразрядный четверичный сумматор | 1991 |

|

SU1827672A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

| Сумматор по модулю три | 1991 |

|

SU1797109A1 |

| Цифровой функциональный преобразователь | 1989 |

|

SU1686438A1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Таблица истинности логических функций г и Z2, реализуемых сумматором по модулю три.

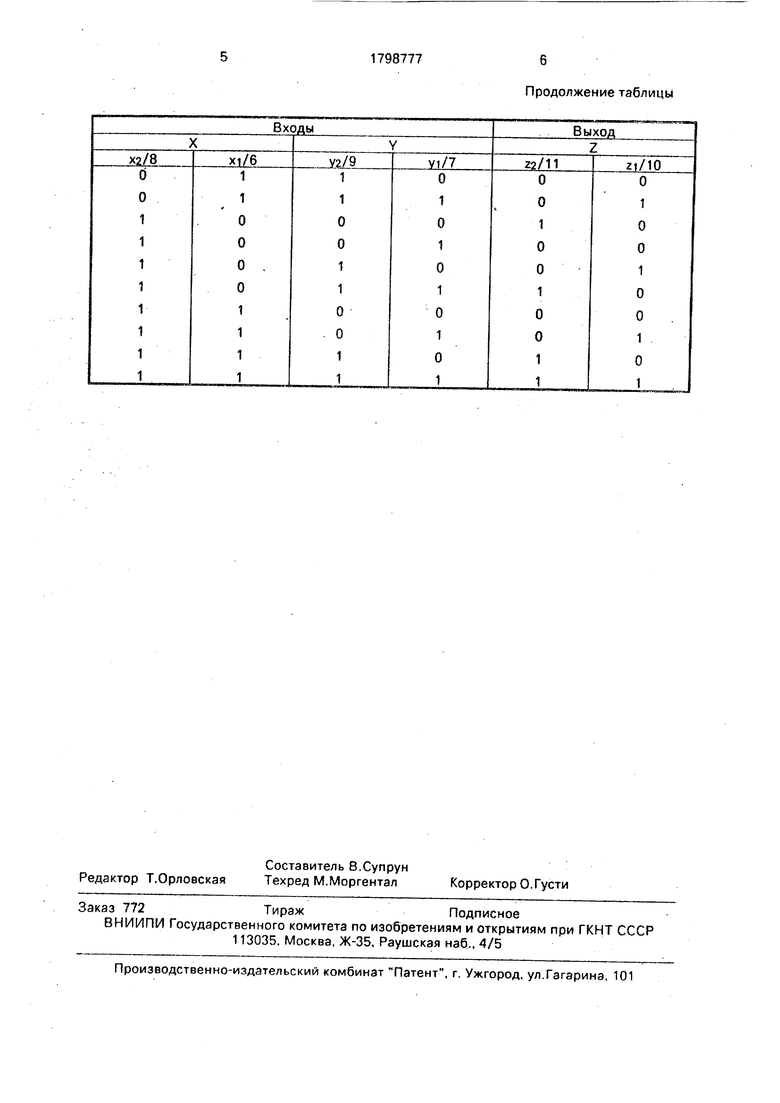

Продолжение таблицы

Авторы

Даты

1993-02-28—Публикация

1991-06-03—Подача