ел С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения достоверности передачи информации | 1987 |

|

SU1418919A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1989 |

|

SU1658396A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1982 |

|

SU1113892A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1987 |

|

SU1478349A1 |

| Устройство для обнаружения ошибок по элементам двоичного сигнала | 1984 |

|

SU1256228A1 |

| Устройство для измерения проскальзываний цифровых сигналов | 1989 |

|

SU1674388A1 |

| Устройство для контроля логических схем | 1985 |

|

SU1252786A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1988 |

|

SU1536514A1 |

| Устройство для определения достоверности передачи двоичной информации | 1975 |

|

SU618857A2 |

Изобретение относится к области автоматики и вычислительной техники, в частности к устройствам автоматизированного контроля моделей, и может быть использовано для определения коэффициента ошибок по единичным элементам при различ- ных отношениях сигнал/помеха при проведении приемосдаточных испытаний модемов в процессе серийного производства. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля модемов с выявлением факта запаздывания отклика. Устройство содержит датчик теста 1, передатчик модема 2, имитатор канала связи 3, блока согласования 4, группу контролируемых блоков 5, элемент ИЛЙ-НЁ 6, датчик испытательной последовательности 7, схему сравнения 8, группу счетчиков 9, регистр синдрома ошибок 10, генератор тестов. 4 ил.

3

00

VI

00 ON

(puei

Изобретение относится к области автоматики и вычислительной техники, в частности, к устройствам автоматизированного контроля модемов и может быть использовано для определения коэффициента ошибок по единичным элементам при различных отношениях сигнал-помеха при проведении приемосдаточных испытаний модемов в процессе серийного производства. . : . :

Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля модемов с выявлением факта запаздывания отклика.

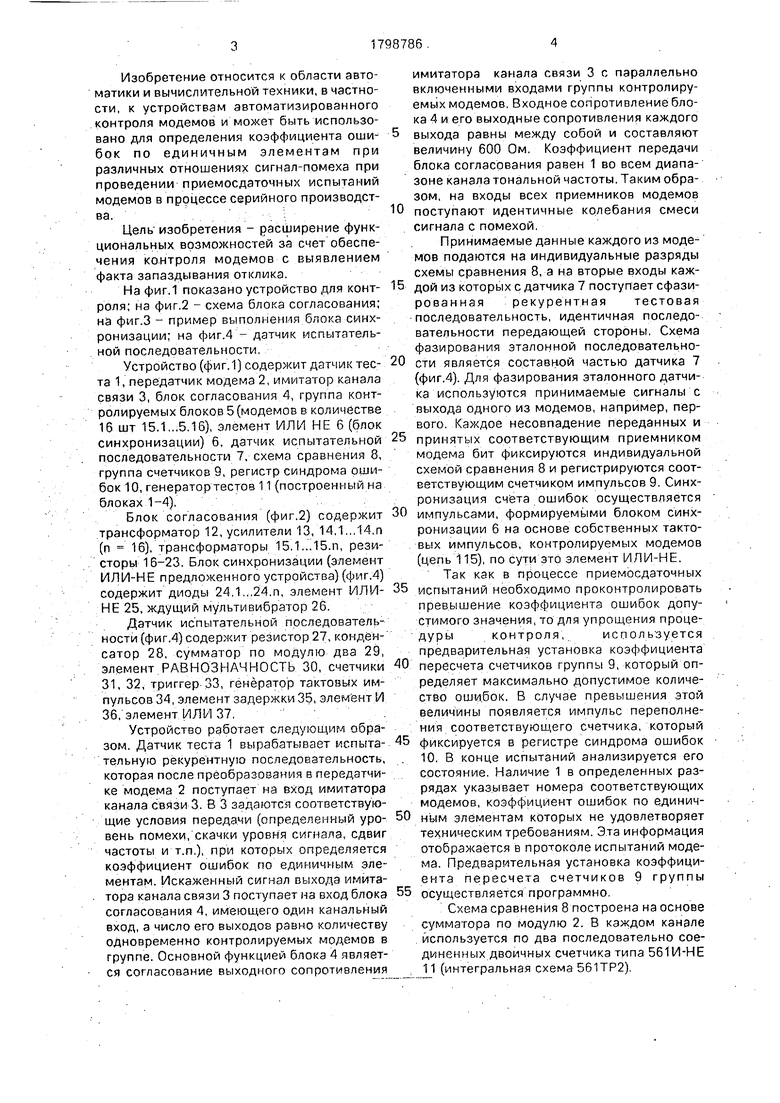

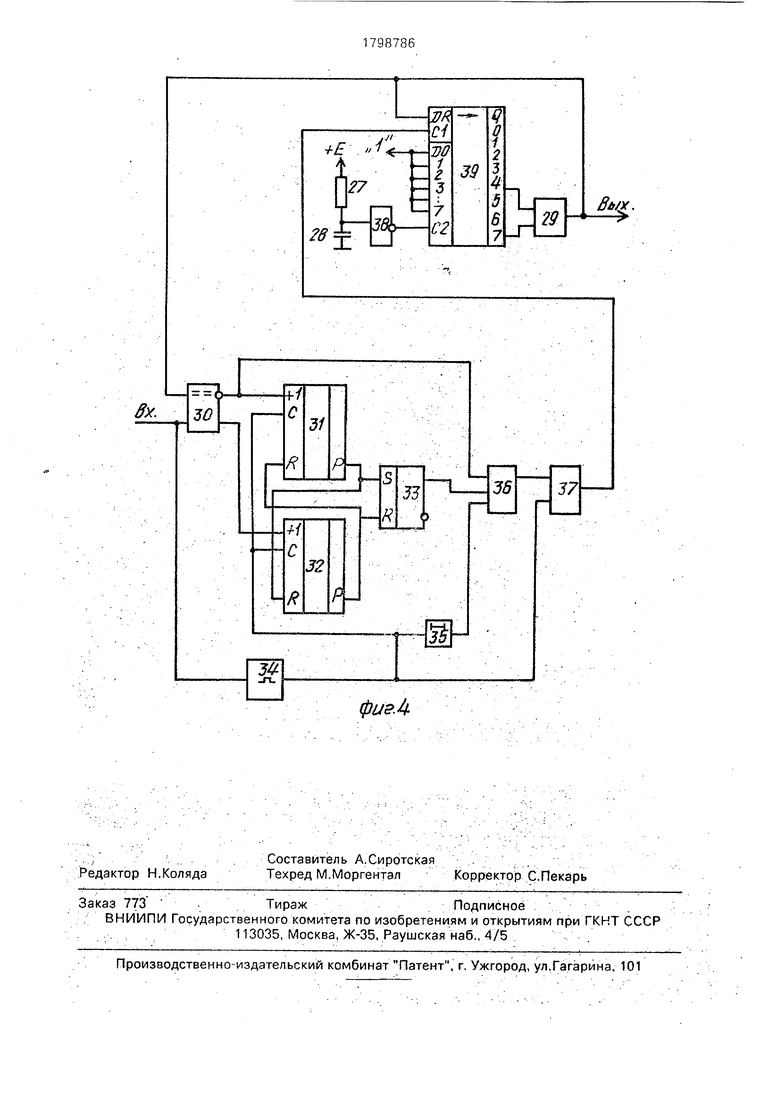

На фиг.1 показано устройство для контроля; на фиг.2 - схема блока согласования; на фиг.З - пример выполнения блока синхронизации; на фиг.4- датчик испытательной последовательности.

Устройство (фиг.1) содержит датчик теста 1, передатчик модема 2, имитатор канала связи 3, блок согласования 4, группа контролируемых блоков 5 (модемов в количестве 16 шт 15.1...5.16), элемент ИЛИ НЕ 6 (блок синхронизации) 6, датчик испытательной последовательности 7, схема сравнения 8, группа счетчиков .9, регистр синдрома ошибок 10, генератор тестов 1.1 (построенный на блоках 1-4).

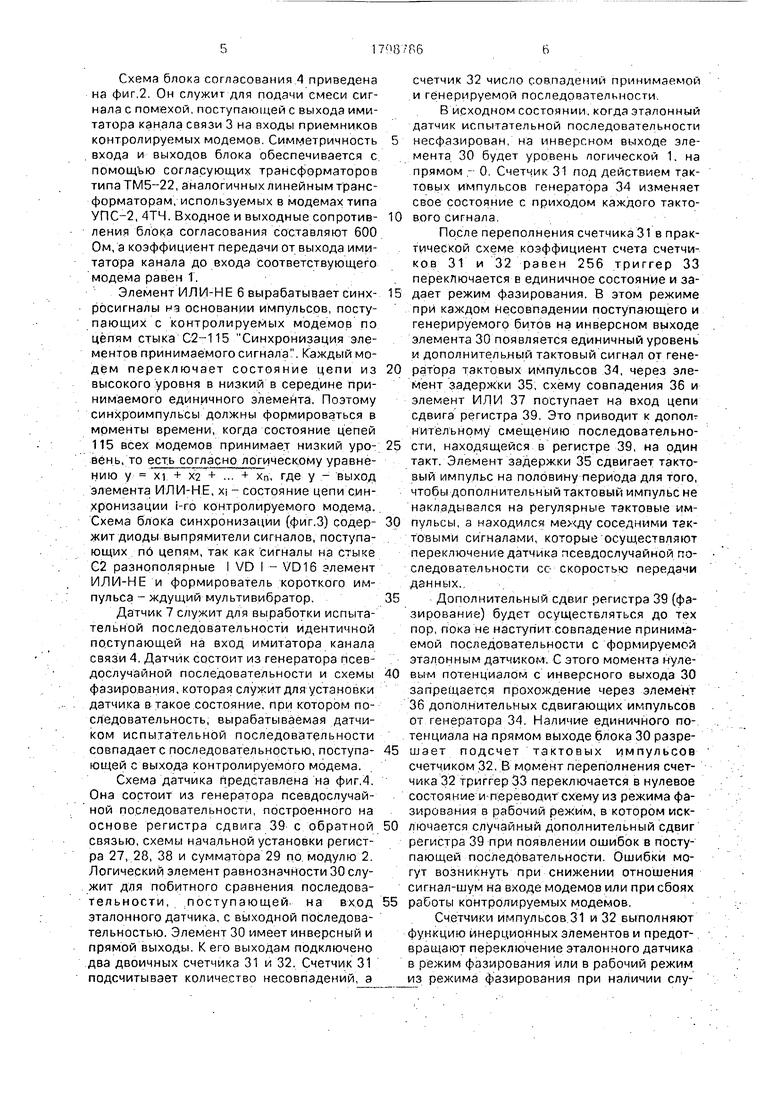

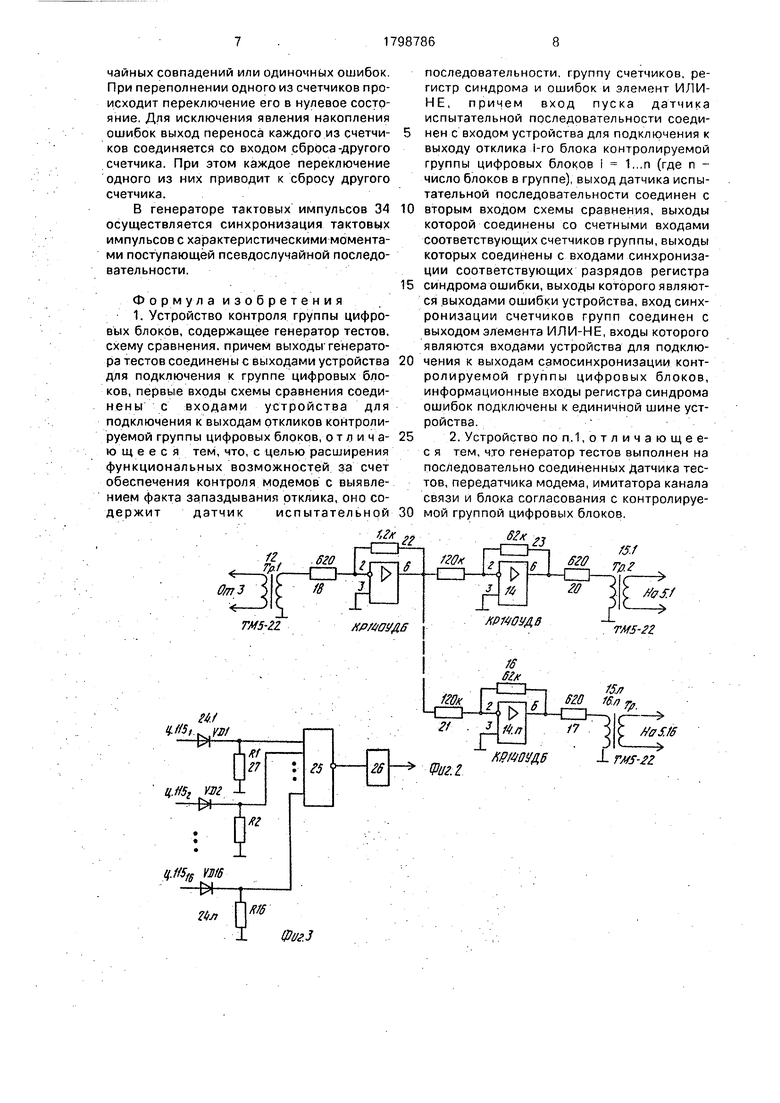

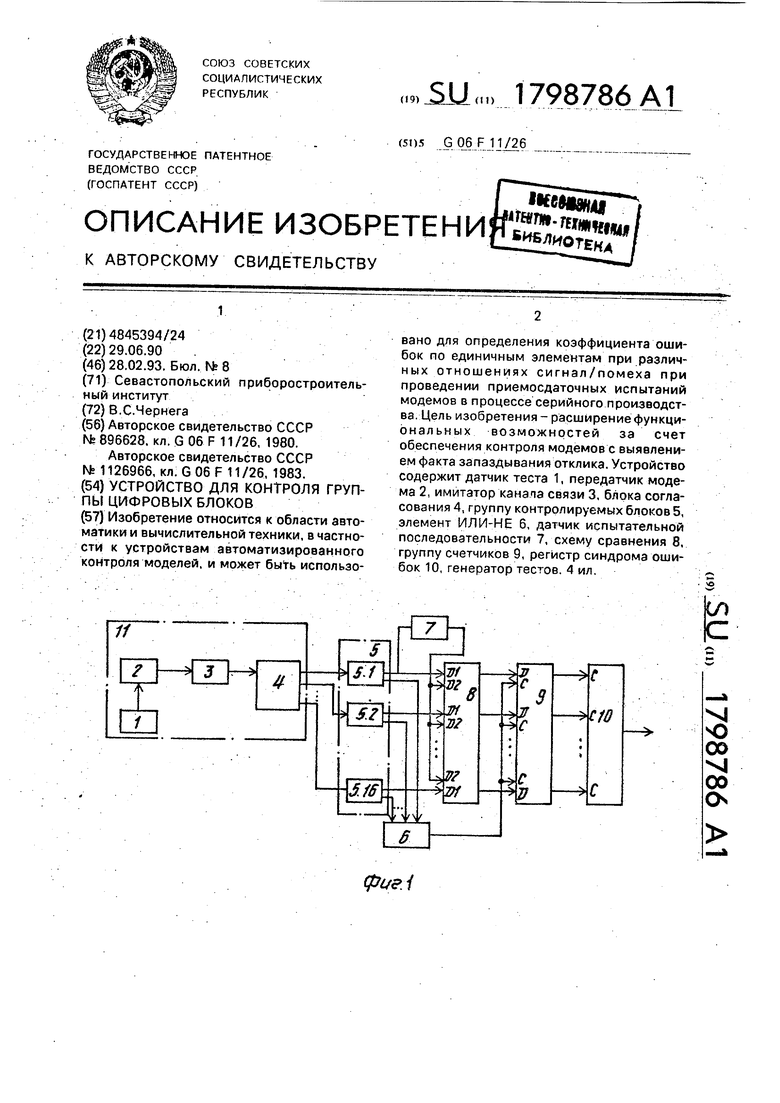

Блок согласования (фиг.2) содержит трансформатор 12, усилители 13, 14.1...14.П (п 16), трансформаторы 15.1...15.л, резисторы 16-23. Блок синхронизации (элемент ИЛИ-НЕ предложенного устройства) (фмг.4) содержит диоды 24.1...24.П, элемент ИЛИ- НЕ 25, ждущий мультивибратор 26.

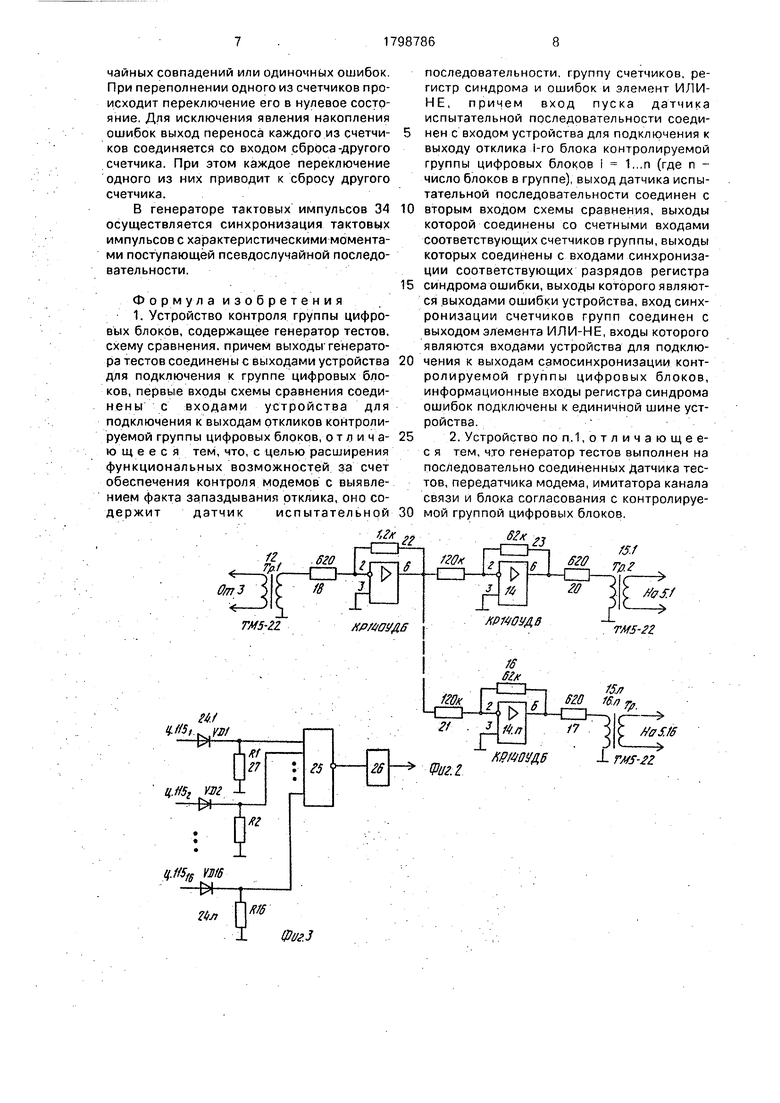

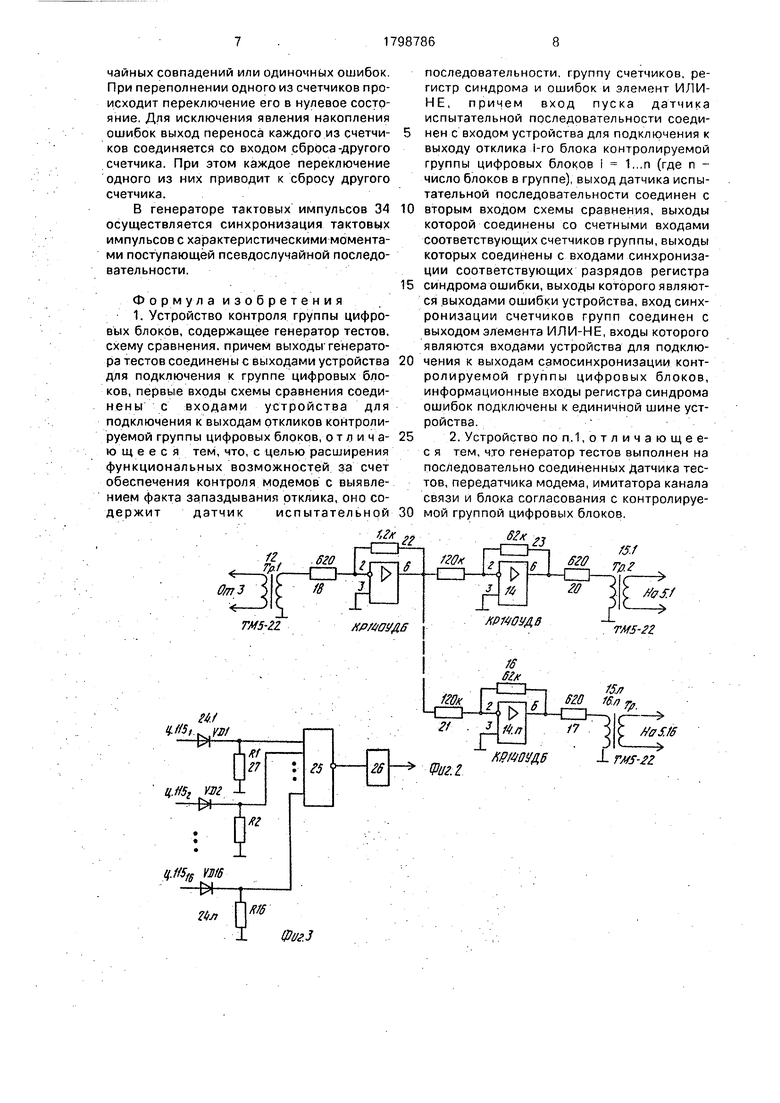

Датчик испытательной последовательности (фиг.4) содержит резистор 27, конден- сатор 28, сумматор по модулю два 29, элемент.РАВНОЗНАЧНОСТЬ 30, счетчики 31, 32, триггер 33, генератор тактовых импульсов 34, элемент задержки 35, элемент И. 36, элемент. ИЛИ 37.

Устройство работает следующим образом, Датчик теста 1 вырабатывает испыта-. тельную рекурентную последовательность, которая после преобразования в передатчике модема 2 поступает на вход имитатора канала связи 3. В 3 задаются соответствующие условия передачи (определенный уровень помехи, скачки уровня сигнала, сдвиг частоты и т.п.), при которых определяется коэффициент ошибок по единичным элементам. Искаженный сигнал выхода имитатора канала связи 3 поступает на вход блока согласования 4, имеющего один канальный вход, а число его выходов равно количеству одновременно контролируемых модемов в группе. Основной функцией блока 4 является согласование выходного сопротивления

имитатора канала связи 3 с параллельно включенными входами группы контролируемых модемов. Входное сопротивление блока 4 и его выходные сопротивления каждого

выхода равны между собой и составляют величину 600 Ом. Коэффициент передачи блока согласования равен 1 во всем диапазоне канала тональной частоты. Таким образом, на входы всех приемников модемов

поступают идентичные колебания смеси сигнала с помехой,

Принимаемые данные каждого из модемов подаются на индивидуальные разряды схемы сравнения 8, а на вторые входы каж5 дои из которых с датчика 7 поступает сфази- рованная рекурентная тестовая последовательность, идентичная последовательности передающей стороны, Схема фазирования эталонной последовательно0 сти является составной частью датчика 7 (фиг.4). Для фазирования эталонного датчика используются принимаемые сигналы с выхода одного из модемов, например, первого. Каждое несовпадение переданных и

5

принятых соответствующим приемником

модема бит фиксируются индивидуальной схемой сравнения 8 и регистрируются соответствующим счетчиком импульсов 9. Синхронизация счёта ошибок осуществляется

0 импульсами, формируемыми блоком синхронизации 6 на основе собственных тактовых импульсов, контролируемых модемов (цепь 115), по сути это элемент ИЛИ-НЕ. Так как в процессе приемосдаточных

5 испытаний необходимо проконтролировать превышение коэффициента ошибок допустимого значения, то для упрощения процедурыконтроля, используется предварительная установка коэффициента

0 пересчета счетчиков группы 9, который определяет максимально допустимое количество ошибок. В случае превышения этой величины появляется импульс переполнения соответствующего счетчика, который

5 фиксируется в регистре синдрома ошибок . 10. В конце испытаний анализируется его состояние. Наличие 1 в определенных разрядах указывает номера соответствующих модемов, коэффициент ошибок по единич0 ным элементам которых не удовлетворяет техническим требованиям. Эта информация отображается в протоколе испытаний модема. Предварительная установка коэффициента пересчета счетчиков 9 группы

5 осуществляется программно.

Схема сравнения 8 построена на основе сумматора по модулю 2. В каждом канале используется по два последовательно соединенных двоичных счетчика типа 561И-НЕ : 11 (интегральная схема 561ТР2).

Схема блока согласования 4 приведена на фиг.2. Он служит для подачи емеси сигнала с помехой, поступающей с выхода имитатора канала связи 3 на входы приемников контролируемых модемов. Симметричность входа и выходов блока обеспечивается с помощ ью согласующих трансформаторов типа ТМ5-22, аналогичных линейным трансформаторам, используемых в модемах типа УПС-2, 4ТЧ. Входное и выходные сопротивления блока согласования составляют 600 Ом, а коэффициент передачи от выхода имитатора канала до входа соответствующего модема равен Т.

Элемент ИЛИ-НЕ 6 вырабатывает синхросигналы нэ основании импульсов, поступающих с контролируемых модемов по цепям стыка С2-115 Синхронизация элементов принимаемого сигнала. Каждый модем переключает состояние цепи из высокого уровня в низкий в середине принимаемого единичного элемента. Поэтому синхроимпульсы должны формироваться в моменты времени, когда состояние цепей 115 всех модемов принимает низкий уровень, то есть согласно логическому уравнению у xi + Х2 + ... + Хп, где у - выход элемента ИЛИ-НЕ, xj - состояние цепи синхронизации 1-го контролируемого модема. Схема блока синхронизации (фиг.З) содержит диоды выпрямители сигналов, поступающих пб цепям, так как сигналы на стыке С2 разнополярные I VD I - VD16 элемент ИЛИ-НЕ и формирователь короткого импульса - ждущий мультивибратор.

Датчик 7 служит для выработки испытательной последовательности идентичной поступающей на вход имитатора канала связи 4. Датчик состоит из генератора псевдослучайной последовательности и схемы фазирования, которая служит для установки датчика в такое состояние, при котором последовательность, вырабатываемая датчиком испытательной последовательности совпадаете последовательностью, поступающей с выхода контролируемого модема.

Схема датчика представлена на фиг.4. Она состоит из генератора псевдослучайной последовательности, построенного на основе регистра сдвига 39 с обратной связью, схемы начальной установки регистра 27, 28, 38 и сумматора 29 по. модулю 2. Логический элемент равнозначности 30 служит для побитного сравнения последовательности, поступающей на вход эталонного датчика, с выходной последовательностью. Элемент 30 имеет инверсный и прямой выходы. К его выходам подключено два двоичных счетчика 31 и 32. Счетчик 31 подсчитывает количество несовпадений, а

счетчик 32 число совпадений принимаемой и генерируемой последовательности.

В исходном состоянии, когда эталонный датчик испытательной последовательности 5 несфазирован, на инверсном выходе элемента 30 будет уровень логической 1. на прямом .- 0. Счетчик 31 под действием тактовых импульсов генератора 34 изменяет свое состояние с приходом каждого такто0 вого сигнала.

После переполнения счетчика 31 в практической схеме коэффициент счета счетчиков 31 и 32 равен 256 триггер 33 переключается в единичное состояние и за5 дает режим фазирования. В этом режиме при каждом несовпадении поступающего и генерируемого битов на инверсном выходе элемента 30 появляется единичный уровень и дополнительный тактовый сигнал от гене0 ратора тактовых импульсов 34, через элемент задержки 35, схему совпадения 36 и элемент ИЛИ 37 поступает на вход цепи сдвига регистра 39. Это приводит к допол нительному смещен ию последовательно5 сти, находящейся в регистре 39, на один такт. Элемент задержки 35 сдвигает тактовый импульс на половину периода для того, чтобы дополнительныйтактовый импульс не накладывался на регулярные тактовые им0 пульсы, а находился мехду соседними тактовыми сигналами, которые осуществляют переключение датчика псевдослучайной последовательности со скоростью передачи данных,.

5Дополнительный сдвиг регистра 39 (фа- зирование) будет осуществляться до тех пор, пока не наступит совпадение принимаемой последовательности с формируемой эталонным датчиком. С этого момента нуле0 вым потенциалом с инверсного выхода 30 запрещается прохождение через элемент 36 дополнительных сдвигающих импульсов от генератора 34, Наличие единичного потенциала на прямом выходе блока 30 разре5 шэет подсчет тактовых импульсов счетчиком 32. В момент переполнения счетчика 32 триггер 33 переключается в нулевое состояние и-переводит схему из режима фа- зировзния в рабочий режим, в котором иск0 лючается случайный дополнительный сдвиг регистра 39 при появлении ошибок в поступающей последовательности. Ошибки могут возникнуть при снижении отношения сигнал-шум на входе модемов или при сбоях

5 работы контролируемых модемов,

Счетчики импульсов.31 и 32 выполняют Функцию инерционных элементов и предотвращают переключение эталонного датчика в режим фззирования или в рабочий режим из режима фазирования при наличии случайных совпадений или одиночных ошибок. При переполнении одного из счетчиков происходит переключение его в нулевое состояние. Для исключения явления накопления ошибок выход переноса каждого из счетчиков соединяется со входом сброса-другого счетчика. При этом каждое переключение одного из них приводит к сбросу другого счетчика.

В генераторе тактовых импульсов 34 осуществляется синхронизация тактовых импульсов с характеристическими моментами поступающей псевдослучайной последовательности.

Формул а изобретения 1. Устройство контроля группы цифровых блоков, содержащее генератор тестов, схему сравнения, причем выходы генератора тестов соединены с выходами устройства для подключения к группе цифровых блоков, первые входы схемы сравнения соединены с входами устройства для подключения к выходам откликов контролируемой группы цифровых блоков, от л и.ч а- ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля модемов с выявлением факта запаздывания отклика, оно содержит датчик испытательнрй

lf.tfSfs УШ

01

4л

последовательности, группу счетчиков, регистр синдрома и ошибок и элемент ИЛИ- НЕ, причем вход пуска датчика испытательной последовательности соединен с входом устройства для подключения к выходу отклика 1-го блока контролируемой группы цифровых блоков i 1...п (где п - число блоков в группе), выход датчика испытательной последовательности соединен с

вторым входом схемы сравнения, выходы которой соединены со счетными входами соответствующих счетчиков группы, выходы которых соединены с входами синхронизации соответствующих разрядов регистра

синдрома ошибки, выходы которого являются .выходами ошибки устройства, вход синхронизации счетчиков групп соединен с выходом элемента ИЛИ-НЕ, входы которого являются входами устройства для подключения к выходам самосинхронизации контролируемой группы цифровых блоков, информационные входы регистра синдрома ошибок подключены к единичной шине устройства.

2, Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что генератор тестов выполнен на последовательно соединенных датчика тестов, передатчика модема, имитатора канала связи и блока согласования с контролируемой группой цифровых блоков.

фигЛ

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения кратных дефектов в группе типовых элементов замены | 1983 |

|

SU1126966A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-28—Публикация

1990-06-29—Подача