зации формируется импульс, который взводит триггер 4 в 1, переводящую коммутатор 5 в состояние транслирования импульсов несравнения на тактовый вход PC 6, которые в нем хранятся. Все импульсы несравнения, выделяемые во время сбоев цикловой

1

Изобретение относится к электросвязи и может использоваться для обнаружения ошибок по элементам двоичного сигнала при испытаниях и регламентных проверках дискретных каналов связи.

Целью изобретения является повышение точности обнаружения ошибок.

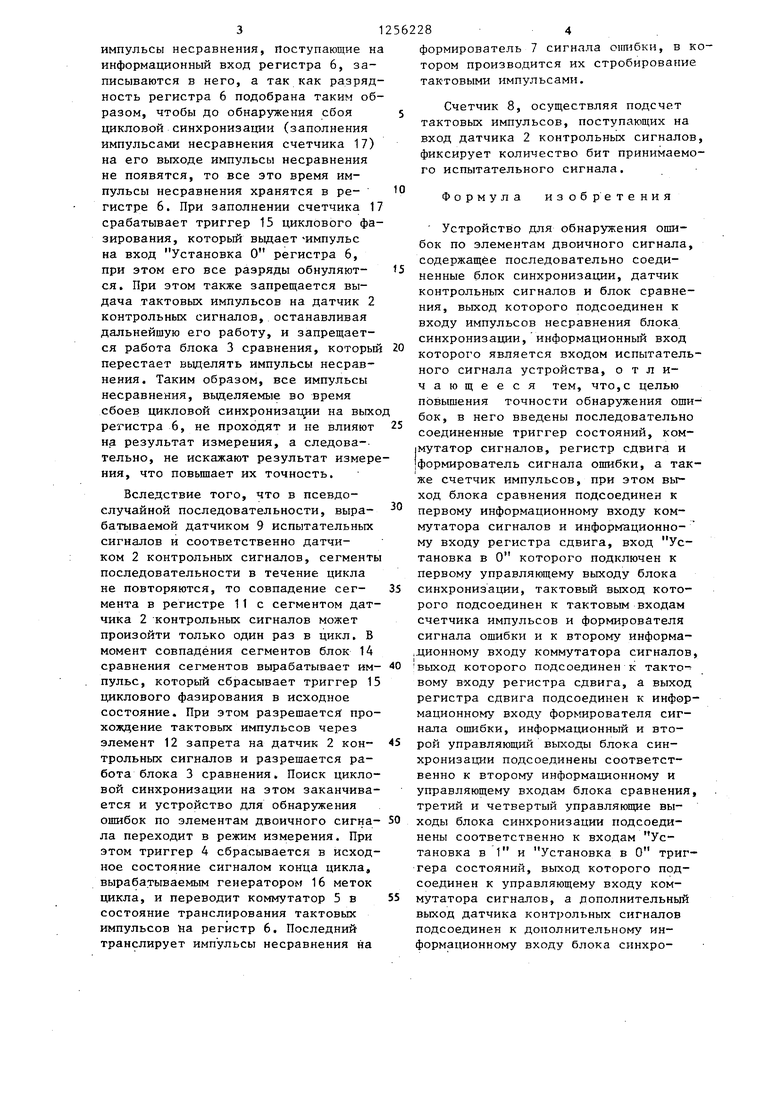

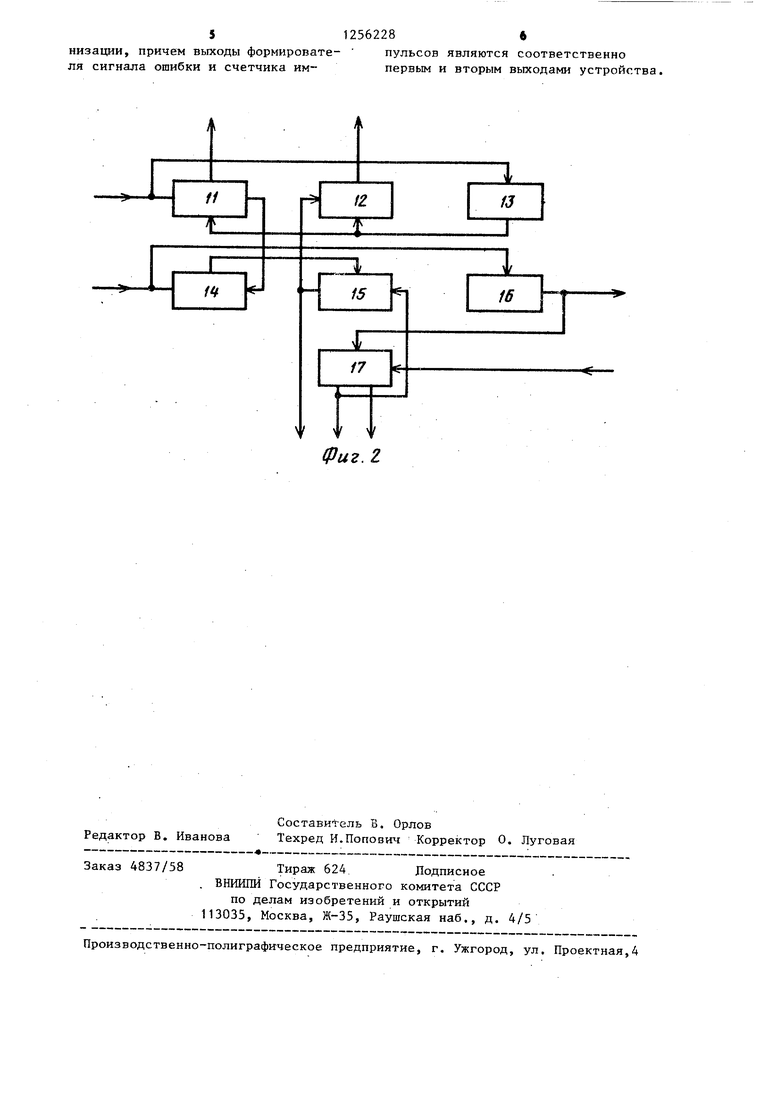

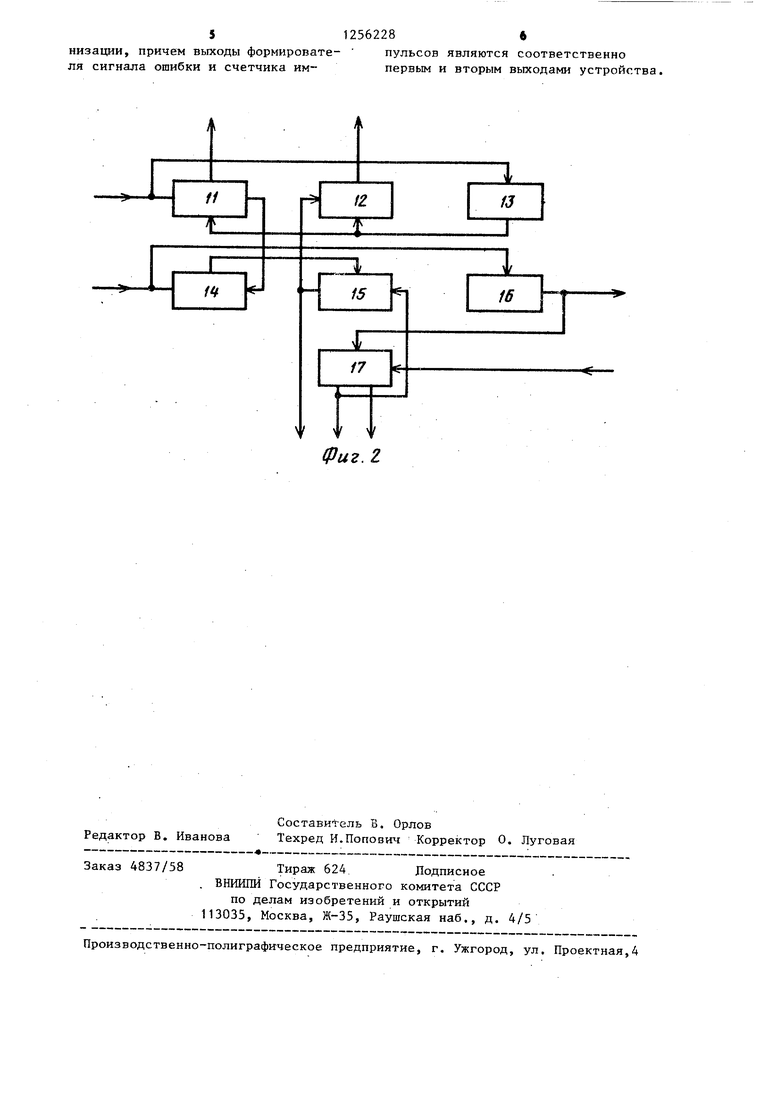

На фиг,1 представлена структурная электрическая схема устройства для обнаружения ошибок по элементам двоичного сигнала , на фиг.2 - структурная электрическая схема блока синхронизации.

Устройство для обнаружения оши- бок по элементам двоичного сигнала содержит блок 1 синхронизации, датчик 2 контрольных сигналов, блок 3 . сравнения, триггер 4 состояний, коммутатор 5 сигналов, регистр 6 сдвига, формирователь 7 сигнала ошибки, счетчик 8 импульсов.

На фиг,1 также представлены датчик 9 испытательных сигналов и дис- кретный канал 10,

Блок 1 синхронизации содержит регистр 11 сдвига, элемент 12 запрета, блок 13 поэлементной синхронизации, блок 14 сравнения сегментов, триггер 15.циклового фазирования, генератор 16 меток цикла, счетчик 17 импульсов

Устройство для обнаружения ошибок по элементам двоичного сигнала работает следующим образом.

Испытательный сигнал с длитель- ностьк) цикла -(равной 32767 элементов) с выхода датчика 9 испытательны сигналов (фиг.1) поступает на вход дискретного канала Ю. С выхода дискретного канала 10 испытательный сигнал поступает на информационный вход блока 1 синхронизации и, пройдя через регистр 11 (фиг,2),. проходит

синхронизации, на выход PC 6 не проходят и не искажают результата измерения, что повышает их точность. Цель достигается введением триггера 4, коммутатора 5, PC 6, ФСО 7 и СИ 8. Дан пример выполнения блока 1 синхронизации. 2 ил.

5

o

5

0

на блок 3 сравнения. В блоке 3 сравнения осуществляется сравнение принятого испытательного сигнала с контрольным сигналом, поступающим с выхода датчика 2 контрольных сигналов.

Сигнал с выхода дискретного канала 10 поступает также на блок 13 поэлементной синхронизации, вьфабаты- вающий тактовые импульсы, которые, проходя через элемент 12 запрета, поступают на тактовый вход датчика 2 контрольных сигналов. Блок 13 поэлементной синхронизации обеспечивает равенство скоростей и совпадение фронтов испытательных и контрольных сигналов, поступающих на блок 3 сравнения.

В моменты включения или нарушения цикловой синхронизации циклы испытательных и контрольных последовательностей совпадать не будут и для проведения измерений необходимо их сфа- зировать, т.е. совместить однозначные элементы циклов. Критерием сбоя цикловой синхронизации является возникновение пакета импульсов несравнения в течение одного цикла, величина которого выбрана равной 22 импульсам. Подсчет импульсов несравнения, выделенных блоком 3 сравнения,- производится счетчиком 17, который устанавливается в исходное состояние импульсами с выхода генератора 16 меток цикла. При появлении второго импульса несравнения в течение одного цикла на выходе второго разряда счетчика 17, являющегося третьим выходом блока 1 синхронизации формируется импульс, который взводит триггер 4 в единицу,а последний, в свою очередь, переводит коммутатор 5 в состояние транслирования импульсов несравнения на тактовый вход регистра 6. В этом случае

импульсы несравнения, поступающие на информационный вход регистра 6, записываются в него, а так как разрядность регистра 6 подобрана таким образом, чтобы до обнаружения сбоя цикловой синхронизации (заполнения импульсами несравнения счетчика 17) на его выходе импульсы несравнения не появятся, то все это время импульсы несравнения хранятся в ре- гистре 6. При заполнении счетчика 17 срабатывает триггер 15 циклового фазирования, который выдает импульс на вход Установка О регистра 6, при этом его все разряды обнуляют- ся. При этом также запрещается выдача тактовых импульсов на датчик 2 контрольных сигналов, останавливая дальнейшую его работу, и запрещается работа блока 3 сравнения, который перестает вьщелять импульсы несравнения. Таким образом, все импульсы несравнения, выделяемые во время сбоев цикловой синхронизации на выхо регистра 6, не проходят и не влияют на результат измерения, а следовательно, не искажают результат измерения, что повышает их точность.

Вследствие того, что в псевдослучайной последовательности, выра- батываемой датчиком 9 испытательных сигналов и соответственно датчиком 2 контрольных сигналов, сегменты последовательности в течение цикла не повторяются, то совпадение сег- мента в регистре 11 с сегментом датчика 2 контрольных сигналов может произойти только один раз в цикл. В момент совпадения сегментов блок 14 сравнения сегментов вырабатывает им- пульс, который сбрасывает триггер 15 циклового фазирования в исходное состояние. При этом разрешается: прохождение тактовых импульсов через элемент 12 запрета на датчик 2 кон- трольных сигналов и разрешается работа блока 3 сравнения. Поиск цикловой синхронизации на этом заканчивается и устройство для обнаружения ошибок по элементам двоичного сигна- ла переходит в режим измерения. При этом триггер 4 сбрасывается в исходное состояние сигналом конца цикла, вырабатываемым генератором 16 меток цикла, и переводит коммутатор 5 в состояние транслирования тактовых импульсов ha регистр 6. Последний транслирует импульсы несравнения на

формирователь 7 сигнала оитбки, в ктором производится их стробирование тактовыми импульсами.

Счетчик 8, осуществляя подсчет тактовых импульсов, поступающих на вход датчика 2 контрольных сигналов фиксирует количество бит принимаемого испытательного сигнала.

Формула изобретения

Устройство для обнаружения ошибок по элементам двоичного сигнала, содержащее последовательно соединенные блок синхронизации, датчик контрольных сигналов и блок сравнения, выход которого подсоединен к входу импульсов несравнения блока синхронизации, информационный вход которого является входом испытательного сигнала устройства, о т л и- чающееся тем, что,с целью повышения точности обнаружения ошибок, в него введены последовательно соединенные триггер состояний, ком- |мутатор сигналов, регистр сдвига и формирователь сигнала ошибки, а также счетчик импульсов, при этом выход блока сравнения подсоединен к первому информационному входу коммутатора сигналов и информационно- му входу регистра сдвига, вход Установка в О которого подключен к первому управляющему выходу блока синхронизации, тактовый выход которого подсоединен к тактовым входам счетчика импульсов и формирователя сигнала ошибки и к второму информа- ,дионному входу коммутатора сигналов выход которого подсоединен к тактовому входу регистра сдвига, а выход регистра сдвига подсоединен к информационному входу формирователя сигнала ошибки, информационный и второй управляющий выходы блока синхронизации подсоединены соответственно к второму информационному и управляющему входам блока сравнения, третий и четвертый управляющие выходы блока синхронизации подсоединены соответственно к входам Установка в 1 и Установка в О триггера состояний, выход которого подсоединен к управляющему входу коммутатора сигналов, а дополнительный выход датчика контрольных сигналов подсоединен к дополнительному информационному входу блока синхро51256228

низации, причем выходы формировате- пульсов являются соответственно ля сигнала ошибки и счетчика им- первым и вторым выходами устройства,

Фиг. г

Редактор В. Иванова

Составитель В. Орлов

Техред И.Попович Корректор О. Луговая

Заказ 4837/58Тираж 624 Подписное

. ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1982 |

|

SU1062881A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство для цикловой синхронизации порогового декодера | 1983 |

|

SU1124441A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010437C1 |

| Устройство для измерения достоверности передачи информации | 1987 |

|

SU1418919A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

Изобретение относится к электросвязи. Повышается точность обна- ружения ошибок. Устр-во содержит блок 1 синхронизации, датчик 2 контрольных сигналов, блок 3 сравнения, триггер 4 состояний, коммутатор 5 сигналов, регистр 6 сдвига (PC), формирователь 7 сигнала ошибки (ФСО), счетчик 8 импульсов (СИ), а также датчик 9 испытательных сигналов и дискретный канал 10, При появлении в течение одного цикла второго импульса несравнения, вьщеленного блоком 3 сравнения, блоком 1 синхрони(Л фиг:1

| Каналы передачи данных | |||

| /Под ред | |||

| Шварцмана В.О | |||

| М., Связь, 1970, с | |||

| АППАРАТ ДЛЯ ОБОГАЩЕНИЯ РУД ПО МЕТОДУ ВСПЛЫВАНИЯ | 1915 |

|

SU279A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-07—Публикация

1984-05-25—Подача