Н зибретенис относится к автоматике и вычислительной технике и может быть использовано для контроля ло- ггтческих схем.

Цель изобретения - увеличение глубины контроля.

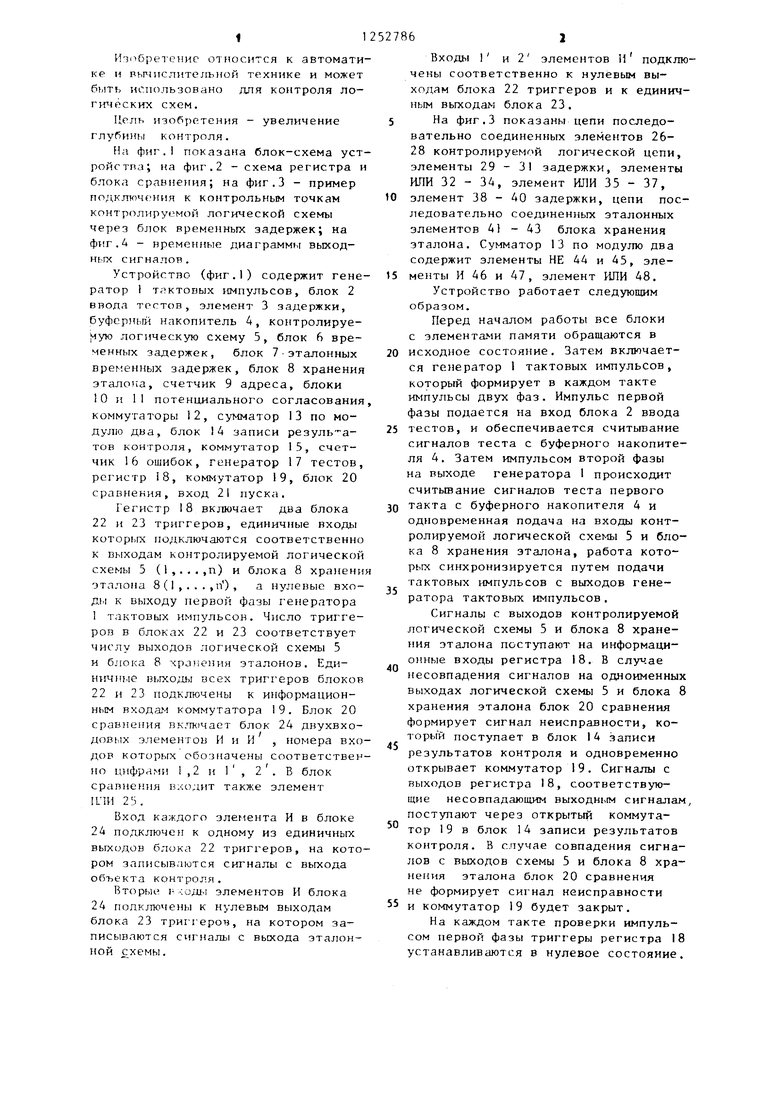

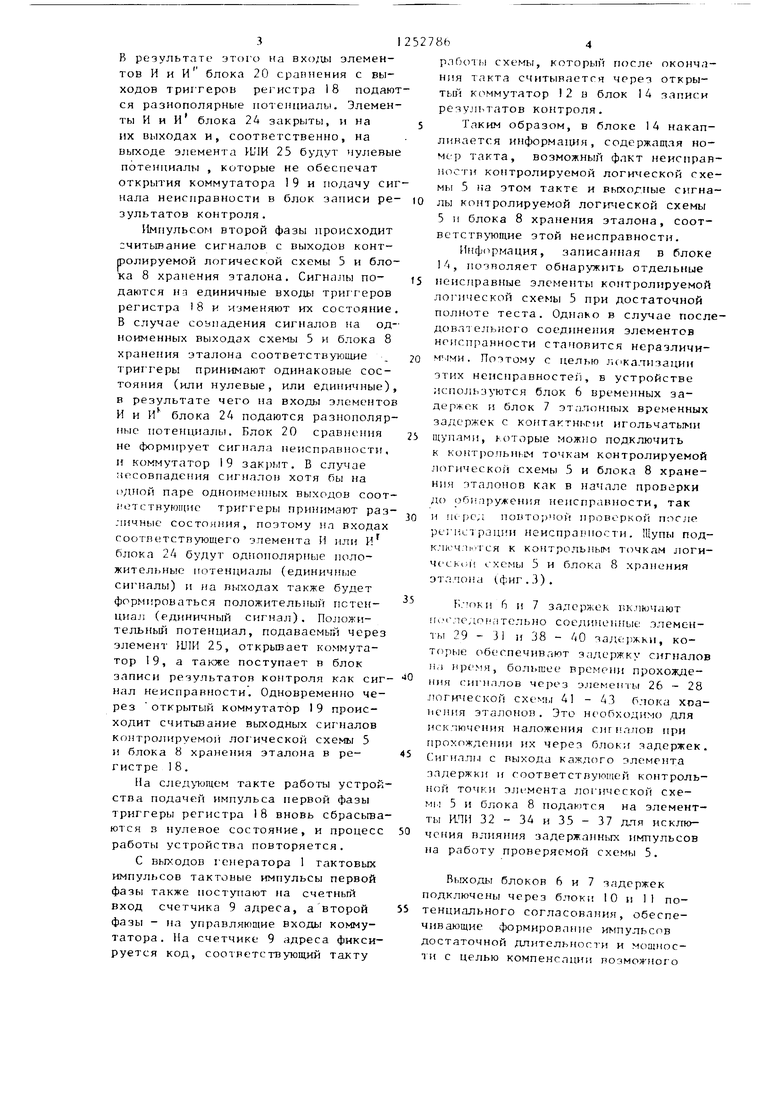

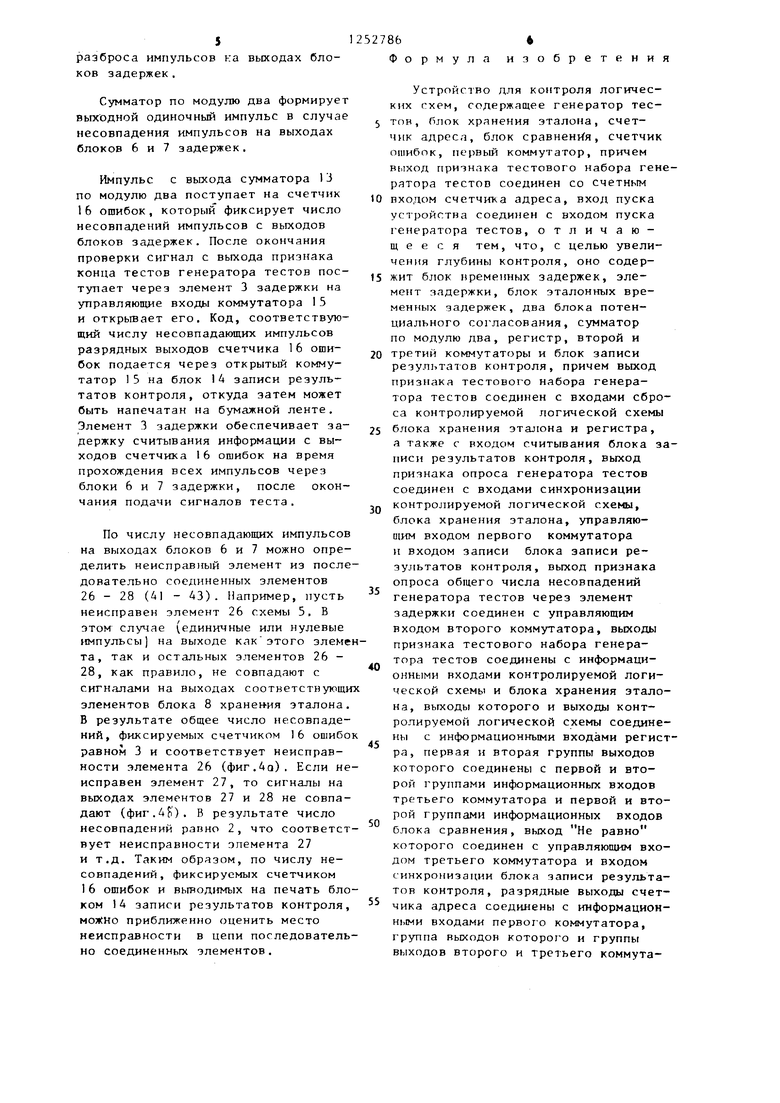

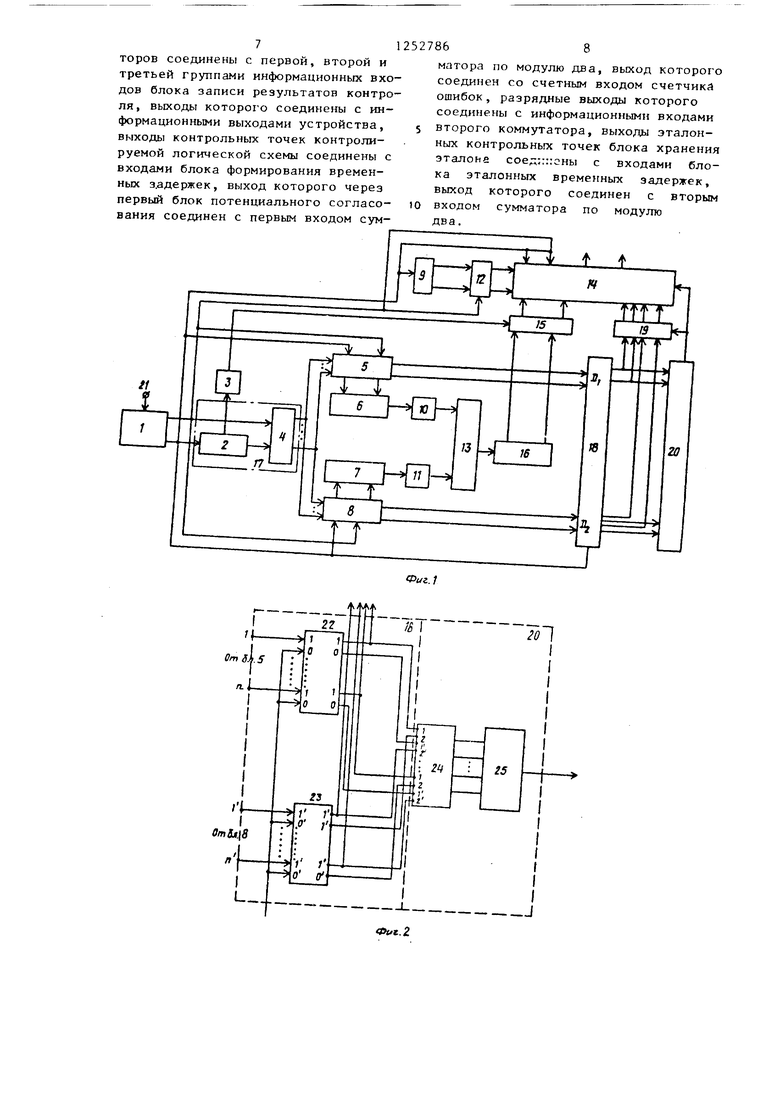

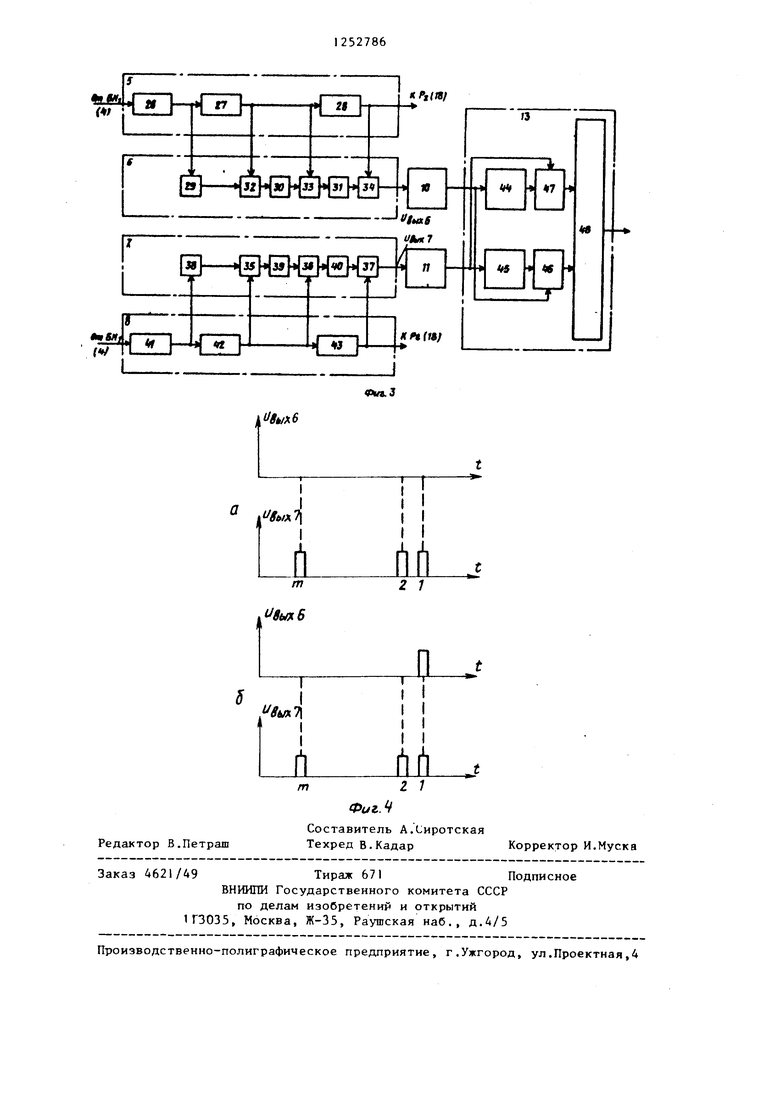

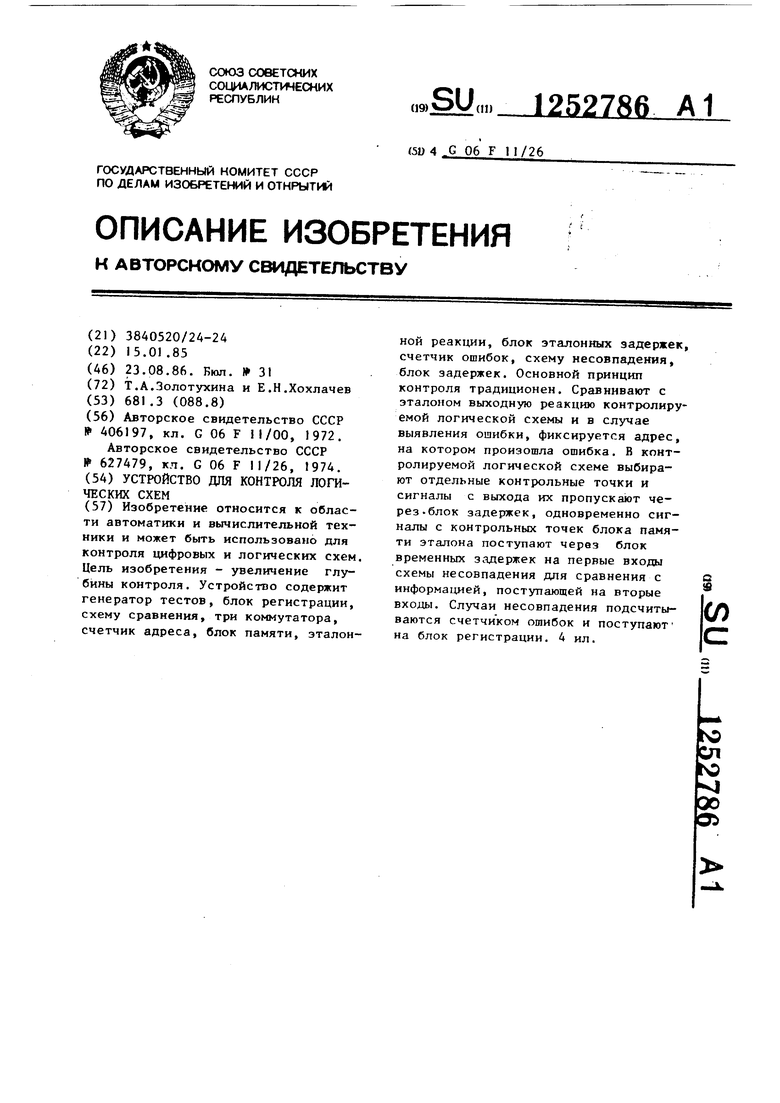

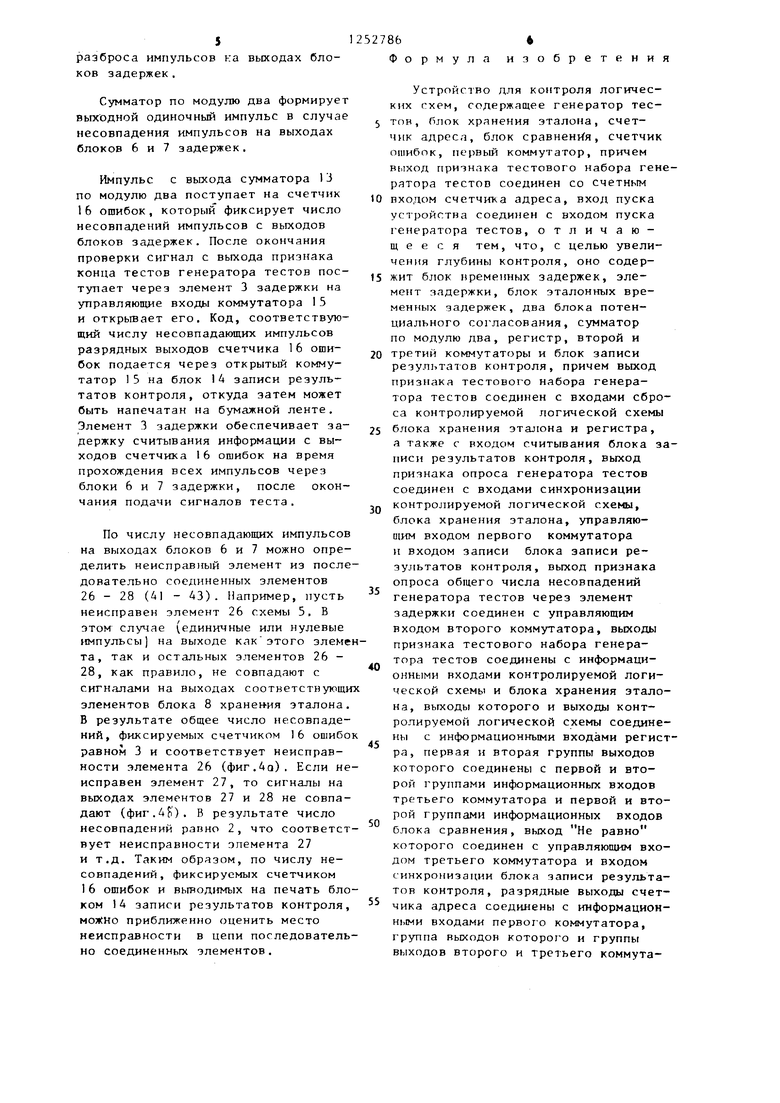

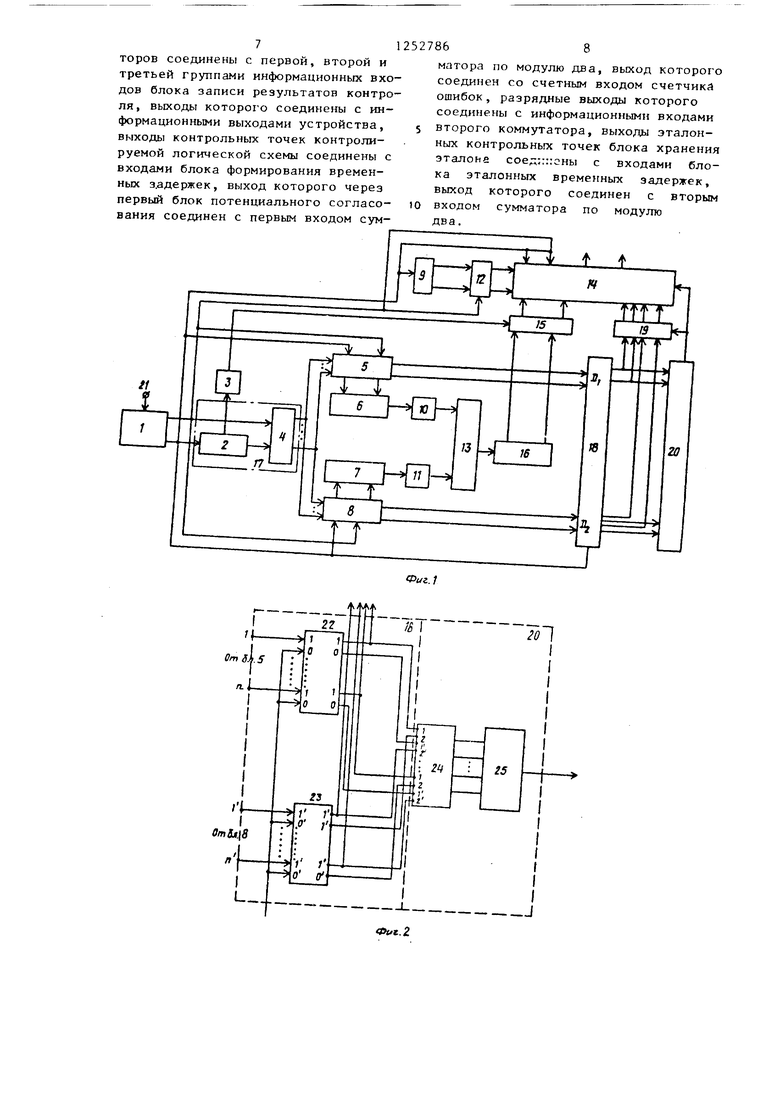

На фиг.1 показана блок-схема уст- ройстпа; на фиг.2 - схема регистра и блока сравнения; на фиг.3 - пример подключения к контрольным точкам контролируемой логической схемы через блок временньгх задержек; на фиг.А - нременные диаграммы выходных сигналов.

Устройство (фиг.1) содержит генератор 1 тяктовых импульсов, блок 2 ввода тостов, элемент 3 задержки, буфсриьш накопитель 4, контролируемую логическую схему 5, блок 6 временных задержек, блок 7 - эталонных временных задержек, блок 8 хранения эталона, счетчик 9 адреса, блоки 10 и 11 потенциального согласования коммутаторы 12, сумматор 13 по мо- два, блок 14 записи резуль а- тов контроля, коммутатор 15, счетчик 16 ошибок, генератор 17 тестов, регистр 18, коммутатор 19, блок 20 сравнения, вход 21 пуска.

Регистр 18 включает два блока 22 и 23 триггеров, единичные входы котор гх подключаются соответственно к выходам контролируемой логической схемы 5 (1,...,п) и блока 8 хранени эталона 8(1,...,п ), а нулевые входы к выходу первой фазы генератора 1 тактовых импульсов. Число триггеров в блоках 22 и 23 соответствует числу выходов логической схемы 5 и блока В хранении эталонов. Единичные выходы всех триггеров блоков 22 и 23 подключены к информационным входам коммутатора 19. Блок 20 сравнения включает блок 24 двухвхо- довых элементов И и fi , номера входов которых обозр1ачены соответственно цифрами 1 ,2 и 1 , 2 . В блок сравнения входит также элемент lUlM 25.

Вход каждого элемента И в блоке 24 подключен к одному из единичных выходов блока 22 триггеров, на котором записываются сигналы с выхода объекта контроля.

Вторые I- -;од1ч элементов И блока 24 подключены к нулевым выходам блока 23 триггеров, на котором записываются сигналы с выхода эталонной схемы.

10

ts

20

25

527862

Входы 1 и 2 элементов И подключены соответственно к нулевым выходам блока 22 триггеров и к единичным выходам блока 23.

На фиг.3 показаны цепи последовательно соединенных элементов 26- 28 контролируемой логической цепи, элементы 29-31 задержки, элементы ИЛИ 32-34, элемент ИЛИ 35-37, элемент 38 - 40 задержки, цепи последовательно соединенных эталонных элементов 41 - 43 блока хранения эталона. Сумматор 13 по модулю два содержит элементы НЕ 44 и 45, элементы И 46 и 47, элемент ИЛИ 48.

Устройство работает следующим образом.

Перед началом работь все блоки с элементами памяти обращаются в исходное состояние. Затем включается генератор 1 тактовых импульсов, который формирует в каждом такте и пyльcы двух фаз. Импульс первой фазы подается на вход блока 2 ввода тестов, и обеспечивается считьгоание сигналов теста с буферного накопителя 4. Затем импульсом второй фазы на выходе генератора 1 происходит считьшание сигналов теста первого такта с буферного накопителя 4 и одновременная подача на входы контролируемой логической схемы 5 и блока 8 хранения эталона, работа которых синхронизируется путем подачи тактовых импульсов с выходов генератора тактовых импульсов.

Сигналы с выходов контролируемой логической схемы 5 и блока 8 хранения эталона поступают на информационные входы регистра 18. В случае несовпадения сигналов на одноименных выходах логической схемы 5 и блока 8 хранения эталона блок 20 сравнения формирует сигнал неисправности, который поступает в блок I4 записи результатов контроля и одновременно открывает коммутатор 19. Сигналы с выходов регистра 18, соответствующие несовпадающим выходным сигналам, поступают через открытый коммутатор 19 в блок 14 записи результатов контроля. В случае совпадения сигналов с выходов схемы 5 и блока 8 хранения эталона блок 20 сравнения не формирует сигнал неисправности и коммутатор 19 будет закрыт.

На каждом такте проверки импульсом первой фазы триггеры регистра 18 устанавливаются в нулевое состояние.

30

35

40

45

50

55

3

в результате этого на входы элементов И и И блока 20 сраянения с выходов триггеров регистра 18 подают ся разиополярные потенциалы. Элементы И и и блока 24 закрыты, и на их выходах и, соответственно, на выходе элемента И 1И 25 будут нулевые потенциалы , которые не обеспечат открьп ия коммутатора 1 9 и подачу сиг нала неисправности в блок записи результатов контроля.

Импульсом второй фазы происходит :читьтание сигналов с выходов контролируемой логической схемы 5 и блока 8 хранения эталона. Сигналы подаются нз единичные входы тригтеров регистра 18 и изменяют их состояние В случае совпадения сигналов на одноименных выходах схемы 5 и блока 8 хранения эталона соответствующие триггерь принимают одинаконые состояния (или нулевые, или един№1ные), в результате чего на входы элементов И и И блока 24 подаются разнополяр- ные потенциалы. Блок 20 сравнения не формирует сигнала неисправности, и коммутатор 19 закрыт. Б случае несовпадения сигналов хотя бы на паре одноименных выходов соответствующие триггеры принимают раз- .1ИЧН1,1е состояния, поэтому на входах соответствующего элемента И или И блока 24 будут однополярные положительные потенциалы (единичные сигналы) и на выходах также будет формироваться положительный пстен- циа; (единичный сигнал). Положительный потенциал, подаваемый через элемент Ш1И 25, открывает коммутатор 19, а также поступает в блок записи результатов контроля как сигнал неисправности. Одновременно через открытый коммутатор I9 происходит считывание выходных сигналов контролируемо) логической схемы 5 и блока 8 хранения эталона в регистре 1 8.

На след пощем такте работы устройства подачей импульса первой фазы триггеры регистра 18 вновь сбрасываются в нулевое состояние, и процесс работы устройства повторяется.

С вьгходов генератора 1 тактовых импульсов тактовые импульсы первой фазы также поступают на счетный вход счетчика 9 адреса, а второй фазы - на управляющие входы коммутатора, lia счетчике 9 адреса фиксируется код, соответствующий такту

527864

рлОспы схемы, который после окончания такта считывается через откры- тый коммутатор 12 в блок 14 записи

результатов контроля.

5 Таким образом, в блоке 14 накапливается информация, содержащая номер такта, возможный факт неиспрал- ности контролируемой логической схе- мы 5 на этом такте и выходные сигна- 10 лы контролируемой лог1Г1еской схемы 5 и блока 8 хранения эталона, соот- встств тощие этой неисправности.

Информация, записа1{ная в блоке 14, позволяет обнаружить отдельные 15 неисправные элементы ко1ттролируемой логической схемы 5 при достаточной полноте теста. Однако в случае после- ДОВЛ1ельяого соединения элементов неисправности становится неразличи- 20 M -iMH. Поэтому с целью локализации этих неиснравносте, в устройстве используются блок 6 време)шых задержек и блок 7 эт; лонных временных задержек с контактнычи игольчатыми 25 щупами, кс)торые можно подключить

к контрольным точкам контролируемой логической схемы 5 и блока В хранения эталонов как в начале npoDi pxH до оГи Пружения неисправности, так 30 и гк рол повторной проверкой после pei iici рации неиспрашюсти. Щупы под- к.чюч.ъчгся к контрольнь М точкам логи- чс ской схемы 5 и блока 8 хранения этл.чона (фиг . 3) .

Ь.- оки б и 7 задержек включают

1Г1 гледонптельно соединенные элементы 29-31 и 38 - 40 задержки, которые обеспечивают задержку сигналов н) нрс мя, большее времеш прохождения сигнллов через элеметч, 26 - 28 логической cxcNibi 41 - 43 блока хса- нения эталонов . Это нс обходимо для исключения наложения сигнллов при прохождении их через блоки задержек.

Сигнллм с выхода каждого элемента

задержки и соответствующей контрольной точки элемента логической схе- мю 5 и блока 8 подаются на элемент- ты НИИ 32 - 34 и 35 - 37 для исклк 0

50

чср(ия нлия1П1я задержанных имнульсов на работу проверяемой схемы 5.

Выходы блоков 6 и 7 задержек подключены через блоки 10 и 11 по- тенциального согласования, обеспечивающие формирование и 1пульсов достаточной длительности и мощнос- 1И с целью компенсации возможного

разброса импульсов ка выходах блоков задержек,

Сумматор по модулю два формирует выходной одиночный импульс в случае несовпадения импульсов на выходах блоков 6 и 7 задержек.

Импульс с выхода сумматора 13 по модулю два поступает на счетчик 16 ошибок, который фиксирует число несовпадений импульсов с выходов блоков задержек. После окончания проверки сигнал с выхода признака конца тестов генератора тестов поступает через элемент 3 задержки на управляющие входы коммутатора 15 и открьтает его. Код, соответствующий числу несовпадающих импульсов разрядных выходов счетчика 16 ошибок подается через открытый коммутатор 15 на блок 14 записи результатов контроля, откуда затем может быть напечатан на бумажной ленте, Элемент 3 задержки обеспечивает задержку считывания информации с выходов счетчика 16 ошибок на время прохождения всех импульсов через блоки 6 и 7 задержки, после окончания подачи сигналов теста ,

По числу несовпадающих импульсов на выходах блоков 6 и 7 можно определить неисправ)1ый элемент из последовательно соединенных элементов 26 - 28 (41 - 43). Например, пусть неисправен элемент 26 схемы 5, В этом случае (единичные или нулевые импульсы) на выходе клк этого элемета, так и остальных элементов 26 - 28, как правило, не совпадают с сигналами на выходах соответствующи элементов блока 8 хранен-ия эталона, В результате общее число несовпадений, фиксируемых счетчиком 16 ошибо равном 3 и соответствует неисправности элемента 26 (фиг,Да). Если неисправен элемент 27, то сигналы на выходах элементов 27 и 28 не совпадают (фиг.), В результате число несовпадений равно 2, что соответствует неисправности элемента 27 и т,д. Таким образом, по числу несовпадений, фиксируемых счетчиком 16 ошибок и вьтодимых на печать блоком 14 записи результатов контроля, можно приближенно оценить место неисправности в цепи последовательно соединенных элементов,

р м у л а

и

«

3 о б р

е т е н и я

Устройство для контроля логических схем, содержащее генератор тестов, блок хранения эталона, счетчик адреса, блок сравнену я, счетчик ошибок, первый коммутатор, причем В.1ход признака тестового набора генератора тестов соединен со счетным

входом счетчика адреса, вход пуска устройства соединен с входом пуска генератора тестов, отличающееся тем, что, с целью увеличения глубины контроля, оно содержит блок нремеиных задержек, элемент задержки, блок эталонных временных задержек, два блока потенциального согласования, сумматор по модулю два, регистр, второй и третий коммутаторы и блок записи результатов контроля, причем выход признака тестового набора генератора тестов соединен с входами сброса контрол1фуеиой логической схемы блока хранения эталона и регистра, а также с входом считывания блока записи результатов контроля, выход признака опроса генератора тестов соединен с входами синхронизации контролируемой логической схемы, блока хранения эталона, управляющим входом первого коммутатора и входом записи блока записи результатов контроля, выход признака опроса общего числа несовпадений генератора тестов через элемент задержки соединен с управляющим входом второго коммутатора, выходы признака тестового набора генератора тестов соединены с информационными входами контролируемой логической схемы и блока хранения эталона, выходы которого и выходы контролируемой логической схемы соединены с информационными входами регистра, первая и вторая группы выходов которого соединены с первой и второй группами информационных входов третьего коммутатора и первой и второй группами информационных входов блока сравнения, выход Не равно которого соединен с управляющим входом третьего коммутатора и входом синхронизации блока записи результатов контроля, разрядные выходы счетчика адреса соединены с информацион- Н1,1ми входами первого коммутатора, группа выходов которог о и группы выходов второго и третьего коммута

71

торов соединены с первой, второй и третьей группами информационных входов блока записи результатов контроля, выходы которого соединены с информационными выходами устройства, выходы контрольных точек контролируемой логической схемы соединены с входами блока формирования временных э.адержек, выход которого через первый блок потенциального согласования соединен с первым входом сум52786

матора по модулю два, выход которого соединен со счетным входом счетчика ошибок, разрядные выходы которого соединены с информационными входами 5 второго коммутатора, выходы эталонных контрольных точек блока хранения эталона соед;:::сны с входами блока эталонных временных задержек, выход которого соединен с вторым 10 входом сумматора по модулю два.

« ffiaf

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1111171A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля цифровых блоков | 1980 |

|

SU943733A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ РАБОТОСПОСОБНОСТИ ОБЪЕКТОВ | 1992 |

|

RU2036505C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля цифровых и логических схем. Цель изобретения - увеличение глубины контроля. Устройство содержит генератор тестов, блок регистрации, схему сравнения, три коммутатора, счетчик адреса, блок памяти, эталонной реакции, блок эталонных задержек, счетчнк ошибок, схему несовпадения, блок задержек. Основной принцип контроля традиционен. Сравнивают с эталоном выходную реакцию контролируемой логической схемы и в случае выявления ошибки, фиксируется адрес, на котором произошла ошибка. В контролируемой логической схеме выбирают отдельные контрольные точки и сигналы с выхода их пропускают через- блок задержек, одновременно сигналы с контрольных точек блока памяти эталона поступают через блок временных задержек на первые входы схемы несовпадения для сравнения с информацией, поступающей на вторые входы. Случаи несовпадения подсчитываются счетчиком ошибок и поступают на блок регистрации. 4 ил. Q в СЛ

м

т вмб

ИfiL

/п2 7

f1hl

т

Редактор В.Петраш

Составитель А.Сиротская Техред В.Кадар

Заказ 4621/49Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1Г3035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

2 ;

Фиг.

Корректор И.Муска

| УСТРОЙСТВО для ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ В ЛОГИЧЕСКИХ СХЕМАХ | 0 |

|

SU406197A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для диагностики дискретных блоков | 1974 |

|

SU627479A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1985-01-15—Подача