со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство допускового контроля параметров | 1991 |

|

SU1798719A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОСЕВОГО ПЕРЕМЕЩЕНИЯ ВАЛА | 1996 |

|

RU2129212C1 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| Устройство для регулирования массовых расходов смешиваемых продуктов | 1988 |

|

SU1695273A1 |

| Устройство для регулирования расхода | 1986 |

|

SU1377832A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для автоматизированной градуировки датчика силы | 1988 |

|

SU1606889A1 |

| Устройство для контроля и диагностики состояний объекта | 1989 |

|

SU1679468A1 |

| Устройство для градуировки датчиков силы | 1989 |

|

SU1682845A1 |

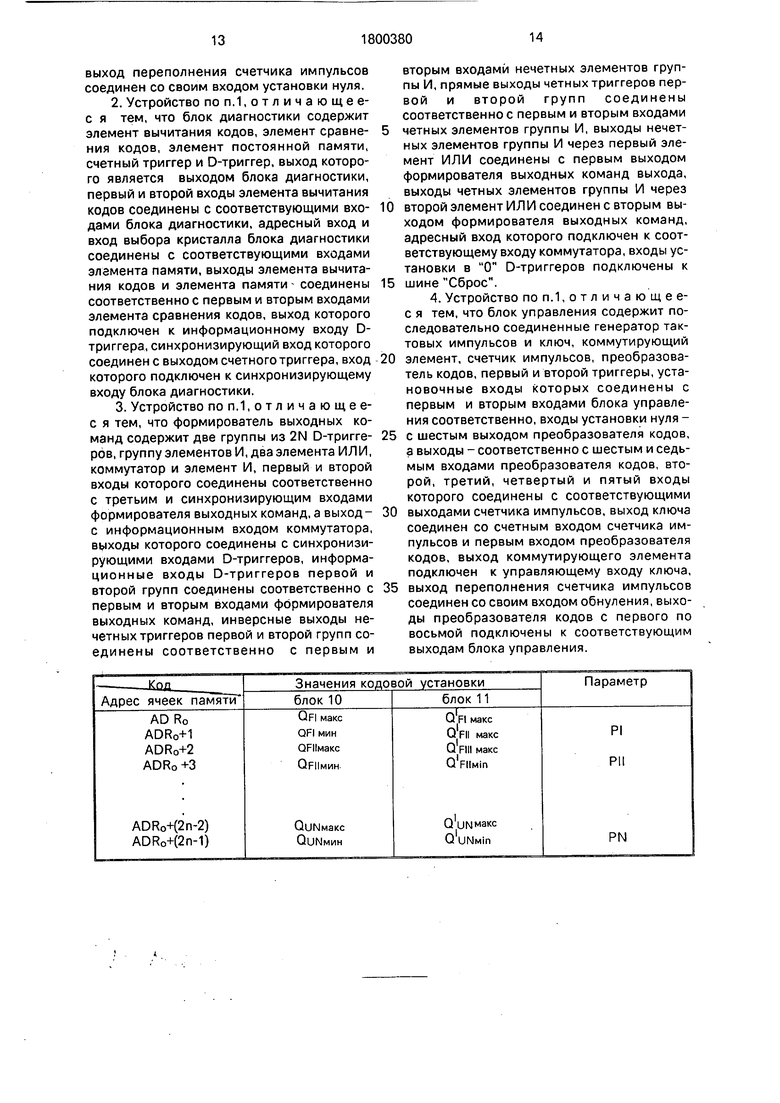

Изобретение относится к измерительной технике и предназначено для использования в устройствах предупредительной и аварийной сигнализации. Сущность изобретения: устройство содержит два измерительных канала, каждый из которых включает N датчиков 1-1...1-N и 2-1...2-N и N параметра преобразователей 3-1...3-N и 4- 1...4-N текущих значений параметра в код, два элемента ИЛИ 5 и 6, два регистра 7 и 8, блок 9 управления, четыре блока 10-13 памяти, два блока 14 и 15 вычитания, два блока 16 и 17 сравнения, два коммутатора 18 и 19, блок 20 диагностики, счетчик 21 импульсов и формирователь 22 выходных команд с соответствующими связями. 3 з.п. ф-лы, 7 ил.

Изобретение относится к измерительной технике и предназначено для использования в системах предупредительной, аварийной и других видах сигнализации повышенной надежности.

Цель изобретения - расширение области применения устройства за счет обеспечения возможности контроля N параметров, измеряемых датчиками разного типа (как частотно-импульсными, так и аналоговыми).

Цель достигается тем, что в устройство допускового контроля параметров, содержащее счетчик импульсов, формирователь выходных команд, выходы которого являются выходами устройства, и два измерительных канала, каждый из которых включает последозательно соединенные датчик параметра и преобразователь текущих значений параметра в код, введены два элемента ИЛИ, два регистра, два коммутатора, блок управления, четыре блока памяти, два блока

вычитания, блок диагностики, два блока сравнения кодов и в каждый измерительный канал включены N-1 датчиков и N-1 преобразователей текущих значений параметра в код, причем выход каждого из N-1 датчиков соединен с входом соответствующего преобразователя текущих значений параметра в код, информационные выходы преобразователей первого измерительного канала через первый регистр подключены к информационным входам третьего блока памяти и к первым группам входов первого блока вычитания и первого блока сравнения кодов, информационные выходы преобразователей текущих значений параметров в код второго измерительного канала через второй регистр подключены к информационным входам четвертого блока памяти и к первым группам входов второго блока вычитания и второго блока сравнения кодов, синхронизирующие выходы преобразователей

00

о о

со

00

о

текущих значений параметров в код первого и второго измерительных каналов через первый и второй элементы ИЛИ подключены к соответствующим входам блока управления, первый и второй выходы которого через первый и второй коммутаторы подключены к входам опроса преобразователей текущих значений параметров в код соответственно первого и второго измерительных каналов, третий и четвертый выходы блока управления соединены с входами разрешения записи первого и второго регистров соответственно, пятый выход этого блока соединен с входами выбора кристаллов третьего и четвертого блоков памяти и блока диагностики, шестой выход блока управления соединен с входами разрешения чтения третьего и четвертого блоков, памяти, выходы которых подключены к вторым входам первого и второго блоков вычитания соответственно, седьмой выход блока управления соединен с входами выбора кристаллов первого и второго блоков памяти и синхронизирующим входом блока диагностики, выход которого подключен к третьему входу формирователя выходных команд, первый и второй входы которого соединены с выходами соответствующих блоков сравнения, восьмой выход блока управления подключен к синхронизирующему входу формирователя выходных команд и счетному входу счетчика импульсов, выходы которого соединены с адресными входами блоков памяти, формирователя выходных команд, коммутаторов и блока диагностики, первый и второй входы которого соединены с выходами соответствующих блоков вычитания, выходы первого и второго блоков памяти соединены с вторыми входами первого и второго блоков сравнения кодов соответственно, а выход переполнения счетчика импульсов соединен со своим входом установки нуля.

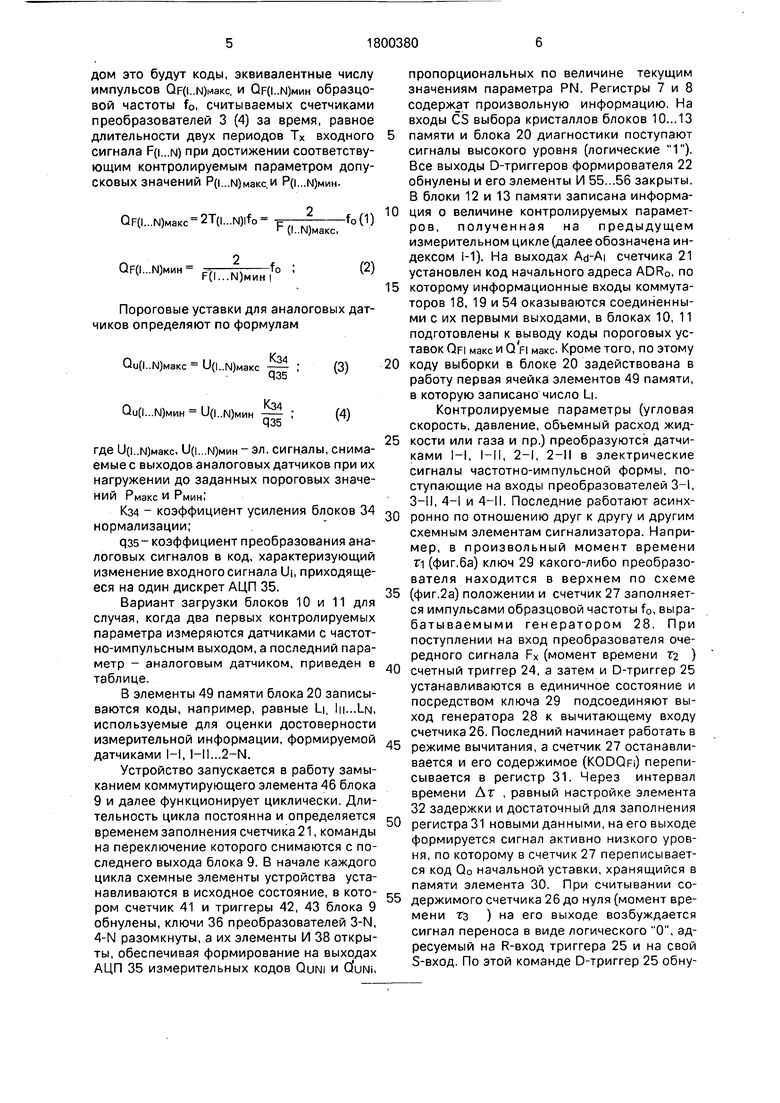

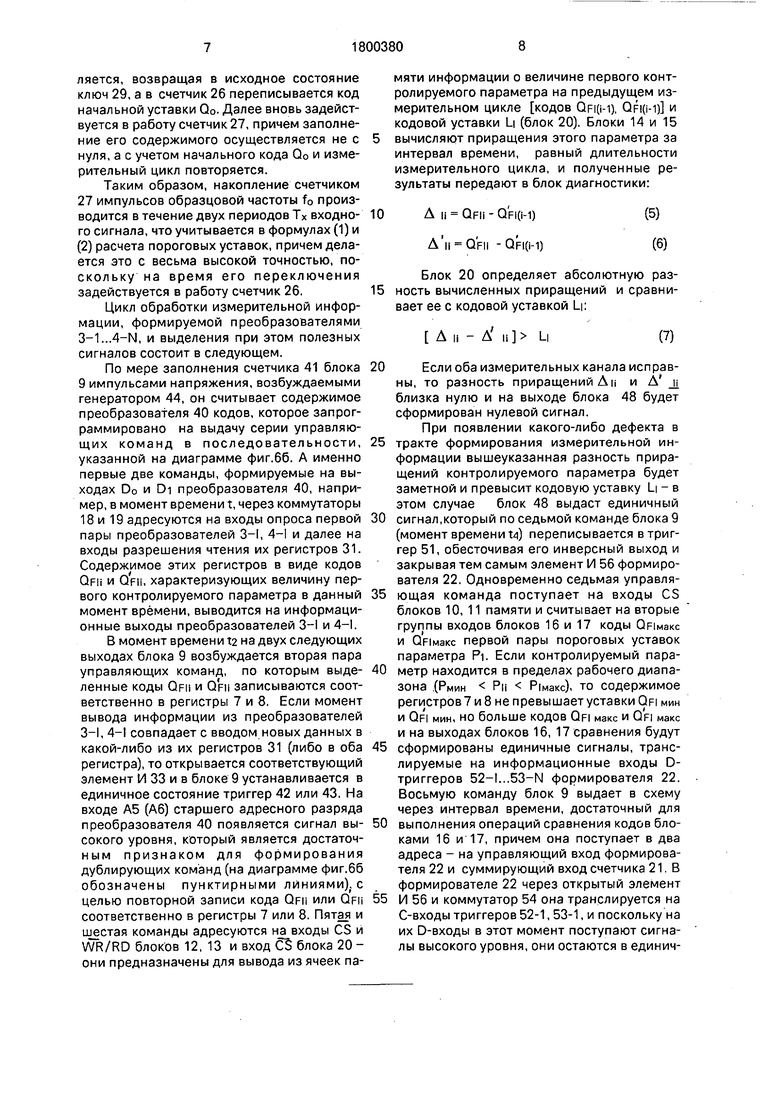

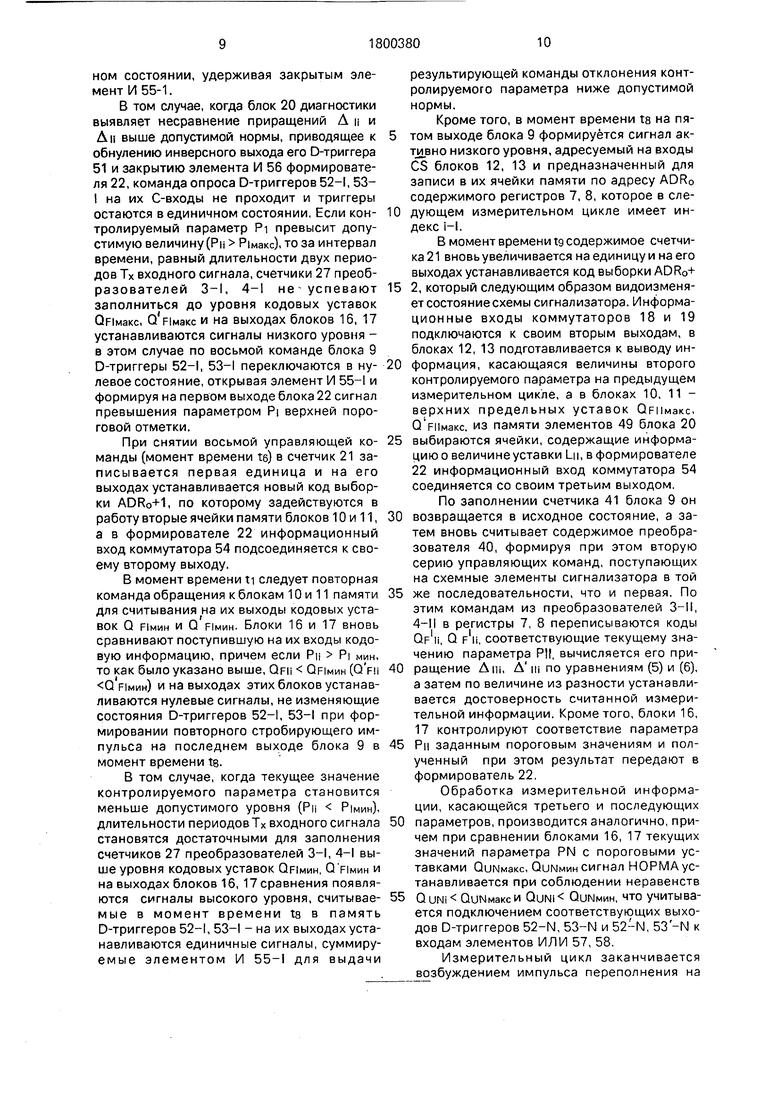

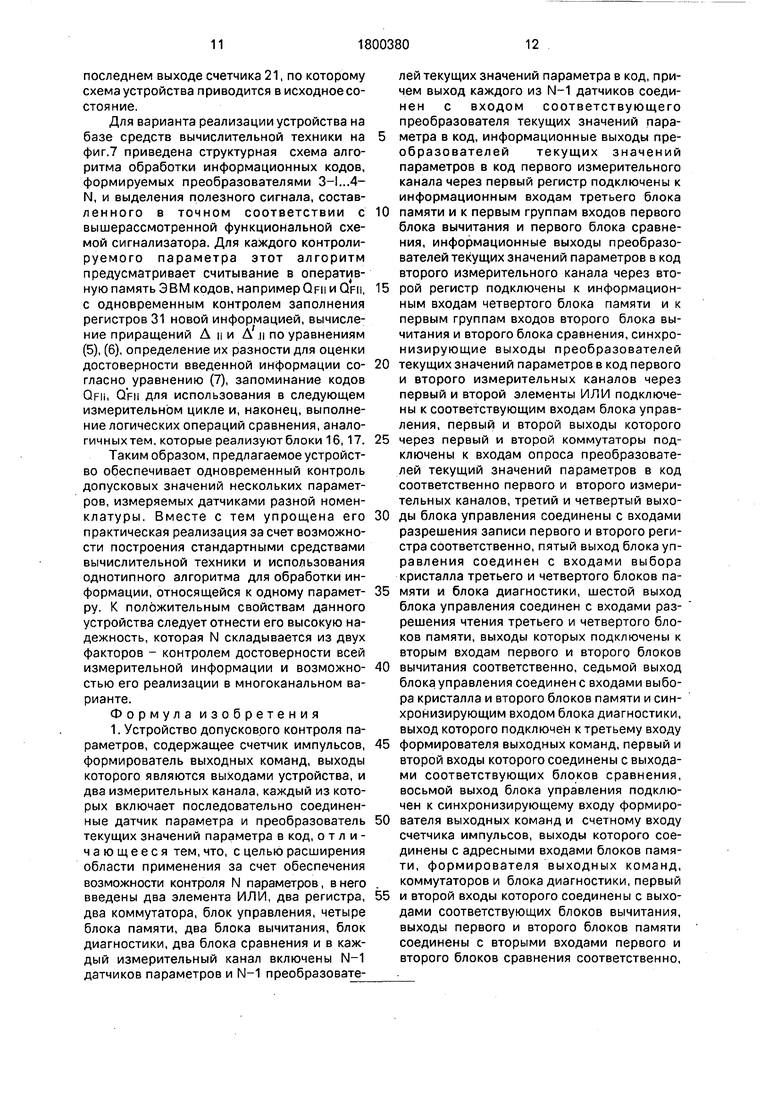

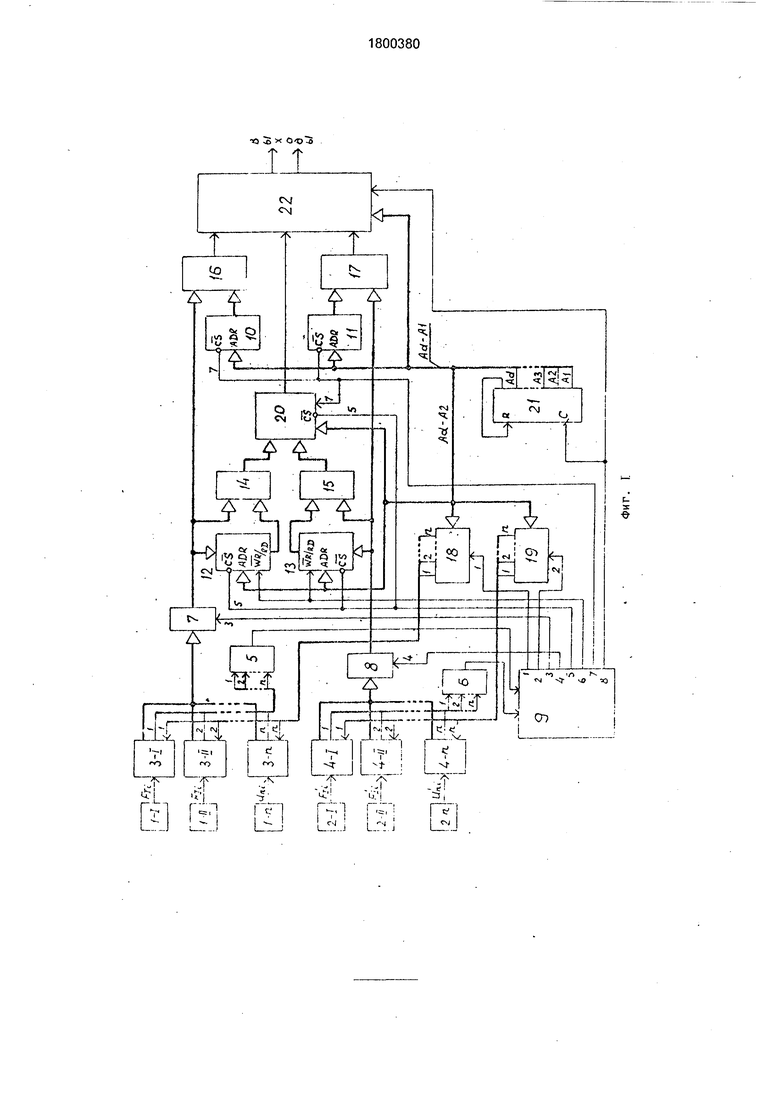

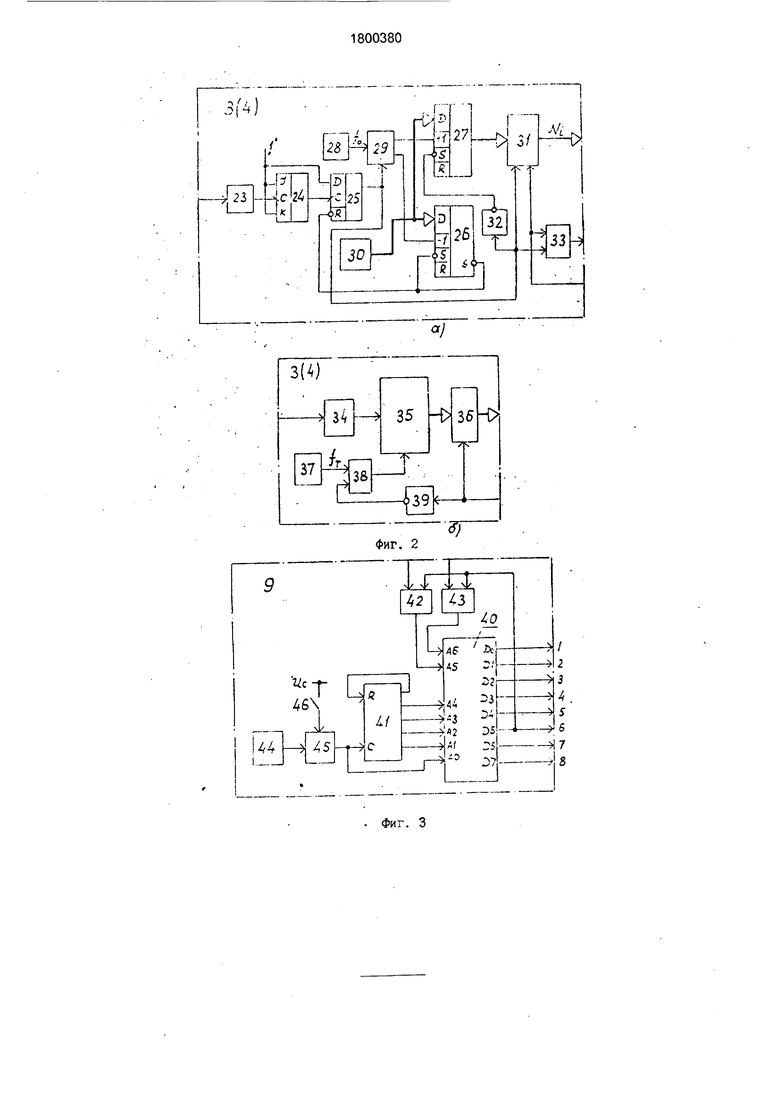

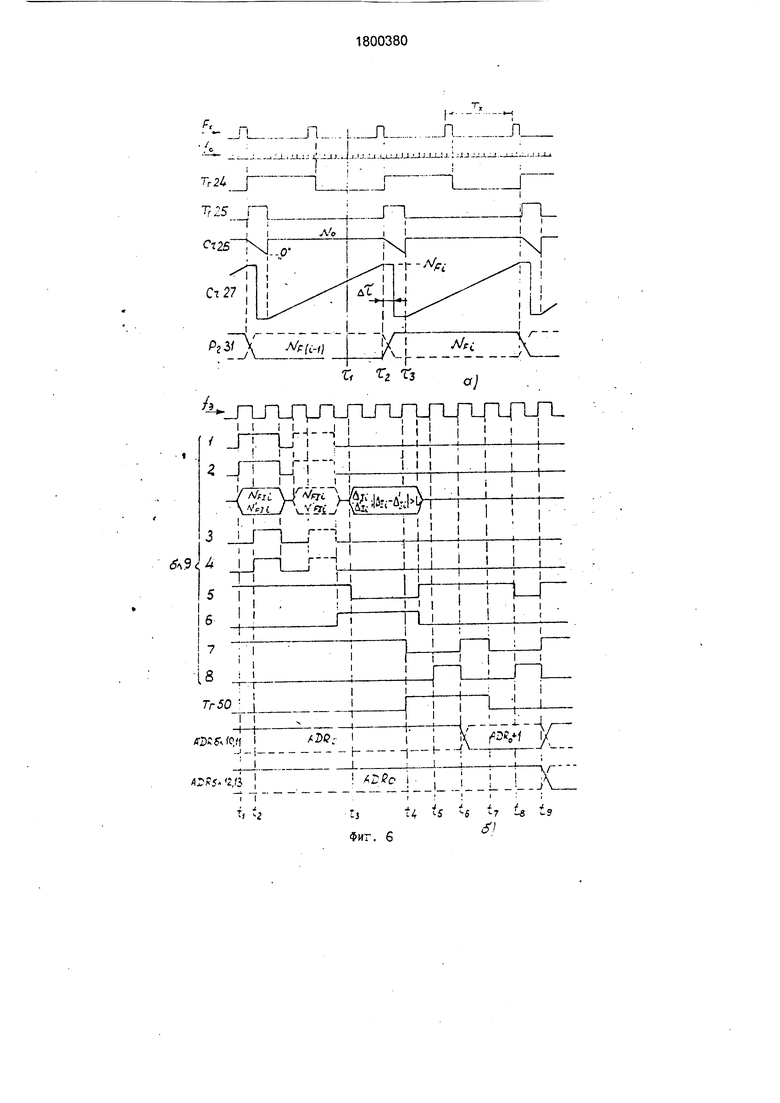

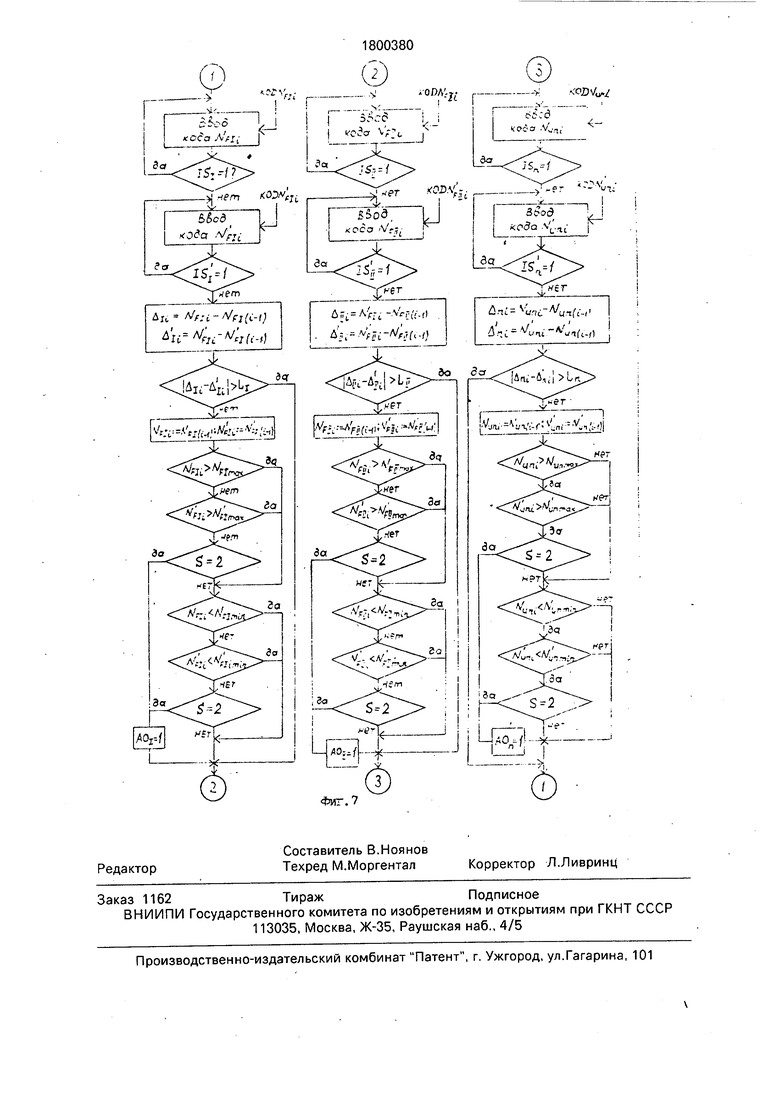

На фиг.1 приведена функциональная электрическая схема устройства, на фиг.2 - варианты построения преобразователей текущих значений параметра в код для датчиков с частотно-импульсным и аналоговым выходами; на фиг.З, 4 и 5 - схемы блока управления, блока диагностики и формирователя выходных команд соответственно; на фиг.6 - временные диаграммы, поясняющие принцип действия устройства; на фиг.7 - структурная схема алгоритма измерительной информации и формирования результирующих сигналов.

Устройство содержит (фиг.1) датчики I-I, I-II...I-N и 2-I, 2-М...2-N контролируемых параметров PI, PII....PN, преобразователи 3-I, 3-II...3-N и 4-I, 4-II...4-N текущих значений

параметров и код, относящиеся соответственно к первому и второму измерительным каналам, элементы ИЛИ 5, 6, регистры 7, 8, блок 9 управления, блоки 10...13 памяти,

блоки 14, 15 вычитания, блоки 16, 17 сравнения кодов, коммутаторы 18, 19, блок 20 диагностики, счетчик 21 импульсов и формирователь 22 выходных команд.

Каждый из преобразователей 3 (4),

0 предназначенный для обработки частотно- импульсного сигнала, в предлагаемом варианте содержит (фиг.2а) формирователь 23 импульсов, счетный триггер 24, D-триггер 25, два счетчика 26 и 27 импульсов, генера5 тор 28 образцовой частоты f0, ключ 29, элемент 30 памяти, регистр 31, элемент 32 задержки и элемент И 33.

В состав преобразователей 3 (4), работающих с датчиками аналогового типа, на0 пример, входят (фиг.26) блоки 34 нормализации входного сигнала, аналого- цифровой преобразователь (АЦП) 35, ключи 36, генератор 37 тактовой частоты fT, элемент И 38 и элемент НЕ 39.

5Блок 9 управления в простейшем варианте содержит (фиг.З) преобразователь 40 кодов, управляемый счетчиком 41 импульсов, два RS-триггера 42, 43, генератор 44 тактовых импульсов, ключ 45 и коммутирую0 щий элемент 46.

Блок 20 предназначен для контроля достоверности измерительной информации, считываемой с выходов преобразователей 3, 4, и включаем субблоки вычитания 47 и

5 сравнения 48 кодов, элементы 49, постоянной памяти, счетный триггер 50 и D-триггер 51.

Формирователь 22 (фиг.5) имеет две группы 0-триггеров52, 53, количество кото0 рых в каждой группе равно удвоенному числу контролируемых параметров, коммутатор 54, элементы И 55-1...55-N, 56 и элементы ИЛИ 57, 58.

При необходимости устройство может

5 иметь третий измерительный канал, построенный аналогично первым двум. При этом блок 20 диагностики имеет дополнительные узлы для попарного сравнения измерительной информации всех трех каналов, а

0 формирователь 22 - еще одну группу D - триггеров-и, например, элементы мажоритарной свертки выходных сигналов.

Устройство работает следующим образом.

5Предварительно в блоки 10 и 11 памяти вводят данные, относящиеся к пороговым уставкам контролируемых параметров и вычисленные с учетом градуировочных характеристик их датчиков Н, I-II...2-N. Для измерительных средств с частотным выходом это будут коды, эквивалентные числу импульсов Ор(..м)макс. и QF(I..N)MHH образцовой частоты f0, считываемых счетчиками преобразователей 3 (4) за время, равное длительности двух периодов Тх входного сигнала F(I...N) при достижении соответствующим контролируемым параметром допу- сковых значений Р(|...м)макс. и Р(|...м)мин.

QF(I...N)MaKC 2T(|...N)|fo -р

(..М)макс,

-fo(D

QF(I...N)MHH

F(I...N)MMH

-fo

Пороговые уставки для аналоговых датчиков определяют по формулам

Qu(I..N)M3KC 11(|..М)макс I(3)

Ои(1...М)мин U(|..N)MHH ;(4) Ч JO

где 1)(|..ы)макс, U(I...N)MHH - эл. сигналы, снимаемые с выходов аналоговых датчиков при их нагружении до заданных пороговых значений Рмакс И РМИН,

Кз4 - коэффициент усиления блоков 34 нормализации;

q35- коэффициент преобразования аналоговых сигналов в код, характеризующий изменение входного сигнала Ui, приходящееся на один дискрет АЦП 35.

Вариант загрузки блоков 10 и 11 для случая, когда два первых контролируемых параметра измеряются датчиками с частотно-импульсным выходом, а последний параметр - аналоговым датчиком, приведен в таблице.

В элементы 49 памяти блока 20 записываются коды, например, равные LI, III...LN, используемые для оценки достоверности измерительной информации, формируемой датчиками l-l, I-II...2-N.

Устройство запускается в работу замыканием коммутирующего элемента 46 блока 9 и далее функционирует циклически. Длительность цикла постоянна и определяется временем заполнения счетчика 21, команды на переключение которого снимаются с последнего выхода блока 9. В начале каждого цикла схемные элементы устройства устанавливаются в исходное состояние, в котором счетчик 41 и триггеры 42, 43 блока 9 обнулены, ключи 36 преобразователей 3-N, 4-N разомкнуты, а их элементы И 38 открыты, обеспечивая формирование на выходах АЦП 35 измерительных кодов QUNI и C/UNI,

пропорциональных по величине текущим значениям параметра PN. Регистры 7 и 8 содержат произвольную информацию. На входы CS выбора кристаллов блоков 10... 13

5 памяти и блока 20 диагностики поступают сигналы высокого уровня (логические 1). Все выходы D-триггеров формирователя 22 обнулены и его элементы И 55...56 закрыты. В блоки 12 и 13 памяти записана информа10 ция о величине контролируемых параметров, полученная на предыдущем измерительном цикле (далее обозначена индексом И). На выходах Ad-Ai счетчика 21 установлен код начального адреса ADR0, по

15 которому информационные входы коммутаторов 18, 19 и 54 оказываются соединенными с их первыми выходами, в блоках 10, 11 подготовлены к выводу коды пороговых ус- тавок QFI макс и Q FI макс. Кроме того, по этому

20 коду выборки в блоке 20 задействована в работу первая ячейка элементов 49 памяти, в которую записано число LI.

Контролируемые параметры (угловая скорость, давление, объемный расход жид25 кости или газа и пр.) преобразуются датчиками I-, l-ll, 2-I, 2-II в электрические сигналы частотно-импульсной формы, поступающие на входы преобразователей 3-I, 3-И, 4-I и 4-Н. Последние работают асинх30 ронно по отношению друг к другу и другим схемным элементам сигнализатора. Например, в произвольный момент времени Ti (фиг.ба) ключ 29 какого-либо преобразователя находится в верхнем по схеме

35 (фиг.2а) положении и счетчик 27 заполняется импульсами образцовой частоты f0, вырабатываемыми генератором 28, При поступлении на вход преобразователя очередного сигнала Fx (момент времени TI )

40 счетный триггер 24, а затем и D-триггер 25 устанавливаются в единичное состояние и посредством ключа 29 подсоединяют выход генератора 2.8 к вычитающему входу счетчика 26. Последний начинает работать в

45 режиме вычитания, а счетчик 27 останавливается и его содержимое (KODQFi) переписывается в регистр 31. Через интервал времени Ат , равный настройке элемента 32 задержки и достаточный для заполнения

50 регистра 31 новыми данными, на его выходе формируется сигнал активно низкого уровня, по которому в счетчик 27 переписывается код QO начальной уставки, хранящийся в памяти элемента 30. При считывании со55 держимого счетчика 26 до нуля (момент времени тз ) на его выходе возбуждается сигнал переноса в виде логического О, адресуемый на R-вход триггера 25 и на свой S-вход. По этой команде D-триггер 25 обнуляется, возвращая в исходное состояние ключ 29, а в счетчик 26 переписывается код начальной уставки Q0. Далее вновь задейст- вуется в работу счетчик 27, причем заполнение его содержимого осуществляется не с нуля, а с учетом начального кода do и измерительный цикл повторяется.

Таким образом, накопление счетчиком 27 импульсов образцовой частоты fo производится в течение двух периодов Тх входно- го сигнала, что учитывается в формулах (1) и (2) расчета пороговых уставок, причем делается это с весьма высокой точностью, поскольку на время его переключения задействуется в работу счетчик 26.

Цикл обработки измерительной информации, формируемой преобразователями 3-1...4-N, и выделения при этом полезных сигналов состоит в следующем.

По мере заполнения счетчика 41 блока 9 импульсами напряжения, возбуждаемыми генератором 44, он считывает содержимое преобразователя 40 кодов, которое запрограммировано на выдачу серии управляющих команд в последовательности, указанной на диаграмме фиг.бб. А именно первые две команды, формируемые на выходах Do и DI преобразователя 40, например, в момент времени t, через коммутаторы 18 и 19 адресуются на входы опроса первой пары преобразователей З-l, 4-I и далее на входы разрешения чтения их регистров 31. Содержимое этих регистров в виде кодов QFII и QFH, характеризующих величину первого контролируемого параметра в данный момент времени, выводится на информационные выходы преобразователей 3-1 и 4-1.

В момент времени t2 на двух следующих выходах блока 9 возбуждается вторая пара управляющих команд, по которым выде- ленные коды QFII и QFII записываются соответственно в регистры 7 и 8, Если момент вывода информации из преобразователей 3-1, 4-1 совпадает с вводом новых данных в какой-либо из их регистров 31 (либо в оба регистра), то открывается соответствующий элемент И 33 и в блоке 9 устанавливается в единичное состояние триггер 42 или 43. На входе А5 (А6) старшего адресного разряда преобразователя 40 появляется сигнал вы- сокого уровня, который является достаточным признаком для формирования дублирующих команд (на диаграмме фиг.бб обозначены пунктирными линиями), с целью повторной записи кода QFM или QFM соответственно в регистры 7 или 8. Пятая и шестая команды адресуются на входы CS и WR/RD блоков 12,13 и вход 65 блока 20 - они предназначены для вывода из ячеек памяти информации о величине первого контролируемого параметра на предыдущем измерительном цикле кодов QFI(M), QFI(H) и кодовой уставки LI (блок 20). Блоки 14 и 15 вычисляют приращения этого параметра за интервал времени, равный длительности измерительного цикла, и полученные результаты передают в блок диагностики:

А и QFII - Q FI(H) A ii QFii -QFiO-1)

(5) (6)

Блок 20 определяет абсолютную разность вычисленных приращений и сравнивает ее с кодовой уставкой LI:

Д и - Д и Li

(7)

Если оба измерительных канала исправны, то разность приращений Ли и А и близка нулю и на выходе блока 48 будет сформирован нулевой сигнал.

При появлении какого-либо дефекта в тракте формирования измерительной информации вышеуказанная разность приращений контролируемого параметра будет заметной и превысит кодовую уставку U - в этом случае блок 48 выдаст единичный сигнал,который по седьмой команде блока 9 (момент временим) переписывается в триггер 51, обесточивая его инверсный выход и закрывая тем самым элемент И 56 формирователя 22. Одновременно седьмая управляющая команда поступает на входы CS блоков 10, 11 памяти и считывает на вторые группы входов блоков 16 и 17 коды QFIMBKC и QpiMaicc первой пары пороговых уставок параметра PL Если контролируемый параметр находится в пределах рабочего диапазона .(Рмин PII Р|макс), то содержимое регистров и 8 не превышает уставки QFI мин и QF I мин, но больше кодов QFI макс и QFI макс и на выходах блоков 16, 17 сравнения будут сформированы единичные сигналы, транслируемые на информационные входы D- триггеров 52-I...53-N формирователя 22. Восьмую команду блок 9 выдает в схему через интервал времени, достаточный для выполнения операций сравнения кодов блоками 16 и 17, причем она поступает в два адреса - на управляющий вход формирователя 22 и суммирующий вход счетчика 21. В формирователе 22 через открытый элемент И 56 и коммутатор 54 она транслируется на С-входы триггеров 52-1, 53-1, и поскольку на их D-входы в этот момент поступают сигналы высокого уровня, они остаются в единичном состоянии, удерживая закрытым элемент И 55-1.

В том случае, когда блок 20 диагностики выявляет несравнение приращений А и и А и выше допустимой нормы, приводящее к обнулению инверсного выхода его D-триггера 51 и закрытию элемента И 56 формирователя 22, команда опроса D-триггеров 52-I, 53- I на их С-входы не проходит и триггеры остаются в единичном состоянии, Если контролируемый параметр Pi превысит допустимую величину (Рм Рыакс), то за интервал времени, равный длительности двух периодов Тх входного сигнала, счетчики 27 преобразователей З-l, 4-I не-успевают заполниться до уровня кодовых уставок Ор1макс, О. и на выходах блоков 16, 17 устанавливаются сигналы низкого уровня - в этом случае по восьмой команде блока 9 D-триггеры 52-I, 53-I переключаются в нулевое состояние, открывая элемент И 55-I и формируя на первом выходе блока 22 сигнал превышения параметром PI верхней пороговой отметки.

При снятии восьмой управляющей команды (момент времени te) в счетчик 21 записывается первая единица и на его выходах устанавливается новый код выборки ADRo+1, по которому задействуются в работу вторые ячейки памяти блоков 10 и 11, а в формирователе 22 информационный вход коммутатора 54 подсоединяется к своему второму выходу.

В момент времени ti следует повторная команда обращения к блокам 10 и 11 памяти для считывания на их выходы кодовых уставок Q FIMHH и Q FIMHH. Блоки 16 и 17 вновь сравнивают поступившую на их входы кодовую информацию, причем если Рн PI мин, то как было указано выше, QFM ОРЫИН (О рм Q FIMHH) и на выходах этих блоков устанавливаются нулевые сигналы, не изменяющие состояния D-триггеров 52-I, 53-I при формировании повторного стробирующего импульса на последнем выходе блока 9 в момент времени te.

В том случае, когда текущее значение контролируемого параметра становится меньше допустимого уровня (Рн Р|Мин), длительности периодовТх входного сигнала становятся достаточными для заполнения счетчиков 27 преобразователей З-l, 4-I выше уровня кодовых уставок QFIMI/IH, Q FIMMH и на выходах блоков 16, 17 сравнения появляются сигналы высокого уровня, считываемые в момент времени ta в память D-триггеров 52-I, 53- - на их выходах устанавливаются единичные сигналы, суммируемые элементом И 55-I для выдачи

результирующей команды отклонения контролируемого параметра ниже допустимой нормы.

Кроме того, в момент времени ts на пятом выходе блока 9 формируется сигнал активно низкого уровня, адресуемый на входы CS блоков 12, 13 и предназначенный для записи в их ячейки памяти по адресу ADR0 содержимого регистров 7, 8, которое в сле0 дующем измерительном цикле имеет индекс i-l.

В момент времени tg содержимое счетчика 21 вновь увеличивается на единицу и на его выходах устанавливается код выборки ADR0+

5 2, который следующим образом видоизменяет состояние схемы сигнализатора. Информационные входы коммутаторов 18 и 19 подключаются к своим вторым выходам, в блоках 12, 13 подготавливается к выводу ин0 формация, касающаяся величины второго контролируемого параметра на предыдущем измерительном цикле, а в блоках 10, 11 - верхних предельных уставок Орпмакс, О рИмакс. из памяти элементов 49 блока 20

5 выбираются ячейки, содержащие информацию о величине уставки LM, в формирователе 22 информационный вход коммутатора 54 соединяется со своим третьим выходом. По заполнении счетчика 41 блока 9 он

0 возвращается в исходное состояние, а затем вновь считывает содержимое преобразователя 40, формируя при этом вторую серию управляющих команд, поступающих на схемные элементы сигнализатора в той

5 же последовательности, что и первая. По этим командам из преобразователей 3-II, 4-И в регистры 7, 8 переписываются коды QF M, Q Р И, соответствующие текущему значению параметра Р||, вычисляется его при0 ращение Am, А ш по уравнениям (5) и (6), а затем по величине из разности устанавливается достоверность считанной измерительной информации. Кроме того, блоки 16, 17 контролируют соответствие параметра

5 РН заданным пороговым значениям и полученный при этом результат передают в формирователь 22.

Обработка измерительной информации, касающейся третьего и последующих

0 параметров, производится аналогично, причем при сравнении блоками 16, 17 текущих значений параметра PN с пороговыми ус- тавками Оиымакс, биммин сигнал НОРМА устанавливается при соблюдении неравенств

5 QUNI QuNwaKcH QuNi QUNMHH, что учитыва- ется подключением соответствующих выходов D-триггеров 52-N, 53-N и 521N, 53 -N к входам элементов ИЛИ 57, 58.

Измерительный цикл заканчивается возбуждением импульса переполнения на

последнем выходе счетчика 21, по которому схема устройства приводится в исходное состояние.

Для варианта реализации устройства на базе средств вычислительной техники на фиг.7 приведена структурная схема алгоритма обработки информационных кодов, формируемых преобразователями 3-I...4- N, и выделения полезного сигнала, составленного в точном соответствии с вышерассмотренной функциональной схемой сигнализатора. Для каждого контролируемого параметра этот алгоритм предусматривает считывание в оперативную память ЭВМ кодов, например QFM и QFM, с одновременным контролем заполнения регистров 31 новой информацией, вычисление приращений А ц и А и по уравнениям (5), (6), определение их разности для оценки достоверности введенной информации со- гласно уравнению (7), запоминание кодов QFII, QFII для использования в следующем измерительном цикле и, наконец, выполнение логических операций сравнения, анало- гичныхтем, которые реализуют блоки 16, 17.

Таким образом, предлагаемое устройство обеспечивает одновременный контроль допусковых значений нескольких параметров, измеряемых датчиками разной номенклатуры. Вместе с тем упрощена его практическая реализация за счет возможности построения стандартными средствами вычислительной техники и использования однотипного алгоритма для обработки информации, относящейся к одному парамет- ру. К положительным свойствам данного устройства следует отнести его высокую надежность, которая N складывается из двух факторов - контролем достоверности всей измерительной информации и возможно- стью его реализации в многоканальном варианте.

Формула изобретения

возможности контроля N параметров, в него введены два элемента ИЛИ, два регистра, два коммутатора, блок управления, четыре блока памяти, два блока вычитания, блок диагностики, два блока сравнения и в каждый измерительный канал включены N-1 датчиков параметров и N-1 преобразовате-

лей текущих значений параметра в код, причем выход каждого из N-1 датчиков соединен с входом соответствующего преобразователя текущих значений параметра в код, информационные выходы преобразователей текущих значений параметров в код первого измерительного канала через первый регистр подключены к информационным входам третьего блока памяти и к первым группам входов первого блока вычитания и первого блока сравнения, информационные выходы преобразователей текущих значений параметров в код второго измерительного канала через второй регистр подключены к информационным входам четвертого блока памяти и к первым группам входов второго блока вычитания и второго блока сравнения,синхронизирующие выходы преобразователей текущих значений параметров в код первого и второго измерительных каналов через первый и второй элементы ИЛИ подключены к соответствующим входам блока управления, первый и второй выходы которого через первый и второй коммутаторы подключены к входам опроса преобразователей текущий значений параметров в код соответственно первого и второго измерительных каналов, третий и четвертый выходы блока управления соединены с входами разрешения записи первого и второго регистра соответственно, пятый выход блока управления соединен с входами выбора кристалла третьего и четвертого блоков памяти и блока диагностики, шестой выход блока управления соединен с входами разрешения чтения третьего и четвертого блоков памяти, выходы которых подключены к вторым входам первого и второго блоков вычитания соответственно, седьмой выход блока управления соединен с входами выбора кристалла и второго блоков памяти и синхронизирующим входом блока диагностики, выход которого подключен к третьему входу формирователя выходных команд, первый и второй входы которого соединены с выходами соответствующих блоков сравнения, восьмой выход блока управления подключен к синхронизирующему входу формирователя выходных команд и счетному входу счетчика импульсов, выходы которого соединены с адресными входами блоков памяти, формирователя выходных команд, коммутаторов и блока диагностики, первый и второй входы которого соединены с выходами соответствующих блоков вычитания, выходы первого и второго блоков памяти соединены с вторыми входами первого и второго блоков сравнения соответственно,

выход переполнения счетчика импульсов соединен со своим входом установки нуля.

вторым входами нечетных элементов группы И, прямые выходы четных триггеров первой и второй групп соединены соответственное первым и вторым входами четных элементов группы И, выходы нечетных элементов группы И через первый элемент ИЛИ соединены с первым выходом формирователя выходных команд выхода, выходы четных элементов группы И через второй элемент ИЛИ соединен с вторым выходом формирователя выходных команд, адресный вход которого подключен к соответствующему входу коммутатора, входы установки в О D-триггеров подключены к шине Сброс.

08C008Ipv n

J i.

Тг Г3

«;

Фиг.

| Устройство допускового контроля частоты | 1982 |

|

SU1149175A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сигнализатор предельных значений угловой скорости | 1984 |

|

SU1296941A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-03-07—Публикация

1991-02-06—Подача