00

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и диагностики состояний технического объекта | 1987 |

|

SU1504653A1 |

| Устройство контроля состояния объектов | 1985 |

|

SU1366993A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1980 |

|

SU888119A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФИЗИЧЕСКОГО ПАРАМЕТРА В СКВАЖИНЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013534C1 |

| Устройство для обучения операторов | 2016 |

|

RU2615836C1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОТКЛОНЕНИЯ САМОХОДНОЙ МАШИНЫ ОТ ПРОЕКТНОЙ ОСИ | 1996 |

|

RU2119053C1 |

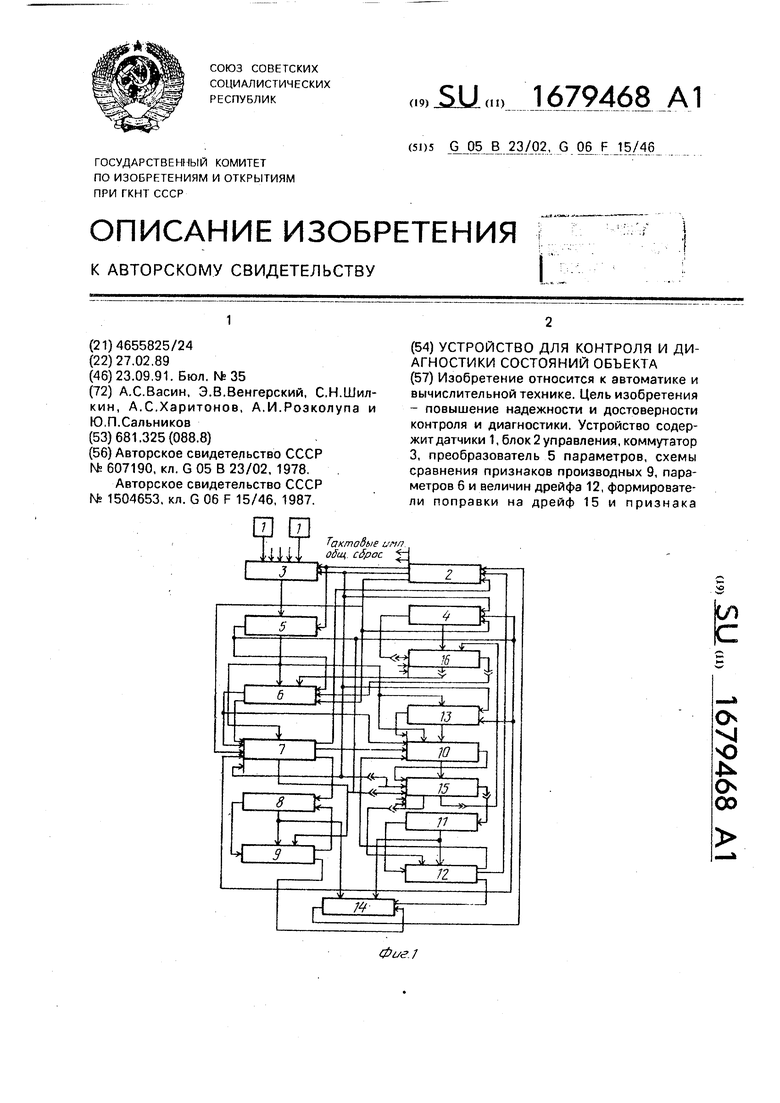

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение надежности и достоверности контроля и диагностики. Устройство содержит датчики 1, блок 2 управления, коммутатор 3, преобразователь 5 параметров, схемы сравнения признаков производных 9, параметров 6 и величин дрейфа 12, формирователи поправки на дрейф 15 и признака

о

о

Јь

о

00

производной 7, блоки хранения эталонных признаков производных 8, измерений параметров первого цикла 13 и допусков 4, блок 14 индикации и блок 16 коррекции пороговых значений параметра. Контроль и диаг- ностироаание с применением коррекции пороговых значений измеряемых параметИзобретение относится к автоматике и вычислительной технике и предназначено для распознавания аварийных состояний объектов контроля.

Целью изобретения является повышение надежности и достоверности контроля и диагностики.

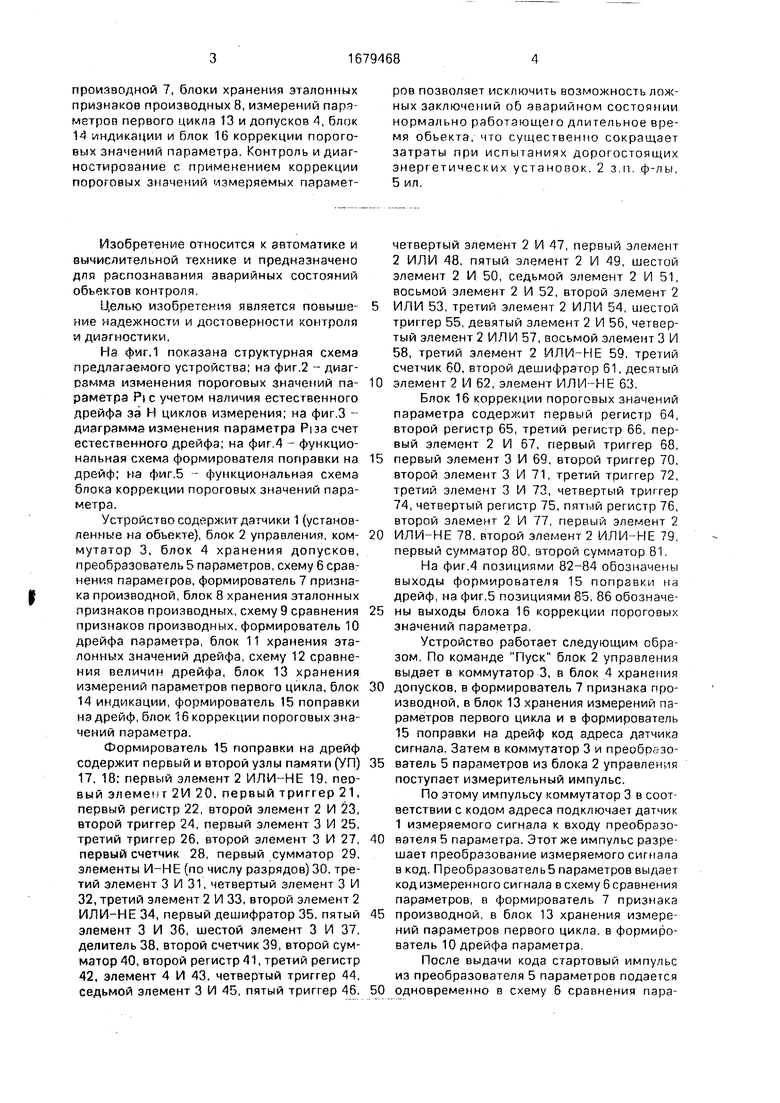

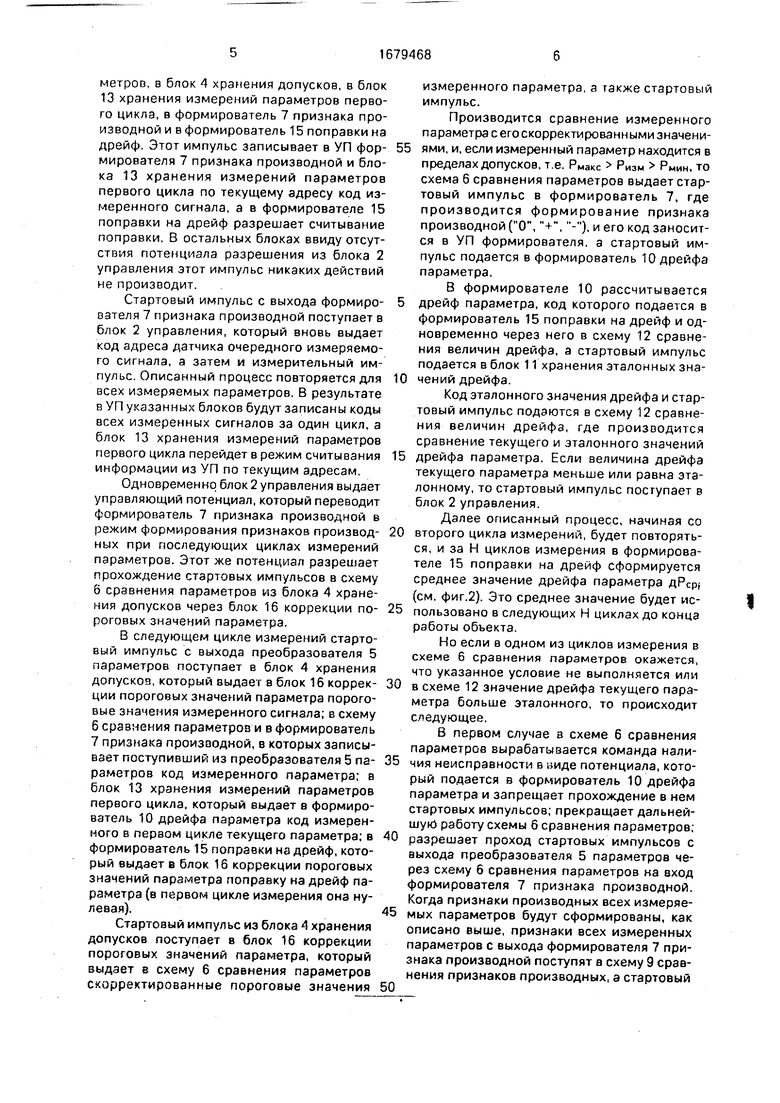

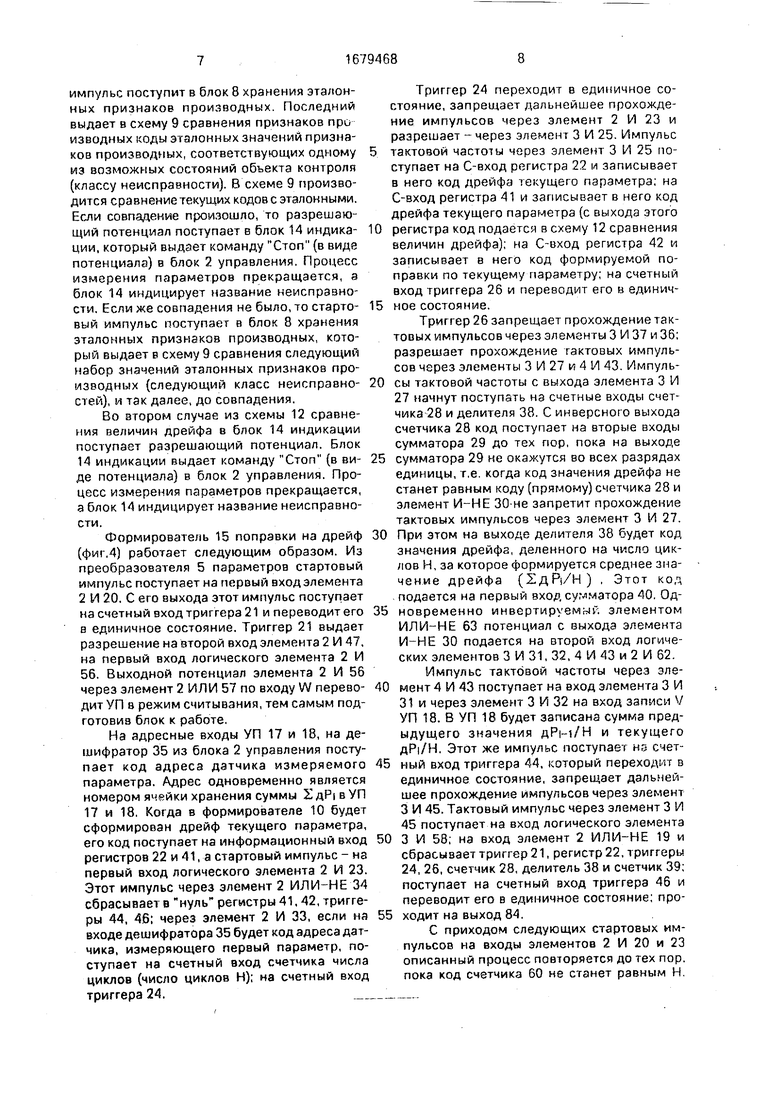

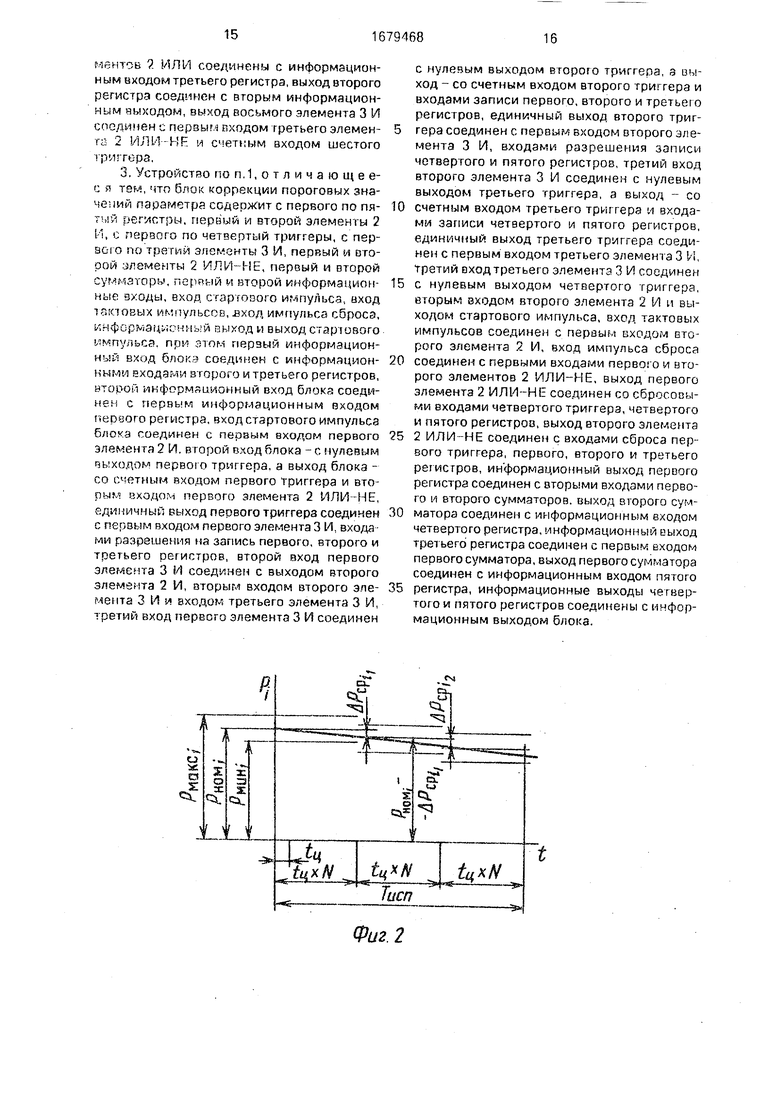

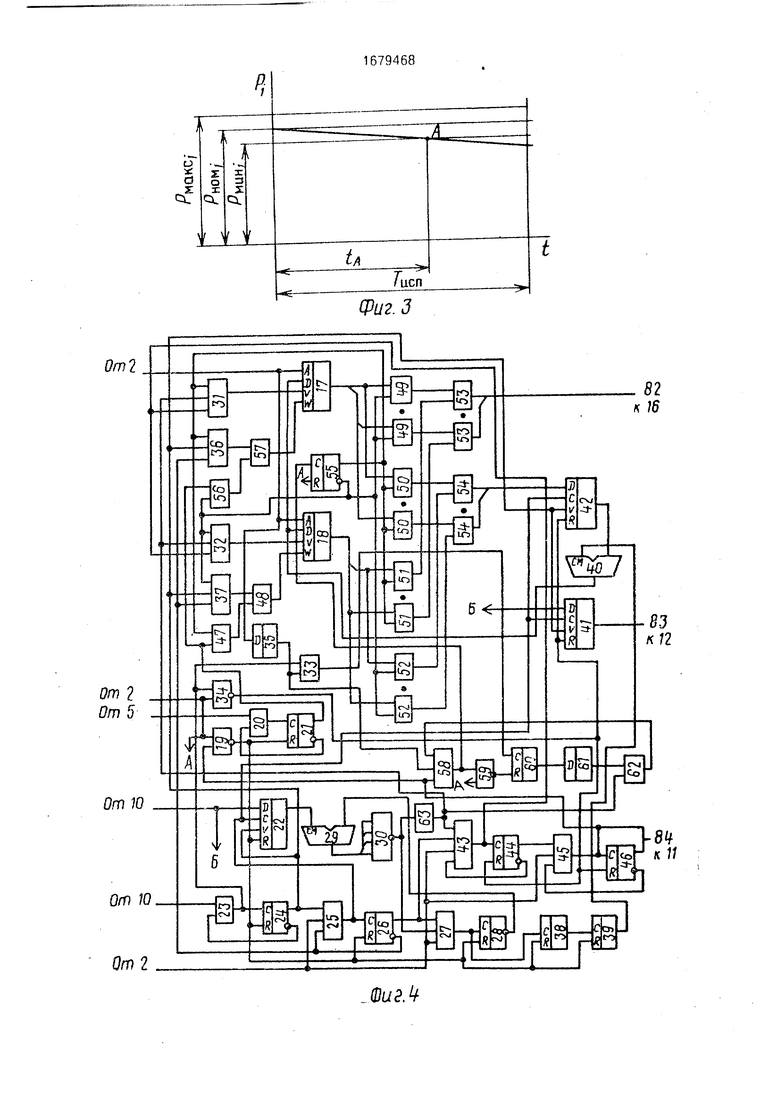

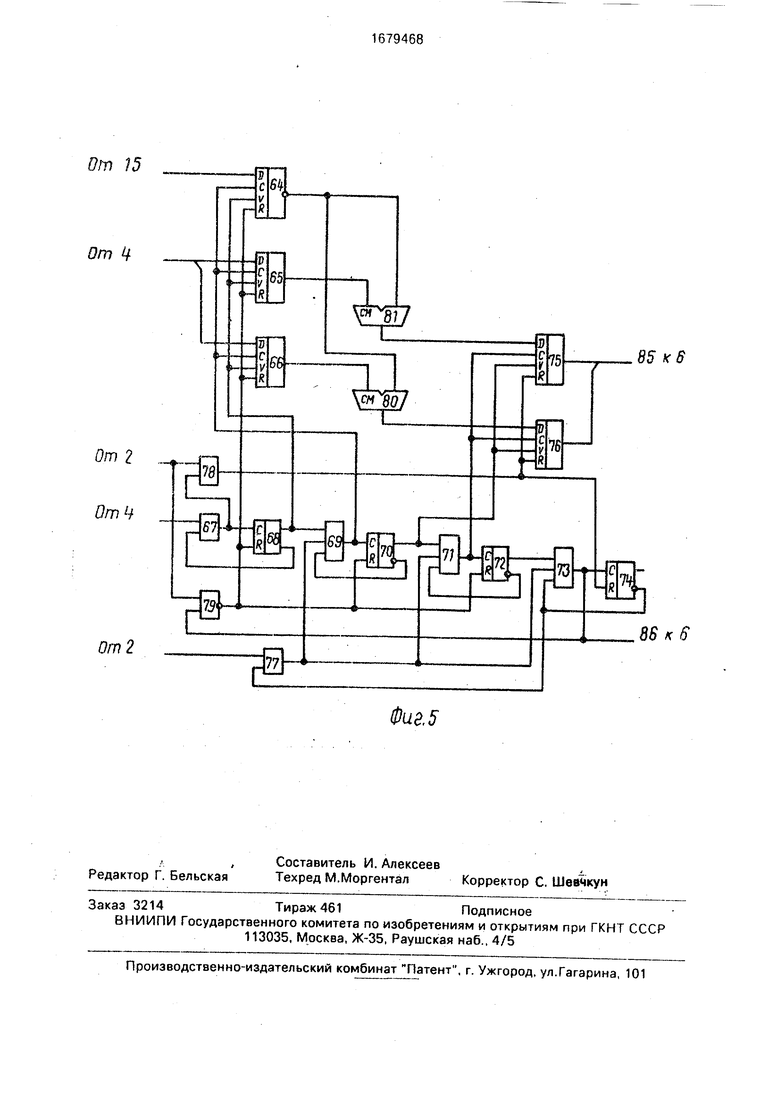

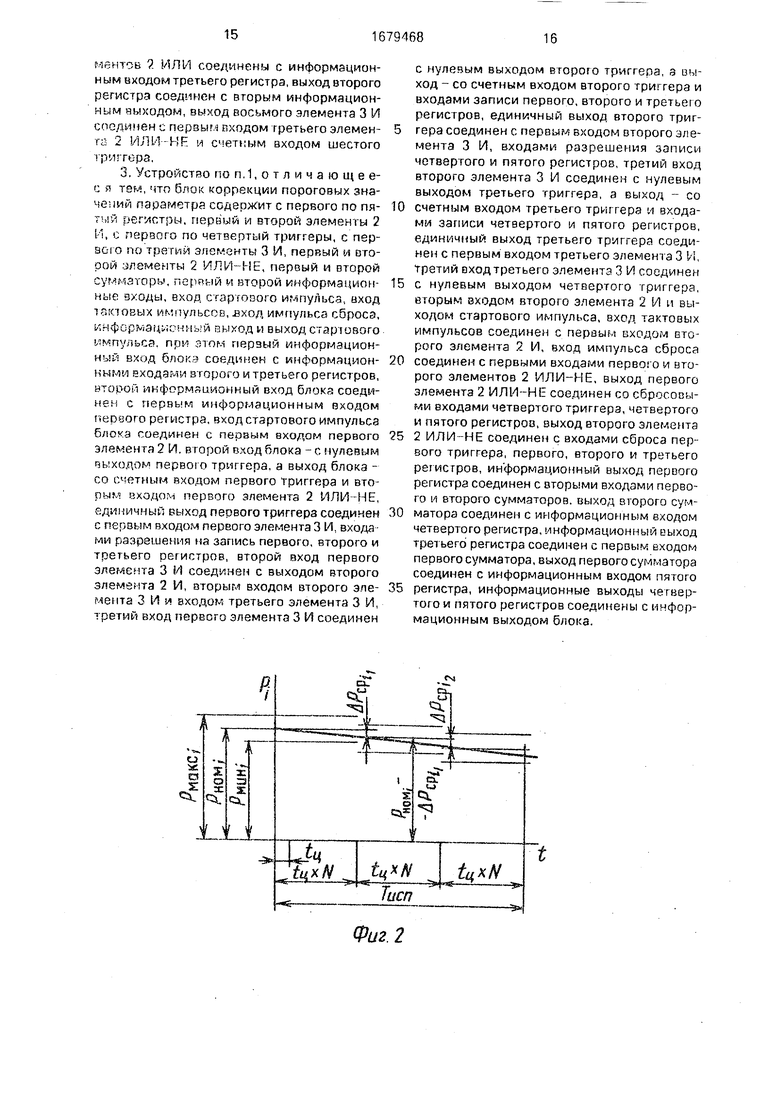

На фиг.1 показана структурная схема предлагаемого устройства; на фиг.2 - диаграмма изменения пороговых значений параметра Р) с учетом наличия естественного дрейфа за Н циклов измерения; на фиг.З - диаграмма изменения параметра счет естественного дрейфа; на фиг,4 - функциональная схема формирователя поправки на дрейф; на фиг.5 - функциональная схема блока коррекции пороговых значений параметра.

Устройство содержит датчики 1 (установленные на объекте), блок 2 управления, коммутатор 3, блок 4 хранения допусков, преобразователь 5 параметров, схему 6 сравнения параметров, формирователь 7 призиа- ка производной, блок 8 хранения эталонных

признаков производных, схему 9 сравнения признаков производных, формирователь 10 дрейфа параметра, блок 11 хранения эталонных значений дрейфа, схему 12 сравнения величин дрейфа, блок 13 хранения измерений параметров первого цикла, блок 14 индикации, формирователь 15 поправки нэ дрейф, блок 16 коррекции пороговых значений параметра.

Формирователь 15 поправки на дрейф содержит первый и второй узлы памяти (УП) 17, 18: первый элемент 2 ИЛИ-НЕ 19, пео- вый элемент 2И 20, первый триггер 21, первый регистр 22, второй элемент 2 И 23, второй триггер 24, первый элемент 3 И 25, третий триггер 26, второй элемент 3 И 27, первый счетчик 28, первый сумматор 29, элементы И-НЕ (по числу разрядов) 30, третий элемент 3 И 31, четвертый элемент 3 И 32, третий элемент 2 И 33, второй элемент 2 ИЛИ-НЕ 34, первый дешифратор 35. пятый элемент 3 И 36, шестой элемент 3 И 37, делитель 38, второй счетчик 39, второй сумматор 40, второй регистр 41, третий регистр 42, элемент 4 И 43, четвертый триггер 44, седьмой элемент 3 И 45, пятый триггер 46,

ров позволяет исключить возможность ложных заключений об аварийном состоянии нормально работающею длительное время объекта, иго существенно сокращает затраты при испытаниях дорогостоящих энергетических установок. 2 з п. ф-лы, 5 ил.

четвертый элемент 2 И 47, первый элемент 2 ИЛИ 48, пятый элемент 2 И 49, шестой элемент 2 И 50, седьмой элемент 2 И 51, восьмой элемент 2 И 52, второй элемент 2

ИЛИ 53, третий элемент 2 ИЛИ 54, шестой триггер 55, девятый элемент 2 И 56, четвертый элемент 2 ИЛИ 57, восьмой элемент 3 И 58, третий элемент 2 ИЛИ-НЕ 59, третий счетчик 60, второй дешифратор 61, десятый

элемент 2 И 62, элемент ИЛИ-НЕ 63.

Блок 16 коррекции пороговых значений параметра содержит первый регистр 64, второй регистр 65, третий регистр 66, первый элемент 2 И 67, первый триггер 68,

первый элемент 3 И 69, второй триггер 70, второй элемент 3 И 71, третий триггер 72, третий элемент 3 И 73, четвертый триггер 74, четвертый регистр 75, пятый регистр 76, второй элемент 2 И 77, первый элемент 2

ИЛИ-НЕ 78. второй элемент 2 ИЛИ-НЕ 79, первый сумматор 80, второй сумматор 81.

На фиг.4 позициями 82-84 обозначены выходы формирователя 15 поправки на дрейф, на фиг.5 позициями 85, 86 обозначены выходы блока 16 коррекции пороговых значений параметра.

Устройство работает следующим образом. По команде Пуск блок 2 управления выдает в коммутатор 3, в блок 4 хранения

допусков, в формирователь 7 признака производной, в блок 13 хранения измерений параметров первого цикла и в формирователь 15 поправки на дрейф код адреса датчика сигнала. Затем в коммутатор 3 и преобоазователь 5 параметров из блока 2 управления поступает измерительный импульс.

По этому импульсу коммутатор 3 в соответствии с кодом адреса подключает датчик 1 измеряемого сигнала к входу преобрэзователя 5 параметра. Этот же импульс разрешает преобразование измеряемого сигнала в код. Преобразовательб параметров выдает код измеренного сигнала в схему 6 сравнения параметров, в формирователь 7 признака

5 производной, в блок 13 хранения измерений параметров первого цикла, в формирователь 10 дрейфа параметра.

После выдачи кода стартовый импульс из преобразователя 5 параметров подается

0 одновременно в схему 6 сравнения параметроо, в блок 4 хранения допусков, в блок 13 хранения измерений параметров первого цикла, в формирователь 7 признака производной и в формирователь 15 поправки на дрейф. Этот импульс записывает в УП формирователя 7 признака производной и блока 13 хранения измерений параметров первого цикла по текущему адресу код измеренного сигнала, а в формирователе 15 поправки на дрейф разрешает считывание поправки, В остальных блоках ввиду отсутствия потенциала разрешения из блока 2 управления этот импульс никаких действий не производит.

Стартовый импульс с выхода формирователя 7 признака производной поступает в блок 2 управления, который вновь выдает код адреса датчика очередного измеряемого сигнала, а затем и измерительный импульс. Описанный процесс повторяется для всех измеряемых параметров. В результате в УП указанных блоков будут записаны коды всех измеренных сигналов за один цикл, а блок 13 хранения измерений параметров первого цикла перейдет в режим считывания информации из УП по текущим адресам.

Одновременно блок 2 управления выдает управляющий потенциал, который переводит формирователь 7 признака производной в режим формирования признаков производных при последующих циклах измерений параметров. Этот же потенциал разрешает прохождение стартовых импульсов в схему б сравнения параметров из блока 4 хранения допусков через блок 16 коррекции пороговых значений параметра.

В следующем цикле измерений стартовый импульс с выхода преобразователя 5 параметров поступает в блок 4 хранения допусков, который выдает в блок 16 коррекции пороговых значений параметра пороговые значения измеренного сигнала; в схему

6сравнения параметров и в формирователь

7признака производной, в которых записывает поступивший из преобразователя 5 параметров код измеренного параметра; в блок 13 хранения измерений параметров первого цикла, который выдает в формирователь 10 дрейфа параметра код измеренного в первом цикле текущего параметра; в формирователь 15 поправки на дрейф, который выдает в блок 16 коррекции пороговых значений параметра поправку на дрейф параметра (в первом цикле измерения она нулевая).

Стартовый импульс из блока 4 хранения допусков поступает в блок 16 коррекции пороговых значений параметра, который выдает в схему 6 сравнения параметров скорректированные пороговые значения

измеренного параметра, а также стартовый импульс.

Производится сравнение измеренного параметра сегоскорректированнымизначени- 55 ями, и, если измеренный параметр находится в пределах допусков, т.е. Рмакс Ризм Рмин, то схема 6 сравнения параметров выдает стартовый импульс в формирователь 7, где производится формирование признака производной (0й,+,-), и его код заносится в УП формирователя, а стартовый импульс подается в формирователь 10 дрейфа параметра.

В формирователе 10 рассчитывается 5 дрейф параметра, код которого подается в формирователь 15 поправки на дрейф и одновременно через него в схему 12 сравнения величин дрейфа, а стартовый импульс подается в блок 11 хранения эталонных зна- 10 чений дрейфа.

Код эталонного значения дрейфа и стартовый импульс подаются в схему 12 сравнения величин дрейфа, где производится сравнение текущего и эталонного значений 5 дрейфа параметра. Если величина дрейфа текущего параметра меньше или равна эталонному, то стартовый импульс поступает в блок 2 управления.

Далее описанный процесс, начиная со 0 второго цикла измерений, будет повторяться, и за Н циклов измерения в формирователе 15 поправки на дрейф сформируется среднее значение дрейфа параметра flPcpi (см. фиг.2). Это среднее значение будет ис- 5 пользовано в следующих Н циклах до конца работы объекта.

Но если в одном из циклов измерения в схеме 6 сравнения параметров окажется, что указанное условие не выполняется или 0 в схеме 12 значение дрейфа текущего параметра больше эталонного, то происходит следующее,

В первом случае а схеме 6 сравнения параметров вырабатывается команда нали- 5 чия неисправности в ииде потенциала, который подается в формирователь 10 дрейфа параметра и запрещает прохождение в нем стартовых импульсов; прекращает дальнейшую работу схемы 6 сравнения параметров; 0 разрешает проход стартовых импульсов с выхода преобразователя 5 параметров через схему 6 сравнения параметров на вход формирователя 7 признака производной. Когда признаки производных всех измеряе- 5 мых параметров будут сформированы, как описано выше, признаки всех измеренных параметров с выхода формирователя 7 признака производной поступят в схему 9 сравнения признаков производных, а стартовый 0

импульс поступит в блок 8 хранения эталонных признаков производных. Последний выдает в схему 9 сравнения признаков при изводных коды эталонных значений признаков производных, соответствующих одному из возможных состояний объекта контроля (классу неисправности). В схеме 9 производится сравнение текущих кодов с эталонными. Если совпадение произошло, то разрешающий потенциал поступает в блок 14 индикации, который выдает команду Стоп (в виде потенциала) в блок 2 управления. Процесс измерения параметров прекращается, s блок 14 индицирует название неисправности. Если же совпадения не было, то стартовый импульс поступает в блок 8 хранения эталонных признаков производных, который выдает в схему 9 сравнения следующий набор значений эталонных признаков производных (следующий класс неисправностей), и так далее, до совпадения.

Во втором случае из схемы 12 сравнения величин дрейфа в блок 14 индикации поступает разрешающий потенциал. Блок 14 индикации выдает команду Стоп (в виде потенциала) в блок 2 управления. Процесс измерения параметров прекращается, а блок 14 индицирует название неисправности.

Формирователь 15 поправки на дрейф (фиг,4) работает следующим образом. Из преобразователя 5 параметров стартовый импульс поступает на первый вход элемента 2 И 20. С его выхода этот импульс поступает на счетный вход триггера 21 и переводит его в единичное состояние. Триггер 21 выдает разрешение на второй вход элемента 2 И 47, на первый вход логического элемента 2 И 56. Выходной потенциал элемента 2 И 56 через элемент 2 ИЛИ 57 по входу W переводит УП в режим считывания, тем самым подготовив блок к работе.

На адресные входы УП 17 и 18, на дешифратор 35 из блока 2 управления поступает код адреса датчика измеряемого параметра. Адрес одновременно является номером ячейки хранения суммы Ј дР| в УП 17 и 18. Когда в формирователе 10 будет сформирован дрейф текущего параметра, его код поступает на информационный вход регистров 22 и 41, а стартовый импульс - на первый вход логического элемента 2 И 23. Этот импульс через элемент 2 ИЛИ-НЕ 34 сбрасываете нуль регистры41,42, триггеры 44, 46; через элемент 2 И 33, если на входе дешифратора 35 будет код адреса датчика, измеряющего первый параметр, поступает на счетный вход счетчика числа циклов (число циклов Н); на счетный вход триггера 24.

Триггер 24 переходит в единичное состояние, запрещает дальнейшее прохождение импульсов через элемент 2 И 23 и разрешает - через элемент 3 И 25. Импульс

тактовой частоты через элемент 3 И 25 поступает на С-вход регистра 22 и записывает в него код дрейфа текущего параметра; на С-вход регистра 41 и записывает в него код дрейфа текущего параметра (с выхода этого

0 регистра код подается в схему 12 сравнения величин дрейфа); на С-вход регистра 42 и записывает в него код формируемой поправки по текущему параметру; на счетный вход триггера 26 и переводит его в единич5 ное состояние.

Триггер 26 запрещает прохождение тактовых импульсов через элементы 3 И 37 и 36; разрешает прохождение тактовых импульсов через элементы 3 И 27 и 4 I/I 43. Импуль0 сы тактовой частоты с выхода элемента 3 И 27 начнут поступать на счетные входы счетчика 28 и делителя 38. С инверсного выхода счетчика 28 код поступает на вторые входы сумматора 29 до тех пор, пока на выходе

5 сумматора 29 не окажутся во всех разрядах единицы, т.е. когда код значения дрейфа не станет равным коду (прямому) счетчика 28 и элемент И-НЕ 30-не запретит прохождение тактовых импульсов через элемент 3 И 27.

0 При этом на выходе делителя 38 будет код значения дрейфа, деленного на число циклов Н, за которое формируется среднее значение дрейфа () , Этот код подается на первый вход сумматора 40. Од5 повременно инвертируемый элементом ИЛИ-НЕ 63 потенциал с выхода элемента И-НЕ 30 подается на второй вход логических элементов 3 И 31, 32, 4 И 43 и 2 И 62. Импульс тактовой частоты через зле0 мент 4 И 43 поступает на вход элемента 3 И 31 и через элемент 3 И 32 на вход записи V УП 18. В УП 18 будет записана сумма предыдущего значения дРы/Н и текущего дР|/Н. Этот же импульс поступает нз счет5 ный вход триггера 44, который переходит в единичное состояние, запрещает дальнейшее прохождение импульсов через элемент 3 И 45. Тактовый импульс через элемент 3 И 45 поступает на вход логического элемента

0 3 И 58; на вход элемент 2 ИЛИ-НЕ 19 и сбрасывает триггер 21, регистр 22, триггеры 24, 26, счетчик 28, делитель 38 и счетчик 39; поступает на счетный вход триггера 46 и переводит его в единичное состояние; про5 ходит на выход 84.

С приходом следующих стартовых импульсов на входы элементов 2 И 20 и 23 описанный процесс повторяется до тех пор. пока код счетчика 60 не станет равным Н.

Тогда дешифратор 61 выдает разрешение на первый вход логического элемента 2 И 62, который в свою очередь разрешает прохождение импульса с выхода элемента 3 И 45 через элемент 3 И 58 на счетный вход триггера 55 и переводит его в единичное состояние; через элемент 2 ИЛИ-НЕ 59 сбрасывает счетчик 60 циклов. Теперь триггер 55 запрещает прохождение импульсов через элементы 3 И 32, 37, 2 И 56; разрешает прохождение информации через элементы 2 И 49 и 52, 50 и 51. В дальнейшем формирование за следующие Н циклов поправки на дрейф производится в УП 17, а выдается нз выход поправка, сформированная за предыдущие Н циклов, из УП 18. То же происходит до конца работы контролируемого объекта.

Блок 16 коррекции пороговых значений параметра (фиг.5) работает следующим образом. На информационный вход регистра 64 из формирователя 15 подается поправка на дрейф дР|. На информационные входы регистров 65 и 66 из блока 4 хранения допусков подается верхнее и нижнее пороговые значения измеряемого параметра соответственно. Стартовый импульс из блока 4 хранения допусков подается на первый вход элемента 2 И 67. С выхода элемента 2 И 67 этот импульс поступает на счетный вход триггера 68 и через элемент 2 ИЛИ-НЕ 78 - на входы сброса регистров 75, 76 и триггера 74. Триггер 68 переходит в единичное состояние, запрещает по второму входу прохождение стартовых импульсов через элемент 2 И 67; разрешает по V-входу запись информации в регистры 64-66; разрешает прохождение импульсов тактовой частоты через элемент 3 И 69.

Импульс тактовой частоты через элемент 2 И 77, через элемент 3 И 69 поступает на счетный вход триггера 70 и С-входы записи информации регистров 64-66. Этот импульс записывает входную информацию в регистры 64-66 и переводит триггер 70 в единичное состояние. Триггер 70 запрещает дальнейшее прохождение импульсов тактовой частоты через элемент 3 И 69, разрешает - через элемент 3 И 71 и по V-входу разрешает запись информации с выходов сумматоров 80 и 81 в выходные регистры 75 и 76.

Следующий импульс тактовой частоты проходит через элемент 3 И 71 на счетный вход триггера 72 и на С-вход записи информации в регистры 75 и 76. Информация с выходов сумматоров 80 и 81 записывается в выходные регистры 75 и 76, а триггер 72 переходит в единичное состояние. Триггер 72 запрещает дальнейшее прохождение импульсов тактовой частоты через элемент 3 И

71 и разрешает - через элемент ЗИ 73. Следующий импульс тактовой частоты проходит через элемент 3 И 73 на счетный вход триггера 74; через элемент 2 ИЛИ-НЕ 79 сбрасы- 5 вает регистры 64-66 и триггеры 68, 70 и 72; проходит на выход 86, Триггер 74 запрещает дальнейшее прохождение импульсов тактовой частоты через элементы 3 И 73 и 2 И 77. На этом работа блока заканчивается до

10 прихода следующего стартового импульса на первый вход элемента 2 И 67.

Возможность распознавания медленно развивающихся неисправностей с помощью изобретения позволяет предотвратить аварий5 ную ситуацию задолго до достижения объектом контроля необратимых изменений. Формула изобретения 1. Устройство для контроля и диагностики состояний объекта, содержащее коммутатор,

0 блок хранения допусков, преобразователь параметров, схему сравнения параметров, формирователь признака производной, блок хранения эталонных признаков производных, схему сравнения признаков произ5 водных, формирователь дрейфа параметра, блок хранения эталонных значений дрейфа, схему сравнения величин дрейфа, блок хранения измерений параметров первого цикла, блок индикации и блок управления, выход из0 мерительного импульса которого соединен с входами измерительного импульса коммутатора и преобразователя параметров, адресный выход - с адресными входами коммутатора, блока хранения допусков, формирователя

5 признака производной, блока хранения измерений параметров первого цикла, а выход разрешающего потенциала соединен с входами разрешающего потенциала блока хранения допусков, схемы сравнения параметров и

0 формирователя признака производной, причем адресный выход коммутатора соединен с адресным входом преобразователя параметров, информационный выход которого соединен с первым информационным

5 входом схемы сравнения параметров, с первым информационным входом формирователя признака производной, с первым информационным входом формирователя дрейфа параметра и с информационным вхо0 дом блока хранения измерений параметров первого цикла, а выход стартового импульса - с первым входом стартового импульса схемы сравнения параметров, входом стартового импульса блока хранения допусков,

5 первым входом стартового импульса формирователя признака производной, входом стартового импульса блока хранения измерений параметров первого цикла, выход стартового импульса схемы сравнения параметров соединен с вторым входом стартозого импульса формирователя признака производной, а выход потенциала разрешения - 6 входами потенциала разрешения Формирователя признака производной и формирователя дрейфа параметра, информационный выход формирователя признака производной соединен с первым информационным входом схемы сравнения признаков производных, первый выход стартового импульса - с первым входом стартового импульса блока управления, второй выход стартового импульса - с первым входом стартового импульса формирователя дрейфа параметра, а третий выход стартового импульса - с первым входом стартового импульса блока хранения эталонных признаков производных, информационный выход которого соединен с вторым информационным входом схемы сравнения признаков производных и пер- DWM информационным входом блоха индикации, а выход стартового импульса - с входом стартового импульса схемы сравнения признаков производных, первый выход стартового импульса схемы сравнения признаков производных соединен с вторым входом стартового импульса блока хранения эталонных признаков производных, а второй выход - с первым входом стартового импульса блока индикации, информационный выход блока хранения эталонных значений дрейфа соединен с первым информационным входом схемы сравнения величин дрейфа и вторым информационным входом блока индикации, а выход стартового импульса блока хранения эталонных значений дрейфа соединен с входом стартового импульса схемы сравнения величин дрейфа, первый выход стартового импульса схемы сравнения величин дрейфа соединен с вторым входом стартового импульса формирователя дрейфа параметра, второй выход стартового импульса - с вторым входом стартового импульса блока управления, а третий выход стартового импульса - с вторым входом стартового импульса блока индикации, информационный выход блока хранения измерений параметров первого цикла соединен с вторым информационным входом формирователя дрейфа параметра, а выход стартового импульса - с третьим входом стартового импульса формирователя дрейфа параметра, отличающееся тем, что, с целью повышения надежности и достоверности контроля и диагностики, в него введены блок коррекции пороговых значений параметра и формирователь поправки на дрейф, информационный вход которого соединен с информационным выходом форми- рователя дрейфа параметра, первый информационный выход - с вторым инфор

мационным входом схемы сравнения величин дрейфа, первый вход стартового импульса - с выходом стартового импульса формирователя дрейфа параметра, второй

вход стартового импульса - с первыми входами стартового импульса блока хранения допусков, схемы сравнения параметров, формирователя признака производной и с выходом стартового импульса преобразова0 теля параметров, адресный вход - с адрес ными входами коммутатора, блока хранения допусков, блока хранения измерений параметров первого цикла, формирователя признака производной и с адресным выхо5 дом блока управления, вход тактовых импульсов и вход импульса сброса - соответственно с выходом тактовых импульсов и выходом импульса сброса блока управления, первый информационный вход

0 блока коррекции пороговых значений параметра соединен с информационным выходом блока хранения допусков, второй информационный вход - с вторым информационным выходом формирователя поправ5 ки на дрейф, информационный выход - с вторым информационным входом схемы сравнения параметров, вход стартового импульса - с выходом стартового импульса блока хранения допусков, выход стартового

0 импульса - с вторым входом стартового импульса схемы сравнения параметров, вход тактовых импульсов и вход импульса сброса - соответственно с выходом тактовых им- пульсоа и выходом импульса сброса блока

5 управления.

0 по третий регистры, с первого по восьмой элементы 3 И, с первого по третий счетчики, делитель, элемент И-НЕ, элемент 4 И, элемент ИЛИ-НЕ, три элемента 2 ИЛИ-НЕ, с первого по четвертый элементы 2 ИЛИ, пер5 вый и второй дешифраторы, первый и второй сумматоры, с первого по десятый элементы 2 И, информационный вход, первый и второй входы стартового импульса, адресный вход, вход тактовых импульсов,

0 вход импульса сброса, выход стартового импульса, первый и второй информационные выходы, при этом первый вход второго элемента 2 И соединен с первым входом стартового импульса, второй вход - с кулевым

5 выходом второго триггера, а выход - со счетным входом второго триггера, первым входом второго элемента 2 ИЛИ-НЕ, с первым входом третьего элемента 2 И, сбросовый вход второго триггера соединен со сбросовыми входами первого и третьего триггеров,

делителя, первого и второго счетчиков, первого регистра л с выходом первого элемента 2 ИЛИ-НЕ, а единичный выход - с первым входом первого элемента 3 И, с разрешающим входом на запись первого регистра, вторым входом пятого элемента 3 И, вторым входом шестого элемента 3 И, с разрешающим входом на запись второго и третьего регистров, второй вход первого элемента 3 И соединен с входом тактовых импульсов, третьим входом второго элемента 3 И, третьим входом элемента 4 И, вторым входом седьмого элемента 3 И, третий вход - с нулевым выходом третьего триггера, третьим входом пятого и шестого элементов 3 И, а выход - со счетным входом третьего триггера, входом записи первого, второго и третьего регистров, единичный выход третьего триггера соединен с первым входом второго элемента 3 И и вторым входом элемента 4 И, второй вход второго элемента 3 И соединен с входом элемента ИЛИ- НЕ и выходом элемента И-НЕ, а выход- со счетными входами первого счетчика и делителя, счетный выход первого счетчика соединен с вторым входом первого сумматора, выход делителя соединен со счетным входом второго счетчика, счетный выход второго счетчика соединен с первым входом второго сумматора, информационные входы первого и второго регистров соединены с информационным входом, первый вход первого элемента 2 И соединен с вторым входом стартового импульса, второй вход - с нулевым выходом первого триггера, а выход - с его счетным входом, единичный выход первого триггера соединен с вторым входом четвертого элемента 2 И и первым входом девятого элемента 2 И, первый вход четвертого элемента 2 И соединен с первым входом третьего и пятого элементов 3 И, единичным входом шестого триггера и вторыми входами шестых и седьмых элементов 2 И, а выход - с вторым входом первого элемента 2 ИЛИ, выход шестого элемента 3 И соединен с первым входом первого элемента 2 ИЛИ, выход которого соединен с входом чтения второго узла памяти, выход четвертого элемента 3 И соединен с входом записи второго узла памяти, выход девятого элемента 2 И соединен с вторым входом четвертого элемента 2 ИЛИ, выход пятого элемента 3 И соединен с первым входом четвертого элемента 2 ИЛИ, выход которого соединен с оходом чтения первого узла памяти, выход третьего элемента 3 И соединен с входом записи первого узла памяти, адресные входы первого и второго узлов памяти и вход первого дешифратора соединены с адресным входом, выход первого дешифратора

соединен с вторым входом третьего элемента 2 И и вторым входом восьмого элемента 3 И, выход третьего элемента 2 И соединен со счетным входом третьего счетчика, выход 5 которого соединен с входом второго дешифратора, вход импульса сброса соединен с первым входом первого элемента 2 ИЛИ- НЕ, вторыми входами второго и третьего элементов 2 ИЛИ-НЕ и входом сброса шес- 10 того триггера, выход второго элемента 2 ИЛИ-НЕ соединен со сбросовыми входами второго и третьего регистров, четвертого и пятого триггеров, выход первого сумматора соединен с входами элемента И-НЕ, нуле- 5 вой выход шестого триггера соединен с вторым входом девятого элемента 2 И, с первыми входами четвертого и шестого элементов 3 И, вторыми входами пятых и восьмых элементов 2 И, выход элемента

0 ИЛИ-НЕ соединен с первым входом элемента 4 И, вторым входом десятого элемента 2 И, вторыми входами третьего и четвертого элементов 3 И, четвертый вход элемента 4 И соединен с нулевым входом

5 четвертого триггера, выход элемента 4 И соединен со счетным входом четвертого триггера, третьими входами третьего и четвертого элементов 3 И, единичный выход четвертого триггера соединен с первым вхо0 дом седьмого элемента 3 И, третий вход которого соединен с нулевым выходом пятого триггера, выход седьмого элемента 3 И соединен со счетным входом пятого триггера, третьим входом восьмого элемента 3 И,

5 вторым входом первого элемента 2 ИЛИ- НЕ и выходом стартового импульса, выход второго дешифратора соединен с первым входом десятого элемента 2 И, выход которого соединен с первым входом восьмого

0 элемента 3 И, выход второго сумматора соединен с информационными входами первого и второго узлов памя t и, выход третьего регистра соединен с вторым входом второго сумматора, выход первого узла памяти сое5 динен с первыми входами пятых и шестых элементов 2 И, выход второго узла памяти соединен с первыми входами седьмых и восьмых элементов 2 И, выходы пятых элементов 2 И соединены с первыми входами

0 вторых элементов 2 ИЛИ, выходы шестых элементов 2 И соединены с первыми входами третьих элементов 2 ИЛИ, выходы седьмых элементов 2 И соединены с вторыми входами вторых элементов 2 ИЛИ, выходы

5 восьмых элементов 2 И соединены с вторыми входами третьих элементов 2 ИЛИ, выходы вторых элементов 2 ИЛИ соединены с первым информационным выходом, выход третьего регистра соединен с вторым входом второго сумматора, выходы третьих элементов . ИЛИ соединены с информационным входом третьего регистра, выход второго регистра соединен с вторым информационным чыходом, выход восьмого элемента 3 И соединен с первым входом третьего элемен- гс. 2 ИЛИ-НЕ и счетным входом шестого ч риггора.

с нулевым выходом второго триггера, а выход - со счетным входом второго триггера и входами записи первого, второго и третьего регистров, единичный выход второго триггера соединен с первым входом второго элемента 3 И, входами разрешения записи четвертого и пятого регистров, третий вход второго элемента 3 И соединен с нулевым выходом третьего триггера, а выход - со счетным входом третьего триггера и входами записи четвертого и пятого регистров, единичный выход третьего триггера соединен с первым входом третьего элемента 3 И, Третий вход третьего элемента 3 И соединен с нулевым выходом четвертого триггера, вторым аходом второго элемента 2 И и выходом стартового импульса, вход тактовых импульсов соединен с первым входом второго элемента 2 И, вход импульса сброса соединен с первыми входами первого и второго элементов 2 ИЛИ-НЕ, выход первого элемента 2 ИЛИ-НЕ соединен со сбросовыми входами четвертого триггера, четвертого и пятого регистров, выход второго элемента 2 ИЛИ-НЕ соединен с входами сброса первого триггера, первого, второго и третьего регистров, информационный выход первого регистра соединен с вторыми входами первого и второго сумматоров, выход второго сумматора соединен с информационным входом четвертого регистра, информационный выход третьего регистра соединен с первым входом первого сумматора, выход первого сумматора соединен с информационным входом пятого регистра, информационные выходы четвертого и пятого регистров соединены с информационным выходом блока.

Фиг. 2

Фиг. 5

| Устройство для контроля параметров | 1975 |

|

SU607190A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство контроля и диагностики состояний технического объекта | 1987 |

|

SU1504653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-23—Публикация

1989-02-27—Подача