f,2

ff л

|

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Программируемый формирователь управляющих воздействий микропроцессорной системы | 1989 |

|

SU1725210A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

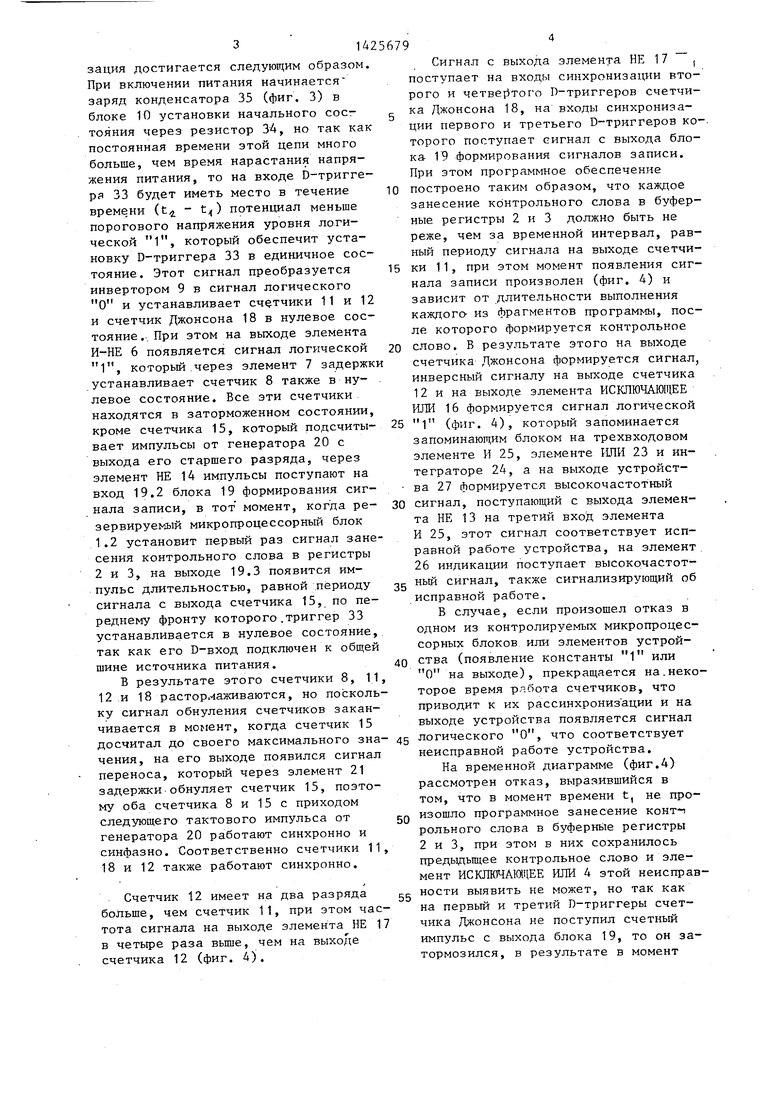

Изобретение может быть использовано для контроля правильности функционирования микропроцессорных систем. Цель изобретения состоит в расширении области применения за счет возможности контроля асинхронных сигналов. Устройство для контроля микропроцессорных систем содержит резервируемые микропроцессорные блоки 1.1 и 1.2, связанные между собой шиной обмена 1.3, а шинами данных 1.4 и 1.5 - с первым 2 и вторым 3регистрами, три элемента ИСКЛЮЧАЮ- DIEE -ИЛИ 4, 5 и 16, элемент И-НЕ 6, два элемента задержки 7 и 21, четыре счетчика 8, 11, 12 и 15, четыре элемента НЕ 9, 13, 14 и 17, счетчик Джонсона 18, построенный на четырех D-триггерах 18.1-18.4, блок 19 формирования сигналов записи, генератор 20 тактовых импульсов, элемент И 25, элемент ИЛИ 23, интегратор 24, элемент 26 индикации и блок 10 установки начального состояния. 3 з.п. ф-лы, 4ил. S (Л с

0i/. /

Изобретение относится к автоматике и вычислительной -технике и предназначено для контроля правильности функционирования микропроцессорных систем.

Цель изобретения - расширение области применения за счет возможности контроля асинхронных сигналов.

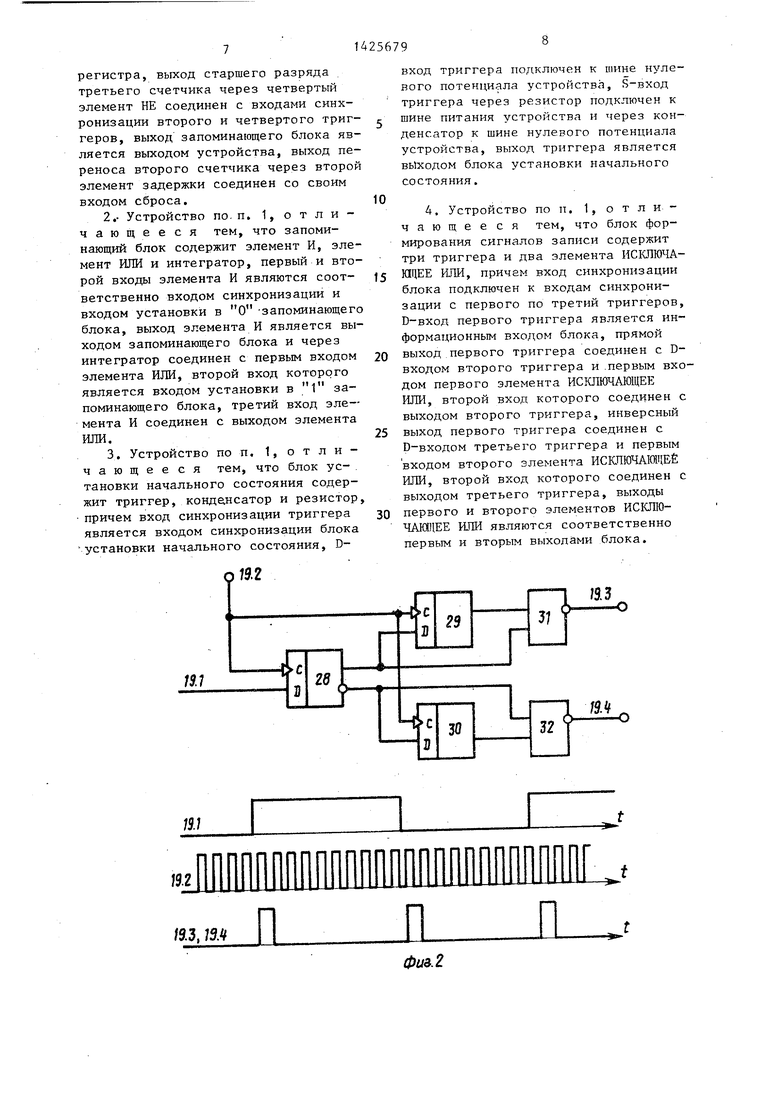

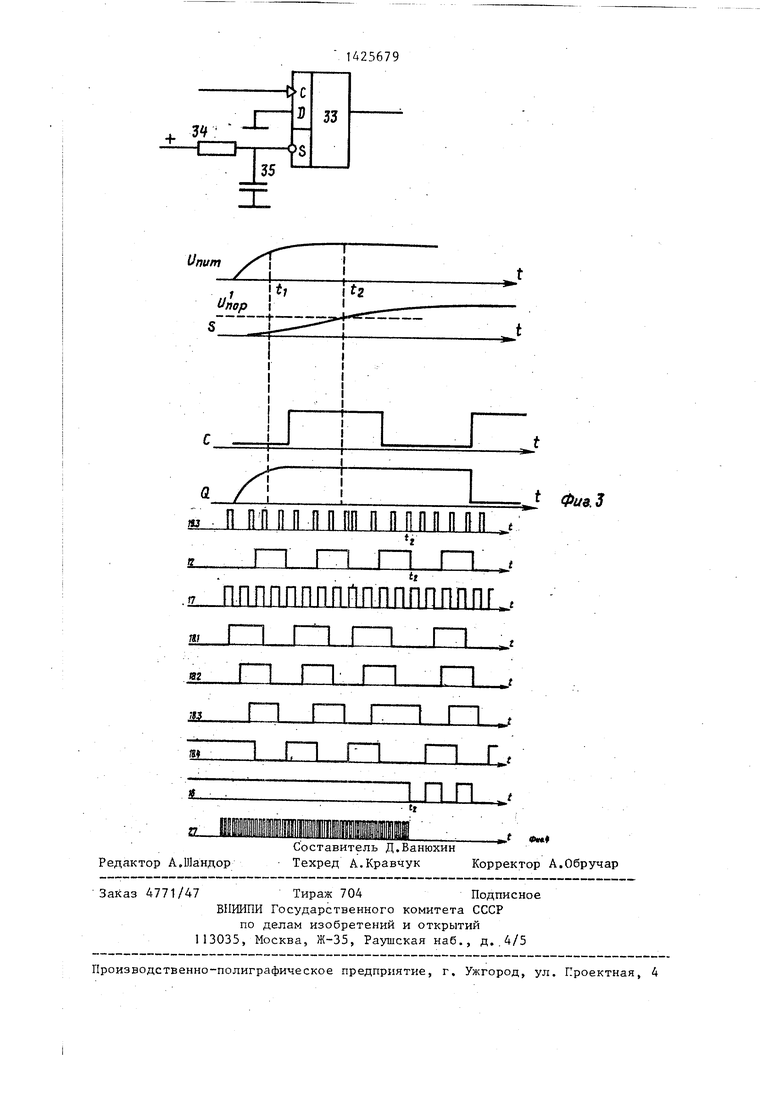

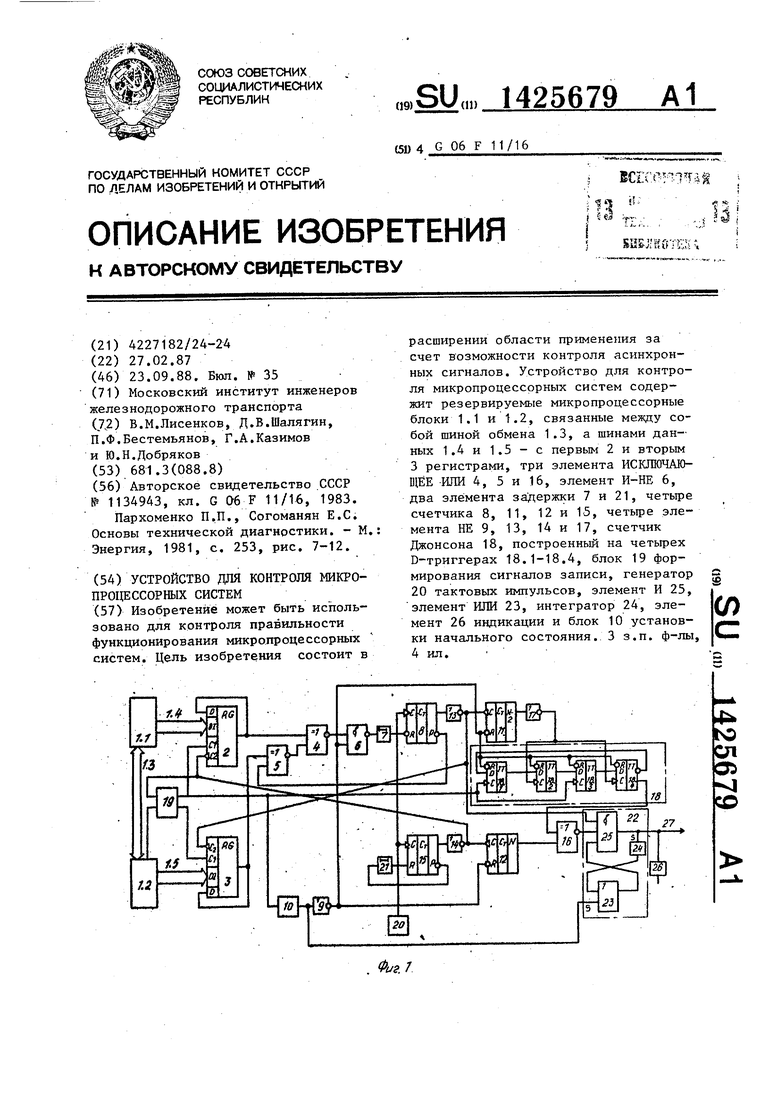

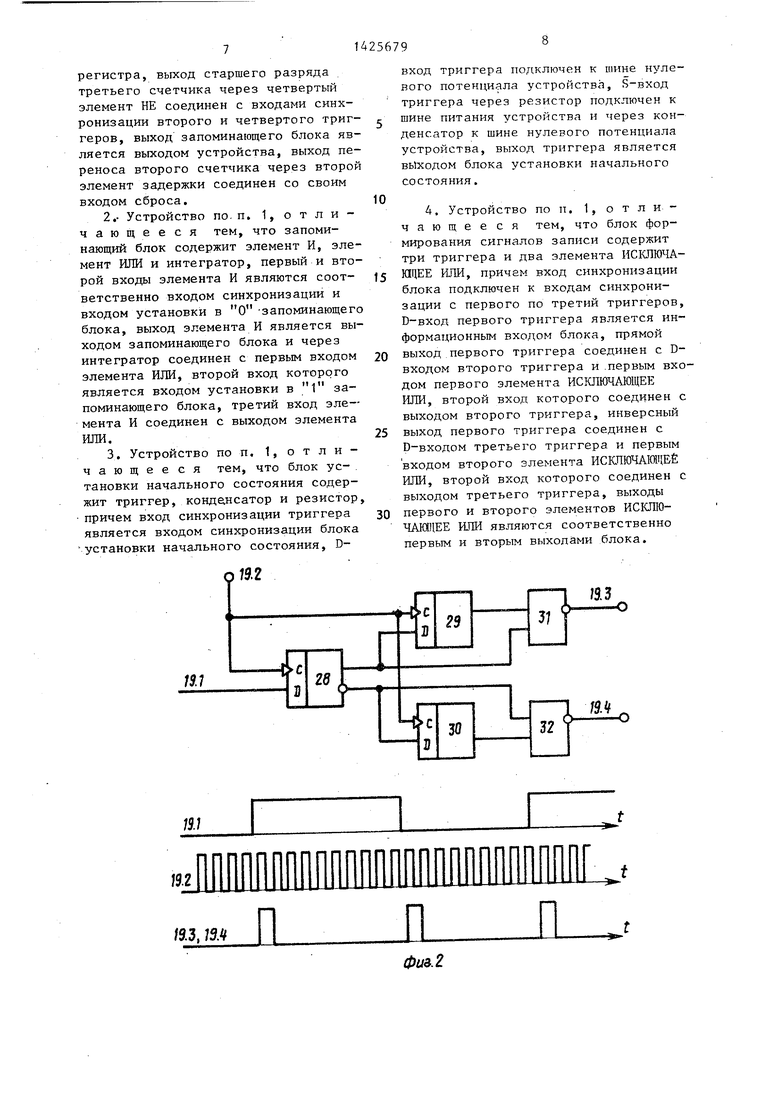

На фиг. 1 представлена структур- ная схема устройства для контроля микропроцессорных систем; на фиг, 2 структурная схема блока формирования сигналов записи и временная диаграмма его работы; на фиг, 3 - схема блока установки начального состояния и временная диаграмма его работы; на фиг, 4 - временные диаграммы работы устройства.

Устройство содержит первый 1,1 и второй 1,2 резервируемые микропроцессорные блоки, шину 1,3 обмена и шины данных: первого 1,4 и второго 1,5 резервируемых микропроцессорных блоков, первый 2 и второй 3 регистры, второй 4 и третий 5 элементы ИСКЛЮ- I ЧАЮЩЕЕ ИЛИ, элемент И-НЕ 6, первый I .элемент 7 задержки, первый счетчик 8, первый элемент НЕ 9, .блок 10 ус- тановки начального состояния, третий I 11 и четвертый 12 счетчики, второй ; 13 и третий 14 элементы НЕ, второй ; счетчик 15, первый элемент ИСКЛЮЧАЮ- I ЩЕЕ ИЛИ 16, четвертьй элемент НЕ 17, счетчик Джонсона 18, содержащий пер- I вый 18,1, второй 18,2, третий 18,3 I и четвертый 18,4 триггеры, блок 19 ; формирования сигналов записи, ин- формационный вход 19,1 и вход синхронизации 19,2 блока формирования сигналов записи, первый 19,3 и второй 19,4 выходы блока формирования сигналов записи, генератор 20 тактовых импульсов, втррой элемент 21 задержки, запоминающий , со- держащий элемент ИЛИ 23, интегратор 24 и элемент И 25, элемент индикации 26 и выход 27 устройства.

Блок 19 формирования сигналов записи (фиг, 2) содержит первый 28, второй 29 и третий 30 триггеры, первый 31 и второй 32 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ,

Блок 10 установки начального сос- тояния (фиг, 3) содержит триггер 33, резистор 34 и конденсатор 35,

Устройство работает следугоощм образом.

5

0 5 О Q с

5

Микропроцессорные резервируемые блоки работают по своей программе и От своих задающих внутренних генера- торов, после выполнения фрагмента программы микропроцессорные блоки обмениваются промежуточными результатами и после окончания процедуры обмена выставляют на шине данных контрольное слово. Микропроцессорный блок 1,2 выдает сигнал смены информации на шине данных, который поступает на вход 19,1 блока 19 формирования сигналов записи, на выходах 19,3 и 19,4 которого формируются сигналы длительностью в период тактового сигнала, который вьфаба ывает- ся на выходе счетчика 15 (временная диаграмма на фиг, 2), По сигналу записи разрешается параллельная запись в регистры 2 и 3, а информация с шин 1,4 и 1,5 данных записывается в регистры по заднему фронту тактовых сигналов, поступающих с выходов счетчиков 15 и 8 соответственно. По окончании сигнала записи регистры 2 и .3 переводятся в режим последовательного сдвига информации, при этом за счет соединения выхода регистра со своим входом последовательной записи информация о контрольном слове не теряется в течение времени, необходимого для последовательного сравнения всех разрядов контрольного слова.

Сравнение осуществляется с помощью элемента-ИСКЛЮЧАЮЩЕЕ ИЛИ 4, на один вход которого поступают сигналы с выхода регистра 2 и на второй вход с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, который инвертирует сигнал с выхода регистра 3, когда на его втором входе, соединенном с выходом перено- ta счетчика 8, присутствует сигнал 1, и повторяет сигнал с выхода регистра 3 в случае сигнала нулевого уровня, В случае, когда на входах элемента 4 сигналы имеют значения 01 или 10, на его выходе сигнал логической , который инвертируется элементом И-НЕ 6, задерживг1ется элементом 7 и подается на вход обнуления счетчика 8, который при подаче уровня логического О подсчитывает импульсы с выхода генератора 20 тактовых импульсов.

Счетчики 8 и 15 работают синхронно, так как тактируются одним генератором 20, Их начальная синхрони31425679

зация достигается следующим образом.

При включении питания начинается заряд конденсатора 35 (фиг. 3) в блоке 10 установки начального сосг тояния через резистор 34, но так как постоянная времени этой цепи много больше, чем время нарастания напряжения питания, то на входе D-тригге- ра 33 будет иметь место в течение времени (t потенциал меньше порогового напряжения уровня логической 1, который обеспечит установку D-триггера 33 в единичное состояние. Этот сигнал преобразуется инвертором 9 в сигнал логического О и устанавливает счетчики 11 и 12 и счетчик Джонсона 18 в нулевое состояние .. При этом на выходе элемента И-НЕ 6 появляется сигнал логической 1, который через элемент 7 задержк устанавливает счетчик 8 также в нулевое состояние. Все эти счетчики находятся в заторможенном состоянии, кроме счетчика 15, который подсчитывает импульсы от генератора 20 с выхода его старшего разряда, через элемент НЕ 14 импульсы поступают на вход 19.2 блока 19 формирования сигнала записи, в тот момент, когда резервируемый микропроцессорный блок 1.2 установит первый раз сигнал занесения контрольного слова в регистры 2 и 3, на выходе 19.3 появится импульс длительностью, равной периоду сигнала с выхода счетчика 15, по переднему фронту которого .триггер 33 устанавливается в нулевое состояние, так как его D-вход подключен к общей шине источника питания.

В результате этого счетчики 8, 11 12 и 18 растормаживаются, но поскольку сигнал обнуления счетчиков заканчивается в момент, когда счетчик 15

до своего максимального зна- 45 логического

О на выхо торое время приводит к выходе устр

чения, на его выходе появился сигнал переноса, который через элемент 21 задержки обнуляет счетчик 15, поэтому оба счетчика 8 и 15 с приходом следующего тактового импульса от генератора 20 работают синхронно и синфазно. Соответственно счетчики 11, 18 и 12 также работают синхронно.

. Счетчик 12 имеет на два разряда больше, чем счетчик 11, при этом частота сигнала на выходе элемента НЕ 17 в четыре раза , чем на выходе счетчика 12 (фиг. 4).

5 логического

Сигнал с выхода элемента НЕ 17 , поступает на входы синхронизации второго и четвертого D-триггеров счетчи- ка Джонсона 18, на входы синхронизации первого и третьего D-триггеров ко-, торого поступает сигнал с выхода блока 19 формирования сигналов записи. При этом программное обеспечение

0 построено таким образом, что каждое занесение контрольного слова в буферные регистры 2 и 3 должно быть не реже, чем за временной интервал, равный периоду сигнала на выходе счетчи5 ки 11, при этом момент появления сигнала записи произволен (фиг. 4) и зависит от длительности выполнения каждого- из фрагментов программы, после которого формируется контрольное

0 слово. В результате этого на выходе счетчика Джонсона формируется сигнал, инверсный сигналу на выходе счетчика 12 и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЖ 16 формируется сигнал логической

5 1 (фиг. 4), который запоминается запоминаюпщм блоком на трехвходовом элементе И 25, элементе ИЛИ 23 и интеграторе 24, а на выходе устройст- ва 27 формируется высокочастотный

0 сигнал, поступающий с выхода элемента НЕ 13 на третий вход элемента И 25, этот сигнал соответствует исправной работе устройства, на элемент 26 индикации поступает высокочастот-

g ный сигнал, также сигнализирующий об исправной работе.

В случае, если произошел отказ в одном из контролируемых микропроцессорных блоков или элементов устрой0 ства (появление константы 1 или

О на выходе), прекращается на.некоторое время работа счетчиков, что приводит к их рассинхрониз ации и на выходе устройства появляется сигнал О,

что соответствует

0

5

неисправной работе устройства.

На временной диаграмме (фиг.4) рассмотрен отказ, выразившийся в том, что в момент времени t, не произошло программное занесение KOHT-I рольного слова в буферные регистры 2 и 3, при этом в них сохранилось щ)едьщьш1ее контрольное слово и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 этой неисправности выявить не может, но так как на первый и третий D-триггеры счетчика Джонсона не поступил счетный импульс с выхода блока 19, то он затормозился, в результате в момент

времени t сигналы на входах элемента ИСКЛЮЧЛИЦЕЕ ИЛИ 16 стали одинаковыми (должны быть взаимоинверсны при исправной работе), и на его выходе

появляется сигнал логического О, которьй запирает элемент И 25, на его выходе появляется сигнал логического О, который передается на выход

элемента ШШ 23, так как на выходе ю блока 10 установки начального состояния имеет место сигнал логического О (фиг. 3), В результате этого элемент И 25 запирается и на выходе

27 устройства появляется сигнал ло- «; гического О.

Восстановление устройства может произойти только -после вмешательства обслуживающего персонала. Самопроизвольное появление сигнала на вы- 20 ходе устройства не произойдет, даже если далее микропроцессорные блоки функционируют правильно.

;Формула изобретения 25

I 1. Устройство для контроля микро- 1процессорных систем, содержащее блок |установки начального состояния, пер- вый элемент ИСКЛОЧАИЦЕЕ ИЛИ, элемент зо индикации, запоминающий блок, выход рсоторого соединен с входом элемента индикации, выход первого элемента СКПЮЧАКЩЕЕ ИШ соединен с входом . установки в О запоминающего блока, ход установки в 1 которого соединен с выходом блока установки на- чального состояния, отличающееся тем, что, с целью расширения области применения за счет ,Q возможности контроля асинхронных сигналов, оно содержит первый и второй регистры, блок формирования сигналов записи, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, пер- дд вый и второй элементы задержки, с первого по четвертый элементы НЕ, с первого по четвертый счетчики, с первого по четвертый триггеры и генератор тактовых импульсов, информационные входы параллельной записи первого и второго регистров являются информационными входами устройства для подключения к шинам данных соответственно первого и второго резерви- руемых микропроцессорных блоков, вы- Ход первого регистра соединен со сво- I1M информационным входом последовательной записи и первым входом вто50

;

о Q д

0

рого элемента ИСКЛЮЧЛЩЕЕ ИЛИ, выход которого соединен с первым входом .элемента И-НЕ, выход которого через первый элемент задержки соединен с входом сброса первого счетчика, выход переноса которого соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго регистра соединен со своим информационным входом последовательной записи и вторым входом третьего элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ, информационный вход блока формирования сигналов записи является входом устройства для подключения к выходу сигнала смены информации на шине данных второго резервируемого микропроцессорного блока, выход генератора тактовых импульсов соединен со счетными входами первого и второго счетчиков, выход блока установки начального состояния через первый элемент НЕ соединен с вторым входом элемента И-НЕ, с входами сброса третьего и четвертого счетчиков и с R-входами с первого по четвертый триггеров, выход первого триггера соединен с D-входом второго триггера, выход которого соединен с D-входом третьег.о триггера, выход которого соединен с D-входом четвертого триггера, инверсный выход которого соединен с D-входом первого триггера, прямой выход четвертого триггера соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом старшего разряда четвертого счетчика, первый выход блока формирования сигналов записи соединен с входом разрешения записи первого регистра, с входом синхронизации блока установки начального состояния и входами синхронизации первого и третьего триггеров, второй выход блока формирования сигналов записи соединен с входом разрешения записи второго регистра, выход старшего разряда первого счетчика через второй элемент НЕ соединен .со счетным входом третьего счетчика и входами синхронизации второго регистра и запоминающего блока, выход старшего разряда второго счетчика через третий элемент НЕ соединен со счетным входом четвертого счетчика и входами синхронизации блока формирования сигналов записи и первого

регистра, выход старшего разряда третьего счетчика через четвертый элемент НЕ соединен с входами синхронизации второго и четвертого триг- геров, выход запоминающего блока является выходом устройства, выход переноса второго счетчика через второй элемент задержки соединен со своим входом сброса.

2,- Устройство по. п. 1, о т л и - чающееся тем, что запоминающий блок содержит элемент И, элемент ИЛИ и интегратор, первый и второй входы элемента И являются соот- ветственно входом синхронизации и входом установки в О -запоминающего блока, выход элемента И является выходом запоминающего блока и через интегратор соединен с первым входом элемента ИЛИ, второй вход которого является входом установки в 1 запоминающего блока, третий вход элемента И соединен с выходом элемента ИЛИ,

3, Устройство по п. 1, отличающееся тем, что блок установки начального состояния содержит триггер, конденсатор и резистор, причем вход синхронизации триггера является входом синхронизации блока установки начального состояния, DО W.2

/9.3, т

вход триггера подключен к шине нулевого потенциала устройства, S-вход триггера через резистор подключен к шине питания устройства и через конденсатор к шине нулевого потенциала устройства, выход триггера является выходом блока установки начального состояния.

п

п

Фив. 2

Unum

a

«..j noon fioi П оепппу;.

i

. пппппппппппппппппг,, n m -I r-1 ,

ЯГ

02

n

т

-I f-1

JU

1 rn n rn Г,

nn .

f Фиа.З

| Устройство для функционального контроля вычислительных машин | 1983 |

|

SU1134943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пархоменко П.П., Согоманян Е.С | |||

| Основы технической диагностики | |||

| - М | |||

| Энергия, 1981, с | |||

| Прибор для измерения угла наклона | 1921 |

|

SU253A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-27—Подача