Изобретение относится к области импульсной техники и может быть использовано в преобразователях частоты для управления электродвигателями переменного тока.

Наиболее близким по технической сущности является цифровой модулятор для управления синхронным электродвигателем (см. патент РФ №2517423, опубл. 27.05.2014, бюл. №15), содержащий два генератора прямоугольных импульсов, три счетчика, три триггера, два элемента ИЛИ, инвертор, три элемента И, шесть элементов И-НЕ, три дешифратора, шесть формирователей импульсов, три сумматора, три регистра, двоично-шестеричный счетчик, схему ограничения, схему сброса, шесть выходных шин, шину входного сигнала, шину знака, шину сигнала, характеризующего конструктивное исполнение двигателя, шину сигнала датчика положения ротора.

Недостаток наиболее близкого цифрового модулятора заключается в том, что он позволяет сформировать трапецеидальное фазное напряжение на выходе преобразователя частоты, а это приводит к появлению относительно больших амплитуд высших гармоник. Кроме того, устройство, взятое за прототип, предназначено только для управления синхронным двигателем по сигналам датчика положения ротора с помощью преобразователя частоты.

Технический результат достигается тем, что в цифровой модулятор для преобразователя частоты, содержащий первый и второй генераторы прямоугольных импульсов, первый, второй третий и четвертый счетчики, первый, второй и третий триггеры, первый, второй и третий элементы И, инвертор, первый, второй, третий, четвертый, пятый и шестой элементы И-НЕ, первый, второй и третий дешифраторы, первый, второй, третий, четвертый и пятый формирователи импульсов, первый и второй сумматоры, первый, второй и третий регистры, схему сброса, причем выход первого генератора прямоугольных импульсов соединен с первыми входами первого и второго счетчиков, выход второго счетчика соединен с первым входом первого триггера, выход третьего счетчика соединен с первым входом второго триггера, выход первого счетчика соединен с первым входом первого элемента И, выход которого соединен с первым входом третьего счетчика, вторыми входами первого и второго счетчиков, первого и второго триггеров и входом инвертора, выход первого регистра соединен с третьим входом второго счетчика, выход первого сумматора соединен с первым входом второго регистра, первый выход которого соединен с первым входом первого сумматора, а второй выход - с первым входом второго сумматора, выход четвертого счетчика соединен с первым входом третьего регистра, первый второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами первого, второго и третьего дешифраторов, выход первого триггера соединен с четвертым входом первого дешифратора, выход второго триггера соединен с четвертым входом второго дешифратора, выход второго сумматора соединен с первым входом третьего триггера, выход первого формирователя импульсов соединен с входом второго формирователя импульсов и вторым входом второго регистра, выход второго формирователя импульсов соединен с вторым входом третьего триггера, выход третьего формирователя импульсов соединен с вторым входом третьего регистра, выход четвертого формирователя импульсов соединен с первым входом второго элемента И, выход схемы сброса соединен с вторыми входами первого и второго элементов И и третьим входом третьего регистра, первый и четвертый выходы первого дешифратора соединены с первыми входами соответственно первого и четвертого элементов И-НЕ, пятый выход второго дешифратора соединен с первым входом второго элемента И-НЕ, второй вход первого сумматора соединен с шиной сигнала, характеризующего конструктивное исполнение, выходы первого, второго, третьего, четвертого, пятого и шестого элементов И-НЕ являются соответственно первым, вторым, третьим, четвертым, пятым и шестым выходами цифрового модулятора, дополнительно введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертый и пятый регистры, причем выход первого генератора прямоугольных импульсов соединен с вторым входом третьего счетчика, шина сигнала задания угла соединена с первым входом четвертого регистра, выход которого соединен с вторым входом второго сумматора, шина первого сигнала задания напряжения соединена с первым входом пятого регистра, выход которого соединен с третьим входом третьего счетчика, шина второго сигнала задания напряжения соединена с первым входом первого регистра, шина сигнала синхронизации соединена с первым входом пятого формирователя импульсов, выход которого соединен с входом четвертого формирователя импульсов и вторыми входами первого, четвертого и пятого регистров, выход инвертора соединен с вторым входом пятого формирователя импульсов, выход схемы сброса соединен с третьими входами первого, четвертого и пятого регистров, выход второго генератора прямоугольных импульсов соединен с первым входом третьего элемента И, выход которого соединен с первым входом четвертого счетчика и входом первого формирователя импульсов, выход второго элемента И соединен с вторым входом четвертого счетчика и третьими входами второго регистра и третьего триггера, выход которого соединен с входом третьего формирователя импульсов и вторым входом третьего элемента И, выход первого триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с четвертым входом третьего дешифратора, выход второго триггера соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй, третий, пятый и шестой выходы первого дешифратора соединены соответственно с вторым и третьим входами первого элемента И-НЕ и вторым и третьим входами четвертого элемента И-НЕ, первый, второй, третий, четвертый и шестой выходы второго дешифратора соединены соответственно с первым и вторым входами пятого элемента И-НЕ, первым входом шестого элемента И-НЕ, вторым входом второго элемента И-НЕ и первым входом третьего элемента И-НЕ, первый, второй, третий, четвертый, пятый и шестой выходы третьего дешифратора соединены соответственно с вторыми входами третьего и шестого элементов И-НЕ и третьими входами второго, шестого, третьего и пятого элементов И-НЕ, первый, второй и третий выходы третьего регистра являются соответственно седьмым, восьмым и девятым выходами цифрового модулятора.

Существенные отличия находят свое выражение в новой совокупности связей между элементами устройства. Указанная совокупность связей позволяет с помощью предлагаемого цифрового модулятора уменьшить амплитуды высших гармоник в выходном напряжении преобразователя частоты и обеспечивает управление скоростью как асинхронного, так и синхронного двигателя.

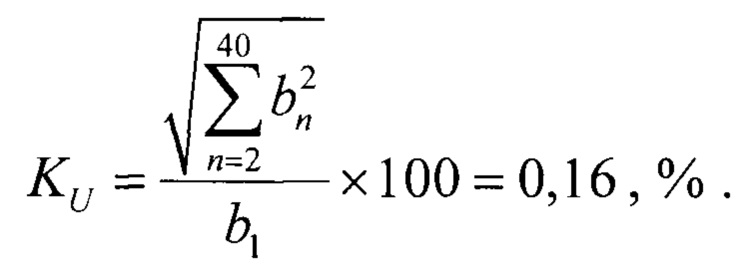

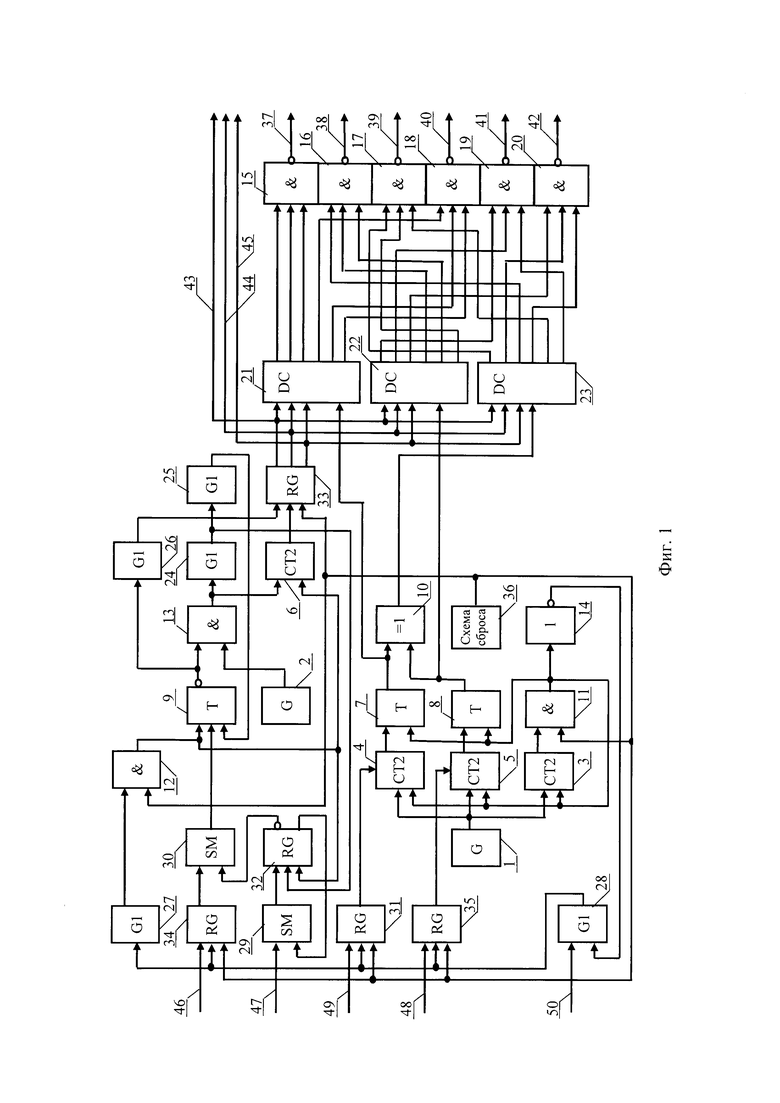

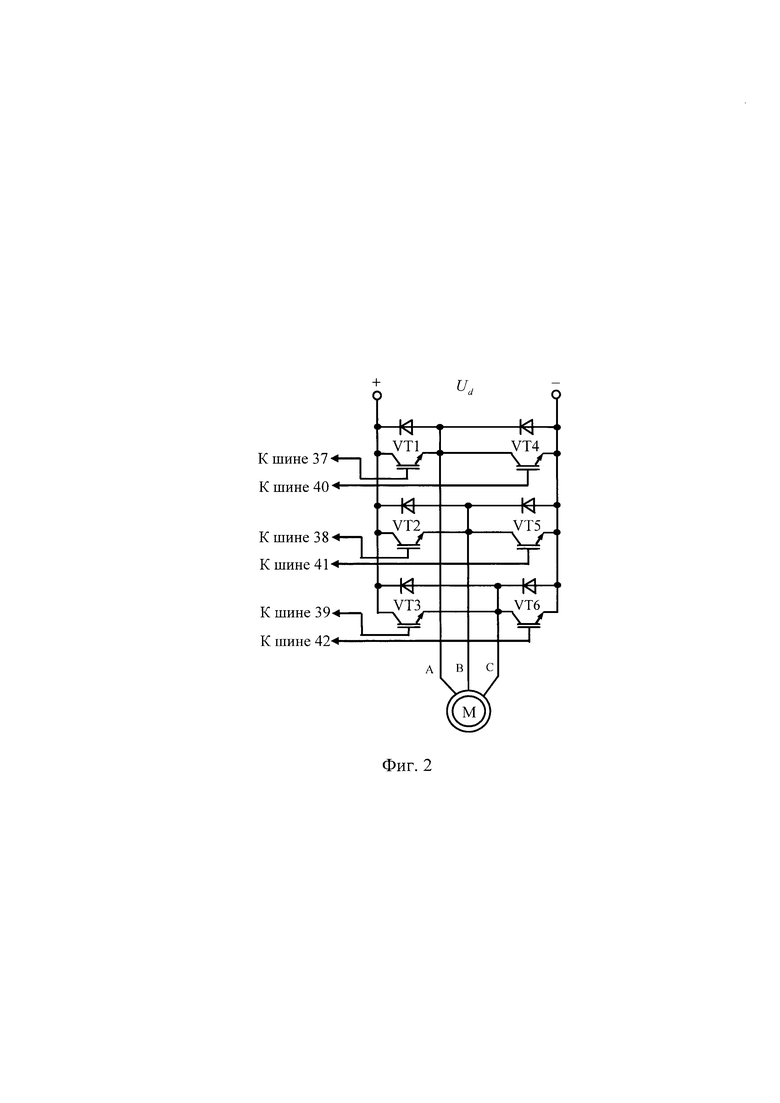

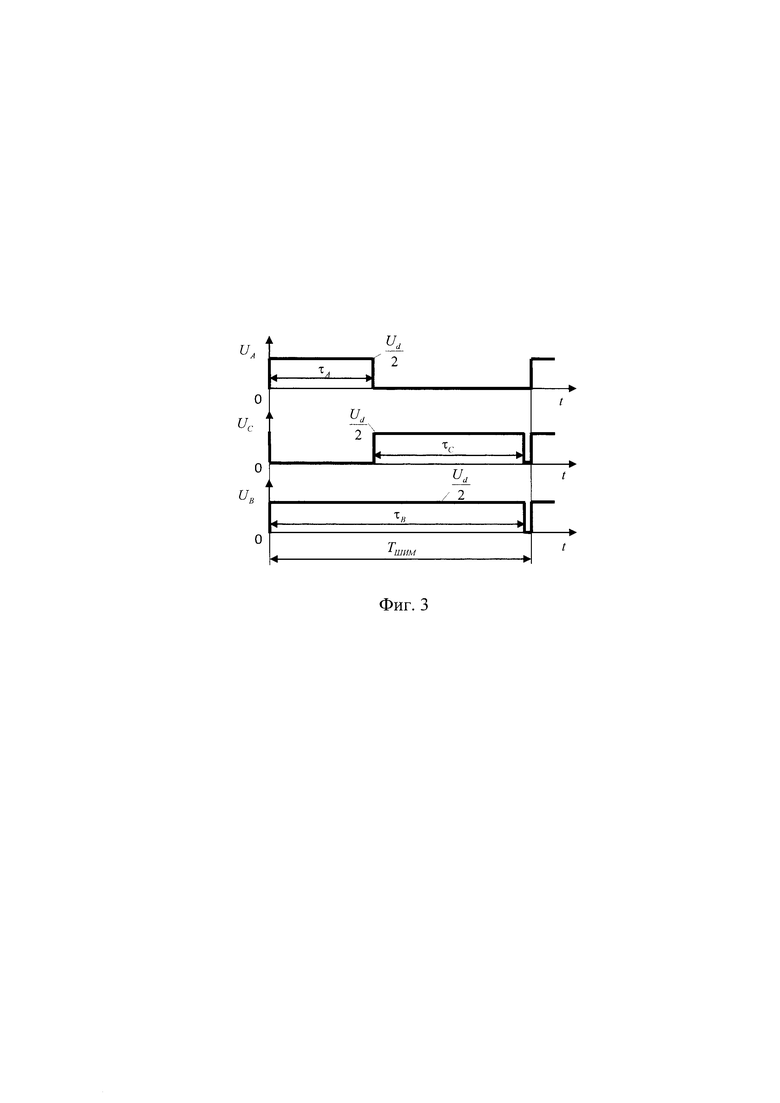

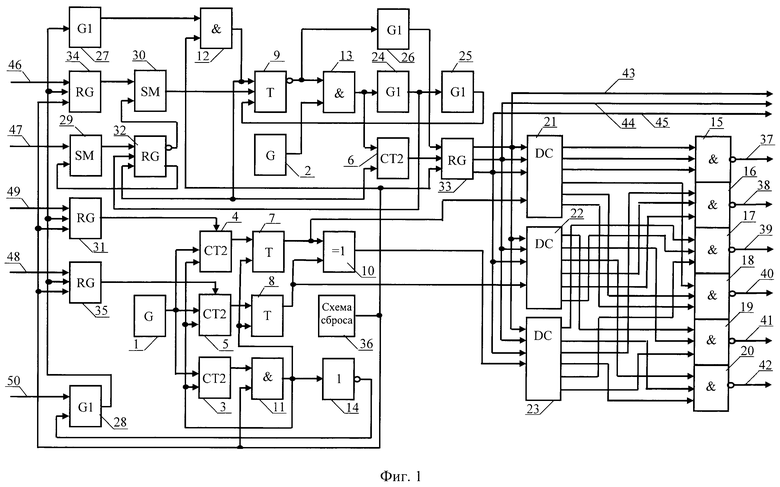

На фиг. 1 представлена функциональная схема цифрового модулятора для преобразователя частоты, на фиг. 2 - схема подключения цифрового модулятора к силовым транзисторам преобразователя частоты, на фиг. 3 - диаграммы фазных напряжений на одном периоде широтно-импульсной модуляции.

Цифровой модулятор для преобразователя частоты (фиг. 1) содержит генераторы 1 и 2 прямоугольных импульсов, счетчики 3, 4, 5 и 6, триггеры 7, 8 и 9, элемент 10 ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы 11, 12 и 13 И, инвертор 14, элементы 15, 16, 17, 18, 19 и 20 И-НЕ, дешифраторы 21, 22 и 23, формирователи 24, 25, 26, 27 и 28 импульсов, сумматоры 29 и 30, регистры 31, 32, 33, 34 и 35, схему 36 сброса, выходные шины 37, 38, 39, 40, 41, 42, 43, 44 и 45, шину 46 сигнала задания угла, шину 47 сигнала, характеризующего конструктивное исполнение, шину 48 первого сигнала задания напряжения, шину 49 второго сигнала задания напряжения и шину 50 сигнала синхронизации.

Выход генератора 1 прямоугольных импульсов соединен с первыми входами (входами обратного счета) счетчиков 3 и 4. Выход переноса счетчика 4 соединен с первым входом (входом сброса) триггера 7. Выход переноса счетчика 5 соединен с первым входом (входом сброса) триггера 8. Выход переноса счетчика 3 соединен с первым входом элемента 11 И, выход которого соединен с первым входом (входом стробирования) счетчика 5, вторыми входами (входами стробирования) счетчиков 3 и 4, вторыми входами (входами установки) триггеров 7 и 8 и входом инвертора 14. Выход регистра 31 соединен с третьим входом (информационным входом предварительной установки) счетчика 4. Выход сумматора 29 соединен с первым (информационным) входом регистра 32, первый (прямой) выход которого соединен с первым входом сумматора 29, а второй (инверсный) выход - с первым входом сумматора 30. Выход (информационный) счетчика 6 соединен с первым (информационным) входом регистра 33, первый второй и третий выходы которого соединены соответственно с первым, вторым и третьим (информационными) входами дешифраторов 21, 22 и 23. Выход триггера 7 соединен с четвертым входом (входом разрешения) дешифратора 21. Выход триггера 8 соединен с четвертым входом (входом разрешения) дешифратора 22. Старший разряд выхода сумматора 30 соединен с первым (информационным) входом триггера 9. Выход формирователя 24 импульсов соединен с входом формирователя 25 импульсов и вторым входом (входом стробирования) регистра 32. Выход формирователя 25 импульсов соединен с вторым входом (входом стробирования) триггера 9. Выход формирователя 26 импульсов соединен с вторым входом (входом стробирования) регистра 33. Выход формирователя 27 импульсов соединен с первым входом элемента 12 И. Выход схемы 36 сброса соединен с вторыми входами первого и второго элементов 11 и 12 И и третьим входом (входом сброса) регистра 33. Первый и четвертый выходы дешифратора 21 соединены с первыми входами соответственно элементов 15 и 18 И-НЕ. Пятый выход дешифратора 22 соединен с первым входом элемента 16 И-НЕ. Второй вход сумматора 29 соединен с шиной 47 сигнала, характеризующего конструктивное исполнение. Выходы первого, второго, третьего, четвертого, пятого и шестого элементов 15, 16, 17, 18, 19 и 20 И-НЕ являются соответственно выходами 37, 38, 39, 40, 41 и 42 цифрового модулятора. Выход генератора 1 прямоугольных импульсов соединен с вторым входом счетчика 5, шина 46 сигнала задания угла соединена с первым (информационным) входом регистра 34, выход которого соединен с вторым входом сумматора 30. Шина 48 первого сигнала задания напряжения соединена с первым входом регистра 35, выход которого соединен с третьим входом (информационным входом предварительной установки) счетчика 5. Шина 49 второго сигнала задания напряжения соединена с первым входом регистра 31. Шина 50 сигнала синхронизации соединена с первым входом формирователя импульсов 28, выход которого соединен с входом формирователя 27 импульсов и вторыми входами (входами стробирования) регистров 31, 34 и 35. Выход инвертора 14 соединен с вторым входом (входом блокировки) формирователя импульсов 28. Выход схемы 36 сброса соединен с третьими входами (входами сброса) регистров 31, 34 и 35. Выход генератора 2 прямоугольных импульсов соединен с первым входом элемента 13 И, выход которого соединен с первым (счетным) входом счетчика 6 и входом формирователя 24 импульсов. Выход элемента 12 И соединен с вторым входом (входом сброса) счетчика 6 и третьими входами (входами сброса) регистра 32 и триггера 9, выход которого соединен с входом формирователя 26 импульсов и вторым входом элемента 13 И. Выход триггера 7 соединен с первым входом элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с четвертым входом (входом разрешения) дешифратора 23. Выход триггера 8 соединен с вторым входом элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ. Второй, третий, пятый и шестой выходы дешифратора 21 соединены соответственно с вторым и третьим входами элемента 15 И-НЕ и вторым и третьим входами элемента 18 И-НЕ. Первый, второй, третий, четвертый и шестой выходы дешифратора 22 соединены соответственно с первым и вторым входами элемента 19 И-НЕ, первым входом элемента 20 И-НЕ, вторым входом элемента 16 И-НЕ и первым входом элемента 17 И-НЕ. Первый, второй, третий, четвертый, пятый и шестой выходы дешифратора 23 соединены соответственно с вторыми входами элементов 17 и 20 И-НЕ и третьими входами второго, шестого, третьего и пятого элементов 16, 20, 17 и 19 И-НЕ. Первый, второй и третий выходы регистра 33 являются соответственно выходами 43, 44 и 45 цифрового модулятора.

Генераторы 1 и 2 прямоугольных импульсов могут быть выполнены, например, на микросхемах КР1533ЛА3 с кварцевой стабилизацией или с времязадающими конденсаторами. Счетчики 3, 4, 5 и 6, например, выполнены на микросхемах КР1533ИЕ7, триггеры 7, 8 и 9 могут быть выполнены, например, на микросхемах КР1533ТМ2. Элемент 10 ИСКЛЮЧАЮЩЕЕ ИЛИ, например, выполнен на микросхеме КР1533ЛП5, элемент 11, 12 и 13 И - на микросхеме КР1533ЛИ1, инвертор 14 - на микросхеме К555ЛН1, элементы 15, 16, 17, 18, 19 и 20 И-НЕ - на микросхемах К555ЛА4. Дешифраторы 21, 22 и 23, могут быть выполнены, например, на микросхемах КР1533ИД7, формирователи 24, 25, 26, 27 и 28 импульсов - на микросхемах К555АГ3, сумматоры 29 и 30 - на микросхемах К555ИМ6, регистры 31, 32, 33, 34 и 35 - на микросхемах КР1533ТМ8. Схема 36 сброса, например, может быть выполнена в виде последовательно соединенных резистора и конденсатора, причем второй вывод резистора присоединяется к шине питания, а второй вывод конденсатора - к общей шине. Вывод резистора, соединенный с конденсатором, является выходом схемы 36 сброса.

Цифровой модулятор для преобразователя частоты работает следующим образом.

После включения напряжения питания схема 36 сброса формирует сигнал, который устанавливает в исходное состояние регистры 31, 33, 34 и 35. Этот же сигнал через элемент 11 И устанавливает в исходное (высокое) состояние выходы триггеров 7 и 8 и стробирует счетчики 3, 4 и 5, а также через элемент 12 И стробирует счетчик 6, сбрасывает триггер 9 и регистр 32. С задержкой времени, определяемой срабатыванием инвертора 14 и длиной импульса формирователя 28 в регистр 34 с шины 46 записывается цифровой код Nθ, определяющий заданный угол поворота вектора напряжения (угол поворота ротора синхронного двигателя), в регистр 35 с шины 48 записывается цифровой код NU1 первого сигнала задания напряжения, в регистр 31 с шины 49 записывается цифровой код NU2 второго сигнала задания напряжения. Через период времени, определяемый частотой генератора 1 прямоугольных импульсов и разрядностью счетчика 3, произойдет очередное стробирование счетчиков 3, 4 и 5 и установка триггеров 7 и 8. При этом сигнал NU1, с выхода регистра 35 записывается в счетчик 5, а сигнал NU2 - в счетчик 4. Импульсы генератора 1 с частотой ƒ0 поступают на входы обратного счета счетчиков 4 и 5. В результате на выходе переноса счетчика 5 через интервал времени

после стробирования появится отрицательный импульс, который поступает на вход сброса триггера 8. При этом на выходе триггера 8 появляется сигнал низкого уровня. На выходе переноса счетчика 4 появляется отрицательный импульс через интервал времени

после стробирования. Этот импульс поступает на вход установки триггера 7. При этом на выходе триггера 7 появляется сигнал низкого уровня. Прямоугольные импульсы с генератора 1 поступают также на счетный вход счетчика 3. Поэтому на выходе переноса счетчика 3 через промежуток времени

где n - количество разрядов двоичного счетчика 3,

после начальной установки появляется отрицательный импульс. Этот импульс, пройдя через элемент 11 И, поступает на вход установки триггеров 7 и 8 и возвращает их в исходное состояние. Отрицательный импульс с выхода счетчика 3 через элемент 11 И также стробирует счетчики 3, 4 и 5, после чего процесс формирования выходных сигналов счетчиков 4 и 5 и триггеров 7 и 8 повторяется. В результате на выходе триггера 8 формируется сигнал со скважностью

а на выходе триггера 7 - со скважностью

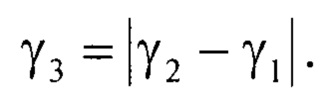

При этом на выходе элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется сигнал высокого уровня со скважностью

Одновременно с работой названных выше элементов сигнал Nθ с выхода регистра 34 поступает на вход сумматора 30, в котором производится вычитание из величины Nθ сигнала на выходе регистра 32. В первоначальный момент времени на инверсном выходе регистра 32 находятся все единицы и с учетом единицы на входе переноса сумматора 30, что обеспечивает выполнение операции вычитания, на старшем разряде выхода сумматора 30 будет находится уровень логического нуля. Поскольку после сброса триггера 9 на его инверсном выходе находится уровень логической единицы импульсы с генератора 2 через элемент 13 И будут поступать на счетный вход счетчика 6 и вход формирователя 24 импульсов. По приходу каждого импульса с формирователя 24 в регистр 32 происходит запись информации с выхода сумматора 29. В начальный момент времени на выходе сумматора 29 присутствует сигнал, характеризующий конструктивное исполнение, поэтому на инверсном выходе регистра появится соответствующий двоичный код. В результате на прямом выходе сумматора 32 формируется линейно нарастающий сигнал. Импульс с выхода формирователя 24 запускает формирователь 25 импульсов. Если к приходу импульса с формирователя 25 на вход стробирования триггера 9 на старшем разряде выхода сумматора 30 появится уровень логической единицы, то она запишется в триггер 9. При этом на его инверсном выходе появится уровень логического нуля, который заблокирует прохождение через элемент 13 И импульсов с генератора 2 и запустит формирователь 24. Импульс с формирователя 26 стробирует регистр 33, в который записывается цифровой код, который сформировался к этому времени на выходе счетчика 6. В результате, в зависимости от величины сигнала Nθ на выходе регистра 33 может появится цифровой код 0, 1, 2, 3, 4 или 5, что обеспечивается соответствующим выбором величины сигнала, характеризующего конструктивное исполнение. Этот код поступает на информационные входы дешифраторов 21, 22 и 23 и выходные шины 43, 44 и 45. В зависимости от цифрового кода на выходе регистра 33 и сигналов с триггеров 7 и 8 и элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ дешифраторы 21, 22 и 23 через элементы 15, 16, 17, 18, 19 и 20 И-НЕ подают сигналы на выходные шины 37, 38, 39, 40, 41 и 42 цифрового модулятора.

Смена информации в регистрах 31, 34 и 35 происходит по приходу импульса с формирователя 28, который запускается при появлении соответствующего сигнала синхронизации на шине 50. Для исключения ложных срабатываний и вычислений импульсы с элемента 11 И блокируют формирователь 28 импульсов.

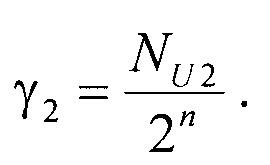

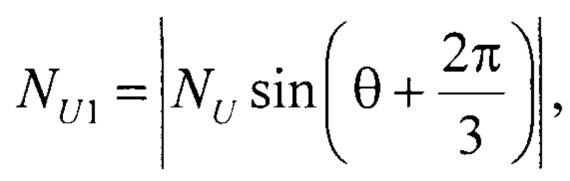

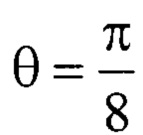

Для того, чтобы предлагаемый цифровой модулятор осуществлял синусоидальную модуляцию в функции заданного угла 9 поворота вектора напряжения, необходимо на шину 49 подавать цифровой код

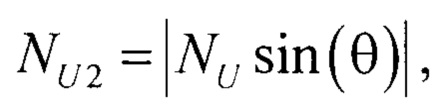

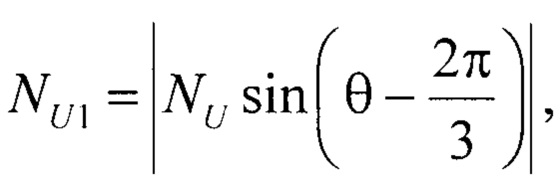

где NU - цифровой код, задающий амплитуду напряжения. На шину 48 необходимо подавать цифровой код

если на шинах 43, 44 и 45 сформирован цифровой код, соответствующий 0, 1, 3 или 4, или

если на шинах 43, 44 и 45 присутствует код, соответствующий 2 или 5.

Если выходные шины 37, 38, 39, 40, 41 и 42 цифрового модулятора подключить к силовым транзисторам частотного преобразователя как показано на фиг. 2, то на статорных обмотках асинхронного двигателя, включенных в звезду, каждый период широтно-импульсной модуляции будет формироваться система фазных напряжений, аналогичная приведенной на фиг. 3. Следует отметить, что на фиг. 3 изображен случай, когда  .

.

Амплитуда импульсов напряжения будет составлять  , а ширина импульсов для фазы А будет составлять, например, для цифровых кодов 0, 1, 3 и 4 на шинах 43, 44 и 45,

, а ширина импульсов для фазы А будет составлять, например, для цифровых кодов 0, 1, 3 и 4 на шинах 43, 44 и 45,

τA=γ2Tшим,

для фазы В - τB=γ1Tшим,

для фазы С - τC=γ3Tшим,

где Tшим - период широтно-импульсной модуляции.

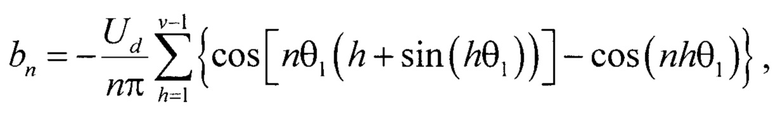

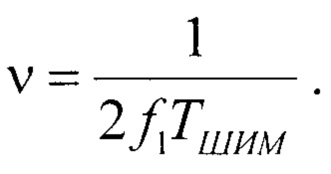

В результате фазное напряжение будет представлять собой кусочно-постоянную функцию, принимающую значения  и 0, причем ширина импульсов будет меняться по синусоидальному закону, если поддерживать постоянной скорость изменения угла θ и соответственно цифрового кода Nθ. Амплитуды высших гармоник в выходном напряжении частотного преобразователя при этом, например, для фазы А будут определяться формулой (для максимального значения фазного напряжения)

и 0, причем ширина импульсов будет меняться по синусоидальному закону, если поддерживать постоянной скорость изменения угла θ и соответственно цифрового кода Nθ. Амплитуды высших гармоник в выходном напряжении частотного преобразователя при этом, например, для фазы А будут определяться формулой (для максимального значения фазного напряжения)

где n - номер гармоники; θ1=2πƒ1Тшим;

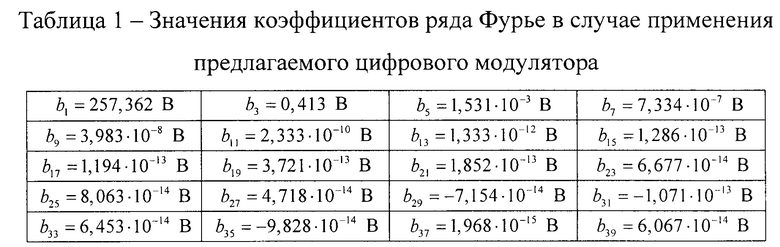

Подсчет по приведенной формуле показывает, что при Ud=515 В, ƒ1=50 Гц, Тшим=2,08333⋅10-4 амплитуды первой и высших гармоник будут принимать следующие значения (таблица 1).

Следовательно, суммарный коэффициент гармонических составляющих (в соответствии с ГОСТ 32144-2013) в выходном напряжении частотного преобразователя будет равен

Это в 24 раза меньше, чем достижимый суммарный коэффициент гармонических составляющих в устройстве, взятом за прототип.

Следует также отметить, что предлагаемый цифровой модулятор с помощью силового преобразователя может обеспечить регулирование скорости не только асинхронного, но и синхронного двигателя, например, в системе векторного управления. Кроме того, цифровой модулятор с помощью силового преобразователя может непосредственно управлять скоростью синхронного двигателя по сигналам датчика положения ротора. В этом случае на шину 46 задания угла должен подаваться цифровой код датчика угла поворота ротора, привязанного к магнитной системе, а на шину 47 конструктивного исполнения - сигнал, учитывающий количество дискрет датчика угла поворота на оборот и число пар полюсов синхронного двигателя.

Таким образом, предлагаемый цифровой модулятор позволяет уменьшить амплитуды высших гармоник в выходном напряжении преобразователя частоты и обеспечивает управление скоростью как асинхронного, так и синхронного двигателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой модулятор для преобразователя частоты | 2021 |

|

RU2762287C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2012 |

|

RU2517423C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| Цифровой модулятор | 1991 |

|

SU1800604A1 |

| Цифровой модулятор для управления синхронным двигателем | 2019 |

|

RU2711049C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ ДВУХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1997 |

|

RU2126198C1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

Изобретение относится к области импульсной техники и может быть использовано в преобразователях частоты для управления электродвигателями переменного тока. Техническим результатом является уменьшение амплитуды высших гармоник в выходном напряжении преобразователя частоты и обеспечение управления скоростью как асинхронного, так и синхронного двигателя. Цифровой модулятор для преобразователя частоты содержит генераторы 1 и 2 прямоугольных импульсов, счетчики 3, 4, 5 и 6, триггеры 7, 8 и 9, элемент 10 ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы 11, 12 и 13 И, инвертор 14, элементы 15, 16, 17, 18, 19 и 20 И-НЕ, дешифраторы 21, 22 и 23, формирователи 24, 25, 26, 27 и 28 импульсов, сумматоры 29 и 30, регистры 31, 32, 33, 34 и 35, схему 36 сброса, выходные шины 37, 38, 39, 40, 41, 42, 43, 44 и 45, шину 46 сигнала задания угла, шину 47 сигнала, характеризующего конструктивное исполнение, шину 48 первого сигнала задания напряжения, шину 49 второго сигнала задания напряжения и шину 50 сигнала синхронизации. 3 ил., 1 табл.

Цифровой модулятор для преобразователя частоты, содержащий первый и второй генераторы прямоугольных импульсов, первый, второй третий и четвертый счетчики, первый, второй и третий триггеры, первый, второй и третий элементы И, инвертор, первый, второй, третий, четвертый, пятый и шестой элементы И-НЕ, первый, второй и третий дешифраторы, первый, второй, третий, четвертый и пятый формирователи импульсов, первый и второй сумматоры, первый, второй и третий регистры, схему сброса, причем выход первого генератора прямоугольных импульсов соединен с первыми входами первого и второго счетчиков, выход второго счетчика соединен с первым входом первого триггера, выход третьего счетчика соединен с первым входом второго триггера, выход первого счетчика соединен с первым входом первого элемента И, выход которого соединен с первым входом третьего счетчика, вторыми входами первого и второго счетчиков, первого и второго триггеров и входом инвертора, выход первого регистра соединен с третьим входом второго счетчика, выход первого сумматора соединен с первым входом второго регистра, первый выход которого соединен с первым входом первого сумматора, а второй выход - с первым входом второго сумматора, выход четвертого счетчика соединен с первым входом третьего регистра, первый второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами первого, второго и третьего дешифраторов, выход первого триггера соединен с четвертым входом первого дешифратора, выход второго триггера соединен с четвертым входом второго дешифратора, выход второго сумматора соединен с первым входом третьего триггера, выход первого формирователя импульсов соединен с входом второго формирователя импульсов и вторым входом второго регистра, выход второго формирователя импульсов соединен со вторым входом третьего триггера, выход третьего формирователя импульсов соединен со вторым входом третьего регистра, выход четвертого формирователя импульсов соединен с первым входом второго элемента И, выход схемы сброса соединен со вторыми входами первого и второго элементов И и третьим входом третьего регистра, первый и четвертый выходы первого дешифратора соединены с первыми входами соответственно первого и четвертого элементов И-НЕ, пятый выход второго дешифратора соединен с первым входом второго элемента И-НЕ, второй вход первого сумматора соединен с шиной сигнала, характеризующего конструктивное исполнение, выходы первого, второго, третьего, четвертого, пятого и шестого элементов И-НЕ являются соответственно первым, вторым, третьим, четвертым, пятым и шестым выходами цифрового модулятора, отличающийся тем, что в него дополнительно введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертый и пятый регистры, причем выход первого генератора прямоугольных импульсов соединен со вторым входом третьего счетчика, шина сигнала задания угла соединена с первым входом четвертого регистра, выход которого соединен со вторым входом второго сумматора, шина первого сигнала задания напряжения соединена с первым входом пятого регистра, выход которого соединен с третьим входом третьего счетчика, шина второго сигнала задания напряжения соединена с первым входом первого регистра, шина сигнала синхронизации соединена с первым входом пятого формирователя импульсов, выход которого соединен с входом четвертого формирователя импульсов и вторыми входами первого, четвертого и пятого регистров, выход инвертора соединен со вторым входом пятого формирователя импульсов, выход схемы сброса соединен с третьими входами первого, четвертого и пятого регистров, выход второго генератора прямоугольных импульсов соединен с первым входом третьего элемента И, выход которого соединен с первым входом четвертого счетчика и входом первого формирователя импульсов, выход второго элемента И соединен со вторым входом четвертого счетчика и третьими входами второго регистра и третьего триггера, выход которого соединен с входом третьего формирователя импульсов и вторым входом третьего элемента И, выход первого триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с четвертым входом третьего дешифратора, выход второго триггера соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй, третий, пятый и шестой выходы первого дешифратора соединены соответственно со вторым и третьим входами первого элемента И-НЕ и вторым и третьим входами четвертого элемента И-НЕ, первый, второй, третий, четвертый и шестой выходы второго дешифратора соединены соответственно с первым и вторым входами пятого элемента И-НЕ, первым входом шестого элемента И-НЕ, вторым входом второго элемента И-НЕ и первым входом третьего элемента И-НЕ, первый, второй, третий, четвертый, пятый и шестой выходы третьего дешифратора соединены соответственно со вторыми входами третьего и шестого элементов И-НЕ и третьими входами второго, шестого, третьего и пятого элементов И-НЕ, первый, второй и третий выходы третьего регистра являются соответственно седьмым, восьмым и девятым выходами цифрового модулятора.

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2012 |

|

RU2517423C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ ДВУХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1997 |

|

RU2126198C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| Цифровой управляемый преобразователь частоты | 1982 |

|

SU1069146A1 |

| Число-импульсный следящий электропривод | 1983 |

|

SU1124256A1 |

| US 4764940 A, 16.08.1988 | |||

| US 10469064 B2, 05.11.2019 | |||

| СТАРИКОВ А.В., ЛИСИН С.Л., РОКАЛО Д.Ю | |||

| Влияние широтно-импульсной модуляции на гармонический состав | |||

Авторы

Даты

2022-06-15—Публикация

2021-07-19—Подача