Изобретение относится к области импульсной техники и может быть использовано в преобразователях частоты для управления электродвигателями переменного тока.

Наиболее близким по технической сущности является цифровой модулятор для преобразователя частоты (см. патент РФ №2644070, опубл. 07.02.2018, бюл. №4), содержащий два генератора прямоугольных импульсов, четыре счетчика, четыре триггера, четыре элемента ИЛИ, инвертор, два элемента И, семь элементов И-НЕ, три дешифратора, три формирователя импульсов, два сумматора, три регистра, двоично-шестеричный счетчик, схему ограничения, схему сброса, шесть выходных шин, шину сигнала задания частоты, шину сигнала задания напряжения и шину знака.

Недостаток наиболее близкого цифрового модулятора заключается в том, что он позволяет сформировать трапецеидальное фазное напряжение на выходе преобразователя частоты, а это приводит к появлению относительно больших амплитуд высших гармоник.

Технический результат достигается тем, что в цифровой модулятор для преобразователя частоты, содержащий первый и второй генераторы прямоугольных импульсов, первый, второй, третий и четвертый счетчики, первый, второй и третий триггеры, первый и второй элементы ИЛИ, элемент И, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И-НЕ, первый, второй и третий дешифраторы, первый и второй формирователи импульсов, сумматор, первый, второй, третий и четвертый регистры, двоично-шестеричный счетчик и схему сброса, причем выход первого генератора прямоугольных импульсов соединен с первыми входами первого и второго счетчиков, выход первого счетчика соединен с первым входом элемента И, выход первого формирователя импульсов соединен с первыми входами первого и второго элементов ИЛИ, первый, второй и третий выходы двочно-шестеричного счетчика соединены соответственно с первым, вторым и третьим входами первого, второго и третьего дешифраторов, выход сумматора соединен с первым входом первого регистра, выход которого соединен с первым входом сумматора, выход схемы сброса соединен с первыми входами первого триггера, второго и третьего регистров, третьего счетчика, двоично-шестиричного счтчика и вторыми входами первого регистра и элемента И, первый выход первого триггера соединен с вторым входом первого элемента ИЛИ, второй выход первого триггера соединен с вторыми входами второго элемента ИЛИ и двоично-шестеричного счетчика, выход второго счетчика соединен с первым входом второго триггера, выход которого соединен с четвертым входом первого дешифратора, выход четвертого счетчика соединен с первым входом третьего триггера, выход которого соединен с четвертым входом второго дешифратора, выход элемента И соединен с вторыми входами второго и третьего триггеров, первого и второго счетчиков и первым входом четвертого счетчика, первый и четвертый выход первого дешифратора соединены с первыми входами соответственно первого и четвертого элемента И-НЕ, пятый выход второго дешифратора соединен с первым входом второго элемента И-НЕ, выход второго генератора прямоугольных импульсов соединен с третьим входом первого регистра и первым входом седьмого элемента И-НЕ, второй вход которого соединен с выходом элемента И, шина сигнала задания частоты соединена с вторым входом второго регистра, выход которого соединен с вторым входом сумматора, шина первого сигнала задания напряжения соединена с вторым входом третьего регистра, выход которого соединен с вторым входом четвертого счетчика, шина сигнала направления вращения соединена с вторым входом первого триггера, шина сигнала синхронизации соединена с первым входом второго формирователя импульсов, выход которого соединен с третьими входами певого триггера, второго и третьего регистров и первым входом четвертого регистра, выход седьмого элемента И-НЕ соединен с вторым входом второго формирователя импульсов, дополнительно введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход схемы сброса соединен с вторым входом четвертого регистра, выход которого соединен с третьим входом второго счетчика, третий вход четвертого регистра соединен с шиной второго сигнала задания напряжения, выходы второго и третьего триггеров соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с четвертым входом третьего дешифратора, выход первого генератора прямоугольных импульсов соединен с третьим входом четвертого счетчика, старший разряд выхода первого регистра соединен с входом первого формирователя импульсов, выходы первого и второго элементов ИЛИ соединены соответственно с вторым и третьим входами третьего счетчика, первый и второй выходы которого соединены соответственно с третьим и четвертым входами двоично-шестиричного счетчика, второй, третий, пятый и шестой выходы первого дешифратора соединены соответственно с вторым и третьим входами первого элемента И-НЕ и вторым и третьим входами четвертого элемента И-НЕ, первый, второй, третий, четвертый и шестой выходы второго дешифратора соединены соответственно с первым и вторым входами пятого элемента И-НЕ, первым входом шестого элемента И-НЕ, вторым входом второго элемента И-НЕ и первым входом третьего элемента И-НЕ, первый, второй, третий, четвертый, пятый и шестой выходы третьего дешифратора соединены соответственно с вторыми входами третьего и шестого элементов И-НЕ и третьими входами второго, шестого, третьего и пятого элементов И-НЕ, третий выход третьего счетчика является первым выходом цифрового модулятора, первый, второй и третий выходы двоично-шестеричного счетчика являются соответственно вторым, третьим и четвертым выходами цифрового модулятора, а выходы первого, второго, третьего, четвертого, пятого и шестого элементов И-НЕ являются соответственно пятым, шестым, седьмым, восьмым, девятым и десятым выходами цифрового модулятора.

Существенные отличия находят свое выражение в новой совокупности связей между элементами устройства. Указанная совокупность связей позволяет с помощью предлагаемого цифрового модулятора уменьшить амплитуды высших гармоник в выходном напряжении преобразователя частоты.

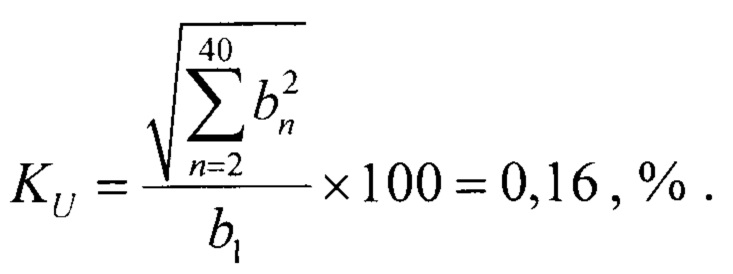

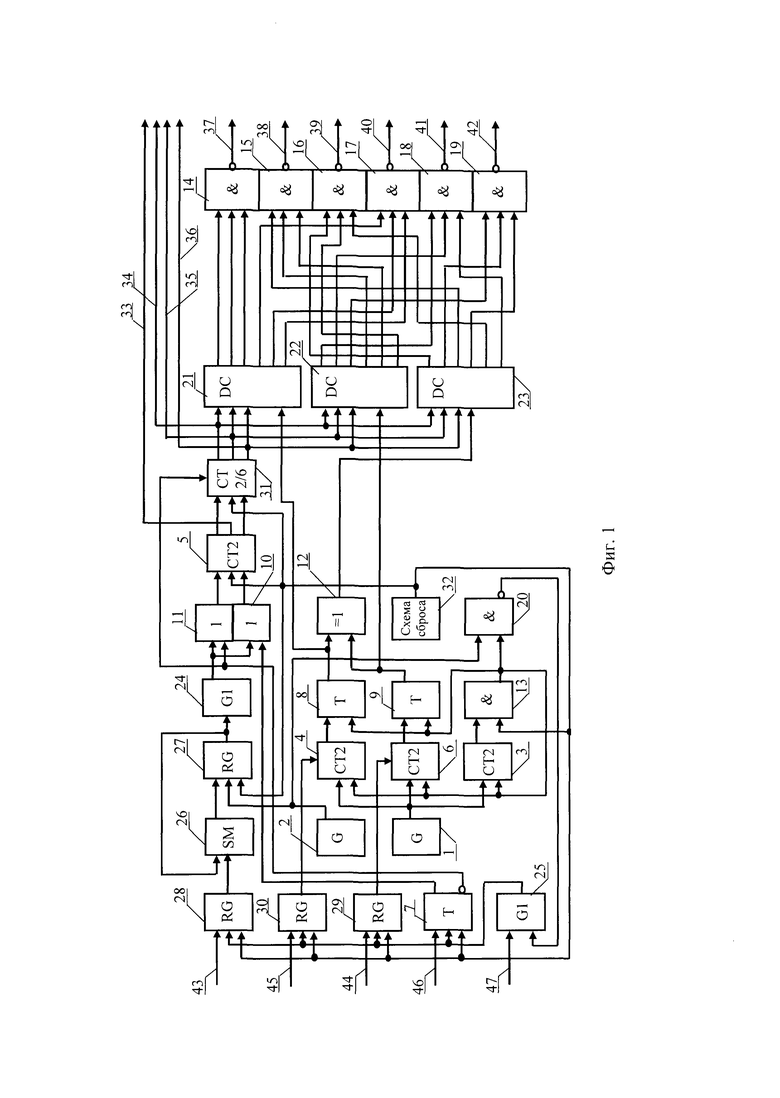

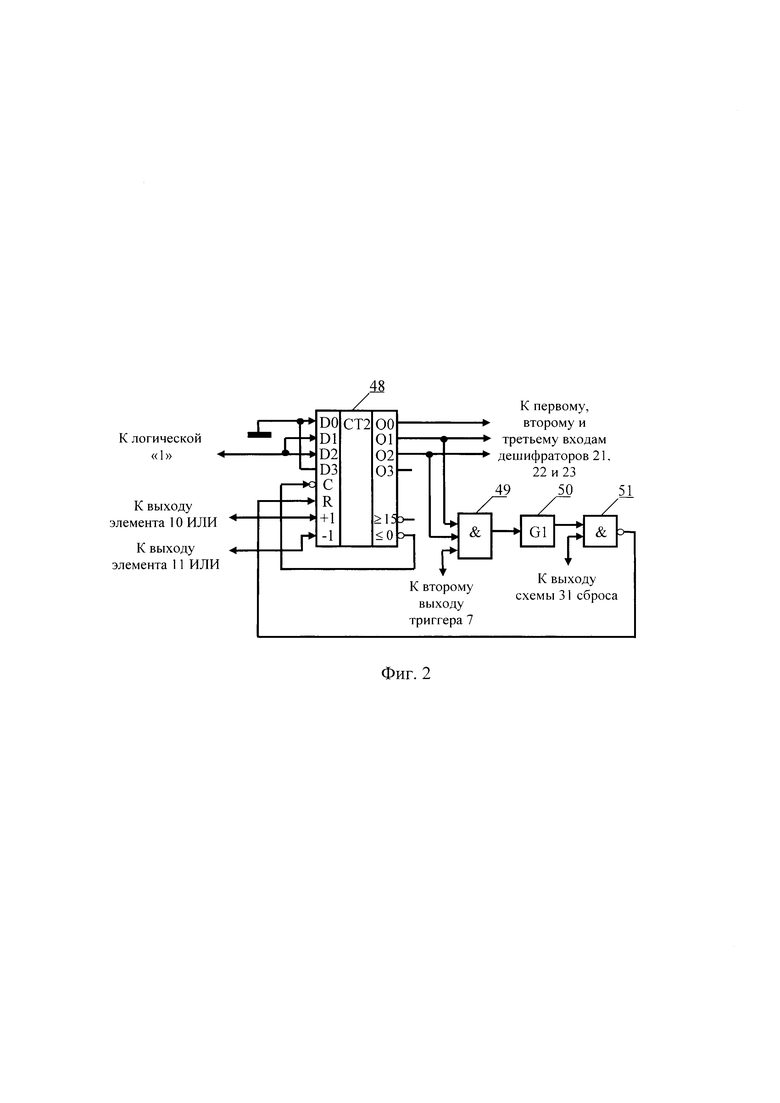

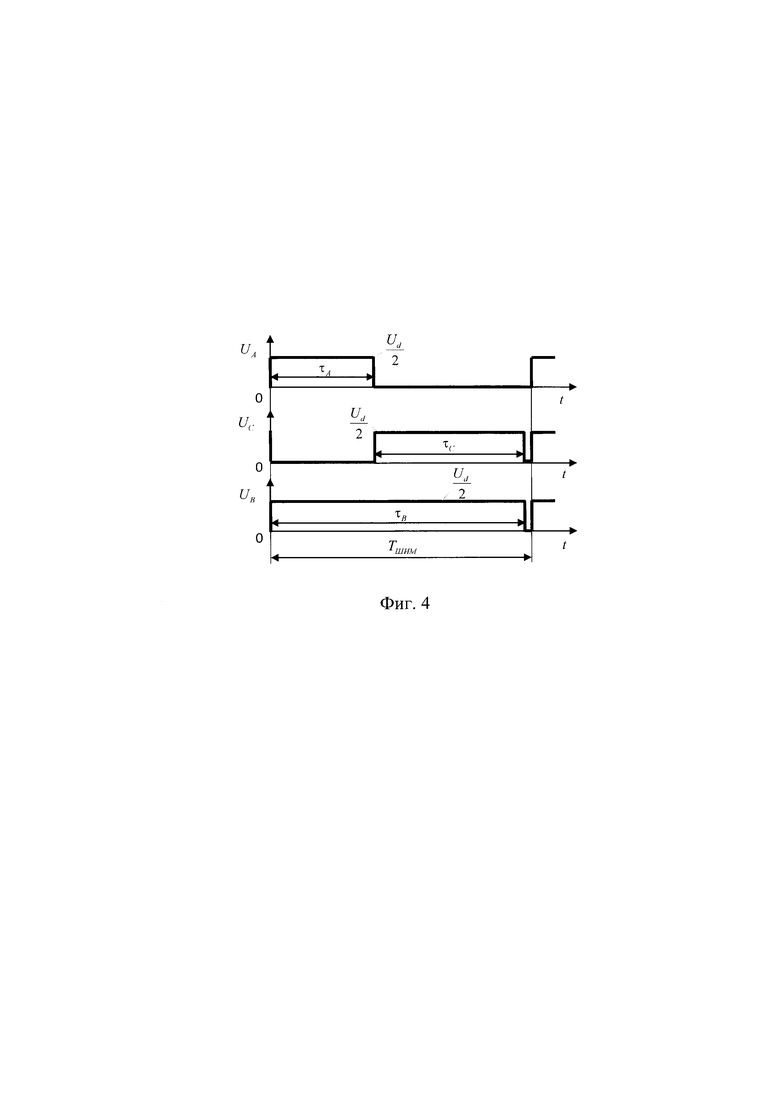

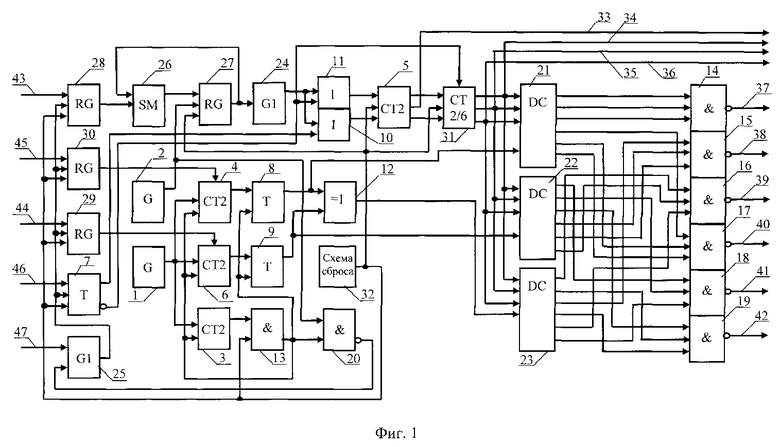

На фиг. 1 представлена функциональная схема цифрового модулятора для преобразователя частоты, на фиг. 2 - функциональная схема двоично-шестеричного счетчика, на фиг. 3 - схема подключения цифрового модулятора к силовым транзисторам преобразователя частоты, на фиг. 4 - диаграммы фазных напряжений на одном периоде широтно-импульсной модуляции.

Цифровой модулятор для преобразователя частоты (фиг. 1) содержит генератор 1 и 2 прямоугольных импульсов, счетчики 3, 4, 5 и 6, триггеры 7, 8 и 9, элементы 10 и 11 ИЛИ, элемент 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент 13 И, элементы 14, 15, 16, 17, 18, 19 и 20 И-НЕ, дешифраторы 21, 22 и 23, формирователи 24 и 25 импульсов, сумматор 26, регистры 27, 28, 29 и 30, двоично-шестеричный счетчик 31, схему 32 сброса, выходные шины 33, 34, 35, 36, 37, 38, 39, 40, 41 и 42, шину 43 сигнала задания частоты, шину 44 первого сигнала задания напряжения, шину 45 второго сигнала задания напряжения, шину 46 сигнала направления вращения и шину 47 сигнала синхронизации.

Выход генератора 1 прямоугольных импульсов соединен с первыми входами (входами обратного счета) счетчиков 3 и 4. Выход переноса счетчика 3 соединен с первым входом элемента 13 И. Выход формирователя 24 импульсов соединен с первыми входами элементов ИЛИ 10 и 11. Первый, второй и третий выходы двочно-шестеричного счетчика 31 соединены соответственно с первым, вторым и третьим входами дешифраторов 21, 22 и 23. Выход сумматора 26 соединен с первым входом регистра 27, выход которого соединен с первым входом сумматора 26. Выход схемы 32 сброса соединен с первыми входами триггера 7, регистров 28 и 29, счетчика 5, двоично-шестиричного счтчика 31 и вторыми входами регистра 27 и элемента 13 И. Первый (прямой) выход триггера 7 соединен с вторым входом элемента 10 ИЛИ. Второй (инверсный) выход триггера 7 соединен с вторыми входами элемента 11 ИЛИ и двоично-шестеричного счетчика 31. Выход переноса счетчика 4 соединен с первым входом (входом сброса) триггера 8, выход которого соединен с четвертым входом (входом разрешения) дешифратора 21. Выход счетчика 6 соединен с первым входом (входом сброса) триггера 9, выход которого соединен с четвертым входом (входом разрешения) дешифратора 22. Выход элемента 13 И соединен с вторыми входами (входами установки) триггеров 8 и 9. Выход элемента 13 И соединен также с вторыми входами (входами стробирования) счетчиков 3 и 4 и первым входом (входом стробирования) счетчика 6. Первый и четвертый выход дешифратора 21 соединены с первым входами соответственно элементов 14 и 17 И-НЕ. Пятый выход дешифратора 22 соединен с первым входом элемента 15 И-НЕ. Выход генератора 2 прямоугольных импульсов соединен с третьим входом (входом стробирования) регистра 27 и первым входом элемента 20 И-НЕ, второй вход которого соединен с выходом элемента 13 И. Шина 43 сигнала задания частоты соединена с вторым (информационным) входом регистра 28, выход которого соединен с вторым входом сумматора 26. Шина 44 первого сигнала задания напряжения соединена с вторым (информационным) входом регистра 29, выход которого соединен с вторым входом (информационным входом предварительной установки) счетчика 6. Шина 46 сигнала направления вращения соединена с вторым входом триггера 7. Шина 47 сигнала синхронизации соединена с первым входом (входом запуска) формирователя 25 импульсов, выход которого соединен с третьими входами (входами стробирования) триггера 7, регистров 28 и 29 и первым входом (входами стробирования) регистра 30. Выход элемента 20 И-НЕ соединен с вторым входом (входом блокироаки) формирователя 25 импульсов. Выход схемы 32 сброса соединен с вторым входом (входом сброса) регистра 30, выход которого соединен с третьим входом (информационным входом предварительной установки) счетчика 4. Третий вход (информационный) регистра 30 соединен с шиной 45 второго сигнала задания напряжения. Выходы триггеров 8 и 9 соединены соответственно с первым и вторым входами элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с четвертым входом (входом разрешения) дешифратора 23. Выход генератора 1 прямоугольных импульсов соединен с третьим входом (входами обратного счета) счетчика 6. Старший разряд выхода регистра 27 соединен с входом формирователя 24 импульсов. Выходы элементов 10 и 11 ИЛИ соединены соответственно с вторым (прямого счета) и третьим (обратного счета) входами счетчика 5, первый и второй выходы (выходы переноса) которого соединены соответственно с третьим (прямого счета) и четвертым (обратного счета) входами двоично-шестиричного счетчика 31. Второй, третий, пятый и шестой выходы дешифратора 21 соединены соответственно с вторым и третьим входами элемента 14 И-НЕ и вторым и третьим входами элемента 17 И-НЕ. Первый, второй, третий, четвертый и шестой выходы дешифратора 22 соединены соответственно с первым и вторым входами элемента 18 И-НЕ, первым входом элемента 19 И-НЕ, вторым входом элемента 15 И-НЕ и первым входом элемента 16 И-НЕ. Первый, второй, третий, четвертый, пятый и шестой выходы дешифратора 23 соединены соответственно с вторыми входами элементов 16 и 19 И-НЕ и третьими входами элементов 15, 19, 16 и 18 И-НЕ. Третий (информационный) выход счетчика 5 является первым выходом цифрового модулятора. Первый, второй и третий выходы двоично-шестеричного счетчика 3 1 являются соответственно вторым, третьим и четвертым выходами цифрового модулятора, а выходы элементов 14, 15, 16, 17, 18 и 19 И-НЕ являются соответственно пятым, шестым, седьмым, восьмым, девятым и десятым выходами цифрового модулятора.

Генераторы 1 и 2 прямоугольных импульсов могут быть выполнены, например, на микросхемах КР1533ЛАЗ с кварцевой стабилизацией или с вре-мязадающими конденсаторами. Счетчики 3, 4, 5 и 6, например, выполнены на микросхемах КР1533ИЕ7, триггеры 7, 8 и 9 могут быть выполнены, например, на микросхемах КР15333ТМ2. Элементы 10 и 11 ИЛИ, например, выполнены на микросхеме КР1533ЛЛ1, элемент 12 ИСКЛЮЧАЮЩЕЕ ИЛИ - на микросхеме КР1533ЛП5, элемент 13 И - на микросхеме КР1533ЛИ1, элементы 14, 15, 16, 17, 18 и 19 И-НЕ - на микросхемах К555ЛА4, элемент 20 И-НЕ - на микросхеме КР1533ЛАЗ. Дешифраторы 21, 22 и 23, могут быть выполнены, например, на микросхемах КР1533ИД7, формирователи 24 и 25 импульсов - на микросхемах К555АГЗ, сумматор 26 - на микросхемах К555ИМ6, регистры 27, 28, 29 и 30 -на микросхемах КР1533ТМ8.

Двоично-шестеричный счетчик 31 (фиг. 2), например, содержит двоичный счетчик 48, элементы 49 И, формирователь 50 импульсов и элемент 51 И-НЕ. Первый, второй и третий разряды выхода счетчика 48 являются соответственно первым, вторым и третьим выходами двоично-шестеричного счетчика 31. Второй и третий выходные разряды счетчика 48 соединены соответственно с первым и вторым входами элемента 49 И, выход которого соединен с входом формирователя 50 импульсов. Выход формирователя 50 импульсов соединен с первым входом элемента 51 И-НЕ, выход которого соединен с входом сброса счетчика 48. Выход переноса счетчика 48 соединен с входом стробирования этого счетчика. Первый и четвертый разряды информационного входа счетчика 48 соединен с общей шиной, а на второй и третий разряды подается сигнал логической единицы. Третий вход элемента 49 И является вторым входом двоично-шестеричного счетчика. Входы прямого и обратного счета счетчика 48 являются соответственно третьим и четвертым входами двоично-шестеричного счетчика 31. Второй вход элемента 51 И-НЕ является первым входом двоично-шестеричного счетчика 31.

Схема 32 сброса, например, может быть выполнена в виде последовательно соединенных резистора и конденсатора, причем второй вывод резистора присоединяется к шине питания, а второй вывод конденсатора - к общей шине. Вывод резистора, соединенный с конденсатором, является выходом схемы 32 сброса.

Цифровой модулятор для преобразователя частоты работает следующим образом.

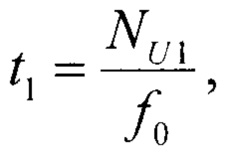

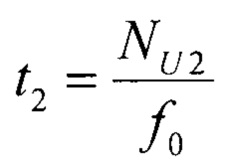

После включения напряжения питания схема 32 сброса формирует сигнал, который устанавливает в исходное состояние триггер 7, счетчик 5, регистры 27, 28, 29 и 30 и двоично-шестеричный счетчик 31. Этот же сигнал через элемент 13 И устанавливает в исходное (высокое) состояние выходы триггеров 8 и 9, а также стробирует счетчики 3, 4 и 6. С задержкой времени, определяемой срабатыванием элемента 20 И-НЕ и длиной импульса формирователя 25 в регистр 28 с шины 43 записывается цифровой код Nf, определяющий требуемую частоту силового преобразователя, в регистр 29 с шины 44 записывается цифровой код NU1 первого сигнала задания напряжения, в регистр 30 с шины 45 записывается цифровой код NU2 второго сигнала задания напряжения, а в триггер 7 с шины 46 -знак требуемого направления вращения. Через период времени, определяемый частотой генератора 1 прямоугольных импульсов и разрядностью счетчика 3, произойдет очередное стробирование счетчиков 4 и 6 и установка триггеров 8 и 9. При этом сигнал NU1 с выхода регистра 29 записывается в счетчик 6, а сигнал NU2 - в счетчик 4. Импульсы генератора 1 с частотой f0 поступают на входы обратного счета счетчиков 4 и 6. В результате на выходе переноса счетчика через интервал времени

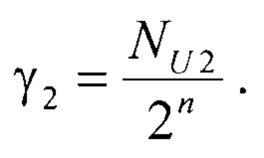

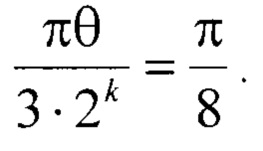

после стробирования появится отрицательный импульс, который поступает на вход сброса триггера 9. При этом на выходе триггера 9 появляется сигнал низкого уровня. На выходе переноса счетчика 4 появляется отрицательный импульс через интервал времени

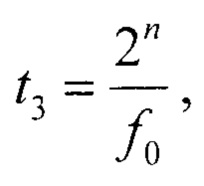

после стробирования. Этот импульс поступает на вход установки триггера 8. При этом на выходе триггера 8 появляется сигнал низкого уровня. Прямоугольные импульсы с генератора 1 поступают также на счетный вход счетчика 3. Поэтому на выходе переноса счетчика 3 через промежуток времени

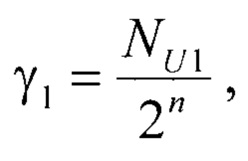

где n - количество разрядов двоичного счетчика, после начальной установки появляется отрицательный импульс. Этот импульс, пройдя через элемент 13 И, поступает на вход установки триггеров 8 и 9 и возвращает их в исходное состояние. Отрицательный импульс с выхода счетчика 3 через элемент 13 И стробирует счетчики 3, 4 и 6, после чего процесс формирования выходных сигналов счетчиков 4 и 6 и триггеров 8 и 9 повторяется. В результате на выходе триггера 9 формируется сигнал со скважностью

А на выходе триггера 8 - со скважностью

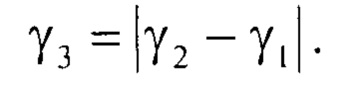

При этом на выходе элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется сигнал высокого уровня со скважностью

Одновременно с работой названных выше элементов сигнал с выхода

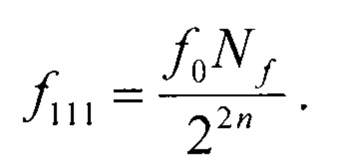

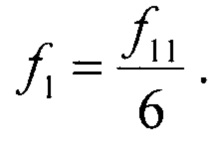

регистра 28 поступает на вход сумматора 26 и суммируется с сигналом на выходе регистра 27. В первоначальный момент времени на выходе регистра 27 находится нулевой сигнал. По приходу импульса с генератора 2 в регистр 27 записывается сигнал с выхода сумматора 26 и далее процесс повторяется. В результате происходит нарастание сигнала на выходе сумматора 26 и регистра 27. Вследствие этого на старшем разряде выхода регистра 27 появляется сигнал высокого уровня с частотой f1, которая при наличии двойной разрядности сумматора 26 и регистра 27 линейно зависит от величины Nf входного сигнала

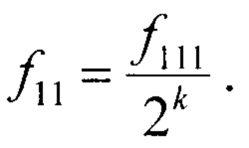

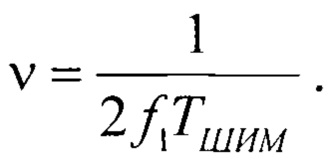

Импульсы со старшего разряда выхода регистра 27 через формирователь 24 импульсов поступают на входы элементов 10 и 11 ИЛИ. При заданном на шине 46 положительном направлении вращения эти импульсы проходят на вход прямого счета счетчика 5, а при отрицательном направлении вращения (реверсе) - на вход обратного счета этого счетчика. Если счетчик 5 имеет k двоичных разрядов, то на его выходах переноса появляются импульсы с частотой

Эти импульсы поступают на соответствующие счетные входы двоично-шестеричного счетчика 31. При этом на первом, втором и третьем выходах названного счетчика формируются периодические сигналы, причем частота f1 появления одного и того же кодового сочетания на этих выходах равна

В зависимости от кодового сочетания сигналов выходов двоично-шестеричного счетчика 31 и сигналов с триггеров 8 и 9 и элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ дешифраторы 21, 22 и 23 через элементы 14, 15, 16, 17, 18 и 19 И-НЕ подают частотно-широтно-модулированный сигнал на выходные шины 37, 38, 39, 40, 41 и 42 цифрового модулятора. При этом частота f1 смены сочетаний работающих выходов меняется в функции сигнала Nf.

Одновременно на шину 33 подается выходной сигнал счетчика 5, а на шины 34, 35 и 36 - выходной сигнал двоично-шестеричного счетчика 31. В результате на совокупности выходных шин 33, 34, 35 и 36 формируется цифровой двоичный код θ, который изменяется от 0 до (6⋅2k-1). На шинах же 34, 35 и 36 цифровой код изменяется от 0 до 5.

Смена информации в триггере 7 и регистрах 28, 29 и 30 происходит по приходу импульса с формирователя 25, который запускается при появлении соответствующего сигнала синхронизации на шине 47. Для исключения ложных срабатываний и вычислений импульсы с генератора 2 и элемента 13 И проходят через элемент 20 И-НЕ и блокируют формирователь 25 импульсов.

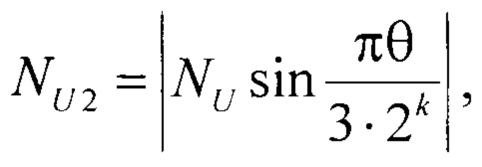

Для того, чтобы предлагаемый цифровой модулятор осуществлял синусоидальную модуляцию, необходимо на шину 45 подавать цифровой код

где NU - цифровой код, задающий амплитуду напряжения.

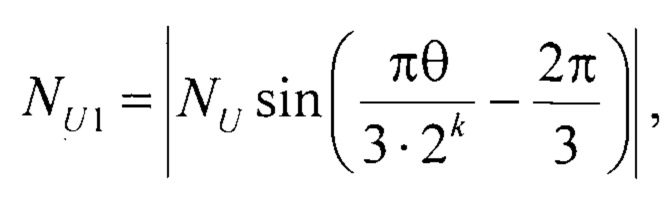

На шину 44 необходимо подавать цифровой код

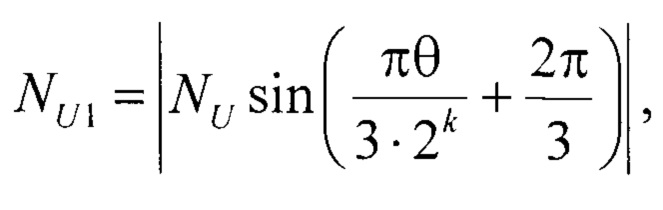

если на шинах 34, 35 и 36 сформирован цифровой код, соответствующий 0, 1, 3 или 4, или

если на шинах 34, 35 и 36 присутствует код, соответствующий 2 или 5.

Если выходные шины 37, 38, 39, 40, 41 и 42 цифрового модулятора подключить к силовым транзисторам частотного преобразователя как показано на фиг. 3, то на статорных обмотках асинхронного двигателя, включенных в звезду, каждый период широтно-импульсной модуляции будет формироваться система фазных напряжений, аналогичная приведенной на фиг. 4. Следует отметить, что на фиг. 4 изображен случай, когда

Амплитуда импульсов напряжения будет составлять  а ширина импульсов для фазы А будет составлять, например, для цифровых кодов 0, 1, 3 и 4 на шинах 34, 35 и 36,

а ширина импульсов для фазы А будет составлять, например, для цифровых кодов 0, 1, 3 и 4 на шинах 34, 35 и 36,

для фазы А - τA=γ2TШИМ,

для фазы В - τB=γ1ТШИМ,

для фазы С - τC=γ3ТШИМ,

где ТШИМ - период широтно-импульсной модуляции.

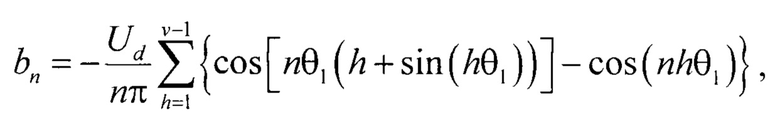

В результате фазное напряжение будет представлять собой кусочно-постоянную функцию, принимающую значения  и 0, причем ширина импульсов будет изменяться по синусоидальному закону. Амплитуды высших гармоник в выходном напряжении частотного преобразователя, например, для фазы А в этом случае будут определяться формулой (для максимального значения фазного напряжения)

и 0, причем ширина импульсов будет изменяться по синусоидальному закону. Амплитуды высших гармоник в выходном напряжении частотного преобразователя, например, для фазы А в этом случае будут определяться формулой (для максимального значения фазного напряжения)

где n - номер гармоники; θ1=2πf1ТШИМ;

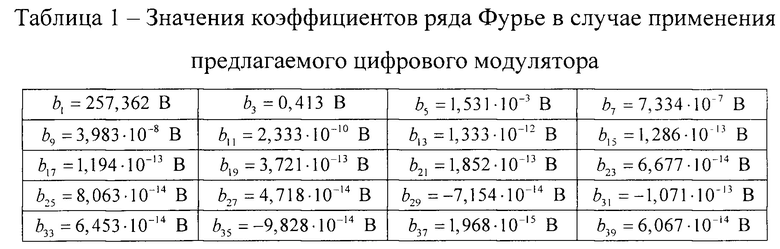

Подсчет по приведенной формуле показывает, что при Ud=515 В, f1=50 Гц, ТШИМ=2,08333⋅10-4 амплитуды первой и высших гармоник будут принимать следующие значения (таблица 1).

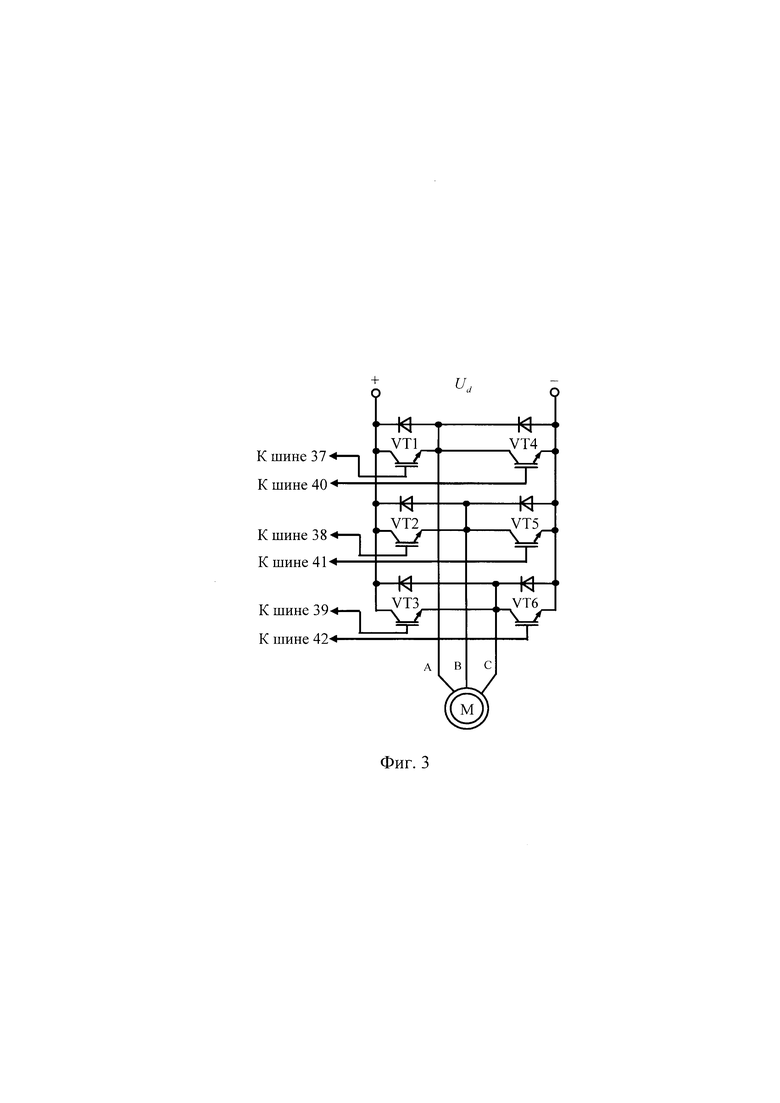

Следовательно, суммарный коэффициент гармонических составляющих (в соответствии с ГОСТ 32144-2013) в выходном напряжении частотного преобразователя будет равен

Это в 24 раза меньше, чем достижимый суммарный коэффициент гармонических составляющих в устройстве, взятом за прототип.

Таким образом, предложенный цифровой модулятор для преобразователя частоты позволяет уменьшить амплитуды высших гармоник в выходном напряжении инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2012 |

|

RU2517423C1 |

| Цифровой модулятор для преобразователя частоты | 2021 |

|

RU2774161C1 |

| Цифровой модулятор | 1991 |

|

SU1800604A1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ ДВУХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1997 |

|

RU2126198C1 |

| Цифровой модулятор для управления синхронным двигателем | 2019 |

|

RU2711049C1 |

| Устройство для моделирования полосы частот с маркером | 1981 |

|

SU970396A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОДНОФАЗНЫМ АСИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2013 |

|

RU2542717C2 |

Изобретение относится к области импульсной техники и может быть использовано в преобразователях частоты для управления электродвигателями переменного тока. Техническим результатом является уменьшение амплитуд высших гармоник в выходном напряжении преобразователя частоты. Цифровой модулятор для преобразователя частоты содержит генераторы 1 и 2 прямоугольных импульсов, счетчики 3, 4, 5 и 6, триггеры 7, 8 и 9, элементы 10 и 11 ИЛИ, элемент 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент 13 И, элементы 14, 15, 16, 17, 18, 19 и 20 И-НЕ, дешифраторы 21, 22 и 23, формирователи 24 и 25 импульсов, сумматор 26, регистры 27, 28, 29 и 30, двоично-шестеричный счетчик 31, схему 32 сброса, выходные шины 33, 34, 35, 36, 37, 38, 39, 40, 41 и 42, шину 43 сигнала задания частоты, шину 44 первого сигнала задания напряжения, шину 45 второго сигнала задания напряжения, шину 46 сигнала направления вращения и шину 47 сигнала синхронизации. 4 ил., 1 табл.

Цифровой модулятор для преобразователя частоты, содержащий первый и второй генераторы прямоугольных импульсов, первый, второй, третий и четвертый счетчики, первый, второй и третий триггеры, первый и второй элементы ИЛИ, элемент И, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И-НЕ, первый, второй и третий дешифраторы, первый и второй формирователи импульсов, сумматор, первый, второй, третий и четвертый регистры, двоично-шестеричный счетчик и схему сброса, причем выход первого генератора прямоугольных импульсов соединен с первыми входами первого и второго счетчиков, выход первого счетчика соединен с первым входом элемента И, выход первого формирователя импульсов соединен с первыми входами первого и второго элементов ИЛИ, первый, второй и третий выходы двочно-шестеричного счетчика соединены соответственно с первым, вторым и третьим входами первого, второго и третьего дешифраторов, выход сумматора соединен с первым входом первого регистра, выход которого соединен с первым входом сумматора, выход схемы сброса соединен с первыми входами первого триггера, второго и третьего регистров, третьего счетчика, двоично-шестиричного счтчика и вторыми входами первого регистра и элемента И, первый выход первого триггера соединен с вторым входом первого элемента ИЛИ, второй выход первого триггера соединен с вторыми входами второго элемента ИЛИ и двоично-шестеричного счетчика, выход второго счетчика соединен с первым входом второго триггера, выход которого соединен с четвертым входом первого дешифратора, выход четвертого счетчика соединен с первым входом третьего триггера, выход которого соединен с четвертым входом второго дешифратора, выход элемента И соединен с вторыми входами второго и третьего триггеров, первого и второго счетчиков и первым входом четвертого счетчика, первый и четвертый выходы первого дешифратора соединены с первыми входами соответственно первого и четвертого элементов И-НЕ, пятый выход второго дешифратора соединен с первым входом второго элемента И-НЕ, выход второго генератора прямоугольных импульсов соединен с третьим входом первого регистра и первым входом седьмого элемента И-НЕ, второй вход которого соединен с выходом элемента И, шина сигнала задания частоты соединена с вторым входом второго регистра, выход которого соединен с вторым входом сумматора, шина первого сигнала задания напряжения соединена с вторым входом третьего регистра, выход которого соединен с вторым входом четвертого счетчика, шина сигнала направления вращения соединена с вторым входом первого триггера, шина сигнала синхронизации соединена с первым входом второго формирователя импульсов, выход которого соединен с третьими входами первого триггера, второго и третьего регистров и первым входом четвертого регистра, выход седьмого элемента И-НЕ соединен с вторым входом второго формирователя импульсов, отличающийся тем, что в него дополнительно введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход схемы сброса соединен с вторым входом четвертого регистра, выход которого соединен с третьим входом второго счетчика, третий вход четвертого регистра соединен с шиной второго сигнала задания напряжения, выходы второго и третьего триггеров соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с четвертым входом третьего дешифратора, выход первого генератора прямоугольных импульсов соединен с третьим входом четвертого счетчика, старший разряд выхода первого регистра соединен с входом первого формирователя импульсов, выходы первого и второго элементов ИЛИ соединены соответственно с вторым и третьим входами третьего счетчика, первый и второй выходы которого соединены соответственно с третьим и четвертым входами двоично-шестиричного счетчика, второй, третий, пятый и шестой выходы первого дешифратора соединены соответственно с вторым и третьим входами первого элемента И-НЕ и вторым и третьим входами четвертого элемента И-НЕ, первый, второй, третий, четвертый и шестой выходы второго дешифратора соединены соответственно с первым и вторым входами пятого элемента И-НЕ, первым входом шестого элемента И-НЕ, вторым входом второго элемента И-НЕ и первым входом третьего элемента И-НЕ, первый, второй, третий, четвертый, пятый и шестой выходы третьего дешифратора соединены соответственно с вторыми входами третьего и шестого элементов И-НЕ и третьими входами второго, шестого, третьего и пятого элементов И-НЕ, третий выход третьего счетчика является первым выходом цифрового модулятора, первый, второй и третий выходы двоично-шестеричного счетчика являются соответственно вторым, третьим и четвертым выходами цифрового модулятора, а выходы первого, второго, третьего, четвертого, пятого и шестого элементов И-НЕ являются соответственно пятым, шестым, седьмым, восьмым, девятым и десятым выходами цифрового модулятора.

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ ДВУХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1997 |

|

RU2126198C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| Цифровой управляемый преобразователь частоты | 1982 |

|

SU1069146A1 |

| Число-импульсный следящий электропривод | 1983 |

|

SU1124256A1 |

| US 4764940 A, 16.08.1988 | |||

| US 10469064 B2, 05.11.2019 | |||

| СТАРИКОВ А.В., ЛИСИН С.Л., РОКАЛО Д.Ю | |||

| Влияние широтно-импульсной модуляции на гармонический состав выходного напряжения частотного | |||

Авторы

Даты

2021-12-17—Публикация

2021-04-15—Подача