В асинхронном режиме входы первый и четвертый (А, А), jn-орой и пятый (В, В), третий и шестой (С, С), а также первый и второй выходы (Z. Z) являются парафазными. Это значит, что на входах и выходах могут присутствовать лишь пары сигналов 10 или 01, которые кодируют логические единицу или нуль соответственно. На выходах (Z, 2) реализуется мажоритарная функция, логическая единица и нуль которой кодируются аналогично. Устройство построено таким образом, что позволяет обнаружить любую одиночную константную неисправность (ОКН) в момент ее первого проявления на выходах (Z, Z), т.е. для определения технического состояния и обнаружения ошибок, которые могут появиться в результате неисправности, в устройстве реализуется самопроверяемый контроль, В асинхронном режиме на всех входах устройства присутствуют значения 10 или 01. В том случае, если в устройстве появилась какая-либо ОКН, проявившаяся на выходах (Z, Z). то она обязательно проявится в виде значений 00 или 11, свидетельствующих о возникновении ошибки. Ни одна ОКН не может привести к такой ситуации.когда на выходах (Z, Z) вместо значений 01 из-за наличия ОКН появятся значения 10. либо наоборот. Вместе с тем, не существует такой ОКН, которая не могла бы проявиться на выходах (Z, если в процессе функционирования входы поступают значения (А,А; В,В; С.С), равные 011001,011010, 100101, 100110. Указанные четыре входных набора представляют собой тест устройства. Их поступление на входы устройства в процессе его функционирования обеспечивает условие самотестируемости. Таким образом, мажоритарное устройство самотестируемо и защищено от ошибок, порождаемых ОКН. т.е. оно в асинхронном режиме работы является самопроверяемым. Для индикации неисправности может быть использован любой сигнальный элемент, например, св етодиод, подключаемый к выходу элемента РАВНОЗНАЧНОСТЬ, входы которого соединены соответственно с первым и вторым выходами устройства.

В синхронном режиме работы третий и шестой входы (С, С), а также первый и второй выходы (Z,Z) не являются парафазными. На этих входах и выходах помимо значений 10 или 01, могут появиться также значения 00, запрещающие выполнение опер ации. Работа устройства синхронизируется поступлением сигналов 01 или 10 на входы {С, С), т.е. при реализации парафазного состояния. На выходах (Z.Z) также появится одно из значений 10 или 01, причем длительность выходного сигнала будет зависеть непосредственно от длительности парафазного сигнала, поступившего на входы (С,С). При последовательном соединении устройств

друг с другом (конвейерный режим), когда выходы (Z, Z) предыдущего устройства под- ключены соответственно к входам (С, С) последующего устройства (например, для формирования цепи переноса), осуществляется самосинхронизация устройств, т.к. выполнение операции в устройстве не начнется до тех пор, пока на его вход (С,С) не поступит парафазный сигнал с выхода предыдущего устройства.

5 Заявляемое мажоритарное устройство по сравнению с прототипом обеспечивает повышение достоверности правильноСгрд- боты в асинхронном режиме за счет того, что любая одиночная константная неисп0 равность обязательно проявляется на его выходах и обнаруживается в момент ее первого проявления, Повышение достоверности обуславливается также тем, что при использовании мажоритарного устройства

5 в качестве схемы переноса в цифровых системах конвейерного типа, например, конвейерных сумматорах, обеспечивается самосинхронизация схем, исключающая возникновение ложных сигналов переноса.

0 Формула изобретения

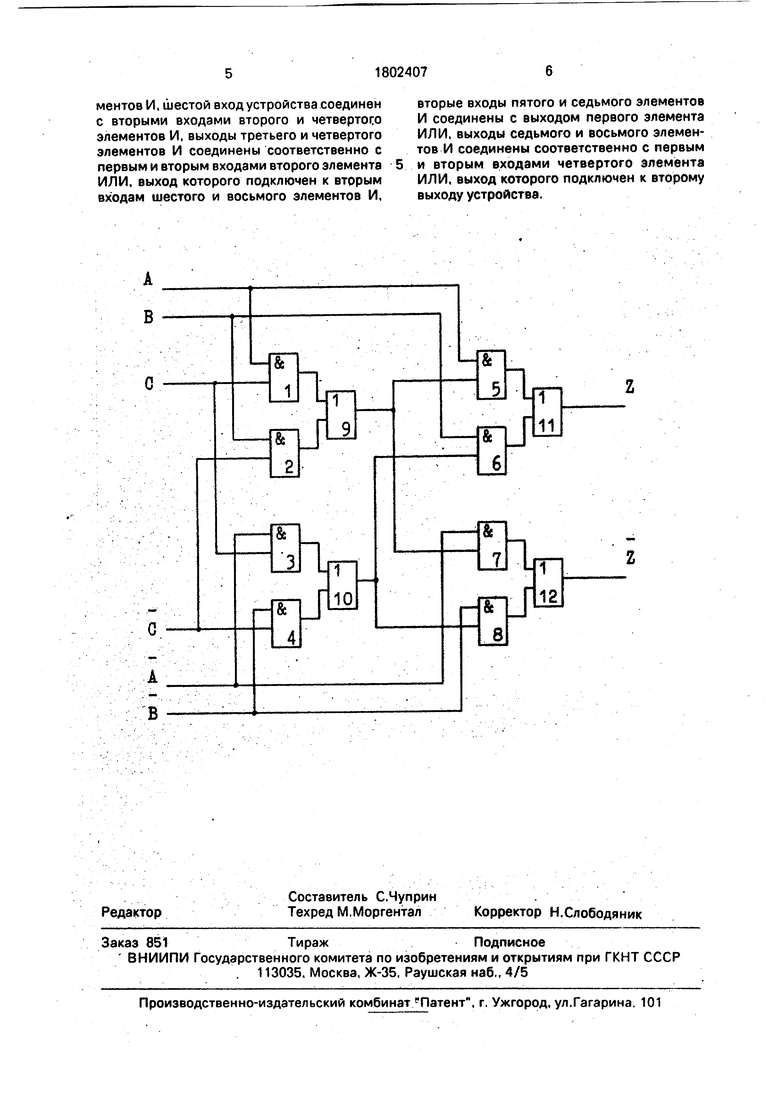

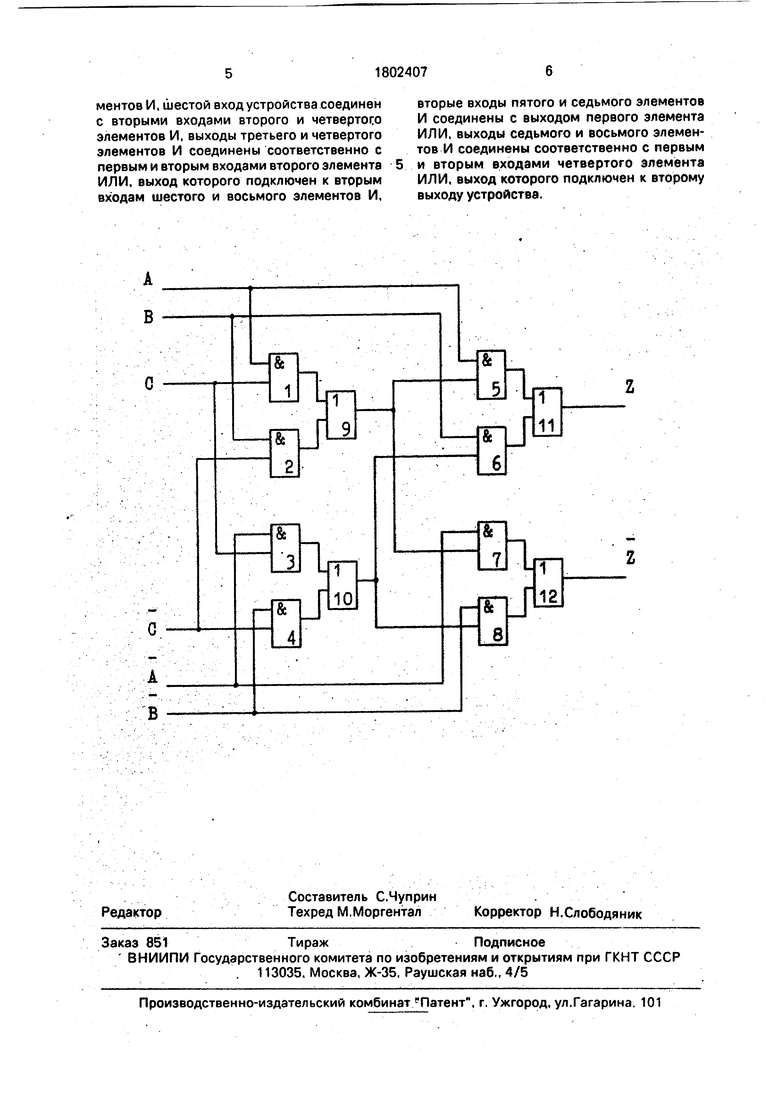

Мажоритарное устройство, содержащее с первого по третий элементы И и первый элемент ИЛИ, первый и второй входы которого соединены соответственно с вы5 ходами первого и второго элементов И, первые входы которых подключены соответственно к первому и второму входам устройства, третий вход которого соединен с вторыми входами первого и третьего-эле-.

0 ментов И, о т л и ч а ю щ ее с я тем, что. с целью повышения надежности устройства за счет обеспечения возможности его самосинхронизации и самопроверяемости, введены с четвертого по восьмой элементы И,

5 с второго по четвертый элементы ИЛИ, с четвертого по шестой входы, а также первый и второй выходы, причем первый и четвертый, а также второй и пятый входы устройства выполнены парафазными, первый и

0 второй входы устройства соединены соответственно с первыми входами пятого и шестого элементов И, выходы которых подключены соответственно к первому и второму входам третьего элемента ИЛИ, вы5 ход которого соединен с первым выходом устройства, четвертый вход устройства подключен соответственно к первым входам третьего и седьмого элементов И, пятый вход устройства подключен соответственно к первым входам четвертого и восьмого элементов И, шестой вход устройства соединен с вторыми входами второго и четвертого элементов И, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого подключен к вторым входам шестого и восьмого элементов И,

вторые входы пятого и седьмого элементов И соединены с выходом первого элемента ИЛИ, выходы седьмого и восьмого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого подключен к второму выходу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1991 |

|

SU1780171A1 |

| Самопроверяемый тестер для кода "1 из 8 | 1986 |

|

SU1324117A1 |

| Устройство для контроля парафазных сигналов | 1987 |

|

SU1510098A1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1336007A2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1336008A2 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2803625C1 |

| Устройство для мажоритарного выбора сигналов | 1991 |

|

SU1807488A1 |

А В

А В

Авторы

Даты

1993-03-15—Публикация

1991-06-08—Подача