Изобретение относится к вычислительной технике, нредназначено для использования в качестве базового элемента для построения логических процессоров, а также для создания высоконадежных средств логического управления, реализуемых на уровне технологии больших интегральных схем, и является усовершенствованием устройства по авт. св. № 1136145.

Цель изобретения - повышение достоверности контроля.

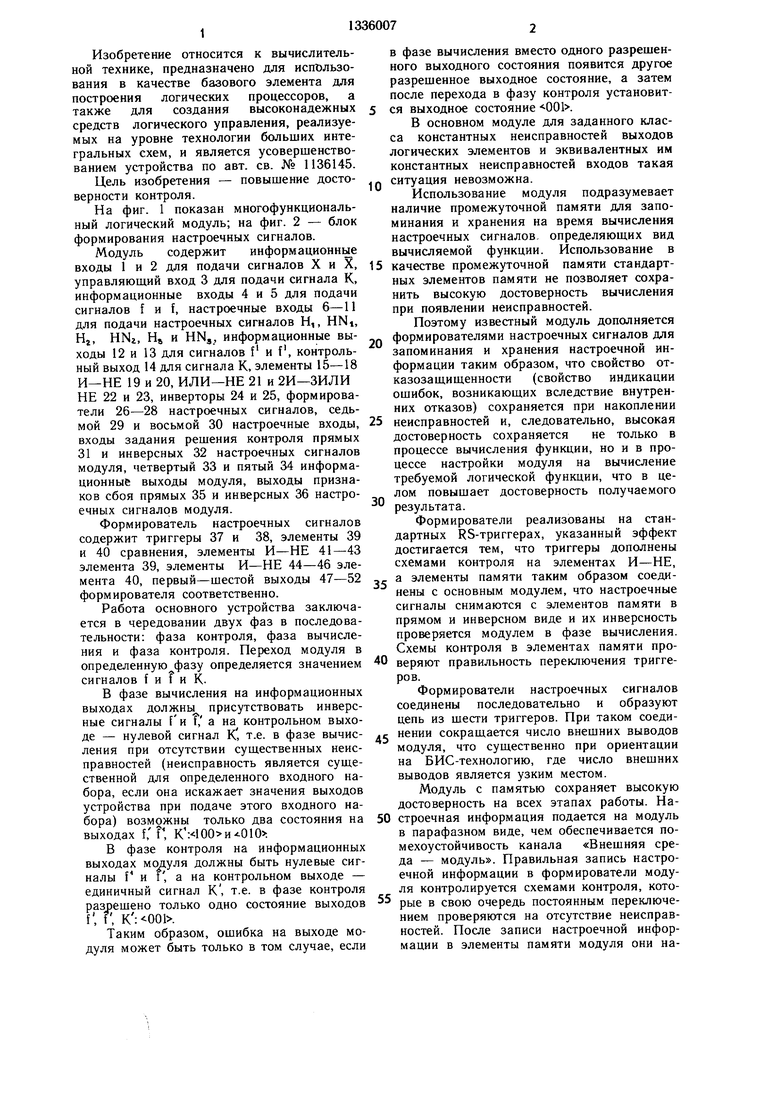

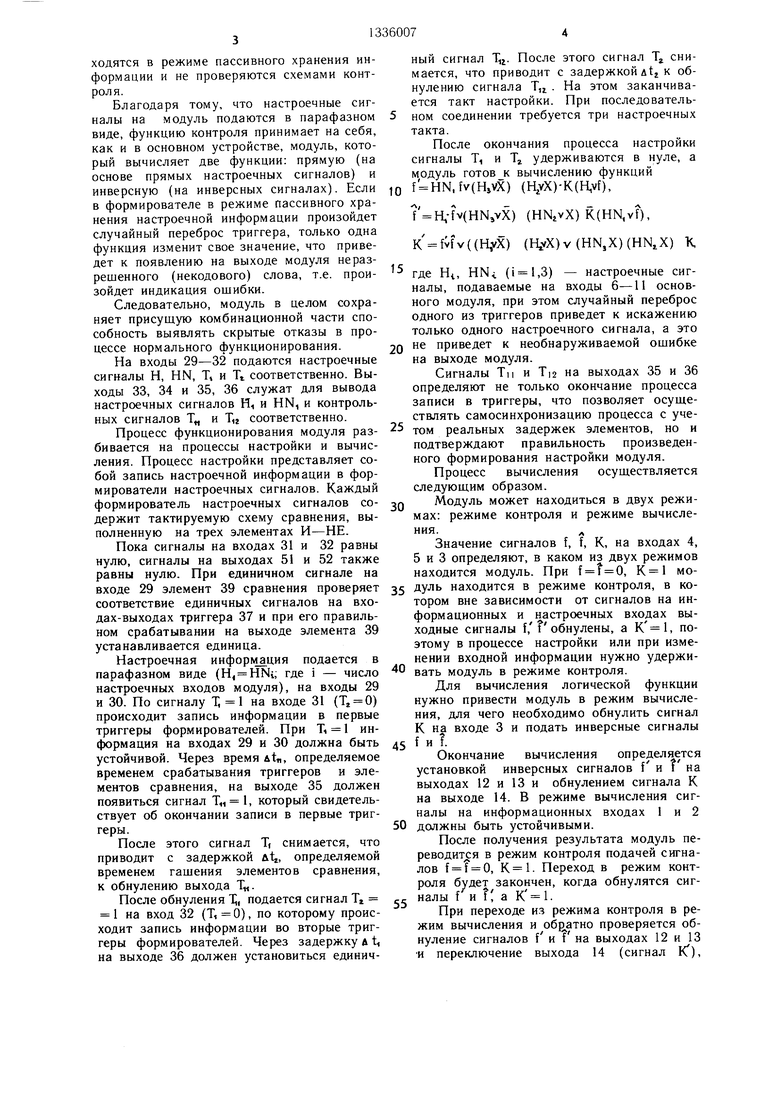

На фиг. 1 показан многофункциональный логический модуль; на фиг. 2 - блок формирования настроечных сигналов.

Модуль содержит информационные входы 1 и 2 для подачи сигналов X и X, управляюший вход 3 для подачи сигнала К, информационные входы 4 и 5 для подачи сигналов f и f, настроечные входы 6-11 для подачи настроечных сигналов Н,, HNi, Hj, HNz, Hj и HNj, информационные выходы 12 и 13 для сигналов f и f , контрольный выход 14 для сигнала К, элементы 15-18 И-НЕ 19 и 20, ИЛИ-НЕ 21 и 2И-ЗИЛИ НЕ 22 и 23, инверторы 24 и 25, формирователи 26-28 настроечных сигналов, седьмой 29 и восьмой 30 настроечные входы, входы задания решения контроля прямых 31 и инверсных 32 настроечных сигналов модуля, четвертый 33 и пятый 34 информационные выходы модуля, выходы признаков сбоя прямых 35 и инверсных 36 настроечных сигналов модуля.

Формирователь настроечных сигналов содержит триггеры 37 и 38, элементы 39 и 40 сравнения, элементы И-НЕ 41-43 элемента 39, элементы И-НЕ 44-46 элемента 40, первый-шестой выходы 47-52 формирователя соответственно.

Работа основного устройства заключается в чередовании двух фаз в последовательности: фаза контроля, фаза вычисления и фаза контроля. Переход модуля в определенную фазу определяется значением сигналов f и f и К.

В фазе вычисления на информационных выходах должнь присутствовать инверсные сигналы и Т, а на контрольном выходе - нулевой сигнал К, т.е. в фазе вычисления при отсутствии сушественных неисправностей (неисправность является существенной для определенного входного набора, если она искажает значения выходов устройства при подаче этого входного набора) возможны только два состояния на выходах

В фазе контроля на информационных выходах модуля должны быть нулевые сигналы f и f , а на контрольном выходе - единичный сигнал К , т.е. в фазе контроля разрешено только одно состояние выходов f , f, .

Таким образом, ошибка на выходе модуля может быть только в том случае, если

0

5

0

5

0

5

0

5

0

5

в фазе вычисления вместо одного разрешенного выходного состояния появится другое разрешенное выходное состояние, а затем после перехода в фазу контроля установится выходное состояние 001.

В основном модуле для заданного класса константных неисправностей выходов логических элементов и эквивалентных им константных неисправностей входов такая ситуация невозможна.

Использование модуля подразумевает наличие промежуточной памяти для запоминания и хранения на время вычисления настроечных сигналов, определяющих вид вычисляемой функции. Использование в качестве промежуточной памяти стандартных элементов памяти не позволяет сохранить высокую достоверность вычисления при появлении неисправностей.

Поэтому известный модуль дополняется формирователями настроечных сигналов для запоминания и хранения настроечной информации таким образом, что свойство от- казозащищенности (свойство индикации ошибок, возникаюш.их вследствие внутренних отказов) сохраняется при накоплении неисправностей и, следовательно, высокая достоверность сохраняется не только в процессе вычисления функции, но и в процессе настройки модуля на вычисление требуемой логической функции, что в целом повышает достоверность получаемого результата.

Формирователи реализованы на стандартных RS-триггерах, указанный эффект достигается тем, что триггеры дополнены схемами контроля на элементах И-НЕ, а элементы памяти таким образом соединены с основным модулем, что настроечные сигналы снимаются с элементов памяти в прямом и инверсном виде и их инверсность проверяется модулем в фазе вычисления. Схемы контроля в элементах памяти проверяют правильность переключения триггеров.

Формирователи настроечных сигналов соединены последовательно и образуют цепь из шести триггеров. При таком соединении сокращается число внешних выводов модуля, что существенно при ориентации на БИС-технологию, где число внешних выводов является узким местом.

Модуль с памятью сохраняет высокую достоверность на всех этапах работы. Настроечная информация подается иа модуль в парафазном виде, чем обеспечивается помехоустойчивость канала «Внешняя среда - модуль. Правильная запись настроечной информации в формирователи модуля контролируется схемами контроля, которые в свою очередь постоянным переключением проверяются на отсутствие неисправностей. После записи настроечной информации в элементы памяти модуля они находятся в режиме пассивного хранения информации и не проверяются схемами контроля.

Благодаря тому, что настроечные сигналы на модуль подаются в парафазном виде, функцию контроля принимает на себя, как и в основном устройстве, модуль, который вычисляет две функции: прямую (на основе прямых настроечных сигналов) и инверсную (на инверсных сигналах). Если в формирователе в режиме пассивного хранения настроечной информации произойдет случайный переброс триггера, только одна функция изменит свое значение, что приведет к появлению на выходе модуля неразрешенного (некодового) слова, т.е. произойдет индикация ошибки.

Следовательно, модуль в целом сохраняет присущую комбинационной части способность выявлять скрытые отказы в процессе нормального функционирования.

На входы 29-32 подаются настроечные сигналы Н, HN, Т, и Т соответственно. Выходы 33, 34 и 35, 36 служат для вывода настроечных сигналов Н, и HN, и контрольных сигналов Т„ и Т соответственно.

Процесс функционирования модуля разбивается на процессы настройки и вычисления. Процесс настройки представляет собой запись настроечной информации в формирователи настроечных сигналов. Каждый формирователь настроечных сигналов содержит тактируемую схему сравнения, выполненную на трех элементах И-НЕ.

Пока сигналы на входах 31 и 32 равны нулю, сигналы на выходах 51 и 52 также равны нулю. При единичном сигнале на входе 29 элемент 39 сравнения проверяет соответствие единичных сигналов на входах-выходах триггера 37 и при его правильном срабатывании на выходе элемента 39 устанавливается единица.

Настроечная ииформа ция подается в парафазном виде (H, HNi; где i - число настроечных входов модуля), на входы 29 и 30. По сигналу Т, 1 на входе 31 (Тг 0) происходит запись информации в первые триггеры формирователей. При Ti 1 информация на входах 29 и 30 должна быть устойчивой. Через время At, определяемое временем срабатывания триггеров и элементов сравнения, на выходе 35 должен появиться сигнал T,i l, который свидетельствует об окончании записи в первые триггеры.

После этого сигнал TI снимается, что приводит с задержкой ut, определяемой временем гашения элементов сравнения, к обнулению выхода Т„.

После обнуления 5, подается сигнал Т 1 на вход 32 (Т, 0), по которому происходит запись информации во вторые триггеры формирователей. Через задержку д t, на выходе 36 должен установиться единичный сигнал TIJ. После этого сигнал Т снимается, что приводит с задержкой Atj к обнулению сигнала Т, . На этом заканчивается такт настройки. При последовательном соединении требуется три настроечных такта.

После окончания процесса настройки сигналы Т, и Тг удерживаются в нуле, а модуль готов к вычислению функций

0 .fv(HjVX) (H,vX)-K(H,vf),

,-fv(HNjvX) (HNjvX) K(HN,v),

K fvfv((H,vX) (HirX)v(HN,X)() К

где HI, HNi (i l,3) - настроечные сигналы, подаваемые на входы 6-11 основного модуля, при этом случайный переброс одного из триггеров приведет к искажению только одного настроечного сигнала, а это

0 не приведет к необнаруживаемой ошибке на выходе модуля.

Сигналы Т|1 и Т|2 на выходах 35 и 36 определяют не только окончание процесса записи в триггеры, что позволяет осуществлять самосинхронизацию процесса с уче5 том реальных задержек элементов, но и подтверждают правильность произведенного формирования настройки модуля.

Процесс вычисления осуществляется следующим образом.

0 Модуль может находиться в двух режимах: режиме контроля и режиме вычисления.

Значение сигналов f, f. К, на входах 4, 5 и 3 определяют, в каком из двух режимов находится модуль. При f , К 1 мо5 дуль находится в режиме контроля, в котором вне зависимости от сигналов на информационных и настроечных входах выходные сигналы , обнулены, а , поэтому в процессе настройки или при изменении входной информации нужно удерживать модуль в режиме контроля.

Для вычисления логической функции нужно привести модуль в режим вычисления, для чего необходимо обнулить сигнал К на входе 3 и подать инверсные сигналы

5 и 1Окончание вычисления определяется

установкой инверсных сигналов f и на выходах 12 и 13 и обнулением сигнала К на выходе 14. В режиме вычисления сигналы на информационных входах 1 и 2 0 должны быть устойчивыми.

После получения результата модуль пе- peвoдитJCя в режим контроля подачей сигналов , . Переход в режим конт0

5

роля будет закончен, когда обнулятся сигналы f и а К 1.

При переходе из режима контроля в режим вычисления и обдатно проверяется обнуление сигналов f и Т на выходах 12 и 13 и переключение выхода 14 (сигнал iC),

при этом обязательно обнаруживается одна из двух возможных константных неисправностей на выходе каждого элемента в модуле, а именно та, которая могла бы привести к появлению неверного единичного сигнала на одном их выходов. Тем самым возможное накопление неисправностей в модуле ограничивается так, что не может привести к ошибке на его выходах, напри- Meg не может быть комбинации сигналов f , f , к , равной 100 вместо 010.

Формула изобретения

1. Многофункциональный логический модуль по авт. св. № 1136145, отличающийся тем, что, с целью повышения достоверности контроля, модуль содержит три формирователя настроечных сигналов, причем седьмой настроечный вход модуля соединен с входом установки первого формирователя настроечных сигналов, вход сброса которого соединен с восьмым настроечным входом модуля, вход задания режима контроля прямых настроечных сигналов которого соединен с первым синхровходом первого формирователя настроечных сигналов, первый и второй выходы которого подключены к первому и третьему настроечным входам модуля, третий и четвертый выходы первого формирователя настроечных сигналов соединены с входами установки и сброса второго формирователя настроечных сигналов соответственно, пятый и шестой выходы первого формирователя настроечных сигналов соединены с первым и вторым синхро- входами второго формирователя настроечных сигналов, первый и второй выходы которого подключены к второму . и четвертому настроечным входам модуля, вход задания режима контроля инверсных настроечных сигналов которого соединен с вторым синхровходом первого формирователя настроечных сигналов, третий, четвертый, пятый и шестой выходы второго формирователя настроечных сигналов соединены с

входами установки сброса, первым и вторым входами синхронизации третьего формирователя настроечных сигналов соответственно, первый и второй выходы третьего формирователя настроечных сигналов подключены к пятому и шестому настроечным входам модуля, третий и четвертый информационные выходы которого соединены с третьим и четвертым выходами третьего

формирователя настроечных сигналов, пятый и шестой выходы которого являются входами признаков сбоя прямых настроечных сигналов и инверсных настроечных сигналов модуля соответственно.

2. Модуль по п. 1, отличающийся тем,

5 что формирователь настроечных сигналов содержит два триггера и два элемента сравнения, причем вход установки первого триггера соединен с входом установки формирователя и с первым входом первого элемента сравнения, вход сброса первого триггера соединен с входом сброса формирователя и с вторым входом первого элемента сравнения, первый и второй синхровходы формирователя соединены с синхровхода- ми первого и второго элементов сравнения

5 соответственно, прямой выход первого триггера соединен с входом установки второго триггера, с третьим входом первого элемента сравнения и с первым входом второго элемента сравнения, инверсный выход первого триггера соединен с входом сброса

0 второго триггера, с четвертым входом первого элемента сравнения и с вторым входом второго элемента сравнения и является первым выходом формирователя, второй выход которого соединен с прямым выходом второго триггера, с третьим входом второго элемента сравнения и с третьим выходом модуля, четвертый выход которого соединен с инверсным выходом второго триггера и с четвертым входом второго элемента сравнения, выходы первого и второго

0 элементов сравнения соединены с пятым и шестым выходами формирователя.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1336008A2 |

| Многофункциональный логический модуль | 1983 |

|

SU1136145A1 |

| Устройство для контроля параметров | 1989 |

|

SU1735871A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство буферной памяти | 1987 |

|

SU1494010A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для диагностики неисправностей многоярусных пирамидальных схем | 1980 |

|

SU980084A1 |

Изобретение относится к области автоматики и вычислительной техники и предназначено для использования в качестве базового элемента для построения логических процессоров, а также для создания высоконадежных средств логического управления, реализуемых на уровне технологии БИС. Цель изобретения - повышение достоверности контроля. Модуль дополнительно содержит три формирователя настроечных сигналов, соединенных последовательно. Каждый формирователь содержит два триггера, соединенных так, что прямой и инверсный выходы одного служат для включения другого по входам установки и сброса соответственно. В модуле получаются включенными шесть триггеров. Сигналы с входов и выходов каждого триггера приходят на элемент сравнения, управляемый сигналами режимов контроля прямых и инверсных настроечных сигналов, снимаемых с выходов всех шести триггеров. 1 з.п. ф-лы, 2 ил. i (Л со 00 05

I. I .J

Фиг.2

Составитель A. Сиротская

Редактор П. ГерешиТехред И. ВересКорректор И. Муска

Заказ 3803/44Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Многофункциональный логический модуль | 1983 |

|

SU1136145A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1985-12-19—Подача