1

Изобретение относится к вычислительной технике, предназначено для использования в качестве базового элемента для построения логических процессоров, а также для создания высоконадежных средств логического управления, реализуемых на уровне технологии больших интегральных схем, и является усовершенствованием устройства по авт. св. № 1136145.

Цель изобретения - повышение достоверности контроля.

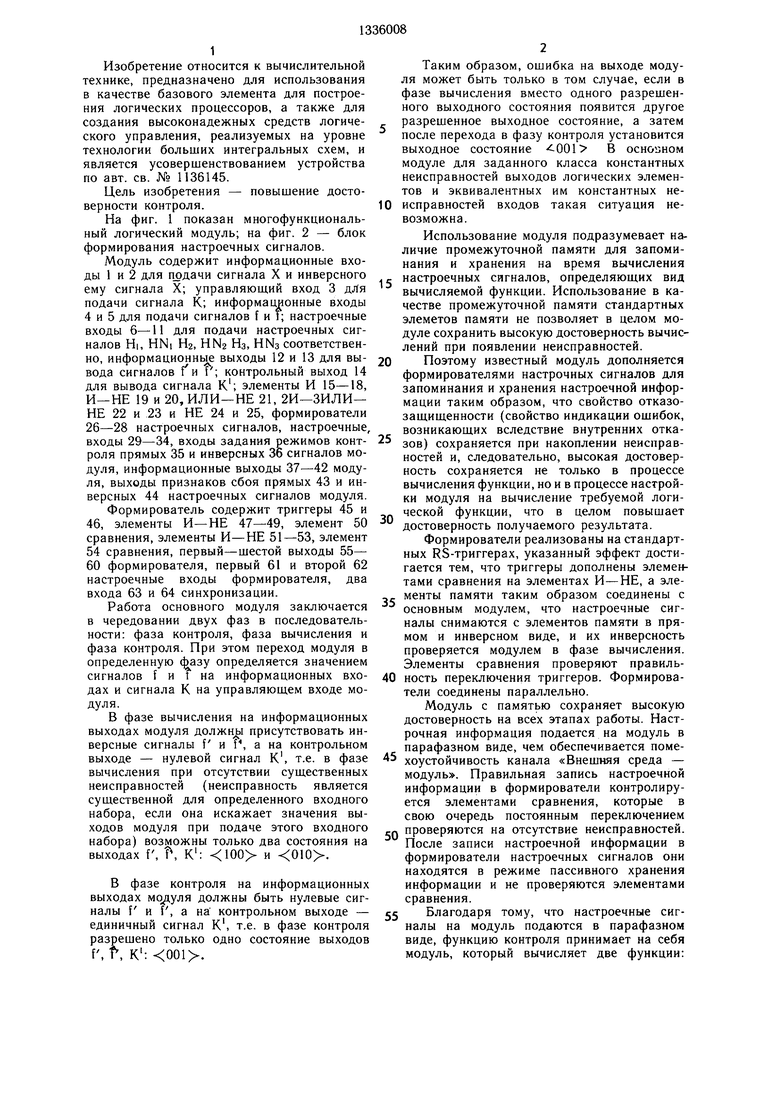

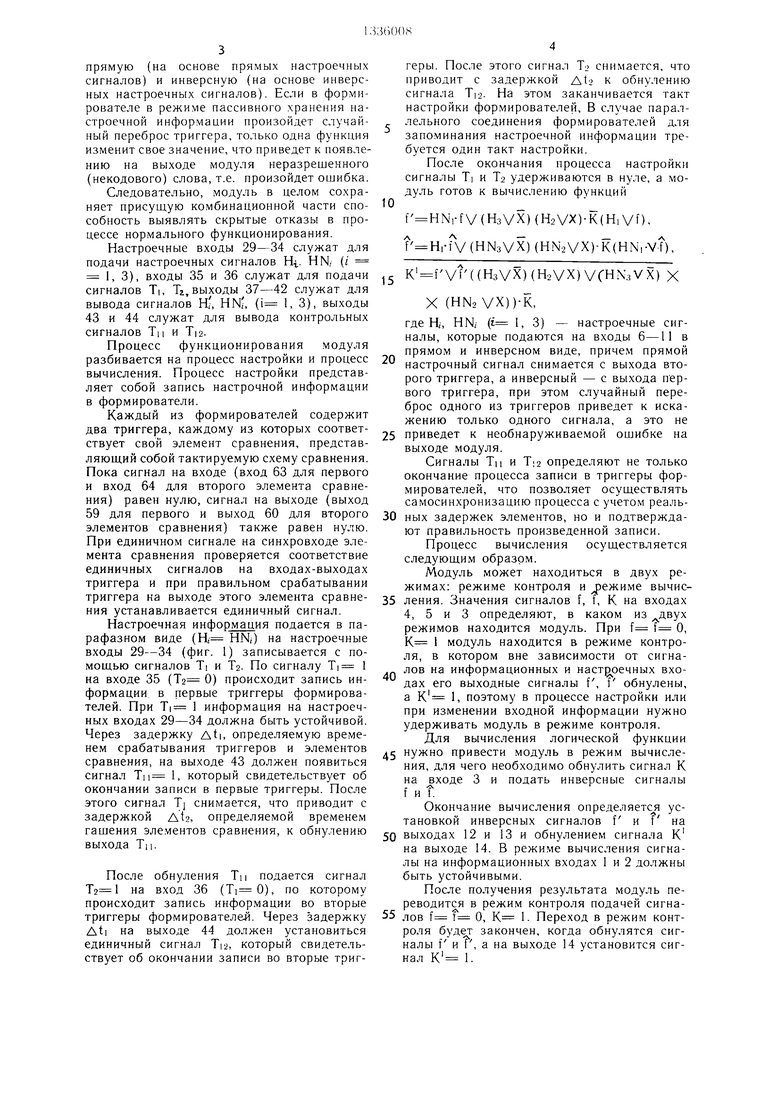

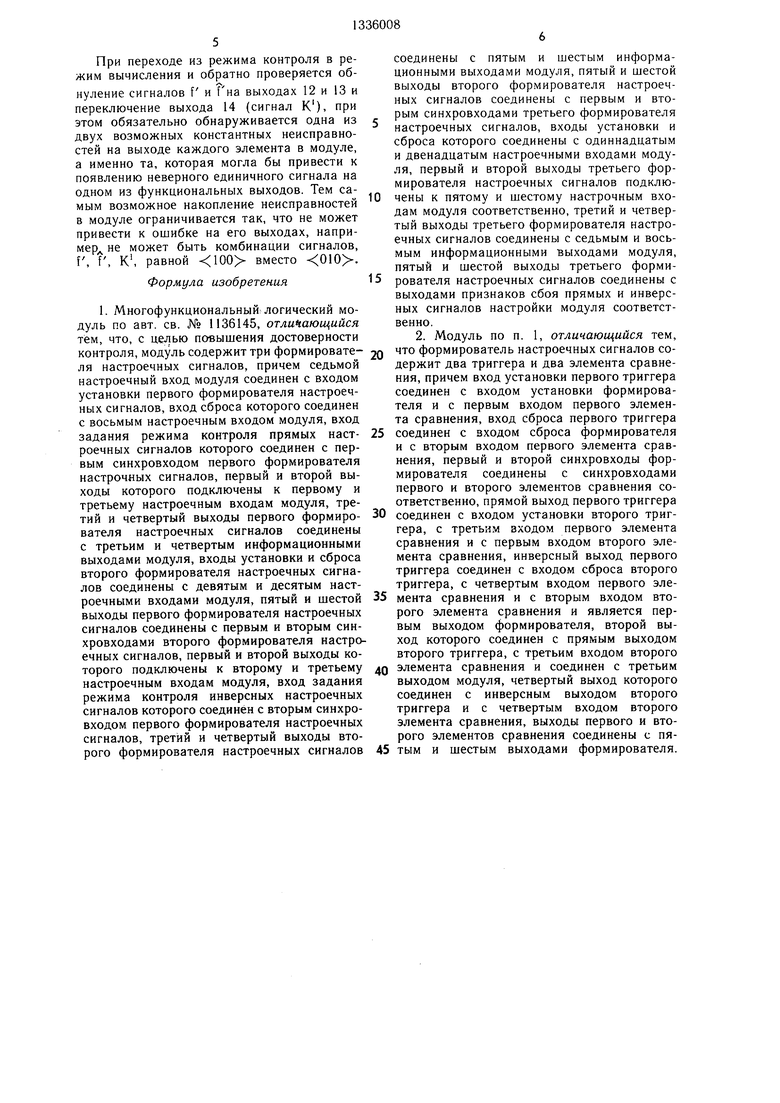

На фиг. 1 показан многофункциональный логический модуль; на фиг. 2 - блок формирования настроечных сигналов.

Модуль содержит информационные входы 1 и 2 для п рдачи сигнала X и инверсного ему сигнала X; управляюший вход 3 дЛя подачи сигнала К; информационные входы 4 и 5 для подачи сигналов f и Г; настроечные входы 6-И для подачи настроечных сигналов HI, HNi Н2, HNa Нз, НМз соответственно, информационнью выходы 12 и 13 для вывода сигналов и f; контрольный выход 14 для вывода сигнала К ; элементы И 15-18, И-НЕ 19 и 20, ИЛИ-НЕ 21, 2И-ЗИЛИ- НЕ 22 и 23 и НЕ 24 и 25, формирователи 26-28 настроечных сигналов, настроечные, входы 29-34, входы задания режимов конт- роля прямых 35 и инверсных 36 сигналов модуля, информационные выходы 37-42 модуля, выходы признаков сбоя прямых 43 и инверсных 44 настроечных сигналов модуля.

Формирователь содержит триггеры 45 и 46, элементы И-НЕ 47-49, элемент 50 сравнения, элементы И-НЕ 51-53, элемент 54 сравнения, первый-шестой выходы 55- 60 формирователя, первый 61 и второй 62 настроечные входы формирователя, два входа 63 и 64 синхронизации.

Работа основного модуля заключается в чередовании двух фаз в последовательности: фаза контроля, фаза вычисления и фаза контроля. При этом переход модуля в определенную фазу определяется значением сигналов f и Т на информационных входах и сигнала К на управляюшем входе модуля.

В фазе вычисления на информационных выходах модуля должн присутствовать инверсные сигналы f и f а на контрольном выходе - нулевой сигнал К , т.е. в фазе вычисления при отсутствии существенных неисправностей (неисправность является существенной для определенного входного набора, если она искажает значения выходов модуля при подаче этого входного набора) возможны только два состояния на выходах f. Т, К : (100 и 010.

В фазе контроля на информационных выходах модуля должны быть нулевые сигналы f и Г, а на контрольном выходе - единичный сигнал К , т.е. в фазе контроля разрешено только одно состояние выходов f. Г, К : 001.

5

0

0

5

5

5

0

5

0

0

Таким образом, ошибка на выходе модуля может быть только в том случае, если в фазе вычисления вместо одного разрешенного выходного состояния появится другое разрешенное выходное состояние, а затем после перехода в фазу контроля установится выходное состояние i.001 В модуле для заданного класса константных неисправностей выходов логических элементов и эквивалентных им константных неисправностей входов такая ситуация невозможна.

Использование модуля подразумевает наличие промежуточной памяти для запоминания и хранения на время вычисления настроечных сигналов, определяющих вид вычисляемой функции. Использование в качестве промежуточной памяти стандартных элеметов памяти не позволяет в целом модуле сохранить высокую достоверность вычислений при появлении неисправностей.

Поэтому известный модуль дополняется формирователями настрочных сигналов для запоминания и хранения настроечной информации таким образом, что свойство отказо- защищенности (свойство индикации ошибок, возникающих вследствие внутренних отказов) сохраняется при накоплении неисправностей и, следовательно, высокая достоверность сохраняется не только в процессе вычисления функции, но и в процессе настройки модуля на вычисление требуемой логической функции, что в целом повышает достоверность получаемого результата.

Формирователи реализованы на стандартных RS-триггерах, указанный эффект достигается тем, что триггеры дополнены элементами сравнения на элементах И-НЕ, а элементы памяти таким образом соединены с основным модулем, что настроечные сигналы снимаются с элементов памяти в прямом и инверсном виде, и их инверсность проверяется модулем в фазе вычисления. Элементы сравнения проверяют правильность переключения триггеров. Формирователи соединены параллельно.

Модуль с памятью сохраняет высокую достоверность на всех этапах работы. Наст- рочная информация подается на модуль в парафазном виде, чем обеспечивается помехоустойчивость канала «Внешняя среда - модуль. Правильная запись настроечной информации в формирователи контролируется элементами сравнения, которые в свою очередь постоянным переключением проверяются на отсутствие неисправностей. После записи настроечной информации в формирователи настроечных сигналов они находятся в режиме пассивного хранения информации и не проверяются элементами сравнения.

Благодаря тому, что настроечные сигналы на модуль подаются в парафазном виде, функцию контроля принимает на себя модуль, который вычисляет две функции:

прямую (на основе прямых настроечных сигналов) и инверсную (на основе инверсных настроечных сигналов). Если в формирователе в режиме пассивного хранения настроечной информации произойдет случайный переброс триггера, только одна функция изменит свое значение, что приведет к появлению на выходе модуля неразрешенного (некодового) слова, т.е. произойдет ошибка.

Следовательно, модуль в целом сохраняет присушую комбинационной части способность выявлять скрытые отказы в процессе нормального функционирования.

Настроечные входы 29-34 служат для подачи настроечных сигналов Н. HN, (i 1, 3), входы 35 и 36 служат для подачи сигналов Т|, Тг, выходы 37-42 служат для вывода сигналов Н , HN , (i 1,3), выходы 43 и 44 служат для вывода контрольных сигналов Ти и Т|2.

Процесс функционирования модуля разбивается на процесс настройки и процесс вычисления. Процесс настройки представляет собой запись настрочной информации в формирователи.

Каждый из формирователей содержит два триггера, каждому из которых соответствует свой элемент сравнения, представляющий собой тактируемую схему сравнения. Пока сигнал на входе (вход 63 для первого и вход 64 для второго элемента сравнения) равен нулю, сигнал на выходе (выход 59 для первого и выход 60 для второго элементов сравнения) также равен нулю. При единичном сигнале на синхровходе элемента сравнения проверяется соответствие единичных сигналов на входах-выходах триггера и при правильном срабатывании триггера на выходе этого элемента сравнения устанавливается единичный сигнал.

Настроечная информация подается в па- рафазном виде (Н, HNj) на настроечные входы 29-34 (фиг. 1) записывается с по- мош,ью сигналов T| и По сигналу Ti 1 на входе 35 (Т2 0) происходит запись информации в первые триггеры формирователей. При Т| 1 информация на настроечных входах 29-34 должна быть устойчивой. Через задержку Ati, определяемую временем срабатывания триггеров и элементов сравнения, на выходе 43 должен появиться сигнал Т|1 1, который свидетельствует об окончании записи в первые триггеры. После этого сигнал Tj снимается, что приводит с задержкой At2, определяемой временем гашения элементов сравнения, к обнулению выхода Тп.

После обнуления Тп подается сигнал Т2 1 на вход 36 (), по которому происходит запись информации во вторые триггеры формирователей. Через задержку Ati на выходе 44 должен установиться единичный сигнал Tia, который свидетельствует об окончании записи во вторые триг0

геры. После этого сигнал То снимается, что приводит с задержкой At к обнулению сигнала Т|2. На этом заканчивается такт настройки формирователей, В случае параллельного соединения формирователей для запоминания настроечной информации требуется один такт настройки.

После окончания процесса настройки сигналы Т| и Т2 удерживаются в нуле, а модуль готов к вычислению функций

0

,-fV(H3VX)(H2VX)-K(H,Vf), t H|-rV(HN3VX)(HN2VX)-K(HNrV-n, K f vt ((H3VX)(H2VX)VCHN3VX) X

X (HN2 VX))-K,

где Н, HN; (t 1, 3) - настроечные сигналы, которые подаются на входы 6-11 в прямом и инверсном виде, причем прямой настрочный сигнал снимается с выхода второго триггера, а инверсный - с выхода п ер- вого триггера, при этом случайный переброс одного из триггеров приведет к искажению только одного сигнала, а это не

5 приведет к необнаруживаемой ошибке на выходе модуля.

Сигналы Ти и Ti2 определяют не только окончание процесса записи в триггеры формирователей, что позволяет осуществлять самосинхронизацию процесса с учетом реаль0 ных задержек элементов, но и подтверждают правильность произведенной записи.

Процесс вычисления осуществляется следующим образом.

Модуль может находиться в двух режимах: режиме контроля и д)ежиме вычис5 ления. Значения сигналов f, f, К на входах 4, 5 и 3 определяют, в каком из двух режимов находится модуль. При f f О, К 1 модуль находится в режиме контроля, в котором вне зависимости от сигна лов на информационных и настроечных входах его выходные сигналы f, f обнулены, а К 1, поэтому в процессе настройки или при изменении входной информации нужно удерживать модуль в режиме контроля. Для вычисления логической функции

5 нужно привести модуль в режим вычисления, чего необходимо обнулить сигнал К на входе 3 и подать инверсные сигналы f и Г.

Окончание вычисления определяетс я установкой инверсных сигналов f и f на

0 выходах 12 и 13 и обнулением сигнала К на выходе 14. В режи.ме вычисления сигналы на информационных входах 1 и 2 должны быть устойчивыми.

После получения результата модуль переводится в режим контроля подачей сигна5 лов f f О, К 1. Переход в режим контроля будет закончен, когда обнулятся сигналы f и f, а на выходе 14 установится сигнал К 1.

При переходе из режима контроля в режим вычисления и обратно проверяется обнуление сигналов f и Гна выходах 12 и 13 и переключение выхода 14 (сигнал К ), при этом обязательно обнаруживается одна из двух возможных константных неисправностей на выходе каждого элемента в модуле, а именно та, которая могла бы привести к появлению неверного единичного сигнала на одном из функциональных выходов. Тем самым возможное накопление неисправностей в модуле ограничивается так, что не может привести к ошибке на его выходах, например не может быть комбинации сигналов, f, f. К , равной 100 вместо 010.

Формула изобретения

1. Многофункциональный; логический модуль по авт. св. № 1136145, отличающийся тем, что, с целью повышения достоверности контроля, модуль содержит три формировате- ля настроечных сигналов, причем седьмой настроечный вход модуля соединен с входом установки первого формирователя настроечных сигналов, вход сброса которого соединен с восьмым настроечным входом модуля, вход задания режима контроля прямых наст- роечных сигналов которого соединен с первым синхровходом первого формирователя настрочных сигналов, первый и второй выходы которого подключены к первому и третьему настроечным входам модуля, третий и четвертый выходы первого формиро- вателя настроечных сигналов соединены с третьим и четвертым информационными выходами модуля, входы установки и сброса второго формирователя настроечных сигналов соединены с девятым и десятым настроечными входами модуля, пятый и шестой выходы первого формирователя настроечных сигналов соединены с первым и вторым син- хровходами второго формирователя настроечных сигналов, первый и второй выходы которого подключены к второму и третьему настроечным входам модуля, вход задания режима контроля инверсных настроечных сигналов которого соединен с вторым синхровходом первого формирователя настроечных сигналов, третий и четвертый выходы второго формирователя настроечных сигналов

0

5

о 5 0 5 Q 5

соединены с пятым и шестым информационными выходами модуля, пятый и шестой выходы второго формирователя настроечных сигналов соединены с первым и вторым синхровходами третьего формирователя настроечных сигналов, входы установки и сброса которого соединены с одиннадцатым и двенадцатым настроечными входами модуля, первый и второй выходы третьего формирователя настроечных сигналов подключены к пятому и шестому настрочным входам модуля соответственно, третий и четвертый выходы третьего формирователя настроечных сигналов соединены с седьмым и восьмым информационными выходами модуля, пятый и шестой выходы третьего формирователя настроечных сигналов соединены с выходами признаков сбоя прямых и инверсных сигналов настройки модуля соответственно.

2. Модуль по п. 1, отличающийся тем, что формирователь настроечных сигналов содержит два триггера и два элемента сравнения, причем вход установки первого триггера соединен с входом установки формирователя и с первым входом первого элемента сравнения, вход сброса первого триггера соединен с входом сброса формирователя и с вторым входом первого элемента сравнения, первый и второй синхровходы формирователя соединены с синхровходами первого и второго элементов сравнения соответственно, прямой выход первого триггера соединен с входом установки второго триггера, с третьим входом первого элемента сравнения и с первым входом второго элемента сравнения, инверсный выход первого триггера соединен с входом сброса второго триггера, с четвертым входом первого элемента сравнения и с вторым входом второго элемента сравнения и является первым выходом формирователя, второй выход которого соединен с прямым выходом второго триггера, с третьим входом второго элемента сравнения и соединен с третьим выходом модуля, четвертый выход которого соединен с инверсным выходом второго триггера и с четвертым входом второго элемента сравнения, выходы первого и второго элементов сравнения соединены с пятым и шестым выходами формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1336007A2 |

| Устройство для контроля логических блоков | 1983 |

|

SU1142837A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1136145A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1401462A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N X N)-МАТРИЦЫ | 1992 |

|

RU2012050C1 |

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1987 |

|

SU1425678A1 |

Изобретение относится к области автоматики и вычислительной техники и предназначено для использования в качестве базового элемента для построения логических процессоров, а также для создания высоконадежных средств логического управления, реализуемых на уровне технологии БИС, и является усовершенствованием модуля по а.с. № 1136145 (второе дополнительное а.с.) Цель изобретения - повышение достоверности контроля. Модуль дополнительно содержит три формирователя настрочных сигналов, соединенных параллельно. В каждый формирователь входят два триггера и две схемы сравнения. После вычисления модуль переводится в режим контроля. При этом происходит проверка прямых и инверсных настроечных сигналов модуля, а также контролируется каждый элемент в модуле так, что оказывается возможным избежать накопления ошибок в модуле. 1 з. п. ф-лы. 2 ил. СП оо оо О5

| Многофункциональный логический модуль | 1983 |

|

SU1136145A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1985-12-19—Подача