ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выдачи информации | 1991 |

|

SU1820389A1 |

| Устройство вывода информации | 1991 |

|

SU1807492A1 |

| Устройство для ввода информации | 1991 |

|

SU1798789A1 |

| Устройство для управления обменом информации | 1990 |

|

SU1721609A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

| Устройство для подключения источников информации к общей магистрали | 1986 |

|

SU1444797A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для передачи сигналов в однонаправленной кольцевой магистрали | 1981 |

|

SU995354A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1464167A1 |

| Многопроцессорная система | 1987 |

|

SU1494005A1 |

Использование: область вычислительной техники в устройствах вывода информации из запоминающих устройств к абонентам, применение в каналах связи ЭВМ с абонентами. Сущность: устройство содержит 3 триггера (1, 2, 3), 2 регистра (4, 5), 5 элементов И (9, 10, 11, 12, 13), 3 элемента ИЛИ (6, 7,8). 7-1-9-2-3-8-12- 3-10-11-4-5, 2-6-1,2-9, 2-13-5. 2 ил.

Фиг./

00

о

со ю

VJ

Изобретение относится к области вычислительной техники, в частности к устройствам вывода информации из ЗУ к абонентам, и может быть использовано в каналах связи ЭВМ с абонентами.

Целью изобретения является увеличение быстродействия устройства за счет уменьшения допустимого периода следования запросов абонента до величины 2ТСи.

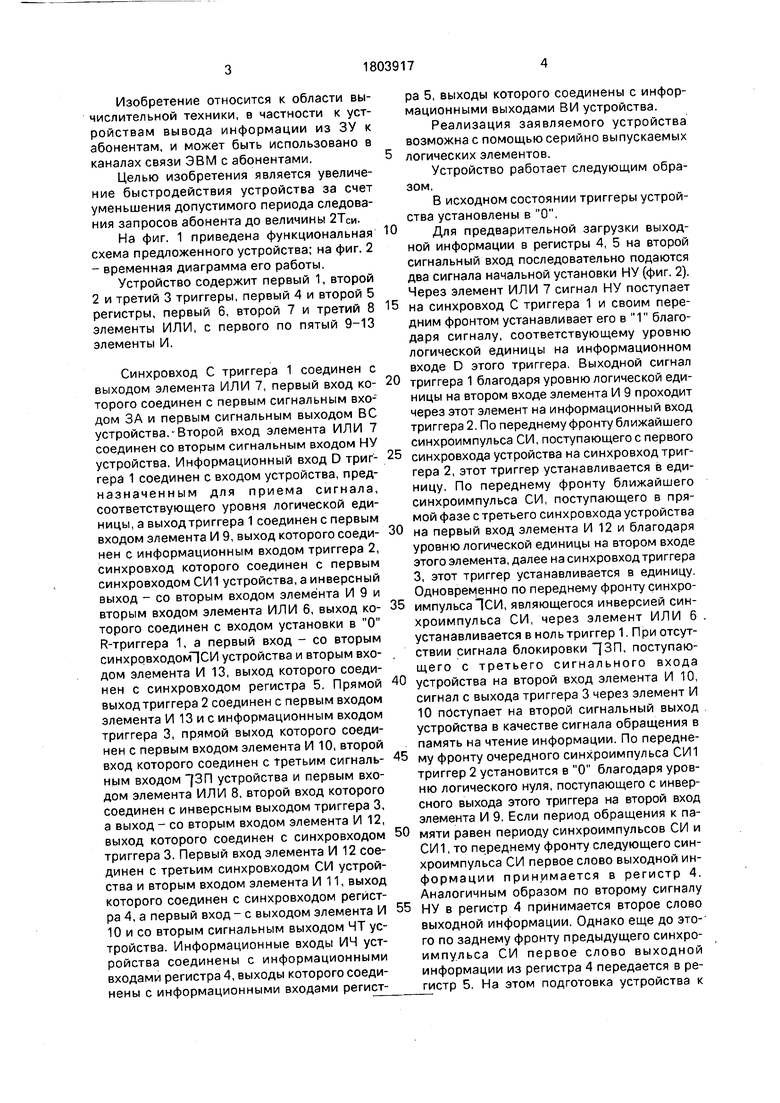

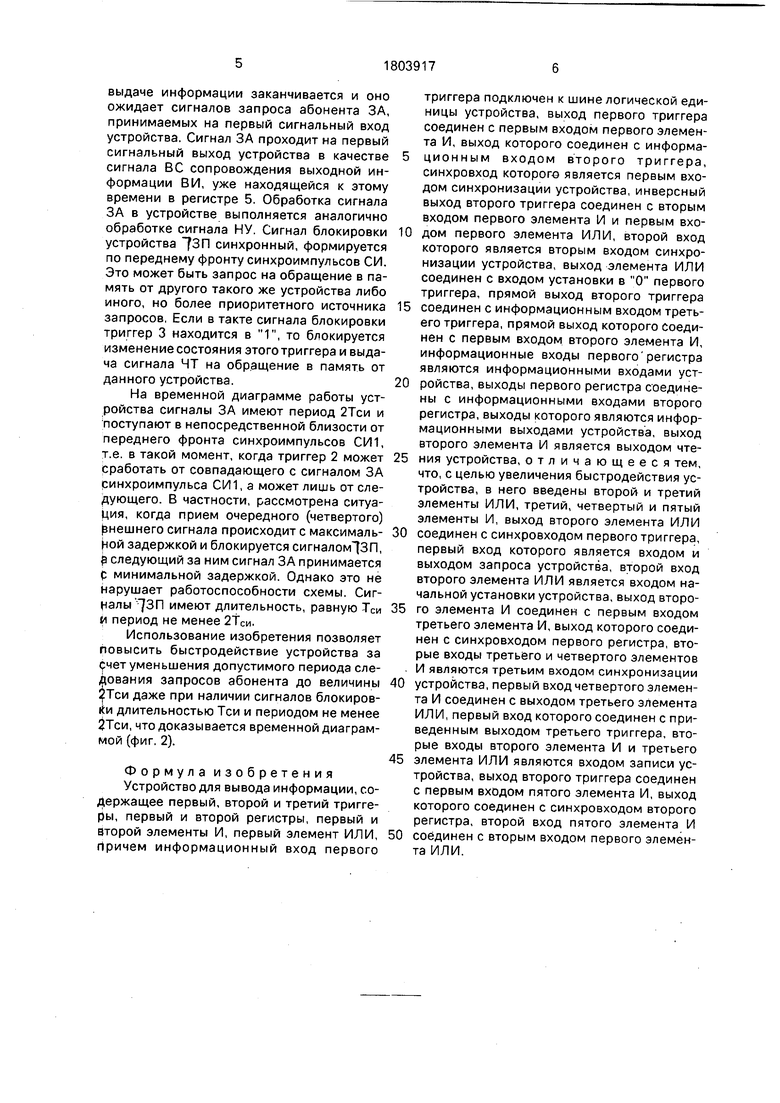

На фиг. 1 приведена функциональная схема предложенного устройства; на фиг. 2 - временная диаграмма его работы,

Устройство содержит первый 1, второй 2 и третий 3 триггеры, первый 4 и второй 5 регистры, первый 6, второй 7 и третий 8 элементы ИЛИ, с первого по пятый 9-13 элементы И.

Синхровход С триггера 1 соединен с выходом элемента ИЛИ 7, первый вход ко- торого соединен с первым сигнальным входом ЗА и первым сигнальным выходом ВС устройства.-Второй вход элемента ИЛИ 7 соединен со вторым сигнальным входом НУ устройства. Информационный вход D триг- гера 1 соединен с входом устройства, предназначенным для приема сигнала, соответствующего уровня логической единицы, а выход триггера 1 соединен с первым входом элемента И 9, выход которого соеди- нен с информационным входом триггера 2, синхровход которого соединен с первым синхровходом СИ1 устройства, а инверсный выход - со вторым входом элемента И 9 и вторым входом элемента ИЛИ 6, выход ко- торого соединен с входом установки в О R-триггера 1, а первый вход - со вторым синхровходом СИ устройства и вторым входом элемента И 13, выход которого соединен с синхровходом регистра 5. Прямой выход триггера 2 соединен с первым входом элемента И 13 и с информационным входом триггера 3, прямой выход которого соединен с первым входом элемента И 10, второй вход которого соединен с третьим сигналь- ным входом |ЗП устройства и первым входом элемента ИЛИ 8, второй вход которого соединен с инверсным выходом триггера 3, а выход - со вторым входом элемента И 12, выход которого соединен с синхровходом триггера 3. Первый вход элемента И 12 соединен с третьим синхровходом СИ устройства и вторым входом элемента И 11, выход которого соединен с синхровходом регистра 4, а первый вход - с выходом элемента И 10 и со вторым сигнальным выходом ЧТ устройства. Информационные входы ИЧ устройства соединены с информационными входами регистра 4, выходы которого соединены с информационными входами регистра 5, выходы которого соединены с информационными выходами ВИ устройства.

Реализация заявляемого устройства возможна с помощью серийно выпускаемых логических элементов.

Устройство работает следующим образом.

В исходном состоянии триггеры устройства установлены в О.

Для предварительной загрузки выходной информации в регистры 4, 5 на второй сигнальный вход последовательно подаются два сигнала начальной установки НУ (фиг. 2). Через элемент ИЛИ 7 сигнал НУ поступает на синхровход С триггера 1 и своим передним фронтом устанавливает его в 1 благодаря сигналу, соответствующему уровню логической единицы на информационном входе D этого триггера. Выходной сигнал триггера 1 благодаря уровню логической единицы на втором входе элемента И 9 проходит через этот элемент на информационный вход триггера 2. По переднему фронту ближайшего синхроимпульса СИ, поступающего с первого синхровхода устройства на синхровход триггера 2, этот триггер устанавливается в единицу. По переднему фронту ближайшего синхроимпульса СИ, поступающего в прямой фазе с третьего синхровхода устройства на первый вход элемента И 12 и благодаря уровню логической единицы на втором входе этого элемента, далее на синхровход триггера 3, этот триггер устанавливается в единицу. Одновременно по переднему фронту синхроимпульса 1СИ, являющегося инверсией синхроимпульса СИ, через элемент ИЛИ 6 устанавливается в ноль триггер 1. При отсутствии сигнала блокировки |ЗП, поступающего с третьего сигнального входа устройства на второй вход элемента И 10, сигнал с выхода триггера 3 через элемент И 10 поступает на второй сигнальный выход устройства в качестве сигнала обращения в память на чтение информации. По переднему фронту очередного синхроимпульса СИ1 триггер 2 установится в О благодаря уровню логического нуля, поступающего с инверсного выхода этого триггера на второй вход элемента И 9. Если период обращения к памяти равен периоду синхроимпульсов СИ и СИ1, то переднему фронту следующего синхроимпульса СИ первое слово выходной информации принимается в регистр 4. Аналогичным образом по второму сигналу НУ в регистр 4 принимается второе слово выходной информации. Однако еще до это- го по заднему фронту предыдущего синхроимпульса СИ первое слово выходной информации из регистра 4 передается в регистр 5. На этом подготовка устройства к

выдаче информации заканчивается и оно ожидает сигналов запроса абонента ЗА, принимаемых на первый сигнальный вход устройства. Сигнал ЗА проходит на первый сигнальный выход устройства в качестве сигнала ВС сопровождения выходной информации ВИ, уже находящейся к этому времени в регистре 5. Обработка сигнала ЗА в устройстве выполняется аналогично обработке сигнала НУ. Сигнал блокировки устройства 73П синхронный, формируется по переднему фронту синхроимпульсов СИ. Это может быть запрос на обращение в память от другого такого же устройства либо иного, но более приоритетного источника запросов, Если в такте сигнала блокировки триггер 3 находится в 1, то блокируется изменение состояния этого триггера и выдача сигнала ЧТ на обращение в память от данного устройства.

На временной диаграмме работы устройства сигналы ЗА имеют период 2Тси и поступают в непосредственной близости от переднего фронта синхроимпульсов СИ1, т.е. в такой момент, когда триггер 2 может сработать от совпадающего с сигналом ЗА синхроимпульса СИ1, а может лишь от следующего. В частности, рассмотрена ситуация, когда прием очередного (четвертого) рнешнего сигнала происходит с максимальной задержкой и блокируется сигналом ЗП, р следующий за ним сигнал ЗА принимается С минимальной задержкой. Однако это не нарушает работоспособности схемы. Сигналы 73П имеют длительность, равную ТСи И период не менее 2ТСи.

Использование изобретения позволяет повысить быстродействие устройства за ;:чет уменьшения допустимого периода следования запросов абонента до величины Тси даже при наличии сигналов блокиров- (Ы длительностью Тси и периодом не менее 2Тси, что доказывается временной диаграммой (фиг. 2).

Формула изобретения Устройство для вывода информации, содержащее первый, второй и третий триггеры, первый и второй регистры, первый и второй элементы И, первый элемент ИЛИ, причем информационный вход первого

триггера подключен к шине логической единицы устройства, выход первого триггера соединен с первым входом первого элемента И, выход которого соединен с информационным входом второго триггера, синхровход которого является первым входом синхронизации устройства, инверсный выход второго триггера соединен с вторым входом первого элемента И и первым входом первого элемента ИЛИ, второй вход которого является вторым входом синхронизации устройства, выход элемента ИЛИ соединен с входом установки в О первого триггера, прямой выход второго триггера

соединен с информационным входом третьего триггера, прямой выход которого Соединен с первым входом второго элемента И, информационные входы первого регистра являются информационными входами устройства, выходы первого регистра соединены с информационными входами второго регистра, выходы которого являются информационными выходами устройства, выход второго элемента И является выходом чтения устройства, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены второй и третий элементы ИЛИ, третий, четвертый и пятый элементы И, выход второго элемента ИЛИ

соединен с синхровходом первого триггера, первый вход которого является входом и выходом запроса устройства, второй вход второго элемента ИЛИ является входом начальной установки устройства, выход второго элемента И соединен с первым входом третьего элемента И, выход которого соединен с синхровходом первого регистра, вторые входы третьего и четвертого элементов И являются третьим входом синхронизации

устройства, первый вход четвертого элемента И соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с приведенным выходом третьего триггера, вторые входы второго элемента И и третьего

элемента ИЛИ являются входом записи устройства, выход второго триггера соединен с первым входом пятого элемента И, выход которого соединен с синхровходом второго регистра, второй вход пятого элемента И

соединен с вторым входом первого элемента ИЛИ.

| Авторское свидетельство СССР № 1554637, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1985 |

|

SU1310828A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-23—Публикация

1991-03-04—Подача