2, Устройство по П.1, отличающее с я тем, что блок управления содержит счетчик, семь триггеров, семь элементов И, два элемента ИЛИ, элемАнт НЕ, причем информацион- ньй вход счетчика является входом блока управления, нулевой вход первого триггера, первые входы первого, второго, третьего и четвертого эле- ментов И, синхровходы второго, третьего, четвертого, пятого и шестого триггеров образуют первую группу входов блока управления, первые входы пятого и шестого элементов И, первьш вход первого элемента 1ШИ, нулевой и единп чный входы седьмого триггера образуют вторую группу.входов блока управления, выход четвертого элемента И является первым выхбдом блока управления, выход четвертого триггера соединен с инс1)ормационным входом пятого триггера, вторым входом первого элемента ИЛИ, первым входом седьмого элемента И и является вторым выходом блока управления, выход седьмого элемента И является третьим выходом блока управления у выходы третьего и седьмого элементов И, счет- чика;четвертого триггера образуют первую группу выходов блока управления, выходы четвертого и седьмого триггеров образуют вторую группу выходов блока управления, при этом в блоке управления первый вход пятого элемента И соединен со счетным входо счетчика, вход записи которого соединен с выходом элемента НЕ, вход которого) соединен.с выходом второго элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И второй вход которого соединен с нуле вым выходом первого триггера, единичный выход, которого соединен с первым входом режима работы счетчика и вторым тзходом первого элемента И, выход которого соединен с вторым входом второго элемента 1ШИ, выход первого элемента ИЛИ Соединен с вторым входом второго элемента И, выход которого соединен с единичным входом первого триггера, второй вход режима работы счетчика соединен с выходом седьмого триггера, второй вход седьмого элемента И соединен с первьп .входом третьего элемента И, второй вход которого соединен с выходом шестого триггера,.информационньй вход которого соединен с выходом пятого

триггера, информационный вход четвертого триггера соединен с единичным выходом третьего триггера, нулевой выход которого соединен с вторым входом шестого элемента И, выход которого соединен с информационным входом второго триггера, выход которого соединен с информационным входом третьего триггера и вторым входом четвертого элемента И..

3. Устройство по п,1, о т л и- чающееся тем, что блок формирования запроса прерывания содер- йсит три триггера, пять элементов И, элемент ИЛИ, причем единичньй вход первого триггера и первьй вход элемента ИЛИ образуют группу входов ус- таповки блока формирования запроса прерывания, синхровход второго триг- гера и первьш вход первого элемента И образуют группу синхровходов блока формирования запроса прерывания, первый и второй входы второго элемента И образуют группу разрешающих входов блока формирования запроса прерывания, третий вход второго элемента И является запускающим входом блока формирования запроса прерывания, еди- ничный и нулевой выходы второго триггера образуют, группу выходов блока формирования запроса прерывания, выход третьего элемента И является выходом блока формирования запроса -прерывания, при этом ВТ блоке формирования запроса прерывания единичньй выход второго триггера соединен с вторым входом первого элемента И и пер- .вым входом четвертого элемента И, второй вход которого соединен с первым в:ходом первого элемента И, выход которого соединен с нулевым входом первого триггера, единичный выход которого соединен с первьм входом пятого элемента И, .второй вход которого соединен с синхровходом второго триггера, информационньй вход которо-. ..го соединен с выходом пятого э:темен- . та И, третий вход которого соединен с нулевым выходом третьего триггера, нулевой вход которого соединен с выхо- - дом второго элемента И, второй вход которого соединен с первьй входом . третьего элемента И, второй вход которого соединен с нулевым выходом первого триггера, выход четвертого элемента И соединен с вторым входом элемента ИЛИ,выход которого соединен с единичньм входом третьего триггера.

Изобретение относится к вычислительной технике, в частности к устройствам управления обменом данными, и может быть использовано для управления передачей данных в каналах ввода-вывода ЭВМ.

Цель изобретения - увеличение быстродействия при организации блочного обмена данными.

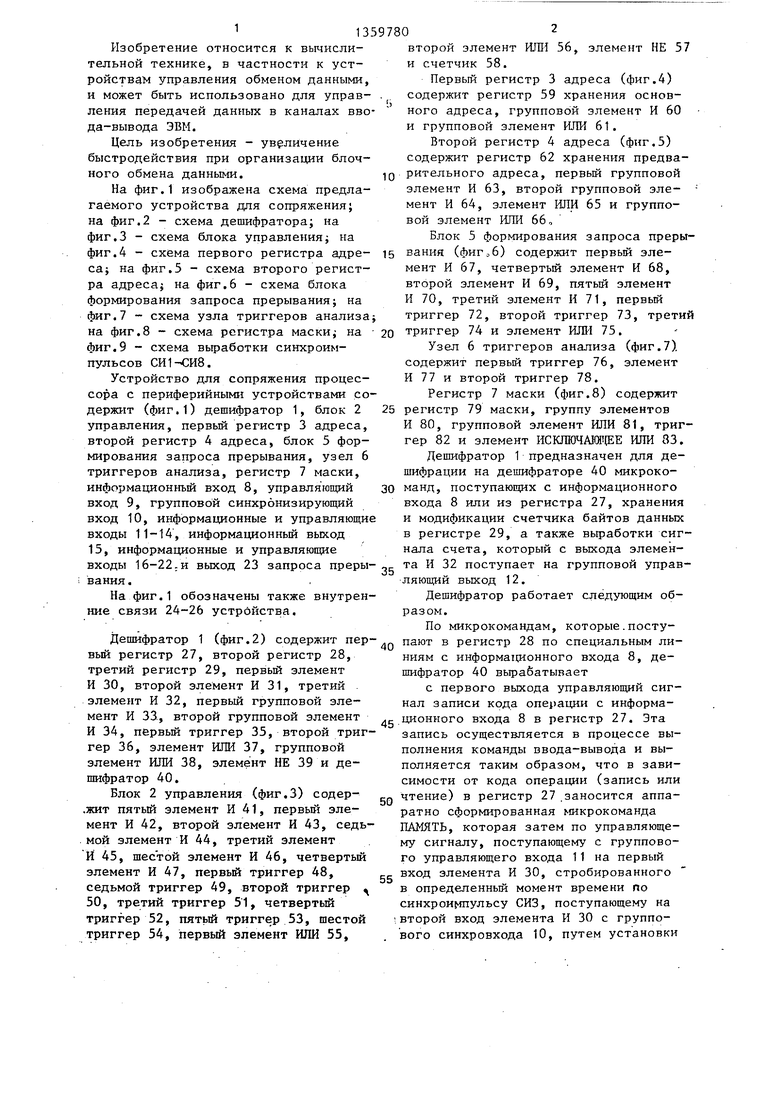

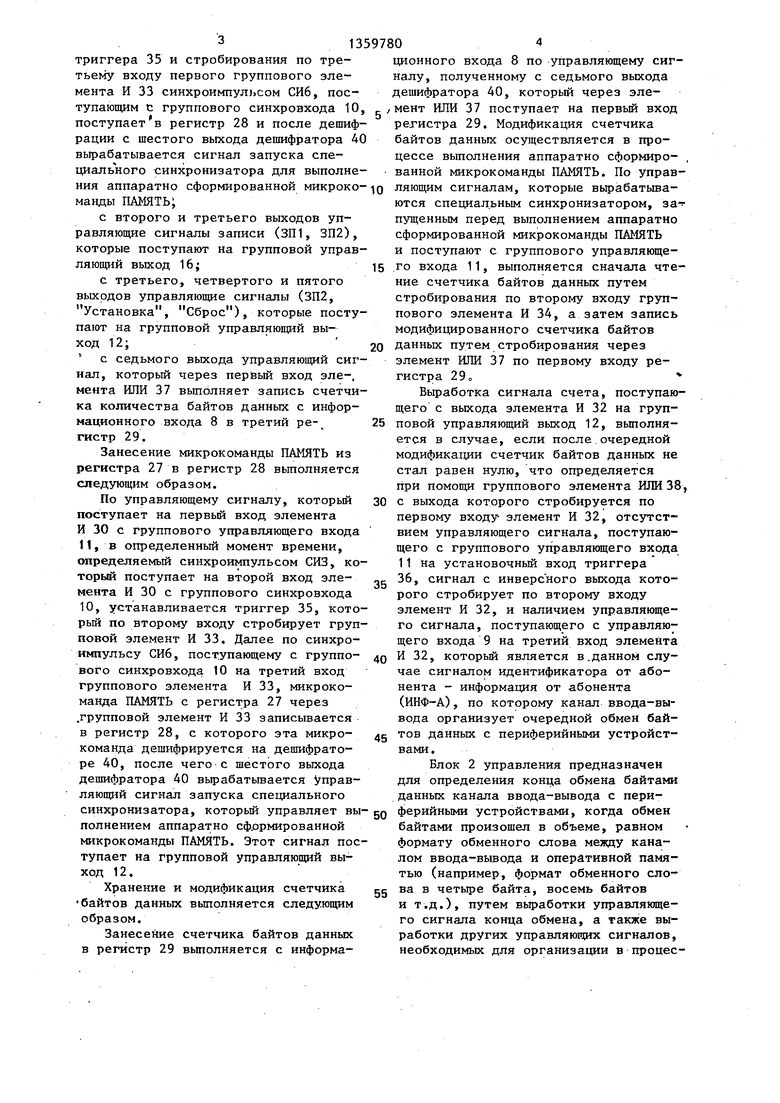

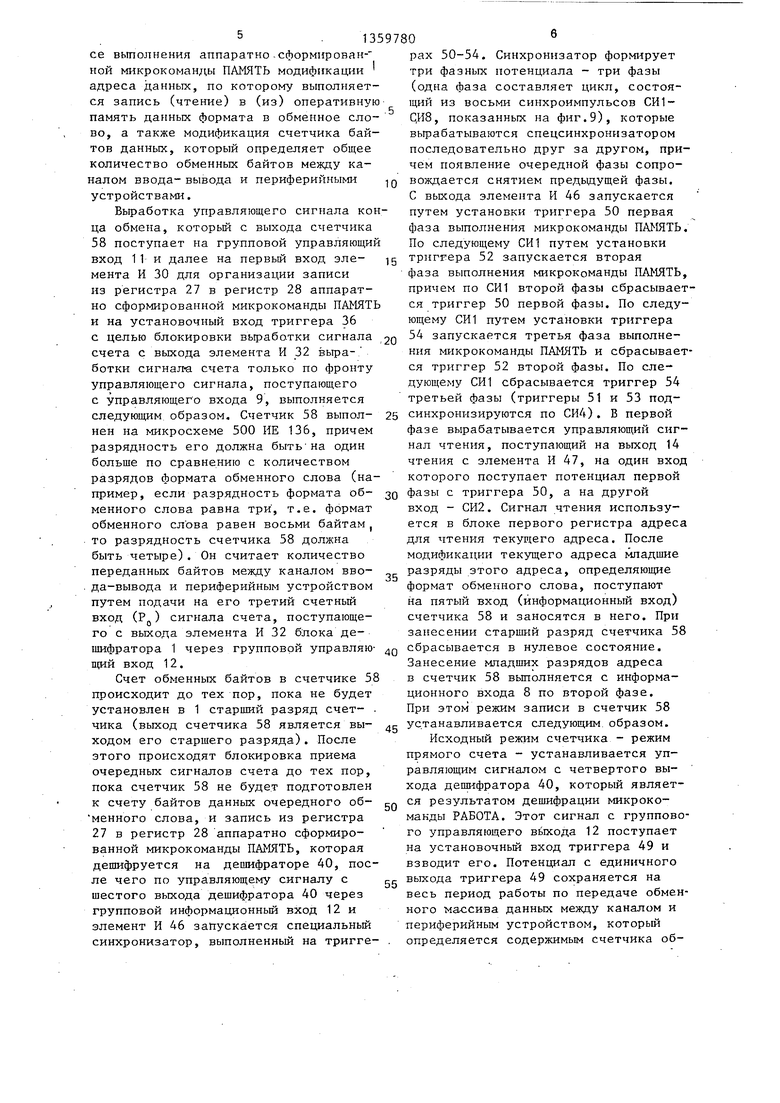

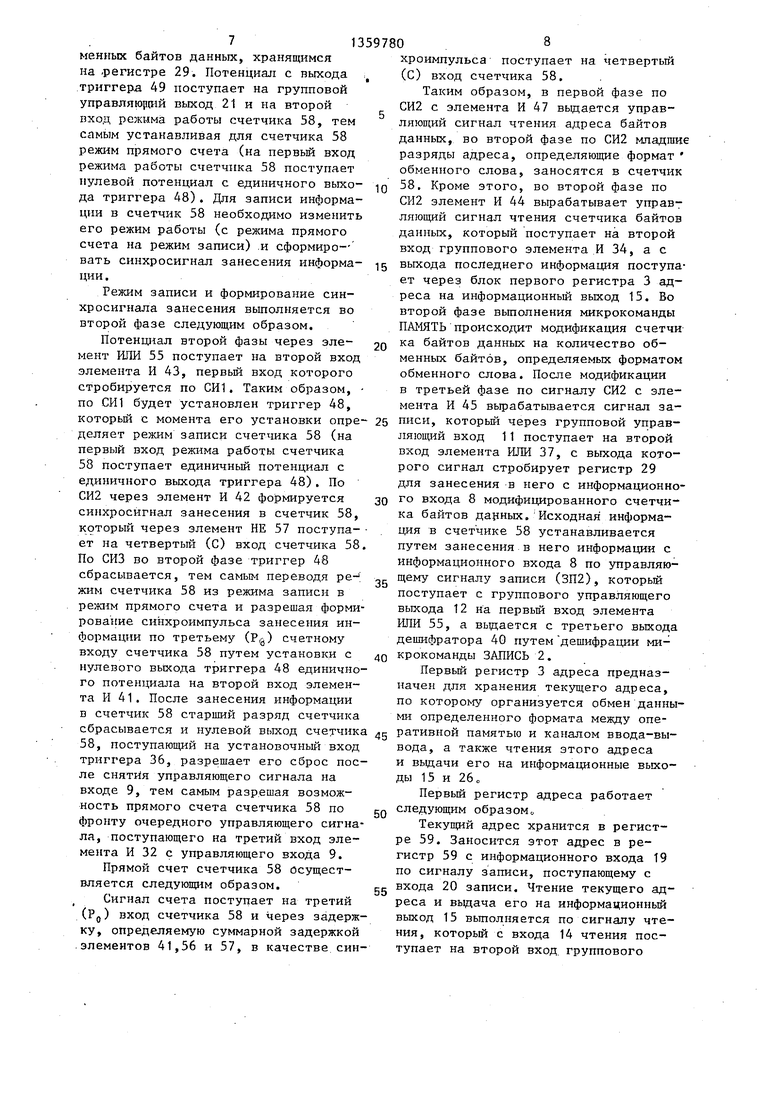

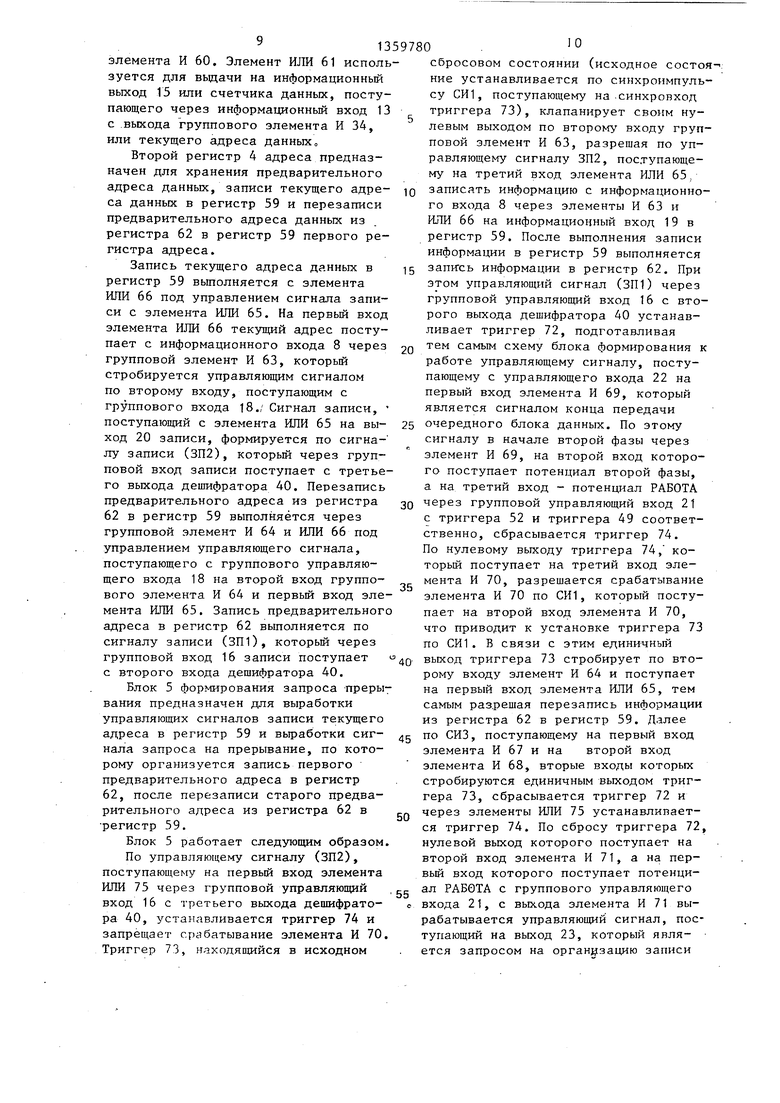

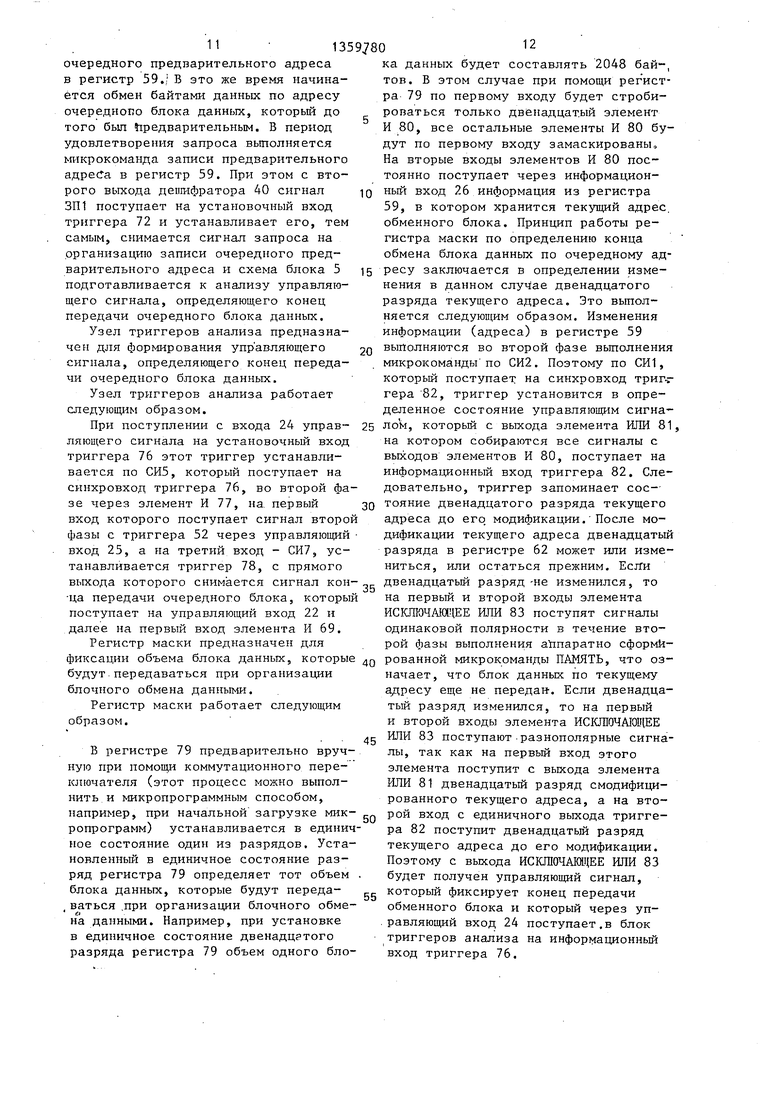

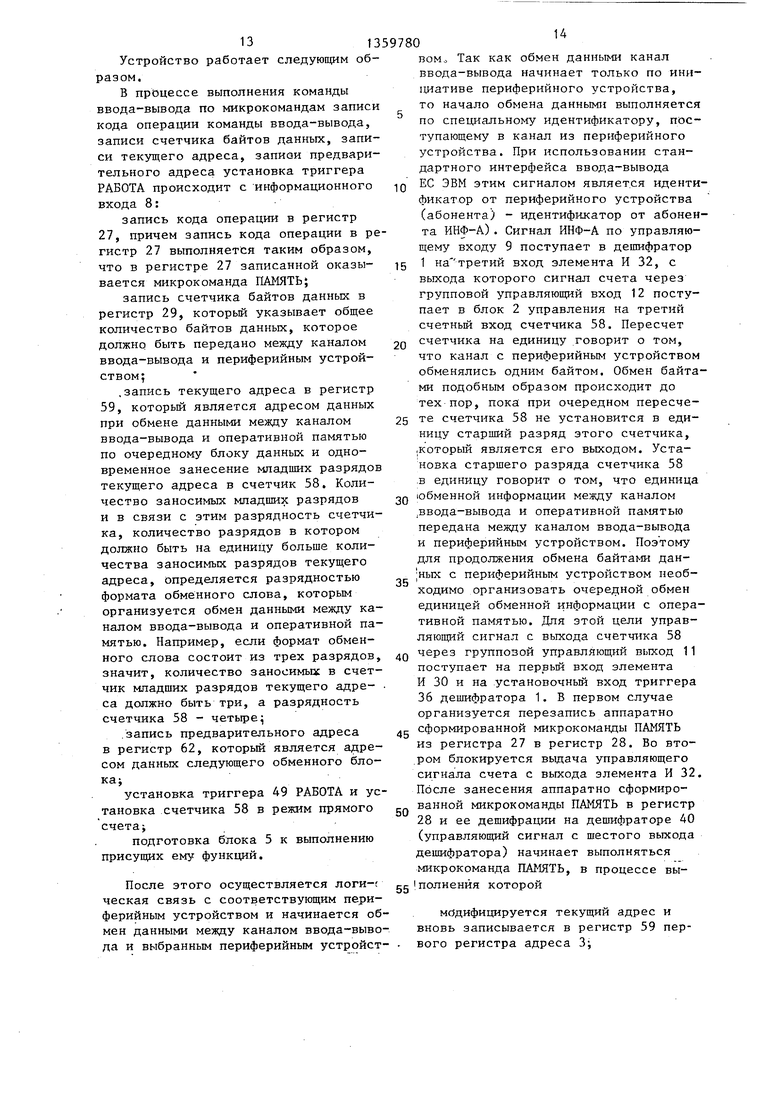

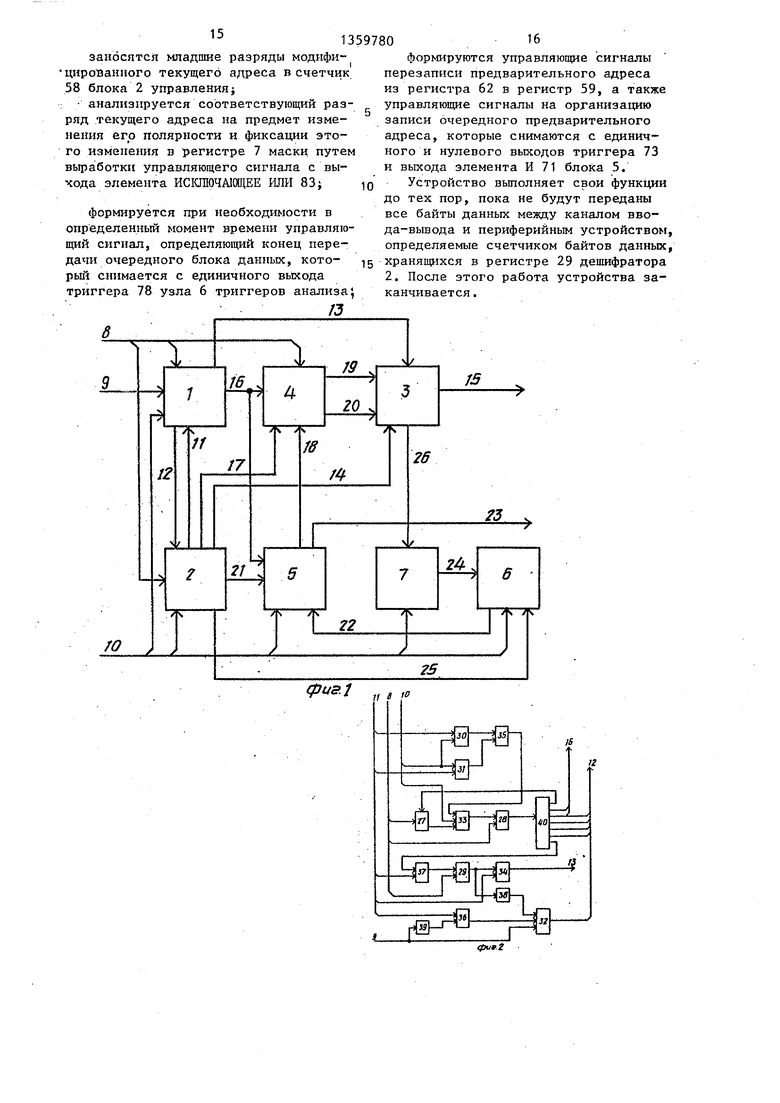

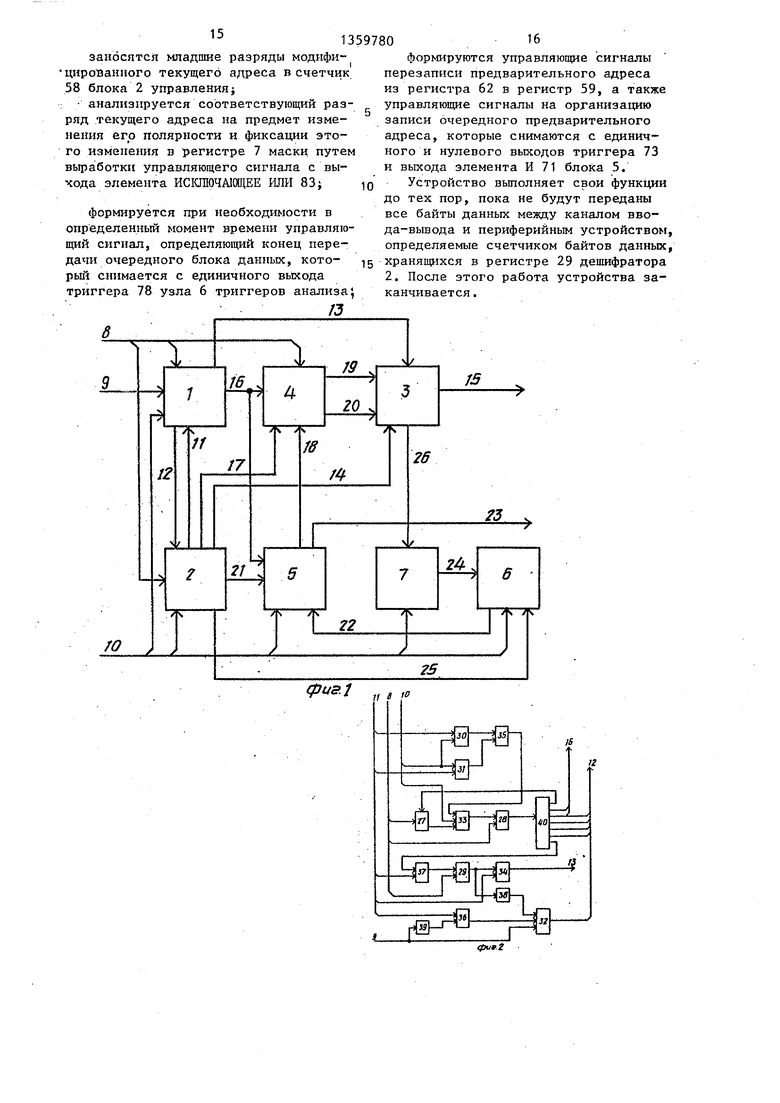

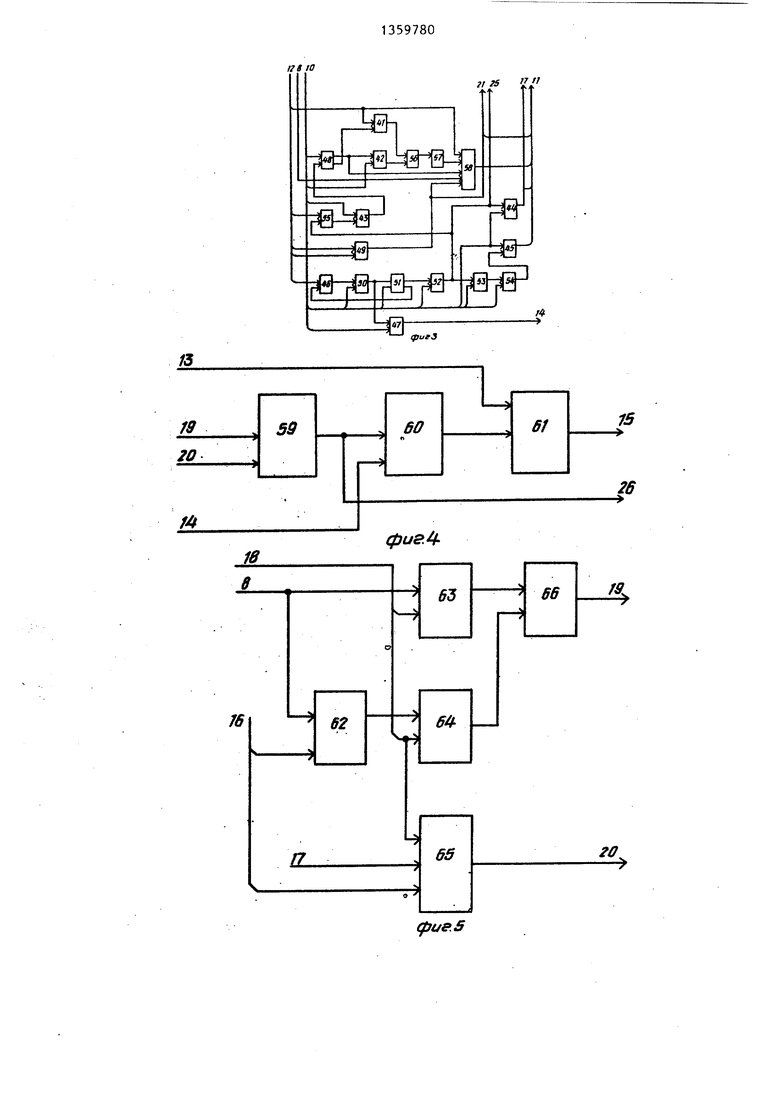

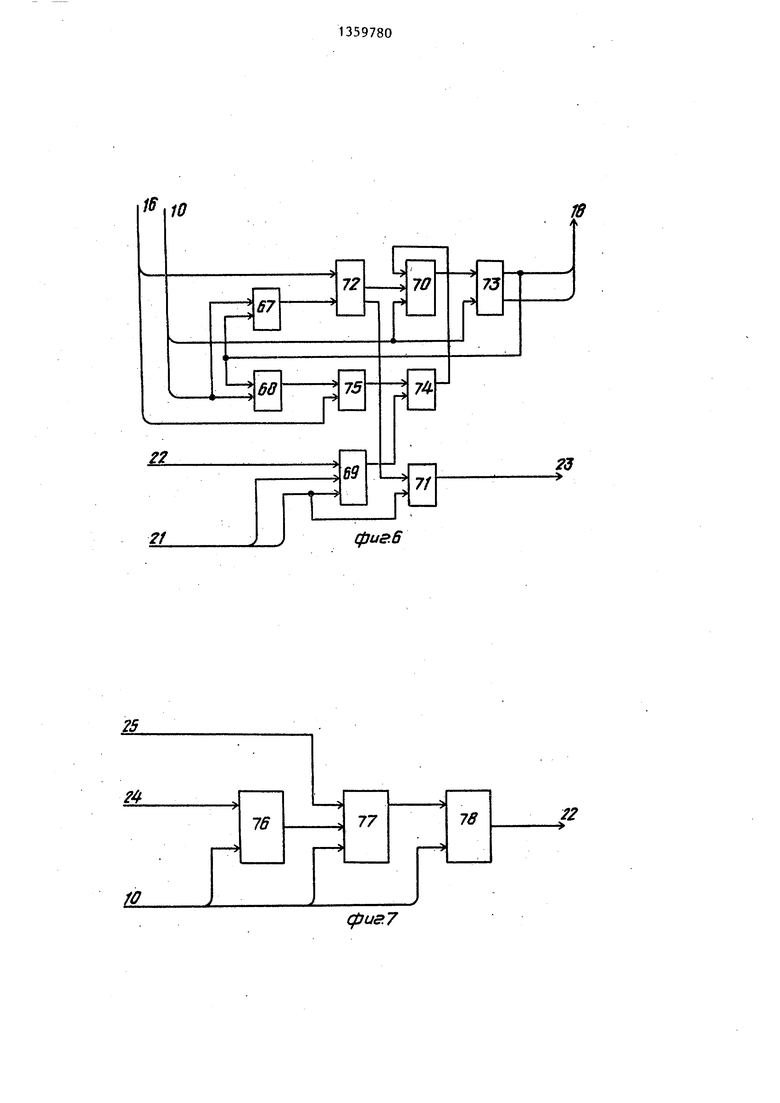

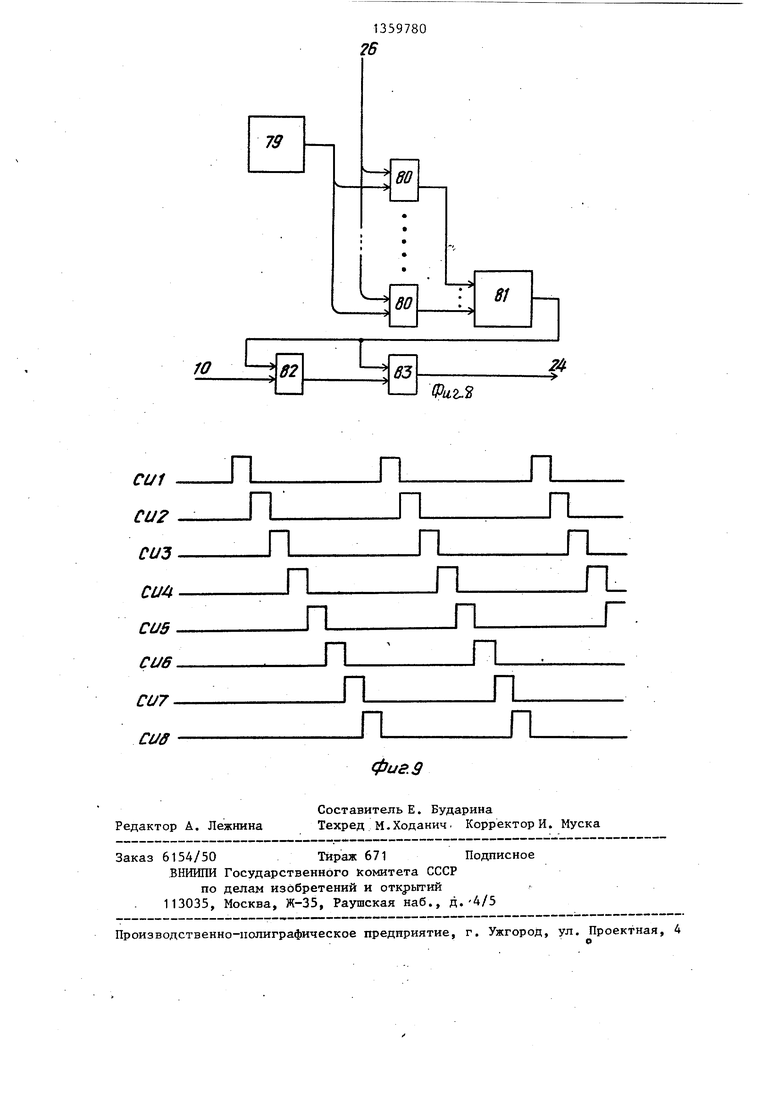

На фиг.1 изображена схема предлагаемого устройства дпя сопряжения; на фиг.2 - схема дешифратора; на фиг.З - схема блока управления; на фиг.4 - схема первого регистра адреса; на фиг.З - схема второго регистра адреса; на фиг.6 - схема блока формирования запроса прерывания; на фиг.7 - схема узла триггеров анализа на фиг.8 - схема регистра маски; на фиг.9 - схема выработки синхроимпульсов СИ1-СИВ.

Устройство для сопряжения процессора с периферийными устройствами содержит (фиг.1) дешифратор 1, блок 2 управления, первый регистр 3 адреса, второй регистр 4 адреса, блок 5 формирования запроса прерывания, узел 6 триггеров анализа, регистр 7 маски, информационный вход 8, управля ющий вход 9, групповой синхронизирующий вход 10, информационные и управляющи входы 11-14, информационный выход

30 манд, поступающих с информационного входа 8 или из регистра 27, хранения и модификации счетчика байтов данных в регистре 29, а также выработки сигнала счета, который с выхода элемен15, информационные и управляющие

входы 16-22.и выход 23 запроса преры- с та И 32 поступает на групповой управвания.,ляющий выход 12.

На фиг.1 обозначены также внутренние связи 24-26 устройства.

Дешифратор работает следующим образом.

Дешифратор 1 (фиг.2) содержит первый регистр 27, второй регистр 28, третий регистр 29, первый элемент И 30, второй элемент И 31, третий элемент И 32, первый групповой элемент И 33, второй групповой элемент И 34, первьй триггер 35, второй триггер 36, элемент ИЛИ 37, групповой элемент ИЛИ 38, элемент НЕ 39 и дешифратор 40.

Блок 2 управления (фиг.З) содер- .жит пятый элемент И 41, первьй элемент И 42, второй элемент И 43, седьмой элемент И 44, третий элемент И 45, шестой элемент И 46, четвертьй элемент И 47, первьй триггер 48, седьмой триггер 49, второй триггер 50, третий триггер 51, четвертый триггер 52, пятьй триггер 53, шестой триггер 54, первый элемент ИЛИ 55,

второй элемент ШШ 56, элемент НЕ 57 и счетчик 58.

Первый регистр 3 адреса (фиг.4) содержит регистр 59 хранения основного адреса, групповой элемент И 60 и групповой элемент ИЛИ 61.

Второй регистр 4 адреса (фиг.5) содержит регистр 62 хранения предваQ рительного адреса, первый групповой элемент И 63, второй групповой эле- мент И 64, элемент ИЛИ 65 и групповой элемент ШШ 66,

Блок 5 формирования запроса преры5 вания () содержит первый элемент И 67, четвертый элемент И 68, второй элемент И 69, пятый элемент И 70, третий элемент И 71, первый триггер 72, второй триггер 73, третий

0 триггер 74 и элемент ИЛИ 75.

Узел 6 триггеров анализа (фиг.7). содержит первый триггер 76, элемент И 77 и второй триггер 78.

Регистр 7 маски (фиг.8) содержит

5 регистр 79 маски, группу элементов И 80, групповой элемент ИЛИ 81, триггер 82 и элемент ИСКШОЧАКШЩЕ ИЛИ 83. Дешифратор 1 предназначен для дешифрации на дешифраторе 40 микроко0 манд, поступающих с информационного входа 8 или из регистра 27, хранения и модификации счетчика байтов данных в регистре 29, а также выработки сигнала счета, который с выхода элемен0

Дешифратор работает следующим образом.

По микрокомандам, которые.поступают в регистр 28 по специальным линиям с информационного входа 8, дешифратор 40 вырабатывает

с первого выхода управляющий сигнал записи кода операции с информа- с.ционного входа 8 в регистр 27. Эта запись осуществляется в процессе выполнения команды ввода-вывода и выполняется таким образом, что в зависимости от кода операции (запись или чтение) в регистр 27 .заносится аппа- ратно сформированная микрокоманда ПАМЯТЬ, которая затем по управляющему сигналу, поступающему с группового управляющего входа 11 на первый вход элемента И 30, стробированного в определенный момент времени по синхроимпульсу СИЗ, поступающему на второй вход элемента И 30 с группового синхровхода 10, путем установки

0

5

тьему входу первого группового элемента И 33 синхроимпул)сом СИб, поступающим с группового синхровхода 10, поступает в регистр 28 и после дешифрации с шестого выхода дешифратора 40 вырабатывается сигнал запуска специального -синхронизатора для выполне-

ния аппаратно сформированной микроко- -JQ ляющим сигналам, которые вьфабатьшаманды ПАМЯТЬ;

с второго и третьего выходов управляющие сигналы записи (ЗП1, ЗП2), которые поступают на групповой управляющий выход 16;15

с третьего, четвертого и пятого выходов управляющие сигналы (ЗП2, Установка, Сброс), которые поступают на групповой управляющий выход 12; 20 с седьмого выхода управляющий сигнал, который через первый вход эле-, мента ИЛИ 37 выполняет запись счетчика количества байтов данных с информационного входа 8 в третий ре- гистр 29.

Занесение микрокоманды ПАМЯТЬ из регистра 27 в регистр 28 вьтолняется следующим образом.

По управляющему сигналу, которьм поступает на первый вход элемента И 30 с группового управляющего входа 11, в определенньй момент времени, определяемый синхроимпульсом СИЗ, который поступает на второй вход элемента И 30 с группового синхровхода 10, устанавливается триггер 35, который по второму входу стробирует групповой элемент И 33, Далее по синхроимпульсу СИб, поступающему с группового синхровхода 10 на третий вход группового элемента И 33, микрокоманда ПАМЯТЬ с регистра 27 через .групповой элемент И 33 записывается в регистр 28, с которого эта микрокоманда дешифрируется на дешифраторе 40, после чего с шестого вьпсода дешифратора 40 вырабатьшается Управляющий сигнал запуска специального

ются специальным синхронизатором, за пущенным перед выполнением аппаратно сформированной микрокоманды ПАМЯТЬ и поступают с группового управляющего входа 11, выполняется сначала чтение счетчика байтов данных путем стробирования по второму входу группового элемента И 34, а затем запись модифицированного счетчика байтов данных путем стробирования через элемент ИЛИ 37 по первому входу регистра 29 о Выработка сигнала счета, поступающего с выхода элемента И 32 на груп- 25 повой управляющий выход 12, вьтолняется в случае, если после очередной модификацией счетчик байтов данных не стал равен нулю, что определяется при помощи группового элемента ИЛИ 38 с выхода которого стробируется по первому входу элемент И 32, отсутствием управляющего сигнала, поступающего с группового управляющего входа 11 на установочный вход триггера 36, сигнал с инверсного выхода которого стробирует по второму входу элемент И 32, и наличием управляющего сигнала, поступающего с управляющего входа 9 на третий вход элемента И 32, которьй является в.данном случае сигналом идентификатора от абонента - информация от абонента (ИНФ-Л), по которому канал ввода-вывода организует очередной обмен байтов данных с периферийными устройствами.

Блок 2 управления предназначен для определения конца обмена байтами данных канала ввода-вывода с пери30

35

40

46

синхронизатора, который управляет вы- gQ ферийными устройствами, когда обмен

полнением аппаратно сформированной микрокоманды ПАМЯТЬ. Этот сигнал поступает на групповой управляющий выход 12.

Хранение и модификация счетчика байтов данных выполняется следующим образом.

Занесение счетчика байтов данных в регистр 29 вьтолняется с информабайтами произошел в объеме, равном формату обменного слова между каналом ввода-вывода и оперативной памятью (например, формат обменного сло- gc ва в четыре байта, восемь байтов

и т.д.), путем выработки управляющего сигнала конца обмена, а также выработки других управляющих сигналов, необходимых для организации в процес

налу, полученному с седьмого выхода дешифратора 40, который через элеумент ИЛИ 37 поступает на первый вход регистра 29. Модификация счетчика байтов данных осуществляется в процессе вьтолнения аппаратно сформиро- ,

ванной микрокоманды ПАМЯТЬ. По управ

ются специальным синхронизатором, за пущенным перед выполнением аппаратно сформированной микрокоманды ПАМЯТЬ и поступают с группового управляющего входа 11, выполняется сначала чтение счетчика байтов данных путем стробирования по второму входу группового элемента И 34, а затем запись модифицированного счетчика байтов данных путем стробирования через элемент ИЛИ 37 по первому входу регистра 29 о Выработка сигнала счета, поступающего с выхода элемента И 32 на груп- 5 повой управляющий выход 12, вьтолняется в случае, если после очередной модификацией счетчик байтов данных не стал равен нулю, что определяется при помощи группового элемента ИЛИ 38, с выхода которого стробируется по первому входу элемент И 32, отсутствием управляющего сигнала, поступающего с группового управляющего входа 11 на установочный вход триггера 36, сигнал с инверсного выхода которого стробирует по второму входу элемент И 32, и наличием управляющего сигнала, поступающего с управляющего входа 9 на третий вход элемента И 32, которьй является в.данном случае сигналом идентификатора от абонента - информация от абонента (ИНФ-Л), по которому канал ввода-вывода организует очередной обмен байтов данных с периферийными устройствами.

Блок 2 управления предназначен для определения конца обмена байтами данных канала ввода-вывода с пери0

5

0

6

ферийными устройствами, когда обмен

байтами произошел в объеме, равном формату обменного слова между каналом ввода-вывода и оперативной памятью (например, формат обменного сло- ва в четыре байта, восемь байтов

и т.д.), путем выработки управляющего сигнала конца обмена, а также выработки других управляющих сигналов, необходимых для организации в процес10

20

се выполнения аппаратно .сформирован- ной микрокоманды ПАМЯТЬ модификации адреса данных, по которому выполняется запись (чтение) в (из) оперативную память данных формата в обменное слово, а также модификация счетчика байтов данных, который определяет общее количество обменных байтов между каалом ввода- вывода и периферийными устройствами.

Выработка управляющего сигнала конца обмена, который с выхода счетчика 58 поступает на групповой управляющий вход 11 и далее на первый вход эле- ig мента И 30 для организации записи из регистра 27 в регистр 28 аппаратно сформированной микрокоманды ПАМЯТЬ и на установочный вход триггера 36 с целью блокировки выработки сигнала счета с выхода элемента И 32 выра- ботки сигнала счета только по фронту управляющего сигнала, поступающего с управляющего входа 9, выполняется следующим образом. Счетчик 58 выполнен на микросхеме 500 НЕ 136, причем разрядность его должна быть на один больше по сравнению с количеством разрядов формата обменного слова (например, если разрядность формата обменного слова равна три , т.е. формат обменного слова равен восьми байтам , то разрядность счетчика 58 должна быть четыре). Он считает количество переданных байтов между каналом вво- да-вывода и периферийным устройством путем подачи на его третий счетный вход (PQ) сигнала счета, поступающего с выхода элемента И 32 блока дешифратора 1 через групповой управляю- 4о щий вход 12.

Счет обменных байтов в счетчике 58 происходит до тех пор, пока не будет установлен в 1 старший разряд счет- чика (выход счетчика 58 является выходом его старшего разряда). После этого происходят блокировка приема очередных сигналов счета до тех пор, пока счетчик 58 не будет подготовлен к счету байтов данньк очередного об- менного слова, и запись из регистра 27 в регистр 28 аппаратно сформированной микрокоманды ПАМЯТЬ, которая дешифруется на дешифраторе 40, после чего по управляющему сигналу с gg шестого выхода дешифратора 40 через групповой информационный вход 12 и элемент И 46 запускается специальный синхронизатор, выполненный на тригге- .

25 30

35

45

50

0

0

gо

g

pax 50-54. Синхронизатор формирует три фазных потенциала - три фазы (одна фаза составляет цикл, состоящий из восьми синхроимпульсов СИ1- QH8, показанных на фиг.9), которые вьфабатываются спецсинхронизатором последовательно друг за другом, причем появление очередной фазы сопровождается снятием предьщущей фазы. С выхода элемента И 46 запускается путем установки триггера 50 первая фаза выполнения микрокоманды ПАМЯТЬ. По следующему СИ1 путем установки триггера 52 запускается вторая фаза выполнения микрокоманды ПАМЯТЬ, причем по СИ1 второй фазы сбрасывается триггер 50 первой фазы. По следующему СИ1 путем установки триггера 54 запускается третья фаза выполнения микрокоманды ПАМЯТЬ и сбрасывается триггер 52 второй фазы. По следующему СИ1 сбрасывается триггер 54 третьей фазы (триггеры 51 и 53 под- 5 синхронизируются по СИ4). В первой фазе вырабатывается управляющий сигнал чтения, поступающий на выход 14 чтения с элемента И 47, на один вход которого поступает потенциал первой 0 фазы с триггера 50, а на другой

вход - СИ2. Сигнал чтения используется в блоке первого регистра адреса для чтения текущего адреса. После модификации текущего адреса младшие разряды этого адреса, определяющие формат обменного слова, поступают на пятый вход (информационный вход) счетчика 58 и заносятся в него. При занесении старший разряд счетчика 58 сбрасывается в нулевое состояние. Занесение младших разрядов адреса в счетчик 58 выполняется с информационного входа 8 по второй фазе. При этом режим записи в счетчик 58 устанавливается следующим образом. Исходный режим счетчика - режим прямого счета - устанавливается управляющим сигналом с четвертого выхода дешифратора 40, который является результатом дешифрации микрокоманды РАБОТА. Этот сигнал с группового управляющего вькода 12 поступает на установочньй вход триггера 49 и взводит его. Потенциал с единичного выхода триггера 49 сохраняется на весь период работы по передаче обменного массива данных между каналом и периферийным устройством, который определяется содержимым счетчика об5

5

0

мениых байтов данных, хранящимся на .регистре 29. Потенциал с выхода триггера 49 поступает на групповой управляюр(ий выход 21 и на второй вход режима работы счетчика 58, тем самым устанавливая для счетчика 58 режим прямого счета (на первьй вход режима работы счетчика 58 поступает нулевой потенциал с единичного выхода триггера 48). Для записи информации в счетчик 58 необходимо изменить его режим работы (с режима прямого счета на режим записи) .и сформиро-- вать синхросигнал занесения информации.

Режим записи и формирование синхросигнала занесения выполняется во второй фазе следующим образом.

Потенциал второй фазы через элемент ИЛИ 55 поступает на второй вход элемента И 43, первый вход которого стробируется по СИ1. Таким образом, по СИ1 будет установлен триггер 48, который с момента его установки опре деляет режим записи счетчика 58 (на первый вход режима работы счетчика 58 поступает единичный потенциал с единичного выхода триггера 48), По СИ2 через элемент И 42 формируется синхросигнал занесения в счетчик 58, который через элемент НЕ 57 поступа- ет на четвертый (С) вход счетчика 58 По СИЗ во второй фазе триггер 48 сбрасывается, тем самым переводя режим счетчика 58 из режима записи в режим прямого счета и разрешая формирование синхроимпульса занесения информации по третьему (Р.) счетному входу счетчика 58 путем установки с нулевого выхода триггера 48 единичного потенциала на второй вход элемента И 41. После занесения информации в счетчик 58 старший разряд счетчика

сбрасывается и нулевой выход счетчика g ративной памятью и каналом ввода-вы58, поступающий на установочный вход триггера 36, разрешает его сброс после снятия управляющего сигнала на входе 9, тем самьш разрешая возможность прямого счета счетчика 58 по фронту очередного управляющего сигнала, поступающего на третий вход элемента И 32 с управляющего входа 9.

Прямой счет счетчика 58 осуществляется следующим образом.

Сигнал счета поступает на третий (Рд) вход счетчика 58 и через задержку, определяемую суммарной задержкой .элементов 41,56 и 57, в качестве синвода, а также чтения этого адреса и вьщачи его на информационные выходы 15 и 26 о

Первый регистр адреса работает gQ следующим образом

Текущий адрес хранится в регистре 59. Заносится этот адрес в регистр 59 с информационного входа 19 по сигналу записи, поступающему с входа 20 записи. Чтение текущего адреса и выдача его на информационный выход 15 вьтолняется по сигналу чтения, который с входа 14 чтения поступает на второй вход, группового

55

5

0

5

хроимпульса поступает на четвертый (с) вход счетчика 58.

Таким образом, в первой фазе по СИ2 с элемента И 47 выдается управляющий сигнал чтения адреса байтов данных, во второй фазе по СИ2 младшие разряды адреса, определяюш;ие формат обменного слова, заносятся в счетчик 58. Кроме этого, во второй фазе по СИ2 элемент И 44 вырабатывает управляющий сигнал чтения счетчика байтов данных, который поступает на второй вход группового элемента И 34, а с выхода последнего информация поступает через блок первого регистра 3 адреса на информационный выход 15. Во второй фазе вьшолнения микрокоманды ПАМЯТЬ происходит модификация счетчи ка байтов данньк на количество обменных байтов, определяемых форматом обменного слова. После модификации в третьей фазе по сигналу СИ2 с элемента И 45 вырабатывается сигнал записи, который через групповой управляющий вход 11 поступает на второй вход элемента ИЛИ 37, с выхода которого сигнал стробирует регистр 29 для занесения в него с информационного входа 8 модифицированного счетчика байтов дарных. Исходная информа- в счетчике 58 устанавливается путем занесения в него информации с информационного входа 8 по управляю- щему сигналу записи (ЗП2), которьй поступает с группового управляющего выхода 12 на первый вход элемента ИДИ 55, а вьщается с третьего выхода дешифратора 40 путем дешифрации микрокоманды ЗАПИСЬ 2.

Первый регистр 3 адреса предназначен для хранения текущего адреса, по которому организуется обмен данными определенного формата между опе0

0

вода, а также чтения этого адреса и вьщачи его на информационные выходы 15 и 26 о

Первый регистр адреса работает Q следующим образом

Текущий адрес хранится в регистре 59. Заносится этот адрес в регистр 59 с информационного входа 19 по сигналу записи, поступающему с входа 20 записи. Чтение текущего адреса и выдача его на информационный выход 15 вьтолняется по сигналу чтения, который с входа 14 чтения поступает на второй вход, группового

5

элемента И 60. Элемент ИЛИ 61 используется для вьдачи на информационный выход 15 или счетчика данных, поступающего через информационньй вход 13 с выхода группового элемента И 34, или текущего адреса данных

Второй регистр 4 адреса предназначен для хранения предварительного адреса данных, записи текущего адреса данных в регистр 59 и перезаписи предварительного адреса данных из регистра 62 в регистр 59 первого регистра адреса.

Запись текущего адреса данных в регистр 59 выполняется с элемента ИЛИ 66 под управлением сигнала записи с элемента ИЛИ 65. На первый вход элемента ИЛИ 66 текущий адрес поступает с информационного входа 8 через групповой элемент И 63, который стробируется управляющим сигналом по второму входу, поступающим с группового входа 18./ Сигнал записи, поступающий с элемента ИЛИ 65 на выход 20 записи, формируется по сигна- лу записи (ЗП2), которьм через групповой вход записи поступает с третьего выхода дешифратора 40. Перезапись предварительного адреса из регистра 62 в регистр 59 выполняется через групповой элемент И 64 и ИЛИ 66 под управлением управляющего сигнала, поступающего с группового управляющего входа 18 на второй вход группового элемента И 64 и первьй вход элемента ИЛИ 65. Запись предварительного адреса в регистр 62 выполняется по сигналу записи (ЗП1), которьй через групповой вход 16 записи поступает с второго входа дешифратора 40.

Блок 5 формирования запроса прерывания предназначен для выработки управляющих сигналов записи текущего адреса в регистр 59 и вьфаботки сигнала запроса на прерывание, по которому организуется запись первого предварительного адреса в регистр 62, после перезаписи старого предварительного адреса из регистра 62 в регистр 59.

Блок 5 работает следующим образом.

По управляющему сигналу (ЗП2), поступающему на первый вход элемента ИЛИ 75 через групповой управляющий вход 16 с третьего выхода дешифратора 40, устанавливается триггер 74 и запрещает срабатывание элемента И 70. Триггер 73, находящийся в исходном

0

5

0

сбросовом состоянии (исходное состоя-i ние устанавливается по синхроимпульсу СИ1, поступающему на-синхровход триггера 73), клапанирует своим нулевым выходом по второму входу групповой элемент И 63, разрешая по управляющему сигналу ЗП2, поступающему на третий вход элемента ИЛИ 65, записать информацию с информационного входа 8 через элементы И 63 и ИЛИ 66 на информационный вход 19 в регистр 59. После выполнения записи информации в регистр 59 выполняется запи сь информации в регистр 62. При этом управляющий сигнал (ЗП1) через групповой управляющий вход 16 с второго выхода дешифратора 40 устанавливает триггер 72, подготавливая тем самым схему блока формирования к работе управляющему сигналу, поступающему с управляющего входа 22 на первый вход элемента И 69, который является сигналом конца передачи 5 очередного блока данных. По этому сигналу в начале второй фазы через элемент И 69, на второй вход которого поступает потенциал второй фазы, а на третий вход - потенциал РАБОТА через групповой управляющий вход 21 с триггера 52 и триггера 49 соответственно, сбрасывается триггер 74. По нулевому выходу триггера 74, который поступает на третий вход элемента И 70, разрешается срабатывание элемента И 70 по СИ1, который поступает на второй вход элемента И 70, что приводит к установке триггера 73 по СИ1. В связи с этим единичный выход триггера 73 стробирует по второму входу элемент И 64 и поступает на первый вход элемента ИЛИ 65, тем самым разрешая перезапись информации из регистра 62 в регистр 59. Далее по СИЗ, поступающему на первый вход элемента И 67 и на второй вход элемента И 68, вторые входы которых стробируются единичным выходом триггера 73, сбрасывается триггер 72 и через элементы ИЛИ 75 устанавливается триггер 74. По сбросу триггера 72, нулевой выход которого поступает на второй вход элемента И 71, а на первый вход которого поступает потенциал РАБОТА с группового управляющего входа 21, с выхода элемента И 71 вырабатывается управляющий сигнал, поступающий на выход 23, который явля- ется запросом на организацию записи

0

5

05

0

5

очередного предварительного адреса в регистр 59. в это же время начинается обмен байтами данных по адресу очередного блока данных, которьй до того был предварительным, В период удовлетворения запроса выполняется микрокоманда записи предварительного адреса в регистр 59. При этом с второго выхода дешифратора 40 сигнал ЗП1 поступает на установочный вход триггера 72 и устанавливает его, тем самым, снимается сигнал запроса на

организацию записи очередного предварительного адреса и схема блока 5 подготавливается к анализу управляющего сигнала, определяющего конец передачи очередного блока данных.

Узел триггеров анализа предназначен для формирования упр авляющего сигнала, определяющего конец передачи очередного блока данных.

Узел триггеров анализа работает следующим образом.

При поступлении с входа 24 управляющего сигнала на установочный вход триггера 76 этот триггер устанавливается по СИ5, который поступает на синхровход триггера 76, во второй фазе через элемент И 77, на первый вход которого поступает сигнал второ фазы с триггера 52 через управляющий вход 25, а на третий вход - СИ7, устанавливается триггер 78, с прямого

выхода которого снимается сигнал кон- двенадцатый разряд-не изменился, то

ца передачи очередного блока, которыйна первый и второй входы элемента

поступает на управляющий вход 22 иИСКЛЮЧАКИЦЕЕ ИЛИ 83 поступят сигналы

далее на первый вход элемента И 69.одинаковой полярности в течение втоРегистр маски предназначен длярой фазы выполнения аДпаратно сформйфшссации объема блока данных, которые Qрованной микрокоманды ПАМЯТЬ, что оз- будут передаваться при организации

начает, что блок данных по текущему адресу еще не передан. Если двенадца- тьм разряд изменился, то на первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ

блочного обмена данными.

Регистр маски работает следующим образом.

В регистре 79 предварительно вручную при помощи коммутационного переключателя (этот процесс можно выполнить и микропрограммным способом, например, при начальной загрузке мик- ропрограмм) устанавливается в единичное состояние один из разрядов. Установленный в единичное состояние разряд регистра 79 определяет тот объем блока данных, которые будут переда- ,ваться .при организации блочного обмена данными. Например, при установке в единичное состояние двенадцатого разряда регистра 79 объем одного бло

5

0

о

ка данных будет составлять 2048 бай-, тов. В этом случае при помощи рег ист- ра 79 по первому входу будет строби- роваться только двенадцатый элемент И 80, все остальные элементы И 80 будут по первому входу замаскированы На вторые входы элементов И 80 постоянно поступает через информацион0 ный вход 26 информация из регистра 59, в котором хранится текущий адрес, обменного блока. Принцип работы регистра маски по определению конца обмена блока данных по очередному адресу заключается в определении изменения в данном случае двенадцатого разряда текущего адреса. Это выполняется следующим образом. Изменения информации (адреса) в регистре 59 выполняются во второй фазе выполнения микрокоманды по СИ2. Поэтому по СИ1, который поступает на синхровход триг гера 82, триггер установится в определенное состояние управляющим сигна25 лом, который с выхода элемента ИЛИ 81, на котором собираются все сигналы с выходов элементов И 80, поступает на информационный вход триггера 82. Следовательно, триггер запоминает состояние двенадцатого разряда текущего адреса до его. модификации. После модификации текущего адреса двенадцатый разряда в регистре 62 может или измениться, или остаться прежним. ЕсЛ и

рованной микрокоманды ПАМЯТЬ, что оз-

начает, что блок данных по текущему адресу еще не передан. Если двенадца- тьм разряд изменился, то на первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 83 поступают.разнополярные сигналы, так как на первый вход этого элемента поступит с выхода элемента ИЛИ 81 двенадцатый разряд смодифици- рованного текущего адреса, а на второй вход с единичного выхода триггера 82 поступит двенадцатьй разряд текущего адреса до его модификации. Поэтому с выхода ИСКШОЧАКЩЕЕ ИЛИ 83 будет получен управляющий сигнал,

которьй фиксирует конец передачи

обменного блока и который через уп- равляющий вход 24 поступает,в блок триггеров анализа на информационный вход триггера 76.

Устройство работает следуюпщм образом,

В процессе выполнения команды ввода-вывода по микрокомандам записи кода операции команды ввода-вывода, записи счетчика байтов данных, записи текущего адреса, записи предварительного адреса установка триггера РАБОТА происходит с информационного входа 8:

запись кода операции в регистр 27, причем запись кода операции в регистр 27 выполняется таким образом, что в регистре 27 записанной оказывается микрокоманда ПАМЯТЬ;

запись счетчика байтов данных в регистр 29, которьй указывает общее количество байтов данных, которое должно быть передано между каналом ввода-вывода и периферийным устройством;

.запись текущего адреса в регистр 59, который является адресом данных при обмене данными между каналом ввода-вывода и оперативной памятью по очередному блоку данных и одновременное занесение младших разрядов текущего адреса в счетчик 58. Количество заносимых младших разрядов и в связи с этим разрядность счетчика, количество разрядов в котором должно быть на единицу больше количества заносимых разрядов текущего адреса, определяется разрядностью формата обменного слова, которым организуется обмен данными между каналом ввода-вывода и оперативной памятью. Например, если формат обменного слова состоит из трех разрядов, значит, количество заносимых в счетчик младших разрядов текущего адре- са должно быть три, а разрядность счетчика 58 - четьфе

.запись предварительного адреса в регистр 62, который является адресом данных следующего обменного бло- ка;

установка триггера 49 РАБОТА и установка счетчика 58 в режим прямого счетаj

подготовка блока 5 к выполнению присущих ему функций.

После этого осуществляется логи-; ческая связь с соответствующим периферийным устройством и начинается обмен данными между каналом ввода-вывода и выбранным периферийным устройствомо Так как обмен данными канал ввода-вывода начинает только по ини- 1щативе периферийного устройства, то начало обмена данными выполняется по специальному идентификатору, поступающему в канал из периферийного устройства. При использовании стандартного интерфейса ввода-вывода Q ЕС ЭВМ этим сигналом является идентификатор от периферийного устройства (абонента) - идентификатор от абонента ИНФ-А). Сигнал ИНФ-А по управляющему входу 9 поступает в дешифратор 5 1 на третий вход элемента И 32, с выхода которого сигнал счета через групповой управляющий вход 12 поступает в блок 2 управления на третий счетный вход счетчика 58. Пересчет Q счетчика на единицу говорит о том, что канал с периферийным устройством обменялись одним байтом. Обмен байтами подобным образом происходит до тех пор, пока при очередном пересче- 5 те счетчика 58 не установится в единицу старший разряд этого счетчика, .который является его выходом. Установка старшего разряда счетчика 58 .в единицу говорит о том, что единица 0 Обменной информации между каналом .ввода-вывода и оперативной памятью передана между каналом ввода-вывода и периферийным устройством. Поэтому для продолжения обмена байтами дан- |ных с периферийным устройством необходимо организовать очередной обмен единицей обменной информации с оперативной памятью. Для этой цели управ- ляющай сигнал с выхода счетчика 58 Q через групповой управляющий выход 11 поступает на первый вход элемента И 30 и на установочньй вход триггера 36 дешифратора 1. В первом случае организуется перезапись аппаратно сформированной микрокоманды ПАМЯТЬ из регистра 27 в регистр 28. Во втором блокируется выдача управляющего сигнала счета с выхода элемента И 32. После занесения аппаратно сформированной микрокоманды ПАМЯТЬ в регистр 28 и ее дешифрации на дешифраторе 40 (управляющий сигнал с шестого выхода дешифратора) начинает вьтолняться микрокоманда ПАМЯТЬ, в процессе вы- 5 полненйя которой

модифицируется текущий адрес и вновь записывается в регистр 59 первого регистра адреса 3;

5

5

0

13

заносятсл младшие разряды модифицнрованиого текущего адреса в счетчик 58 блока 2 управления

: - анализируется соответствующий разряд текущего адреса на предмет изменения его полярности и фиксации этого изменения в регистре 7 маски путем выработки управляющего сигнала с выхода элемента ИС1ШОЧАЮЩЕЕ ИЛИ 83;

формируется при необходимости в определенный момент времени управляющий сигнал, определяющий конец передачи очередного блока данных, кото- рьй снимается с единичного выхода триггера 78 узла 6 триггеров анализа

/3

ffJUS-l

16

формируются управляющие сигналы перезаписи предварительного адреса из регистра 62 в регистр 59, а также управляющие сигналы на организацию записи очередного предварительного адреса, которые снимаются с единичного и нулевого выходов триггера 73 и выхода элемента И 71 блока 5.

Устройство выполняет свои функции до тех пор, пока не будут переданы все байты данных между каналом ввода-вывода и периферийньм устройством, определяемые счетчиком байтов данных, хранящихся в регистре 29 дешифратора 2. После этого работа устройства заканчивается.

11 S

IS

гг

Г П411 J1

Н3-Л3 1&

40

И

фиг. г

л к

(pufS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

(fJt/e.S

фиг

| Селекторный канал | 1973 |

|

SU519703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент CUJA № 3699530, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-15—Публикация

1985-03-12—Подача