lp J.1

Изобретение относится к вычислительной технике, в частности к устройствам ввода информации в ЗУ, и может быть использовано в каналах ЭВМ.

Целью настоящего изобретения является повышение быстродействия устройства.

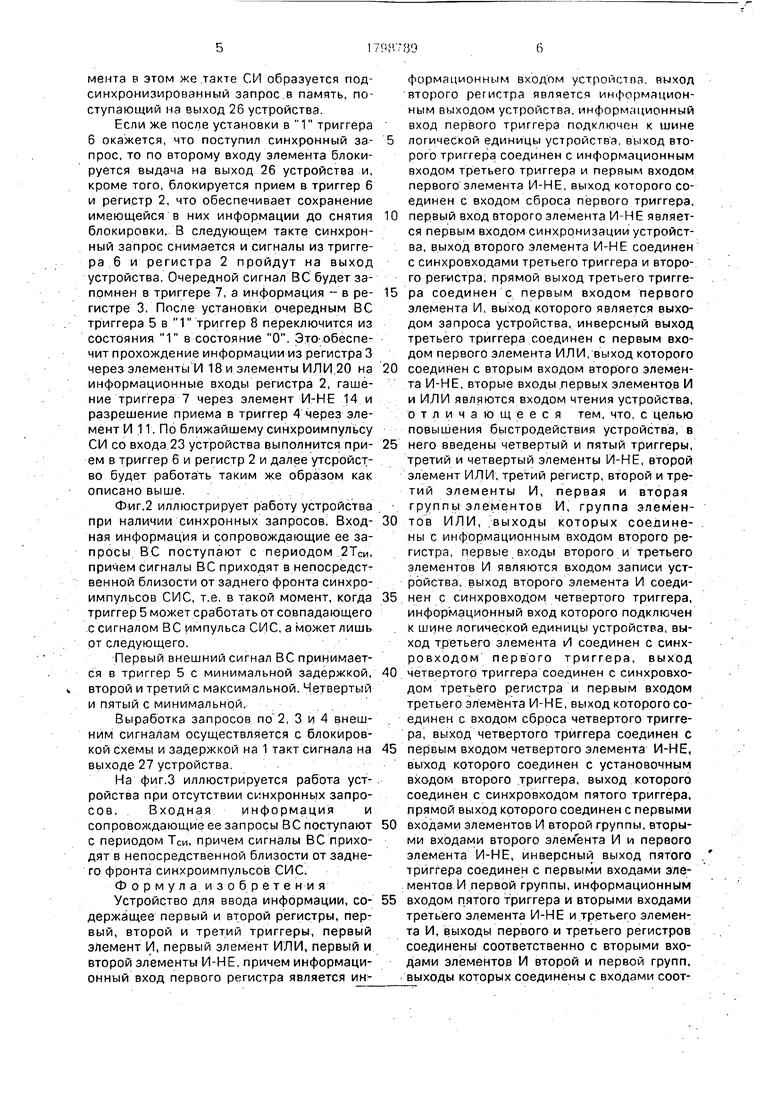

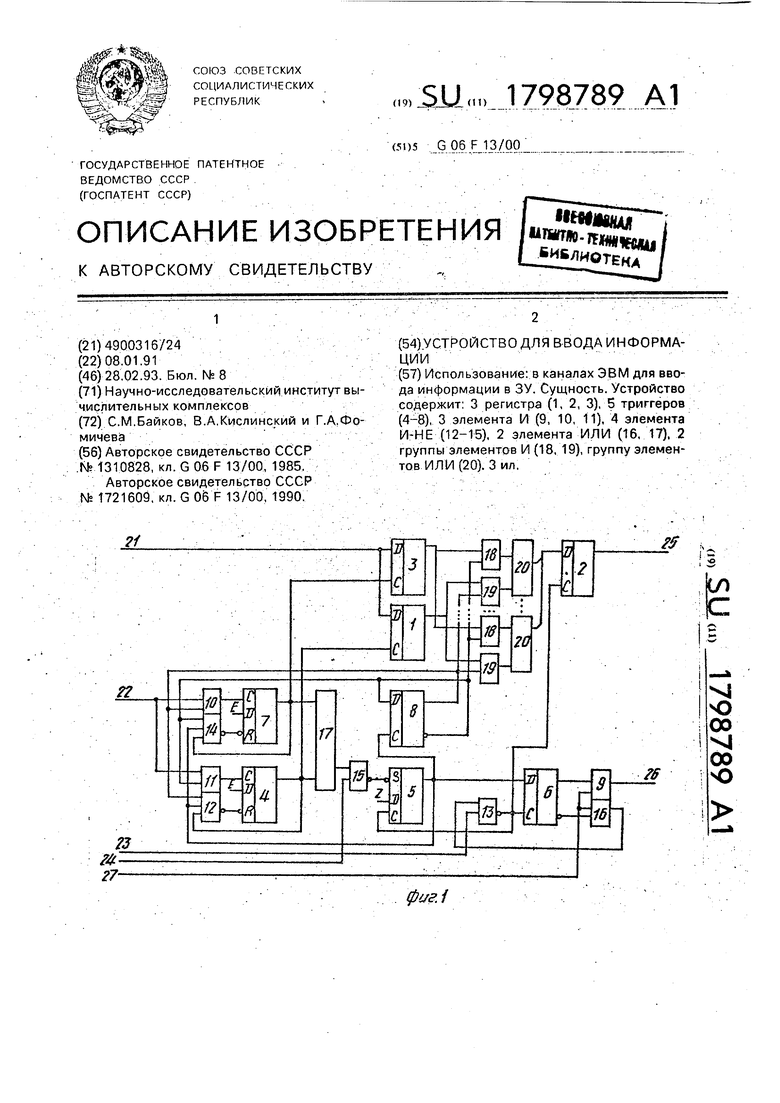

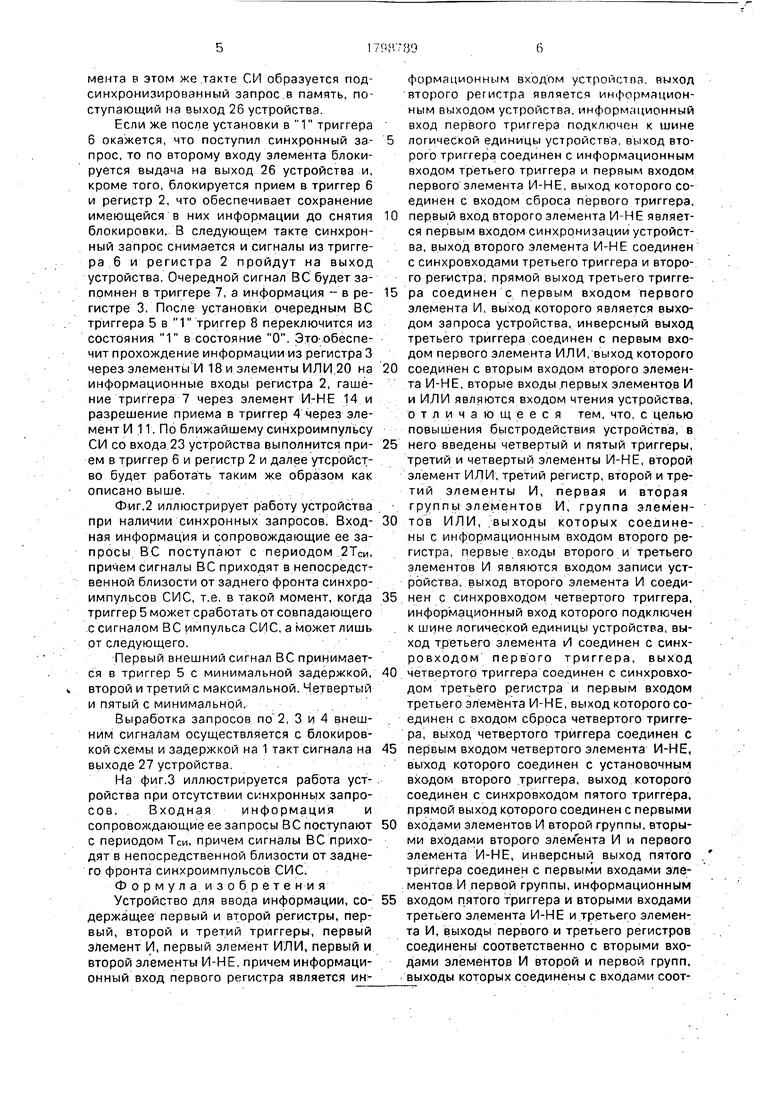

На фиг.1 приведена функциональная схема предложенного устройства; на фиг.2 и 3 - временные диаграммы его работы при наличии синхронных запросов и при их отсутствии соответственной

Устройство (фиг.1) содержит с первого по третий регистры 1, 2, 3, с первого по пятый триггеры.4-8, с первого по третий элементы I/I 9,10,11, с первого по четвертый элементы И-НЕ 12-15, первый и второй элементы ИЛИ 16, 17, первую и вторую группы элементов И 18, 19, группу элементов ИЛИ 20. .

Информационный вход регистра 1 соединен с информационным входом регистра 3 и с информационным входом 21 устройства; синхровход регистра 1 соединен с вторым входом элемента ИЛИ 17, с третьим входом элемента И-НЕ 12 и выходом триггера 4; синхровход регистра 3 соединен с первым входом элемента ИЛИ 17, с первым входом элемента И-НЕ 14 и выходом триггера 7; информационный вход триггера 4 соединен с шиной логической единицы устройства, синхровход этого триггера соединен с выходом элемента. И 11, первый вход которого соединен с первым входом элемента И 10 и со вторым сигнальным входом 22 устройства; выход элемента И 10 соединен с синхровходом триггера 7, информационный вход которого соединен с шиной логической единицы устройства, вход сброса триггера 4 соединен с выходом элемента И-НЕ. 12, вход сброса триггера 7 соединен с выходом элемента И-НЁ 14, выход элемента ИЛИ 17 соединен с первым входом элемента И-НЕ 15, выход которого соединен установочным входом триггера 5, выход которого соединен с синхровходом триггера 8, с первым входом элемента И-НЕ 12. третьим входом элемента И-НЕ 14 и информационным входом триггера 6, синхровход которого соединен с синхровходами регистра 2, триггера 5 и выходом элемента И-НЕ 13, первый вход которого соединен с первым входом 23 синхронизации устройства, второй вход элемента И-НЕ 15 соединен с входом 24 синхронизации устройства, информационный вход триггера 5 соединен с шиной логического нуля устройства, инверсный выход триггера 8 соединен с первыми входами элементов И 18 первой группы, информационным входом триггера 8 и вторыми входами элементов И-НЕ 14 и И 11,

прямой выход триггера 8 соединен с первыми входами элементов И 19 второй группы и вторыми входами элементов И 10 и И-НЕ 12, выходы первого и третьего регистров 1,

3 соединены соответственно со вторыми входами элементов И 19, 18 второй и первой групп, выходы которых соединены с входами соответствующих элементов ИЛИ 20 группы, выходы которых соединены с ин0 формационными входами регистра 2, выход которого соединен с информационным выходом устройства 25, прямой выход триггера б соединен с первым входом элемента И 9, выход которого соединен с выхо5 дом 26 запроса устройства, инверсный выход триггера 6 соединен с первым входом элемента ИЛИ 16, выход которого соединен со вторым входом элемента И-НЕ 12, вторые входы элементов И 9 и ИЛИ 16 соединены

0 со входом 27 чтения устройства.

Устройство работает следующим образом. В исходном состоянии все триггеры установлены в О. Сопровождающий информацию входной сигнал (ВС), поступая с

5 22 входа устройства на первый вход элемента И 11, на второй вход которого поступает уровень логической единицы с инверсного выхода триггера 8, устанавливает триггер 4 в состояние 1. С помощью выходного сиг0 нала этого триггера информация, поступающая на вход 21 устройства, запоминается в регистре 1. По фронту ближайшего синхроимпульса СИС, поступающего на 24 вход устройства, триггер 5 установится сигналом

5 с выхода триггера 4 в состояние 1. Сигнал с выхода триггера 5 поступает на синхровход триггера 8 и устанавливает его в состо- яние 1 за счет разрешения с его инверсного выхода; на всех входах злемен0 та И-НЕ 12 установится уровень логической единицы и триггер 4 установится в состояние О. На втором входе элемента И 10 установится уровень логической единицы с прямого выхода триггера 8, не препятству5 ющий прохождению следующего сигнала

ВС в триггер 7. Поскольку на первом входе

элемента ИЛИ 16 уже имеется 1, поступа ющэя с инверсного выхода триггера 6, то по

фронту ближайшего синхроимпульса СИ,

0 поступающего на вход 23 устройства, триггер 6 установится в состояние 1 и благодаря разрешению на первых входах группы элементов И 19 с прямого выхода триггера 8 информация из регистра 1 будет передана

5 в регистр 2, а триггер 5 установится в состояние О.

Если в этом периоде синхронный запрос, поступающий на вход 27 устройства, отсутствует, то благодаря разрешению на втором входе элемента VI 9 на выходе злемента в этом же .такте СИ образуется под- синхронизировэнный запрос.в память, поступающий на выход 26 устройства.

Если же после установки в 1 триггера 6 окажется, что поступил синхронный запрос, то по второму входу элемента блокируется выдача на выход 26 устройства и, кроме того, блокируется прием в триггер 6 и регистр 2, что обеспечивает сохранение имеющейся в них информации до снятия блокировки. В следующем такте синхронный запрос снимается и сигналы из триггера 6 и регистра 2 пройдут на выход устройства. Очередной сигнал ВС будет запомнен в триггере 7, а информация - в регистре 3. После установки очередным ВС триггера 5 в 1 триггер 8 переключится из состояния 1 в состояние О. Это обеспечит прохождение информации из регистра 3 через элементы И 18 и элементы ИЛИ.20 на информационные входы регистра 2, гашение триггера 7 через элемент И-НЕ 14 и разрешение приема в триггер 4 через элемент И 11. По ближайшему синхроимпульсу СИ со входа 23 устройства выполнится прием в триггер 6 и регистр 2 и далее утсройст- во будет работать таким же образом как описано выше,

Фиг.2 иллюстрирует работу устройства при наличии синхронных запросов. Входная информация и сопровождающие ее запросы. ВС поступают с периодом 2ТСи, причем сигналы ВС приходят в непосредственной близости от заднего фронта синхроимпульсов СИС, т.е. в такой момент, когда триггер 5 может сработать от совпадающего с сигналом ВС импульса СИС, а может лишь от следующего.

Первый внешний сигнал ВС принимается в триггер 5 с минимальной задержкой, второй и третий с максимальной. Четвертый и пятый с минимальной.

Выработка запросов по 2, 3 и 4 внешним сигналам осуществляется с блокировкой схемы и задержкой на 1 такт сигнала на выходе 27 устройства.

На фиг.З иллюстрируется работа устройства при отсутствии синхронных запросов. Входная информация и сопровождающие ее запросы ВС поступают с периодом ТСи, причем сигналы ВС приходят в непосредственной близости от заднего фронта синхроимпульсов СИС.

Ф о р м у л а и з о б р е т е н и я

Устройство для ввода информации, содержащее первый и второй регистры, первый, второй и третий триггеры, первый элемент И, первый элемент ИЛИ, первый и второй элементы И-НЕ, причем информационный вход первого регистра является информационным входом устройства, выход второго регистра является информационным выходом устройства, информационный вход первого триггера подключен к шине логической единицы устройства, выход второго триггера соединен с информационным входом третьего триггера и первым входом первого элемента И-НЕ, выход которого соединен с входом сброса первого триггера,

0 первый вход второго элемента И-НЕ является первым входом синхронизации устройства, выход второго элемента И-НЕ соединен с синхровходами третьего триггера и второго регистра, прямой выход третьего тригге5 ра соединен с первым входом первого элемента И, выход которого является выходом запроса устройства, инверсный выход третьего триггера соединен с первым входом первого элемента ИЛИ, выход которого

0 соединён с вторым входом второго элемента И-НЕ, вторые входы .первых элементов И и ИЛИ являются входом чтения устройства, от л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в

5 него введены четвертый и пятый триггеры, третий и четвертый элементы И-НЕ, второй элемент ИЛИ, третий регистр, второй и третий элементы И, первая и вторая группы элементов И, группа элемен0 тов ИЛИ, .выходы которых соедине- . ны с информационным входом второго регистра, первые входы второго и третьего элементов И являются входом записи устройства, выход второго элемента И соеди5 нен с синхровходом четвертого триггера, информационный вход которого подключен к шине логической единицы устройства, выход третьего элемента И соединен с синхровходом первого триггера, выход

0 четвертого триггера соединен с синхровходом третьего регистра и первым входом третьего элемента И-НЕ, выход которого соединен с входом сброса четвертого тригге- ра, выход четвертого триггера соединен с

5 первым входом четвертого элемента И-НЕ, выход которого соединен с установочным входом второго триггера, выход которого соединен с синхровходом пятого триггера, прямой выход которого соединен с первыми

0 входами элементов И второй группы, вторыми входами второго элемента И и первого элемента И-НЕ, инверсный выход пятого . триггера соединен с первыми входами элементов И.первой группы, информационным

5 входом пятого триггера и вторыми входами третьего элемента И-НЕ и третьего элемента И, выходы первого и третьего регистров соединены соответственно с вторыми входами элементов И второй и первой групп, выходы которых соединены с входами соответствующих элементов ИЛИ группы, выход первого триггера соединен с синхровходом первого регистра, вторым входом второго элемента ИЛИ и третьим входом первого элемента И-НЕ, выход второго триггера соединен с третьим входом третьего элемента И-НЕ, выход второго элемента И-НЕ соединен с синхровходом второго триггера, инси П П П П П П

формационный вход которого подключен к шине логического нуля устройства, второй вход четвертого элемента И-НЕ является вторым входом синхронизации устройства, информационный вход третьего регистра объединен с информационным входом первого регистра,

П П П П П П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1991 |

|

SU1803917A1 |

| Устройство для управления обменом информации | 1990 |

|

SU1721609A1 |

| Устройство вывода информации | 1991 |

|

SU1807492A1 |

| Устройство для буферизации команд | 1991 |

|

SU1789982A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для выдачи информации | 1991 |

|

SU1820389A1 |

| Устройство для сопряжения процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1211747A1 |

Использование: в каналах ЭВМ для ввода информации в ЗУ. Сущность. Устройство содержит: 3 регистра (1, 2, 3), 5 триггеров (4-8), 3 элемента И (9, 10, 11), 4 элемента И-НЕ (12-15), 2 элемента ИЛИ (16, 17), 2 группы элементов И (18, 19), группу элементов ИЛИ (20). 3 ил.

сисГТ П П П П П П П П П П П

вс F/t . |Г1ГЛ Ш

тУ

г4

та ГП

JJ

7-J

J2.

2В

g/ XT

Ж.

Jd:

ог.2 си П П П. П П П П П П П

сие

S3 П П П ГТ П П П П:

М

Т2

Гг-I Гз-I Г4-1 П-I

Г5

JЈ

2/

)СГ XF- Уз У7- Х1ГА5

AL

ж

3±

JZ

L2

ЗК

Ж

Л.

ж

Ј.

)2L

Jd

IE

| Устройство для обмена информацией | 1985 |

|

SU1310828A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-28—Публикация

1991-01-08—Подача