Изобретение относится к вьмисли- тельной технике и может быть использовано в многопроцессорных вычислительных системах.

Цель изобретения - повышение достоверности функционирования многопроцессорной системы за счет перераспределения заданий с отказавших процессоров на работающие.

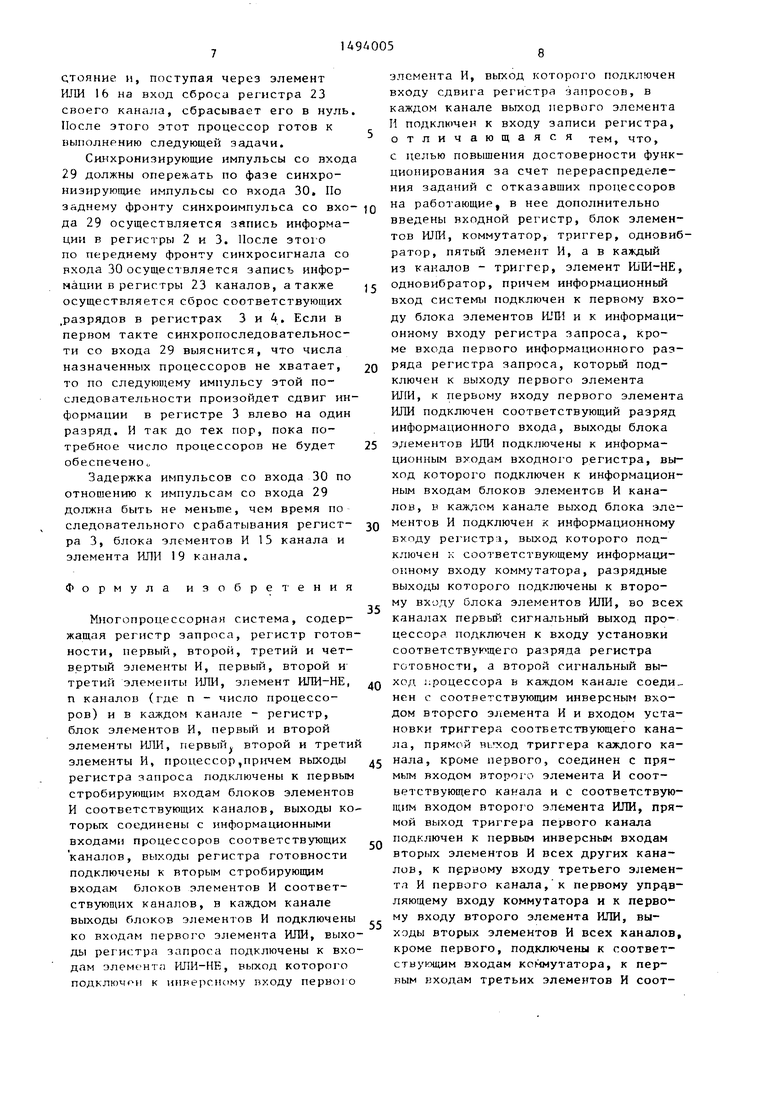

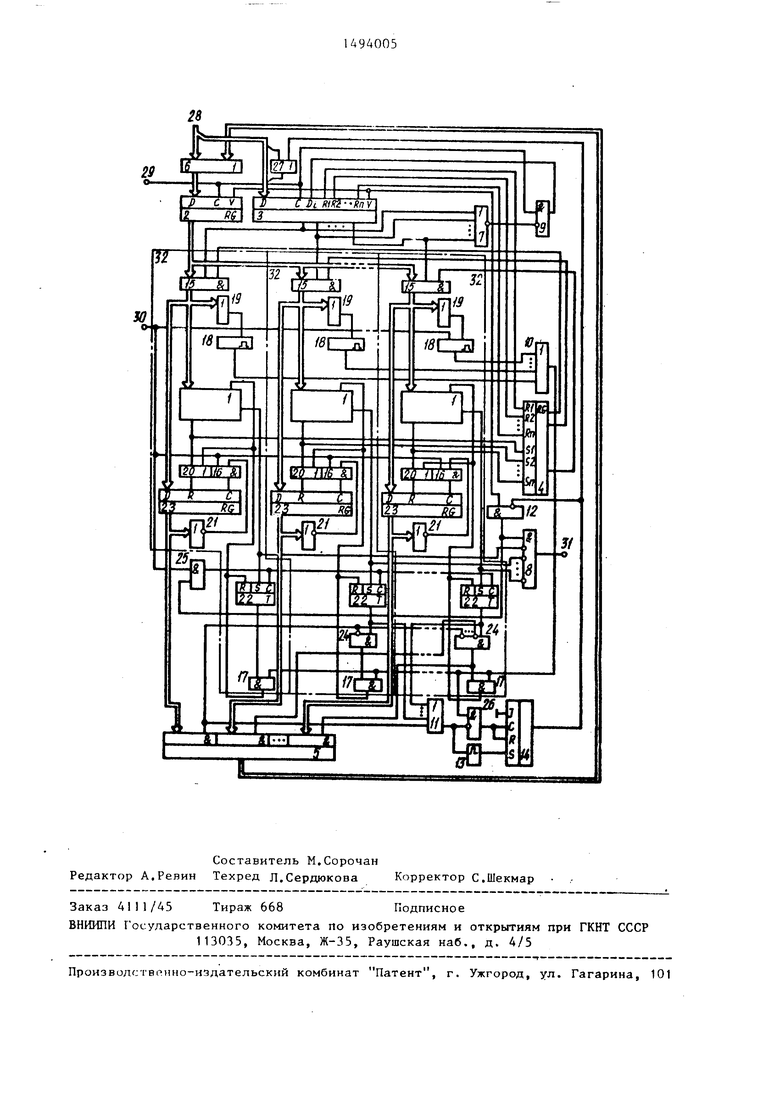

На чертеже изображена функциональная схема многопроцессорной системы.

Многопроцессорная система содержит процессоры 1, входной регистр 2, регистр 3 запроса, регистр 4 готовности, коммутатор 5, блок элементов ИЛИ 6, элемент Ш1И-НЕ 7, элементы И 8 и 9, элементы ШШ 10 и 11, элемент И 12, одновибратор 13, триггер 14, .блоки элементов И 15 каналов, элементы И 16 и 17 каналов, одновибраторы 18 каналов, элементы гШИ 19 и 20 каналов, элементы ИЛИ-НЕ 21 каналов, триггеры 22 каналов, регистры 23 каналов, элементы И 24 каналов, элементы И 25 и 26, элемент ИЛИ , 27, информационный вход 28, синхровходы 29 и 30, вьгход 31 и каналы 32.

Многопроцессорная система работает следующим образом.

В исходном состоянии регистр 3 запроса, регистр 2 кода задачи (входной регистр), регистры 23 каналов и триггер 14 находятся в нулевом состоянии (цепи установки в исходное состояние не показаны) Процессоры 1 всех каналов исправны и свободны Поэтому все разряды регистра 4 готовности находятся в единичном состоя-г НИИ. На выходе 31 многопроцессорной системы установлен единичный сигнал.

СО 4

сл

На вход 28 многопроцессорной системы поступает заявка для обслуживания, состоящая из двух частей: кода задачи и кода необходимого числа процессоров для решения этой задачи. Число необходимых процессоров определяется числом единиц во второй части кода заявки. Код записи задачи через блок элементов ШШ 6 поступает на вход регистра 2, а код необходимого числа процессоров поступает на вход регистра 3.

Так как в регистре 3 запроса в исходном состоянии хранится нулевая информация, то на выходе элемента ИЛИ-НЕ 7 будет единичный сигнал. Этот сигнал, поступая на входы регисров 2 и 3, разрешает запись в них кода задачи и кода необходимого числа процессоров соответственно. Запись осуществляется по заднему фронту импульса, поступающего с синхровхода 29 многопроцессорной системы на С-вх ды регистров 2 и 3.

С выхода регистра 2 код задачи поступает на информационные входы блоков элементов И 15 всех каналов. На вторые управляющие входы всех блоков элементов И 15 с разрядных выходов регистра 4 готовности поступают единичные разрешающие сигналы, так как все процессоры 1 в исходном состоянии свободны и исправны. На первые управляющие входы блоков элементов И 15 поступают единичные разрещающие сигналы с разрядных выходов регистра 3 запроса только для тех каналов, которым соответствуют единичные значе

НИН разрядов кода, записанного в этом регистре,. Через открытые блоки элементов И 15 код задачи поступает на информационные входы, выбранные процессорами 1, и на информационные входы регистров 23 соответствующих каналов.

В каналах, в процессоры которых поступила задача на выполнение, и на выходах элементов ИЛИ 19 появятся единичные сигналы. Эти сигналы по- tтyпят на разрещающие входы соответствующих одновибраторов 18, которые по переднему фронту синхроимпульса со входа 30 сформируют импульс. Этот импульс, поступая на соответствующие входы регистра 3 запроса и регистра 4 готовности, устанавливает их разряды, соответствующие занятым процессорам 1, в нулевое состояние, Синхроимпульс со входа 30, поступая через открытый элемент И 16 на С-входы регистров 23 всех каналов, разрешает запись кода задачи с выходов блоков элементов И 15 тех каналов, которые приняли задачу на обслуживание.

0

0 5

5

0

5

0

5

0

Если все процессоры 1, назначенные для выполнения задачи, свободны и приняли задачу к исполнению, то на выходе элемента ИЛИ-НЕ 7 будет вновь единичный сигнал.,Этот сигнал через открытый элемент И 12 и открытый по 5 другим входам (так как все процессоры исправны ) элемент И 8 поступит на выход 3 готовности ,в результате чего многопроцессорная система будет готова к приему очередной заявки по входу 28.

Если некоторые из назначенных процессоров 1 заняты выполнением ранее поступивших задач, то все разряды регистра 3 запроса будут сброшены в. нуль. На выходе элемента ИЛИ-НЕ 7 будет нулевой сигнал, который запрещает приход очередной заявки на вход 28о Действуя на инверсный вход элемента И 9, этот сигнал разрешает приход импульса с синхронизирующего входа 29 на сдвигающий вход регистра 3 запроса. По этому импульсу производится сдвиг содержимого регистра 3 влево на один разряд. Процесс циклического сдвига информации продолжается до тех пор, пока необходимое число процессоров не будет назначено для выполнения данной задачи. После этог о на выходе элемента ИЛИ-НЕ 7 появляется единичный сигнал, поступающий на выход 31 и разрешающий подачу очередной заявки на вход 28.

Рассмотрим работу многопроцессорной системы в случае отказа одного или нескольких процессоров.

Предположим одновременно отказали два процессора: 1,М и 1,К, Отказавшие процессоры выставят на своих сигнальных выходах единичные сигналы, которые поступят на единичные S-входы триггеров 22 соответствующих каналов и по заднему фронту синхроимпульса, поступающего со входа 30 через открытый элемент И 25 на С-входы триггеров 22 каналов, запишутся в триггеры 22 М-го и К-го каналов, С выходов триггеров 22 оба единичные сигнала поступят на прямые входы эле

ментов И 2А.М и 24.К. Но сигнал появится на выходе только элемента И 24,М, так как с его выхода единичный сигнал, поступающий на инверсные входы элементов И 24 всех более старших каналов, закроет их. Будет закрыт также и элемент И 24.К.

Единичный сигнал с выхода элемент И 24.М откроет соответствующий вход (информационный) коммутатора 5 и код задачи отказавшего процессора из регистра 23.М через коммутатор 5 и вторые входы блока элементов ИЛИ 6 поступит на входы входного регистра 2. Одновременно единичный сигнал, сформированный элементом ИЛИI1, запустит передним фронтом одновибрато- ра 13.. Короткий импульс с одновибра- тора 13, поступая на единичный S-вход триггера 14, установит его в единичное состояние. Единичный сигнал с выхода триггера 14 через элемент ИЛИ 27 поступит на вход первого разряда регистра 3 запроса.

Задним фронтом синхроимпульса, поступающего с синхровхода 29, код задачи отказавшего процессора запишется во входной регистр 2, а единица

0

кроет элемент И 26, в результате чего по заднему фронту импульса с выхода элемента ИЛИ 10 триггер 14 установится в нуль и многопроцессорная система будет готова к обслуживанию следуюшлх заявок.

В случае отказавших процессоров на выходе элемента 11ЛИ 1 1 будет сохраняться единичный сигнал, в результате чего элемент И 26 останется закрытым по своему инверсному входу ; и триггер 14 останется в единичном состоянии. Запись заявок от вновь

5 отказавших процессоров 1 будет запрещена, так как остается закрытым элемент И 25 и синхроимпульсы со входа 30 на С-входы триггеров 22 пройти не могут„

После обнуления триггера 22.М за - кроется элемент И 24„М и откроется элемент И 24.К,в результате чего повторится процесс поиска и передачи свободному и исправному процессору.

5 I,R задачи,которую решал отказавший процессор 1,К,

После перераспределения задачи от второго отказавшего процессора 1.К на выходе элемента ИЛИ 11 появится

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Многопроцессорная система | 1989 |

|

SU1695318A1 |

| Устройство для распределения заявок по процессорам | 1990 |

|

SU1798782A1 |

| Устройство приоритета | 1990 |

|

SU1742820A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1837309A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах. Цель изобретения - повышение достоверности функционирования системы за счет перераспределения заданий с отказавших процессоров на работающие. Многопроцессорная система содержит три регистра, коммутатор, триггер, одновибратор, блок элементов ИЛИ, три элемента ИЛИ, пять элементов И, элемент ИЛИ-НЕ и каналы, каждый из которых содержит процессор, регистр, триггер, блок элементов И, два элемента ИЛИ, одновибратор, три элемента И. При отказе двух и более процессоров устройство перераспределяет задачи, решаемые на этих процессорах, код которых хранится в регистрах каналов, на другие (работающие и свободные) процессоры системы. 1 ил.

(число потребных процессоров) запишет-зо нулевой сигнал, который откроет элеся в первый разряд регистра 3 запроса.

Далее устройство работает как и при обслуживании очередной заявки

После того, как найден процессор для выполнения заявки от отказавшего процессора 1.К, на выходе элемента ИЛИ 10 появляется единичный импульс, поступивший с выхода одновибраторов 18.Р канала, процессор 1.Р которого принял к исполнению данную заявку. При этом очередной синхроимпульс со входа 30 не может записать запрос от вновь отказавшего в триггере 22 какого-либо канала, так как элемент И 25 закрыт нулевым сигналом, поступающим с выхода элемента И 12, на вход которого поступает единичный сигнал с выхода триггера 14.

Импульсный сигнал с выхода элемен та ИЛИ 10 пройдет через открытый элемент И 17.М и своим передним фронтом сбросит в нуль триггер 22.М и регистр 23.М, а также,поступая на управляющий вход процессора 1 .М, снимет с его сигнального выхода единичный сигнал. Если отказавший процессор единст- венный, то на выходе элемента ИЛИ 11 появится нулевой сигнал, который от5

Нрнт и 26, в результате чего импульс одновибратора 18,Б, пройдя через элемент ИЛИ 10, своим задним фронтом переведет триггер 14 в нулевое состояние. После этого откроется элемент И 12, а следовательно, и элемент И 25. Если к этому моменту времени появились отказавшие процессоры, то элемент И 8 останется закрытым, на вы0 ходе 31 останется нулевой сигнал и подача новых заявок на вход 28 будет запрещена. По очередному импульсу, поступившему на синхровход 30, заявки от отказавших процессоров запишутг

5 ся в триггеры 22 соответствующих каналов и процесс их обслуживания во зобновится.

Если после обслуживания отказавших процессоров все остальные процессоры находятся в исправном состоянии, то элемент И 8 открывается и на выходе 31 появляется единичный сигнал, разрешающий подачу новых заявок на информационные входы 28,

е После успешного выполнения задачи соответствующий процессор 1 вццает единичный сигнал на выход 32, который устанавливает соответственный разряд регистра 4 готовгюсти в единичное со- ,

стояние и, поступая через элемент ИЛИ 16 на вход сброса регистра 23 своего канала, сбрасывает его в нуль После этого этот процессор готов к выполнению следующей задачи.

Синхронизирующие импульсы со вход 29 должны опережать по фазе синхро- ниэирую1цие импульсы со входа 30, По заднему фронту синхроимпульса со вхо да 29 осуществляется запись информации в регистры 2 и 3. После этого по переднему фронту синхросигнала со входа 30 осуществляется запись информации в регистры 23 каналов, а также осуществляется сброс соответствующих .разрядов в регистрах 3 и 4. Если в первом такте синхропоследовательнос- ти со входа 29 выяснится, что числа назначенных процессоров не хватает, то по следующему импульсу этой последовательности произойдет сдвиг информации в регистре 3 влево на один разряд. И так до тех пор, пока потребное число процессоров не будет обеспечено

Задержка импульсов со входа 30 по отнощению к импульсам со входа 29 должна быть не меньше, чем время по следовательного срабатывания регист- ра 3, блока элементов И 15 канала и элемента ИЛИ 19 канала.

Формула изобретения

Многопроцессорная система, содержащая регистр запроса, регистр готовности, первый, второй, третий и четвертый элементы И, первьш, второй и третий элементы ИЛИ, элемент , п каналов (где п - число процессоров) и в каждом канале - регистр, блок элементов И, первый и второй элементы ИЛИ, первый второй и трети элементы И, процессор,причем выходы регистра запроса подключены к первым стробирующим входам блоков элементов И соответствующих каналов, выходы которых соединены с информационными входами процессоров соответствующих каналов, выходы регистра готовности подключены к вторым стробирующим входам блоков элементов И соответ- ствуюп1их каналов, в каждом канале выходы блоков элементов И подключены ко входам первого элемента ИЛИ, выходы регистра запроса подключены к входам элем€ нта ИЛИ-НЕ, выход которого подключон к инверсному входу первого

j 0 5

о

5

Q д g

элемента И, выход которого подключен входу сдвига регистра запросов, в каждом канале выход первого элемента И подключен к входу записи регистра, отличающаяся тем, что, с целью повыщения достоверности функционирования за счет перераспределения заданий с отказавших процессоров на работающие, в нее дополнительно введены входной регистр, блок элементов ИЛИ, коммутатор, триггер, одновиб- ратор, пятый элемент И, а в каждый из каналов - триггер, элемент ШШ-НЕ, одновибратор, причем информационный вход системы подключен к первому входу блока элементов ШШ и к информационному входу регистра запроса, кроме входа первого информационного разряда регистра запроса, который подключен к выходу первого элемента ИЛИ, к первому входу первого элемента ИЛИ подключен соответствующий разряд информационного входа, выходы блока элементов ИЛИ подключены к информационным входам входного регистра, выход которого подключен к информационным входам блоков элементов И каналов, в каждом канале выход блока элементов И подключен к информационному входу регистр;, выход которого подключен к соответствующему информационному входу коммутатора, разрядные выходы которого подключены к второму входу блока элементов ИЛИ, во всех каналах первый сигнальный выход процессора подключен к входу установки соответствующего разряда регистра готовности, а второй сигнальный выход ;фоцессора в каждом канале соеди„ нен с соответствующим инвepcны i входом второго элемента И и входом установки триггера соответствующего канала, прямой выход триггера каждого канала, кроме первого, соединен с прямым входом второго элемента И соответствующего канала и с соответствующим входом второго элемента ИЛИ, прямой выход триггера первого канала подключен к первым инверсным входам вторых элементов И всех других каналов, к первому входу третьего элемента И первого канала, к первому ляющему входу коммутатора и к перво - му входу второго элемента ИЛИ, выходы вторых элементов И всех каналов, кроме первого, подключены к соответствующим входам ко чнутатора, к первым входам третьих элементов И соответствующих каналов, в каддом канале выход третьего элемента И сбединен с входом сброса триггера, с входом сброса соответствующего процессора и с вторым входом второго элемента ИЛИ канала, выход которого подключен к входу сброса регистра канала, в каждом канале выходы регистра подключены к входам элемента ИЛИ-НЕ , выход которого подключен к первому входу первого элемента И канала, выход первого элемента ИЛИ каждого канала подключен к стробирующему входу одно- вибратора этого же канала, выход KoTO рого подключен к соответствующим входам сброса регистра запроса, регистра готовности и к соответствующему входу третьего элемента ИЛИ, выход которого подключен к прямому входу третьего элемента И и к вторым входам третьих элементов И каналов, выход второго элемента ИЛИ подключен к инверсному входу третьего элемента И и через одновибратор - к входу уста- новки триггера, вход триггера подключен к общей шине логического нуля, выход третьего элемента И подключен к К-входу и к синхронному входу триггера, выход триггера подключен к второму входу первого элемента ИЛИ и к инверсному входу четвертого элемента И, выход которого подключен к прямому входу второго и к Первому входу пятого элементов И, выход пятого элемента И подключен к синхровходам триггеров каналов , выход элемента ИЛИ-НЕ подключен к прямому входу четвертого элемента И, к входам разрешения записи регистра запроса и входного регистра, первый синхровход системы устройства подключен к входам записи регистра запроса и входногр регистра, а также к прямому входу первого элемента И, второй синхровход системы подключен к вторым входам первых элементов И, второй синхровход системы подключен к вторым вхо- .дам первых элементов И и к входам запуска одновибраторов каналов, к второму входу пятого элемента И, выход второго элемента И является разрешающим выходом системы, выход второго элемента И К-го канала (, N-1) соединен с К-ми входами вторых элементов всех каналов с (К+1)--го по N-й.

29

М

CS

3

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заявок по процессорам | 1983 |

|

SU1151965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-15—Публикация

1987-11-10—Подача