Изобретение относится к электросвязи, предназначено для преобразования аналоговых сигналов в цифровую Форму и может быть использовано в специализированных электронных АТС малой емкости и средней емкости, а также в других областях электронной техники, где требуется высококачественное аналого-цифровое преобразование сигналов.

Целью изобретения является расширение динамического диапазона преобразуемых сигналов

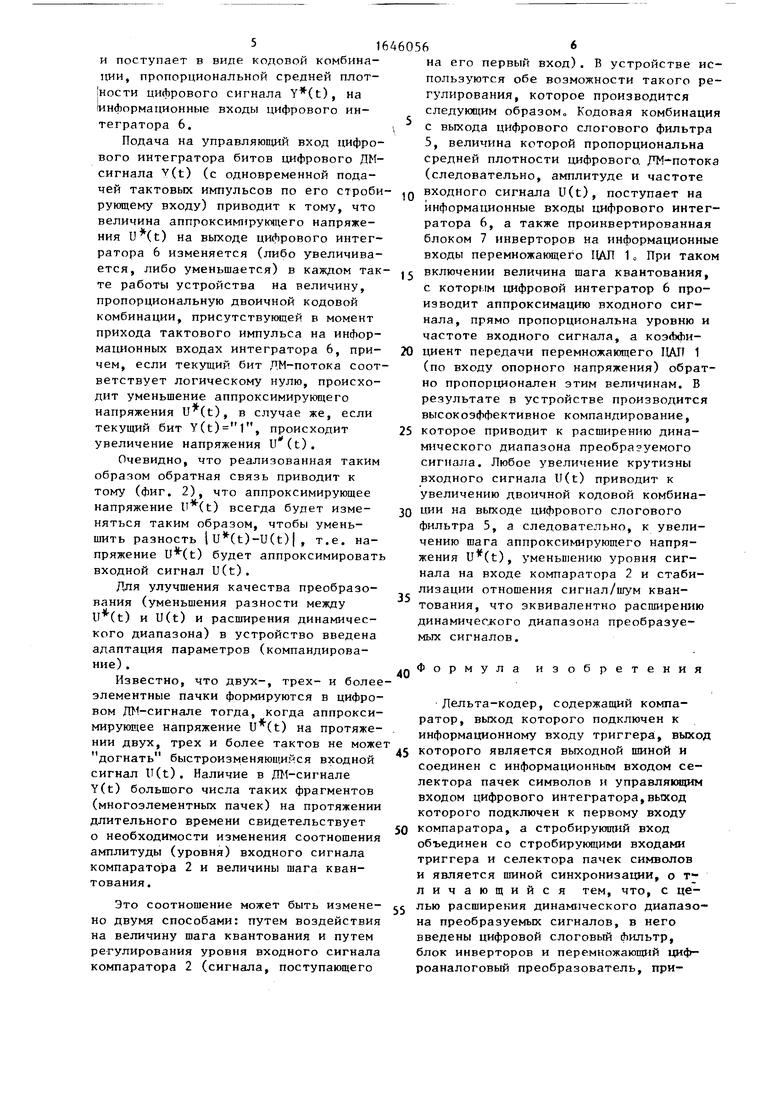

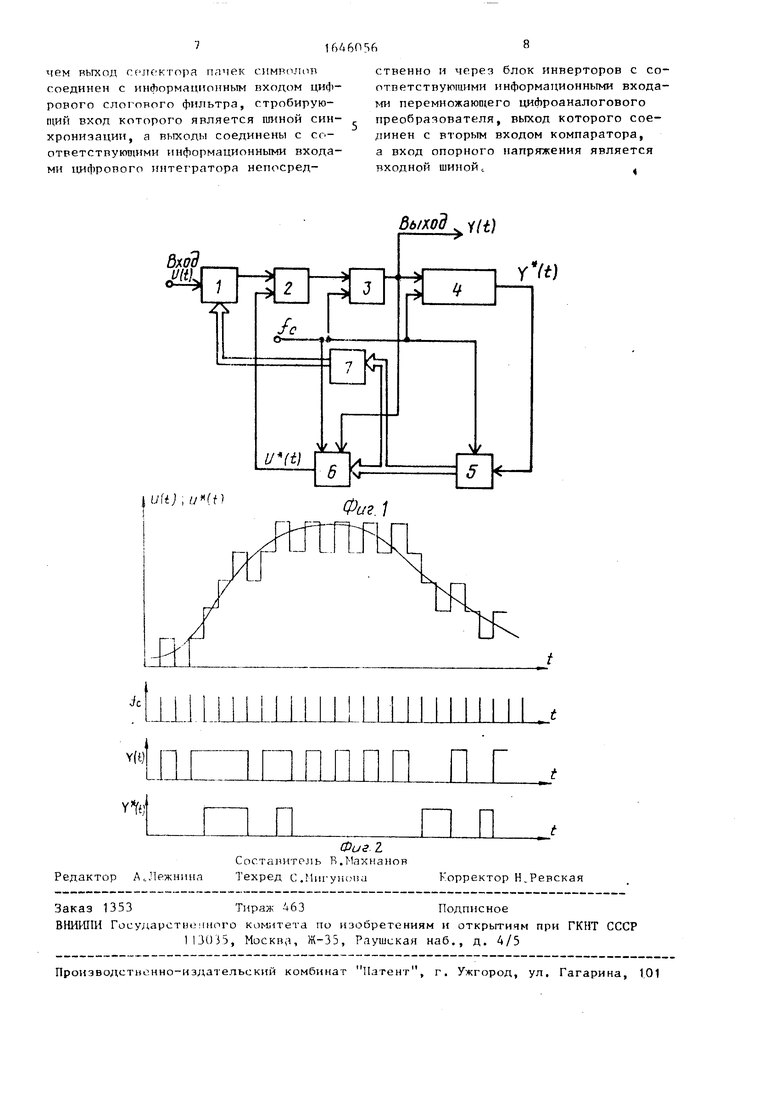

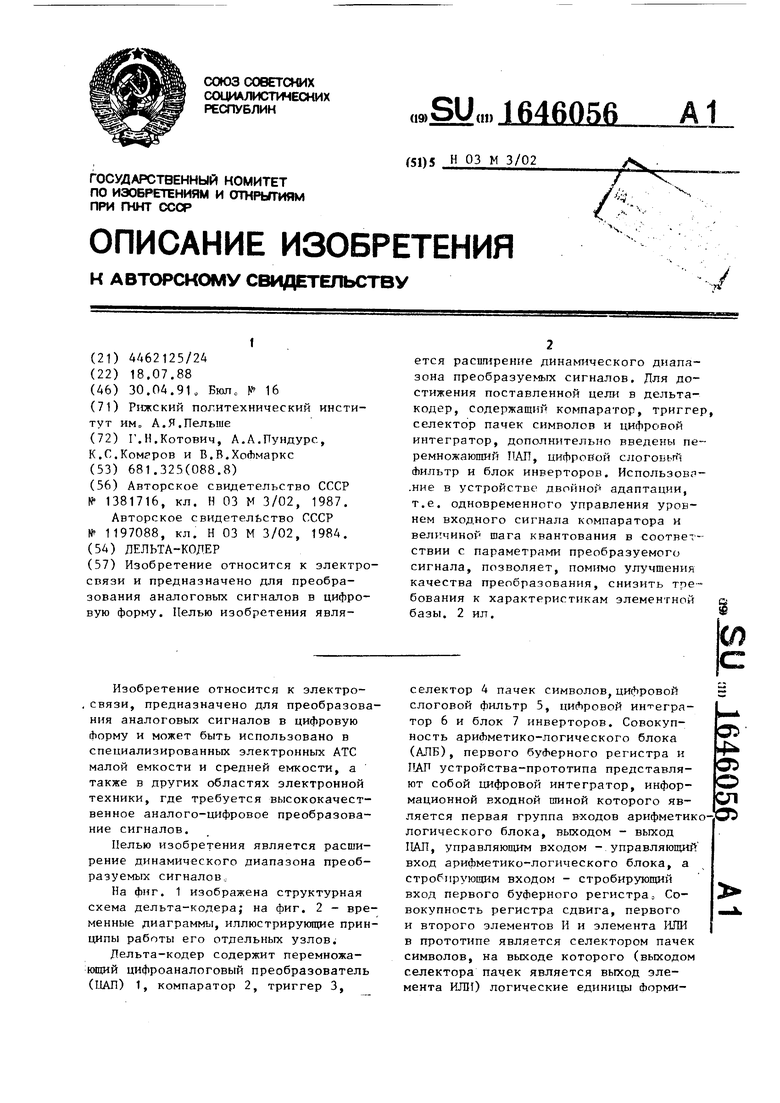

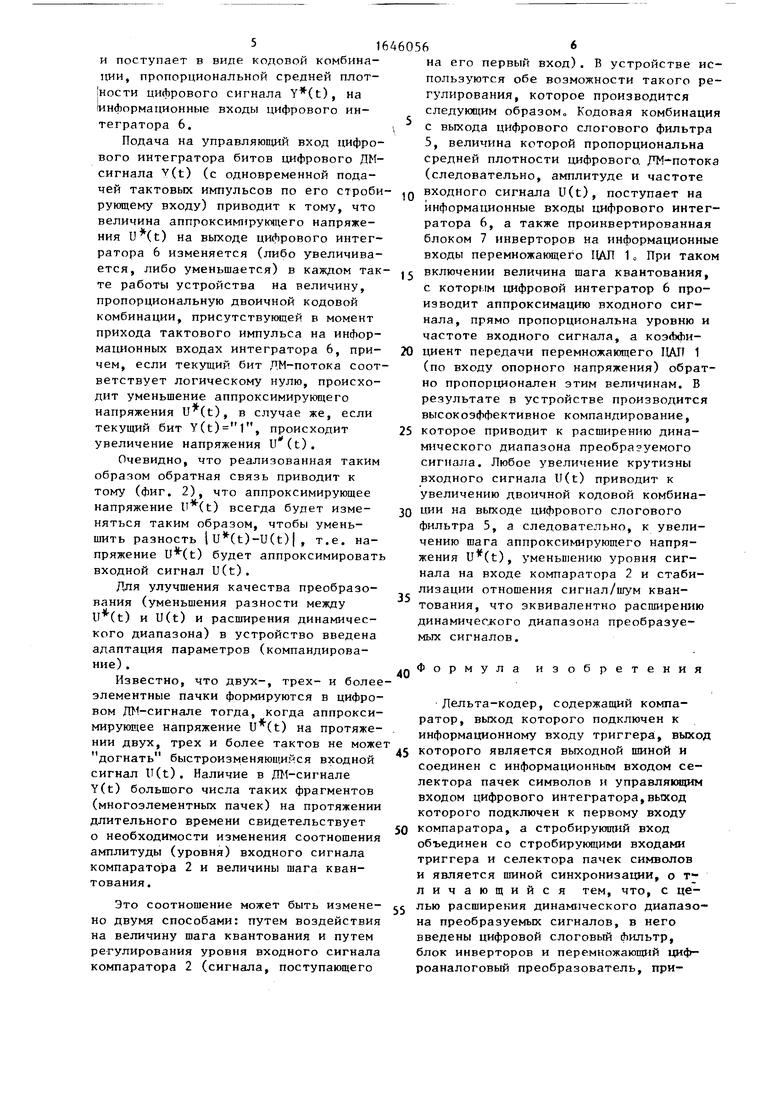

На Фиг. 1 изображена структурная схема дельта-кодера; на фиг. 2 - временные диаграммы, иллюстрирующие принципы работы его отдельных узлов.

Дельта-кодер содержит перемножающий цифроаналоговый преобразователь (ПАП) 1, компаратор 2, триггер 3,

селектор 4 пачек символов,цифровой слоговой фильтр 5, цифровой интегратор 6 и блок 7 инверторов. Совокупность арифметико-логического блока (АЛБ), первого буферного регистра и ПАП устройства-прототипа представляют собой цифровой интегратор, информационной входной шиной которого является первая группа входов арифметико- логического блока, выходом - выход ПАЛ, управляющим входом - управляющий вход арифметико-логического блока, а стробирующим входом - стробирующин вход первого буферного регистра, Совокупность регистра сдвига, первого и второго элементов И и элемента ИЛИ в прототипе является селектором пачек символов, на выходе которого (выходом селектора пачек является выход элемента ИЛИ) логические единицы ФормиО54. О5 О СП

да

руются в случае наличия в дельта-мо- дулированном (ДМ) потоке двух и более элементных пачек (следующих подряд однотипных символов), Информаци- онным и стробирующим входами селектора пачек являются информационный и стробирующий входы регистра сдвига соответственно о

В качестве цифрового слогового Фильтра, в частности, может быть .использован цифровой ДМ-фильтр, Anna-- ратурно данный Фильтр может быть реализован множеством способов, например на регистре сдвига, наборе бу- Ферных регистров с параллельной записью и сумматоре, причем на информационный вход Фильтра поступает цифровой ДМ-поток, который с приходом тактовых импульсов на гтробирующий вход регистра заполняет его разряды,, Каждый бит ДМ-потока поступает на один из информационных входов соответствующего буферного регистра, все остальные входы которого заземлены. Исполь- зование тех или иных входов буферных регистров зависит от конкретных требований к характеристикам цифрового слогового Фильтра. Характеристики Фильтра, в свою очередь, определяют- ся конкретными условиями применения дельта-кодера, а также типом и параметрами входного сигнала„

Появление логических единиц в разрядах регистра сдвига вызывает Форми- рование заданных двоичных чисел на выходах соответствующих буферных регистров. Просуммировавптись сумматором, эти числа Формируют отклик цифрового фильтра на входное воздействие.

Дельта-кодер работает следующим образомо

Входной аналоговый сигнал U(t) поступает на вход опорного напряжения перемножающего ЦАП 1 и появляется на его выходе, ослабленный в К раз Коэффициент ослабления К определяется двоичной кодовой комбинацией на информационных входах перемножающего ПАТ 1:

иеых

П иех

Аде

2Г

г - разрядность перемножающего

ЦАП 1;

А. - кодовая комбинация на информационных входах перемножающего ПАП 1, представленная

$ 0 5 0

,. 0

5

0

5

в десятичной системе счисления .

Если предположить, что в момент начала работы двоичная кодовая комбинация на выходе цифрового слогового фильтра 5 соответствует числу 0 в десятичной системе счисления (комбинация 000...000), то проинвертирован- ная блоком 7 инверторов комбинация ( 111... 111) на информационных входах перемножающего ПАП 1 соответствует числу -1 в десятичной системе счисления, а следовательно, входной сигнал U(t) коммутируется на выход перемножающего ПАП с максимальным коэффициентом передачи.

Этот сигнал поступает на вход компаратора 2, где сравнивается с аппроксимирующим сигналом и(О, присутствующим на другом входе компаратора 2„ В случае, если U(t)U(t), на выходе компаратора 2 формируется логический ноль. При U(t) L U(t) компаратор 2 выдает логическую единицу. Двухуровневый сигнал с выхода компаратора 2 поступает на информационный вход триггера 3, на стробирующий вход которого подаются тактовые импульсы с шины синхронизации. С приходом каждого тактового импульса логический потенциал, присутствующий на информаци- онном входе триггера 3, записывается в него, появляется на его выходе и поддерживается там как минимум до прихода следующего импульса тактовой последовательности. Таким образом, Формируются биты выходного ДМ-сигна- ла, каждый из которых поступает на выход устройства, а также одновременно на информационный вход селектора А пачек символов и на управляющий вход цифрового интегратора 6. С приходом очередных тактовых импульсов Фрагмент цифрового ДМ-потока последовательно записывается в селектор 4 пачек символов и анализируется последним на предмет наличия двух и более элементных пачек. Принцип Формирования выходного сигнала селектора А пачек символов при использовании в нем двухразрядного (для наглядности) регистра сдвига иллюстрируется временными диаграммами на Лиг. 2.

Сигнал Y (t) с выхода селектора А пачек символов (фиг. 1) поступает на информационный вход цифрового слогового фильтра 5, усредняется им

и поступает в виде кодовой комбинации, пропорциональной средней плот- ности цифрового сигнала Y(t), на информационные входы цифрового интегратора 6.

Подача на управляющий вход цифрового интегратора битов цифрового ДМ- сигнала v(t) (с одновременной подачей тактовых импульсов по его строби рующему входу) приводит к тому, что величина аппроксимирующего напряжения U (t) на выходе цифрового интегратора 6 изменяется (либо увеличивается, либо уменьшается) в каждом такте работы устройства на величину, пропорциональную двоичной кодовой комбинации, присутствующей в момент прихода тактового импульса на информационных входах интегратора 6, причем, если текущий бит ДМ-потока соответствует логическому нулю, происходит уменьшение аппроксимирующего напряжения U (t), в случае же, если текущий бит Y(t)l, происходит увеличение напряжения U(t).

Очевидно, что реализованная таким образом обратная связь приводит к тому (фиг. 2), что аппроксимирующее напряжение U(t) всегда будет изменяться таким образом, чтобы уменьшить разность { U(t)-U(t) | , т.е. напряжение (t) будет аппроксимировать входной сигнал U(t).

Для улучшения качества преобразования (уменьшения разности между U(t) и U(t) и расширения динамического диапазона) в устройство введена адаптация параметров (компандирова- ние) .

Известно, что двух-, трех- и более элементные пачки формируются в цифровом ДМ-сигнале тогда, когда аппроксимирующее напряжение U(t) на протяжении двух, трех и более тактов не може догнать быстроизменяющийся входной сигнал U(t). Наличие в ДМ-сигнале Y(t) большого числа таких фрагментов (многоэлементных пачек) на протяжении длительного времени свидетельствует о необходимости изменения соотношения амплитуды (уровня) входного сигнала компаратора 2 и величины шага квантования.

Это соотношение может быть изменено двумя способами: путем воздействия на величину шага квантования и путем регулирования уровня входного сигнала компаратора 2 (сигнала, поступающего

0

5

на его первый вход). В устройстве используются обе возможности такого регулирования, которое производится следующим образом Кодовая комбинация с выхода цифрового слогового фильтра 5, величина которой пропорциональна средней плотности цифрового ДМ-потока (следовательно, амплитуде и частоте входного сигнала U(t), поступает на информационные входы цифрового интегратора 6, а также проинвертированная блоком 7 инверторов на информационные входы перемножающего НАЛ 1 о При таком включении величина шага квантования, с которнм цифровой интегратор 6 производит аппроксимацию входного сиг

частоте входного сигнала, а коэФФи- циент передачи перемножающего ДАЛ 1 (по входу опорного напряжения) обратно пропорционален этим величинам. В результате в устройстве производится высокоэффективное компандирование, которое приводит к расширению динамического диапазона преобразуемого сигнала. Любое увеличение крутизны входного сигнала U(t) приводит к увеличению двоичной кодовой комбинации на выходе цифрового слогового фильтра 5, а следовательно, к увеличению шага аппроксимирующего напряжения U(t), уменьшению уровня сигнала на входе компаратора 2 и стабилизации отношения сигнал/шум квантования, что эквивалентно расширению динамического диапазона преобразуемых сигналов.

40

Формула изобретения

Дельта-кодер, содержащий компаратор, выход которого подключен к информационному входу триггера, выход 5 которого является выходной шиной и соединен с информационным входом селектора пачек символов и управляющим входом цифрового интегратора,выход которого подключен к первому входу компаратора, а стробирующий вход объединен со стробирующими входами триггера и селектора пачек символов и является шиной синхронизации, о т- личающийся тем, что, с целью расширения динамического диапазона преобразуемых сигналов, в него введены цифровой слоговый Фильтр, блок инверторов и перемножающий циф- роаналоговый преобразователь, при0

5

чем выход селектора пачек символов соединен с информационным входом цифрового слогового фильтра, стробирую- щий вход которого является шиной синхронизации, а выходы соединены с соответствующими информационными входами цифрового интегратора непосредственно и через блок инверторов с соответствующими информационными входами перемножающего циФроаналогового преобразователя, выход которого соединен с вторым входом компаратора, а вход опорного напряжения является входной шиной с4

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

| Дельта-модулятор | 1978 |

|

SU752799A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-модулятор | 1987 |

|

SU1474850A1 |

| Дельта-кодер | 1988 |

|

SU1605310A1 |

| Дельта-модулятор | 1984 |

|

SU1203707A1 |

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

Изобретение относится к электросвязи и предназначено для преобразования аналоговых сигналов в цифровую форму. Целью изобретения является расширение динамического диапазона преобразуемых сигналов. Для достижения поставленной цели в дельта- кодер, содержащий компаратор, триггер, селектор пачек символов и цифровой интегратор, дополнительно введены перемножающий ПАП, цифровой слогоььгм Фильтр и блок инверторов. Использовл- .ние в устройстве двойной адаптации, т.е. одновременного управления уровнем входного сигнала компаратора и величиной шага квантования в соответствии с параметрами преобразуемого сигнала, позволяет, помимо улучшения качества преобразования, снизить тпе- бования к характеристикам элементной базы. 2 ил.

) ,U(il

Фиг.1

П П П П П П Г ,

п п п ,

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-30—Публикация

1988-07-18—Подача