ь

ю сг со

ND

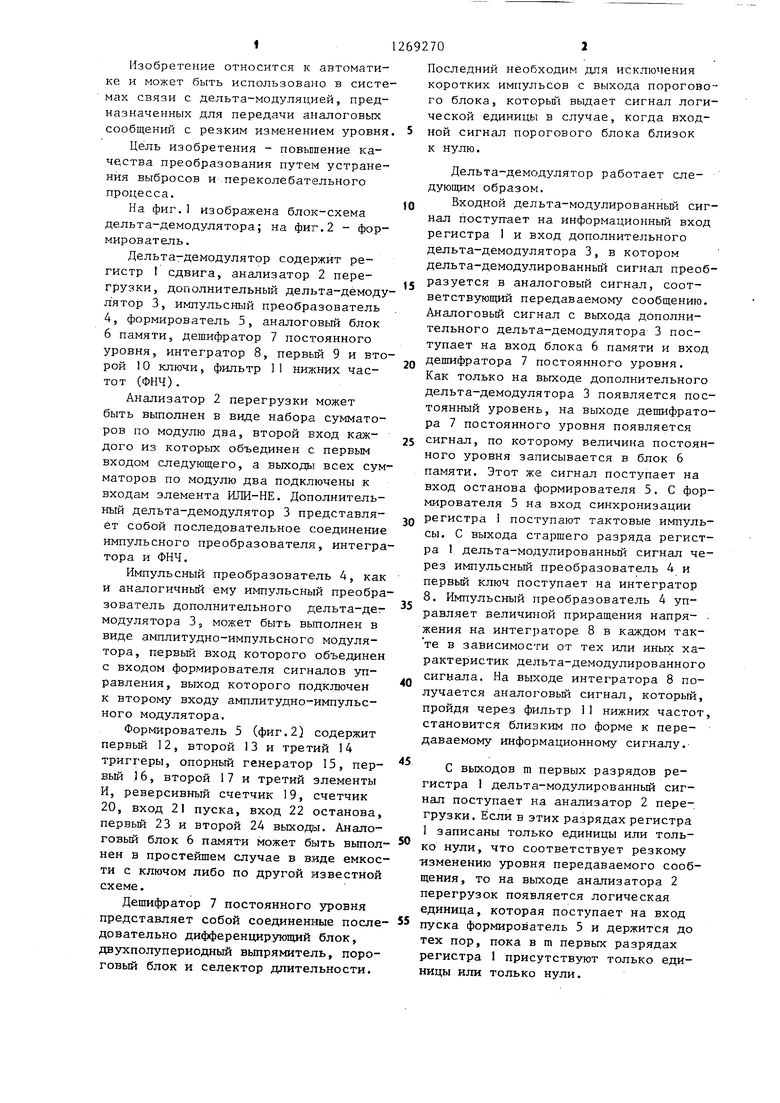

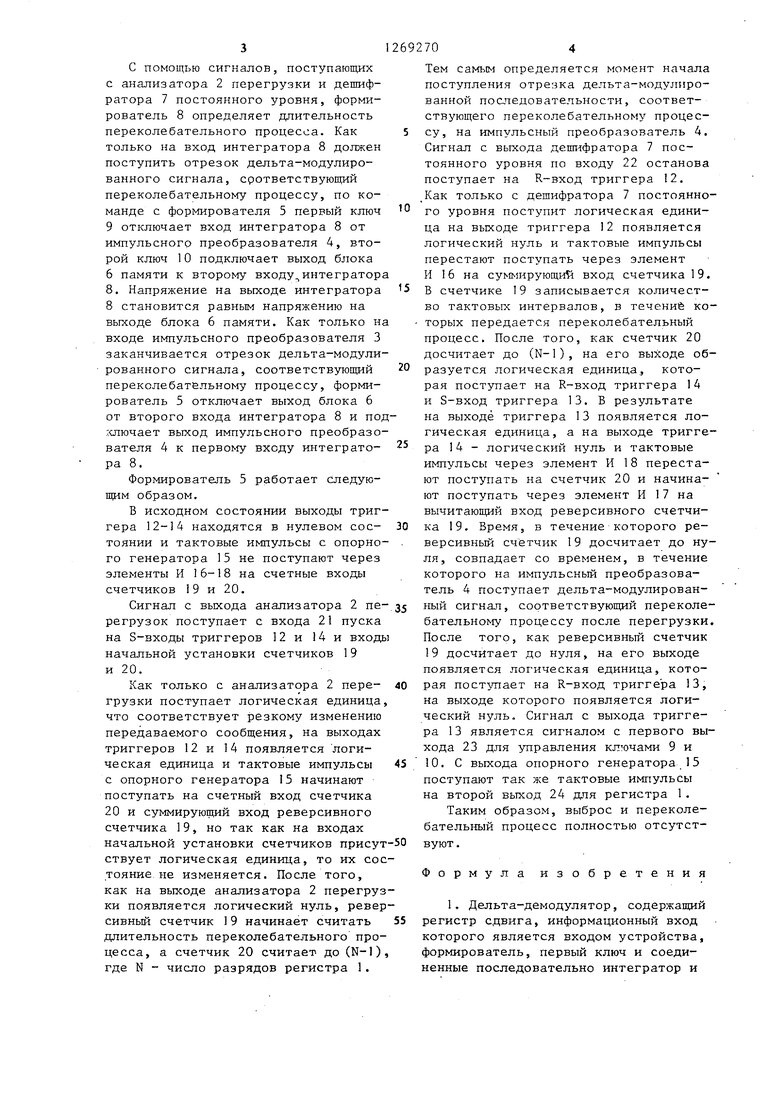

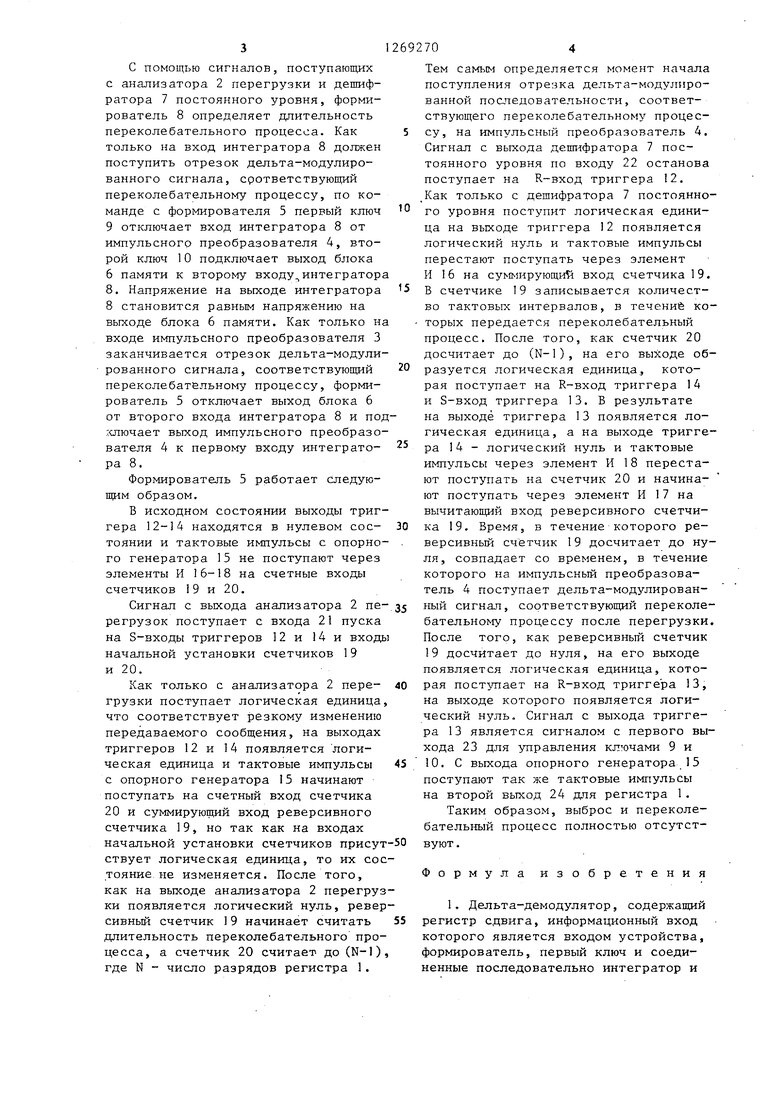

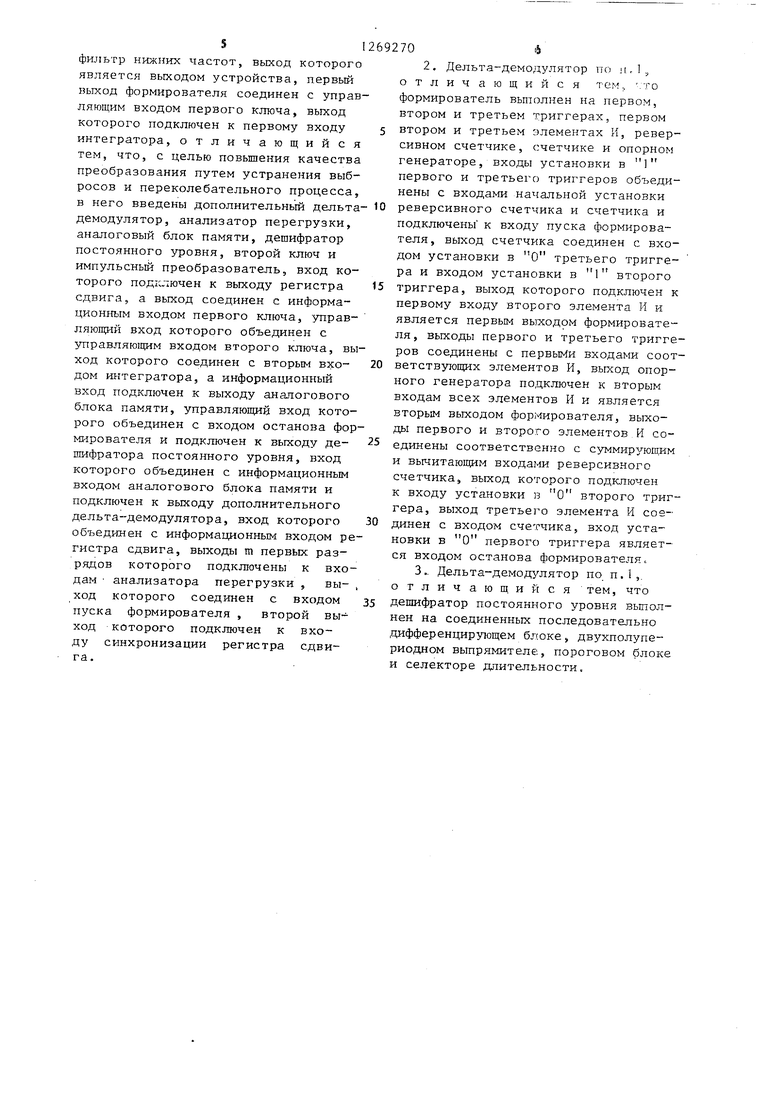

Изобретение относится к автоматике и может быть использовано в систе мах связи с дельта-модуляцией, предназначенных для передачи аналоговых сообщений с резким изменением уровня Цель изобретения - повьяление кач« ства преобразования путем устранения выбросов и .переколебательного процесса. На фиг.1 изображена блок-схема дельта-демодулятора; на фиг.2 - формирователь. Дельта-демодулятор содержит регистр 1 сдвига, анализатор 2 перегрузки, дополнительный дельта-демоду лятор 3, импульсный преобразователь 4, формирователь 5, аналоговый блок 6 памяти, дешифратор 7 постоянного уровня, интегратор 8, первьш 9 и вто рой 10 ключи, фильтр 1 нижних частот (ФНЧ). Анализатор 2 перегрузки может быть выполнен в виде набора сумматоров по модулю два, второй вход каждого из которых объединен с первым входом следующего, а выходы всех сум маторов по модулю два подключены к входам элемента ИЛИ-НЕ. Дополнительный дельта-демодулятор 3 представляет собой последовательное соединение импульсного преобразователя, интегра тора и ФНЧ. Импульсный преобразователь 4, как и аналогичный ему импульсный преобра зователь дополнительного дельта-дег модулятора 3, может быть выполнен в виде амплитудно-импульсного модулятора, первый вход которого объединен с входом формирователя сигналов управления, выход которого подключен к второму входу амплитудно-импульсного модулятора. Формирователь 5 (фиг.2) содержит первый 12, второй 13 и третий 14 триггеры, опорный генератор 15, первый 16, второй 17 и третий элементы И, реверсивный счетчик 19, счетчик 20, вход 21 пуска, вход 22 останова первьй 23 и второй 24 выходы. Аналоговый блок 6 памяти может быть вьтол нен в простейшем случае в виде емкос ти с ключом либо по другой известной схеме. Дешифратор 7 постоянного уровня представляет собой соединенные после довательно дифференцирующий блок, двухполупериодный вьтрямитель, пороговый блок и селектор длительности. Последний необходим для исключения коротких импульсов с выхода порогового блока, KOTopbDi вьщает сигнал логической единицы в случае, когда входной сигнал порогового блока близок к нулю. Дельта-демодулятор работает следующим образом. Входной дельта-модулированный сигнал поступ-ает на информационный вход регистра 1 и вход дополнительного дельта-демодулятора 3, в котором дельта-демодулированньоЧ сигнал преобразуется в аналоговый сигнал, соответствующий передаваемому сообщению. Аналоговый сигнал с выхода дополнительного дельта-демодулятора 3 поступает на вход блока 6 памяти и вход дешифратора 7 постоянного уровня. Как только на выходе дополнительного дельта-демодулятора 3 появляется постоянный уровень, на выходе дешифратора 7 постоянного уровня появляется сигнал, по которому величина постоянного уровня записывается в блок 6 памяти. Этот же сигнал поступает на вход останова формирователя 5. С формирователя 5 на вход синхронизации регистра I поступают тактовые импульсы. С выхода старшего разряда регистра 1 дельта-модулированный сигнал через импульсный преобразователь 4 и первый ключ поступает на интегратор 8. Импульсный преобразователь 4 управляет величиной приращения напря- . жения на интеграторе 8 в каждом такте в зависимости от тех или иных характеристик дельта-демодулированного сигнала. На выходе интегратора 8 получается аналоговый сигнал, который, пройдя через фильтр I1 нижних частот, становится близким по форме к передаваемому информационному сигналу.С вьпх:одов m первых разрядов регистра I дельта-модулированный сигнал поступает на анализатор 2 перегрузки. Если в этих разрядах регистра 1 записаны только единицы или только нули, что соответствует резкому изменению уровня передаваемого сообщения, то на выходе анализатора 2 перегрузок появляется логическая единица, которая поступает на вход пуска формирователь 5 и держится до тех пор, пока в m первых разрядах регистра I присутствуют только единицы или только нули.

с помощью сигналов, поступаютцих с анализатора 2 перегрузки и дешифратора 7 постоянного уровня, формирователь 8 определяет длительность переколебательного процесса. Как только на вход интегратора 8 должен поступить отрезок дельта-модулированного сигнала, срответствующий переколебательному процессу, по команде с формирователя 5 первый ключ 9 отключает вход интегратора 8 от импульсного преобразователя 4, второй ключ 10 подключает выход блока 6 памяти к второму входу интегратора 8. Напряжение на выходе интегратора 8 становится равным напряжению на выходе блока 6 памяти. Как только на входе импульсного преобразователя 3 заканчивается отрезок дельта-модулированного сигнала, соответствующий переколебательному процессу, формирователь 5 отключает выход блока 6 от второго входа интегратора 8 и под ;слючает выход импульсного преобразователя 4 к первому входу интегратора 8.

Формирователь 5 работает следующим образом.

В исходном состоянии выходы триггера 12-14 находятся в нулевом состоянии и тактовые импульсы с опорного генератора 15 не поступают через элементы И 16-18 на счетные входы счетчиков 19 и 20.

Сигнал с выхода анализатора 2 перегрузок поступает с входа 21 пуска на S-входы триггеров 12 и 14 и входы начальной установки счетчиков 19 и 20.

Как только с анализатора 2 перегрузки поступает логическая единица, что соответствует резкому изменению передаваемого сообщения, на выходах триггеров 12 и 14 появляется логическая единица и тактовые импульсы с опорного генератора 15 начинают поступать на счетный вход счетчика 20 и суммирующий вход реверсивного счетчика 19, но так как на входах начальной установки счетчиков присутствует логическая единица, то их состояние не изменяется. После того, как на выходе анализатора 2 перегрузки появляется логический нуль, реверсивный счетчик 19 начинает считать длительность переколебательного процесса, а счетчик 20 считает до (N-1), где N - число разрядов регистра 1.

692704

Тем самым определяется момент начала поступления отрезка дельта-модулированной последовательности, соответствующего переколебательному процес5 су, на импульсный преобразователь 4. Сигнал с выхода дегсгифратора 7 постоянного уровня по входу 22 останова поступает на R-вход триггера 12. Как только с дешифратора 7 постоянно10

го уровня поступит логическая единица на выходе триггера 2 появляется логический нуль и тактовые импульсы перестают поступать через элемент И 16 на суммирующий вход счетчика 19. в счетчике 19 записывается количество тактовых интервалов, в течение которых передается переколебательный процесс. После того, как счетчик 20 досчитает до (N-1), на его выходе образуется логическая единица, которая поступает на R-вход триггера 14 и S-вход триггера 13. В результате на выходе триггера 13 появляется логическая единица, а на выходе триггера 14 - логический нуль и тактовые импульсы через элемент И 18 перестают поступать на счетчик 20 и начинают поступать через элемент И I7 на вычитающий вход реверсивного счетчика 19. Время, в течение которого реверсивный счетчик 19 досчитает до нуля, совпадает со временем, в течение которого на импульсный преобразователь 4 поступает дельта-модулированный сигнал, соответствующий переколебательному процессу после перегрузки. После того, как реверсивньш счетчик 19 досчитает до нуля, на его выходе появляется логическая единица, которая поступает на R-вход триггера 3, на выходе которого появляется логический нуль. Сигнал с выхода триггера 13 является сигналом с первого выхода 23 для управления ключами 9 и

10. С выхода опорного генератора 15 поступают так же тактовые импульсы на второй выход 24 для регистра 1.

Таким образом, выброс и переколебательный процесс полностью отсутствуют.

Формула изобретения

1. Дельта-демодулятор, содержащий регистр сдвига, информационный вход которого является входом устройства, формирователь, первый ключ и соединенные последовательно интегратор и

5

фильтр нижних частот, выход которого является выходом устройства, первый выход формирователя соединен с управляющим входом первого ключа, выход которого подключен к первому входу интегратора, отличающийся тем, что, с целью повышения качества преобразования путем устранения выбросов и переколебательного процесса, в него введены дополнительный дельтадемодулятор, анализатор перегрузки, аналоговый блок памяти, дешифратор постоянного уровня, второй ключ и импульсный преобразователь, вход которого под1;лючен к выходу регистра сдвига 5 а выход соединен с информационным входом первого ключа, :управляющий вход которого объединен с ут равляю1 р м входом второго ключа, выход которого соединен с вторым входом интегратора, а информационный вход подключен к выходу аналогового блока памяти, управляющий вход которого объединен с входом останозза формирователя и подключен к выходу дешифратора постоянного уровня, вход которого объединен с информационным входом аналогового блока памяти и подключен к выходу дополнительного дельта-демодулятора, вход которого объединен с информационньш входом регистра сдвига, выходы m первых разрядов которого подключены к входам анализатора перегрузки , выход которого соединен с входом пуска формирователя , второй выход которого подключен к входу синхронизации регистра сдвига.

69270 Ь

2, Дельта-демодулятор по и,,, отличающийся тем,, .то формирователь вьтолнен на первом, втором и третьем триггерах, первом 5 втором и третьем элементах И, реверсивном счетчике, счетчике и опорном генераторе, входы установки в 1 первого и третьего триггеров объединены с входами начальной установки

10 реверсивного счетчика и счетчика и подключены к входу пуска формирователя, выход счетчика соединен с входом установки в О третьего триггера и входом установки в 1 второго 15 триггера, выход которого подключен к первому входу второго элемента И и является первым выходом формирователя, выходы первого и третьего триггеров соединены с первыми входами соот20 ветствующих элементов И, выход опорного генератора подключен к вторым входам всех элементов И и является вторым выходом формирователя, выходы первого и второго элементов И со25 единены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выход которого подключен к входу установки в О второго триггера, выход третьего элемента И сое30 динен с входом счетчика, вход установки в О первого триггера является входом останова формирователя. 3.. Дельта-демодзшятор по п.1,. отличающийся тем, что 5 дешифратор постоянного уровня выполнен на соединенных последовательно дифференцирующем блоке, двухполупериодном выпрямителе, пороговом блоке и селекторе длительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| Дельта-декодер | 1986 |

|

SU1432779A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство для измерения плотности распределения экстремумов | 1983 |

|

SU1101840A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Цифровой демодулятор сигналов с фазово-импульсной модуляцией | 1985 |

|

SU1379939A1 |

Изобретение относится к автоматике. Его использование в системах связи с дельта-модуляцией, предназначенных для передачи аналоговых сообщений с резким изменением уровня, позволит повысить качество преобразования путем устранения выбросов и переколебательного процесса. Дельтадемодулятор содержит регистр сдвига, формирователь, ключ, интегратор и фильтр нижних частот. Благодаря введению импульсного преобразователя, другого ключа, анализатора перегрузки, дополнительного дельта-демодулятора, аналогового блока памяти и дешифратора постоянного уровня сигнал, соответствующий выбросу и переколебательному процессу, заменяется устаноФ вившимся сигналом постоянного уровня. 2 3. п. ф-лы, 2 ил. сл

| Дельта-модулятор | 1983 |

|

SU1112552A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-11-07—Публикация

1984-09-24—Подача