/2

4

:л

шЛ

«А

ю

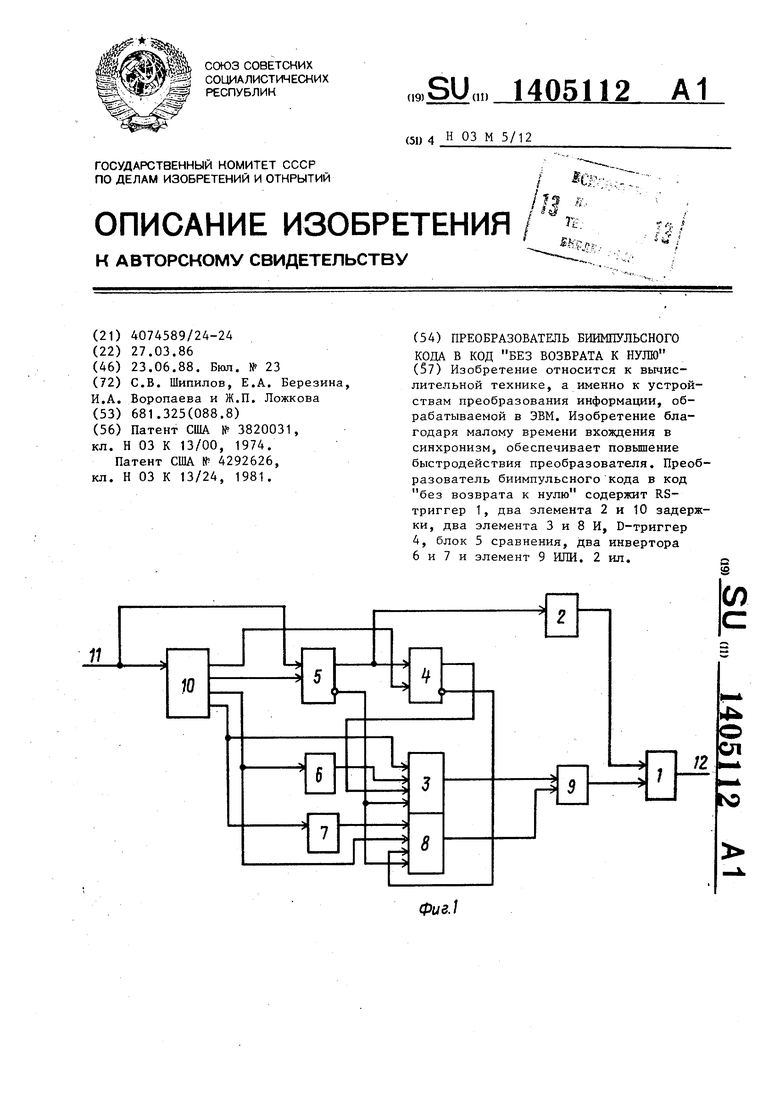

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, обрабатываемой в ЭВМ.

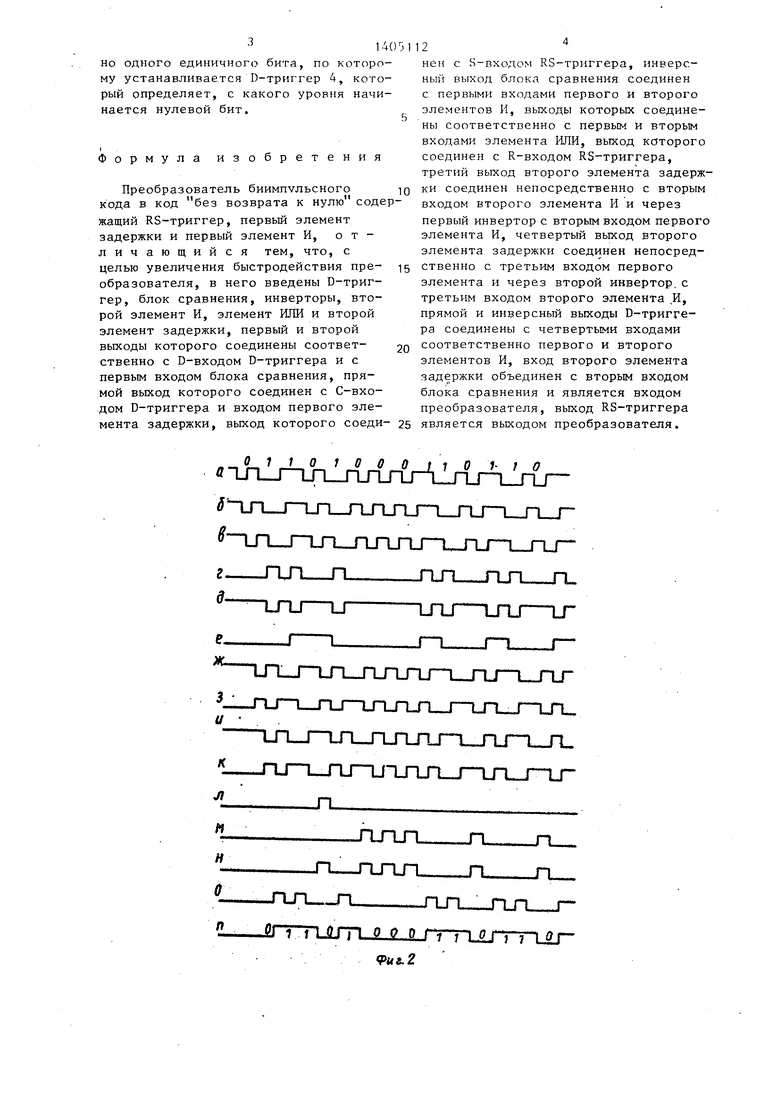

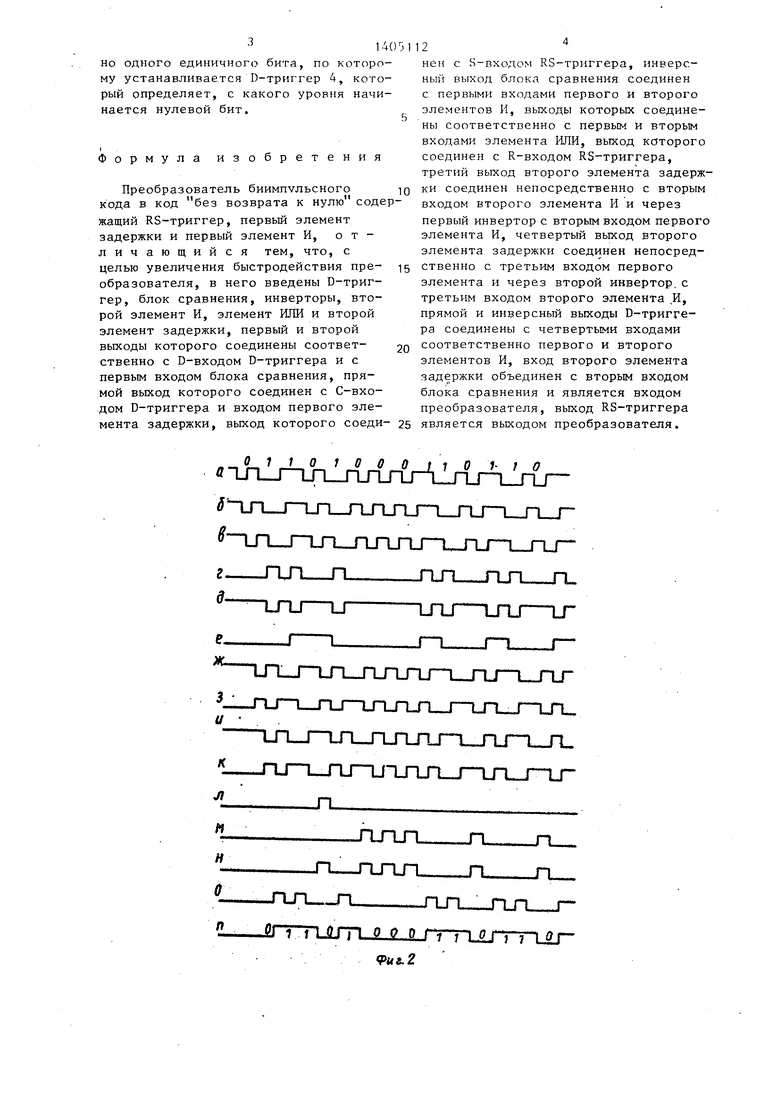

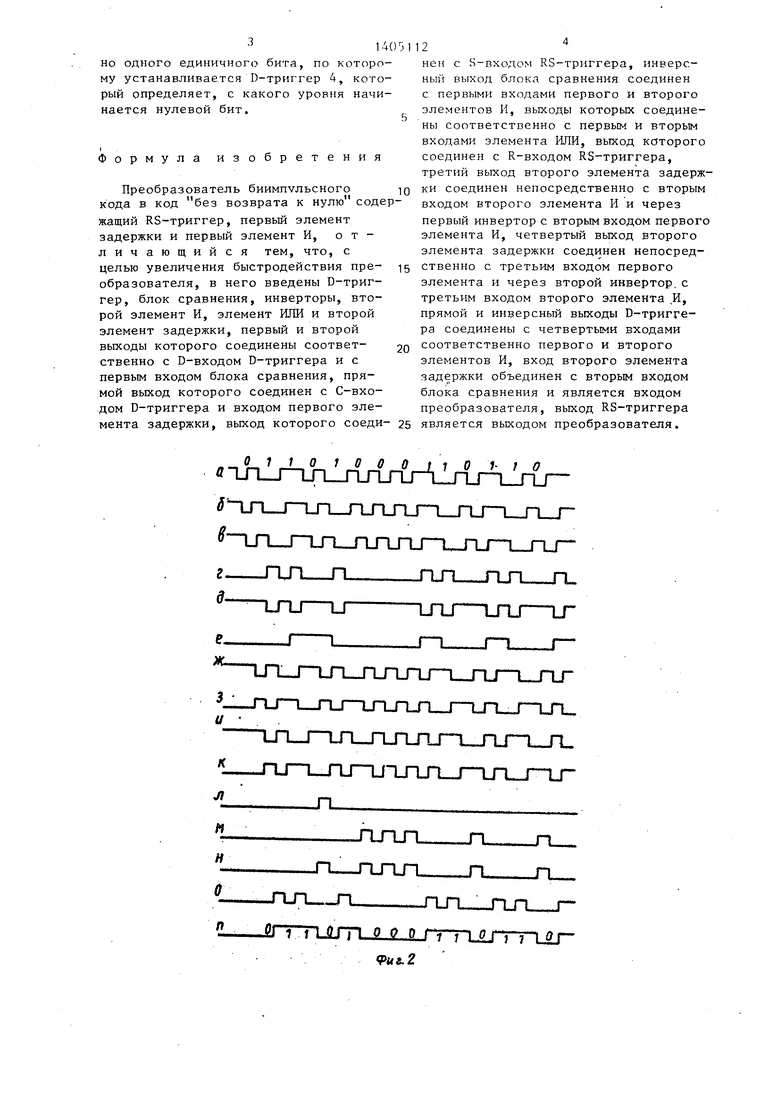

Целые изобретения является увеличение быстродействия преобразователя На фиг. 1 представлена функционал

I ная схема преобразователя J на фиг. 2 временные диаграммы, поясняющие его

I работу.

Преобразователь биимпульсного кода в код без возврата к нулю содержит RS-триггер 1, первый элемент 2 задержки, первый элемент И 3, D-триггер 4, блок 5 сравнения, первый и второй инверторы 6 и 7, второй элемент И 8, элемент ИЛИ 9 и второй элемент 10 задержки, вход 11 и выход 12.

На фиг.. 2 соответствующими индексами обозначены входной сигнал а, сигнал б на первом выходе элемента 10, сигнал в на втором выходе элемента 10, сигнал г на прямом выходе блока 5, сигнал д на инверсном выходе

яблока 5, сигнал е на прямом выходе триггера 4, сигнал ж на третьем вы|ходе элемента 10, сигнал з на выходе инвертора 6, сигнал и на четверiтом выходе элемента 10, сигнал к на

I выходе инвертора 7, сигнал л на выходе элемента 3, сигнал м на выходе

элемента 8, сигнал н на выходе элеме

|та 9, сигнал о на выходе элемента 2, сигнал п на выходе триггера 1.

Элемент 10 задержки формирует на своих выходах сих налы, задержанные

1относительно исходного биимпульсного кода соответственно на первом выходе на четверть периода, на втором - на

;полпериода, на третьем - на период и на четвертом - на три вторых периода.

Блок 5- сравнения формирует сигналы, соответствующие синхроимпульсам единичных бит.

D-триггер 4 запоминает уровень последнего единичного бита информаци

Элемент 2 задержки предназначен для согласования фазы синхроимпульсо единичных бит с фазой синхроимпульсов нулевых бит.

RS-триггер 1 формирует выходной код без возврата к нулю (БВН) .

Элемент ЩШ 9 суммирует синхроимпульсы нулевых бит.

Элемент И 3 предназначен для выделения синхроимпульсов нулевых бит.

0

5

0

5

0

5

0

5

0

5

начинающихся с высокого уровня. Элемент И 8 предназначен для вьщеления синхроимпульсов нулевых бит, начинающихся с низкого уровня.

Преобразователь работает следующим образом.

Виимпульсный код, поданный на вход 11, поступает на вход элемента 10 задержки. В результате сравнения этого кода и задержанного на полпериода кода на выходе блока 5 сравнения появляются синхроимпульсы еди- ничных бит, по которым устанавливается состояние D-триггера 4 в зависимости от уровня единичного бита. Если после единичного бита следует несколько нулевых бит, то состояние D-триггера 4 не меняется. Единичное состояние D-триггера 4 свидетельствует о том, что нулевые биты, следующие за единичным, начинаются с низкого, уровня, а нулевое состояние - с высокого уровня. Задержанньй на период код с третьего выхода элемента 10 задержки и инверсный код, задержанный на полтора периода, с выхода инвертора 7 подаются на вход элемента И 8. В связи с тем, что отдельные импульсы (результат совпадения в элементе ИЗ) совпадают с синхроимпульсами единичных бит, такие импульсы блокируются инверсными синхроимпульсами единичных бит. Нулевое состояние D-триггера 4 разрешает прохождение синхроимпульсов нулевых бит, которые начинались с высокого уровня. Аналогично элементу И 8 на выходе элемента И 3 выделяются синхроимпульсы нулевых бит, которые начинаются с низкого уровня, а на выходе элемента ИЛИ 9 образуются синхроимпульсы нулевых бит, которые задержаны относительно синхроимпульсов единичных бит на полпериода. Поэтому синхроимпульсы единичных бит задерживаются элементом 2 задержки на полпериода и подаются на S-вход RS-тригге- ра 1. На выходе RS-триггера 1 образуется код БВН, поскольку на R-вход RS-триггера 1 подаются синхроимпульсы нулевых бит, на S-вход - синхроимпульсы единичных бит.

Таким образом, преобразователь обеспечивает преобразование бии myльc- ного кода в код БВН на скорости обмена, равной предельному быстродействию применяемой элементной базы. Для вхождения в синхронизм достаточО 1 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь биимпульсного кода в код "без возврата к нулю | 1988 |

|

SU1501273A1 |

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809538A1 |

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809537A1 |

| ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНОГО КОДА В ОДНОПОЛЯРНЫЙ | 2002 |

|

RU2227367C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259010C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| Устройство приема двоичной информации в последовательном коде | 1991 |

|

SU1771075A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для приема информации | 1988 |

|

SU1672571A1 |

| Преобразователь кода | 1987 |

|

SU1495998A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, обрабатываемой в ЭВМ. Изобретение благодаря малому времени вхождения в синхронизм, обеспечивает повышение быстродействия преобразователя. Преобразователь биимпульсного кода в код без возврата к нулю содержит RS- триггер 1, два элемента 2 и 10 задержки, два элемента 3 и 8 И, D-триггер 4, блок 5 сравнения, два инвертора 6 и 7 и элемент 9 ИЛИ. 2 ил. с

| Патент США № 3820031, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4292626, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-23—Публикация

1986-03-27—Подача