Изобретение относится к технике для промыслово-геофизических исследований скважин, в частности к сейсмоакустическим методам.

Создание современных модификаций аппаратуры для сейсмоакустических методов исследования скважин сдерживается недостаточной скоростью передачи цифровых данных по каротажному кабелю. Отчасти проблема решается использованием в скважинных приборах цифровых модемов с многоуровневым кодированием, применяемых в HDSL-технологиях для передачи данных по телефонным линиям связи. Но это ограничивает термостойкость скважинной аппаратуры. По мере увеличения глубин исследования необходимость высокой битовой скорости дополняется требованием термостойкости, что ставит вопрос об эффективных и простых формирователях цифрового сигнала для каротажного кабеля.

Известен способ формирования балансного пятиуровневого сигнала в линии, реализованный в преобразователе, в котором на основе анализа восьми бит входных данных и величины текущего небаланса в выходном сигнале, по определенным правилам производят замену входных данных балансирующими комбинациями (В.А.Шувалов, авт.св. №651491, опубл. 08.03.79, бюл. №9). Замена производится так, чтобы текущая сумма небаланса выходных данных не выходила за определенные границы, а балансирующая комбинация в приемнике была бы вновь правильно преобразована в исходные данные.

Как видно, в формировании выходного импульса преобразователя участвует большое число бит, что является недостатком, поскольку может привести к размножению ошибок при обратном преобразовании данных.

Кроме того, в спектре выходного сигнала преобразователя присутствует явная компонента на тактовой частоте Fт, которая порождается кодовыми комбинациями в канале связи, состоящими из двух-трех импульсов одинаковой полярности, расположенных на соседних тактовых интервалах. Отсюда следует, что для правильного выделения таких кодовых комбинаций на приемной стороне потребуется необоснованно широкая полоса канала связи.

Известны также способ преобразования двоичного сигнала в трехуровневый балансный сигнал (код AMI) и устройство для его осуществления, изложенные в методе передачи цифровых данных, в котором входные нулевые биты передаются в линию как ноль, а единичные биты передаются поочередно как импульсы положительной и отрицательной полярности (R.H.Barker, янв. 25, 1955, патент США 2700696). Практическая схема преобразователя для реализации данного метода содержит счетный триггер, который своими выходами соединен с двумя схемами совпадения (мультиплексором), выходы которого соединены с входами формирователя выходного сигнала, состоящего из двух выходных схем, формирующих положительный и отрицательный импульсы на общей нагрузке (Кэтермоул К.В. Принципы импульсно-кодовой модуляции. Перевод с англ. под ред. В.В.Маркова. М., «Связь», 1974, стр.344, 345).

К достоинствам кода AMI относят простоту реализации кодера и выгодную форму спектра его линейного сигнала, где основная энергия сосредоточена вблизи полутактовой частоты Fт/2. Благодаря этому код AMI широко используется в магистральных системах передачи цифровых данных. Недостаточная синхронизирующая способность кода при длительном нулевом сигнале достаточно просто повышается добавлением дополнительных импульсов в линейный сигнал (коды HDBn). Другой более важный недостаток кода AMI состоит в его невысокой битовой скорости, близкой к величине 2 бит/Гц.

Цель предлагаемого способа преобразования заключается в повышении пропускной способности канала связи.

Указанная цель достигается тем, что в способе преобразования двоичного сигнала в пятиуровневый сигнал, включающем поочередную смену полярности импульсов в линии, входные данные задерживаются на один битовый интервал в триггере задержки и в зависимости от значения текущего бита и предопределенной полярности направляются на один из четырех входов пятиуровневого формирователя выходного сигнала условно, обозначенных как +1, +2, -1, -2, который при появлении на его входах единичного импульса выдает в линию одноименные импульсы, причем значению ноль текущего бита соответствует единичное значение амплитуды импульса в линии, а значению единица - удвоенное или наоборот, остальные входные нулевые биты передаются в линию как ноль, при этом перевод триггера задержки в единичное состояние на текущем такте обуславливает перевод его в нулевое состояние не позднее момента окончания следующего такта.

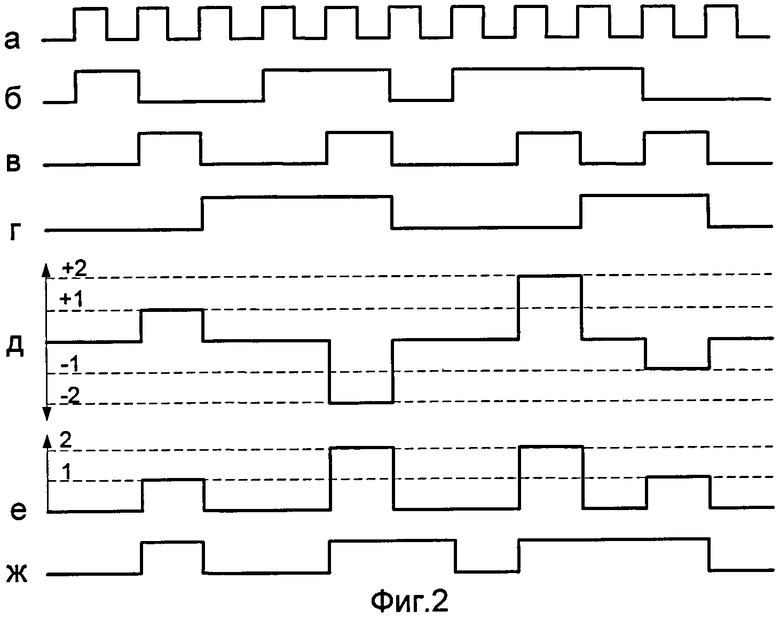

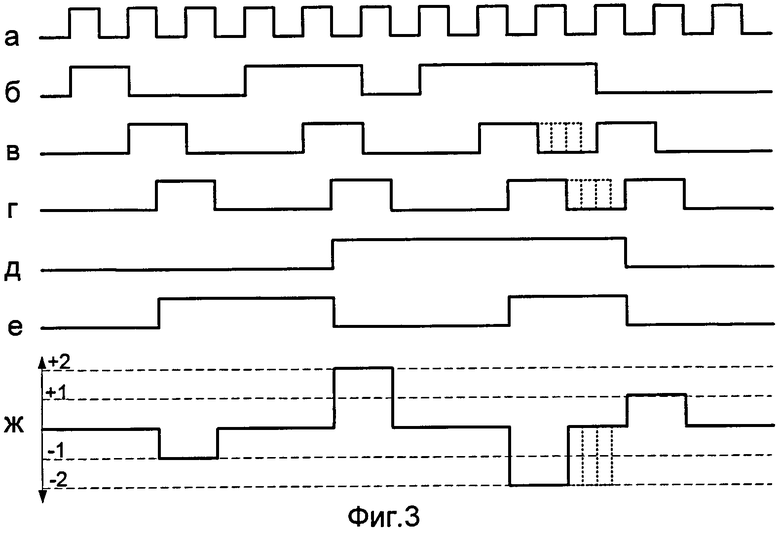

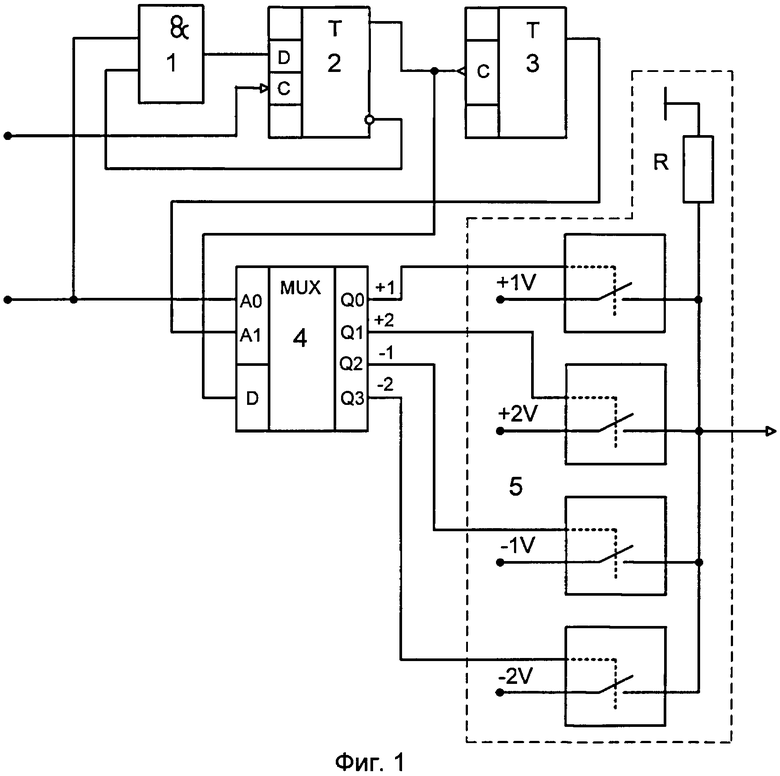

На фиг.1 изображена функциональная схема устройства, на фиг.2 - временные диаграммы работы, на фиг.3 - модифицированные временные диаграммы.

Преобразование двоичного сигнала в пятиуровневый сигнал производится по следующим правилам:

1. Полярность первого импульса в линии устанавливается произвольно, а полярность последующих импульсов в линии поочередно меняется на противоположную. Данное правило считается известным.

2. Передаче подлежат дибиты входных данных со значениями 10, 11, причем обнаружение первого единичного бита в указанных дибитах инициирует посылку импульса в линию.

3. Амплитуда импульса в линии в зависимости от значения 2-го бита принимает два значения, которые соотносятся как 1:2. Нулевому значению второго бита в означенных дибитах может соответствовать малое значение амплитуды импульса в линии, а большему - большая. Остальные входные нулевые биты передаются в линию как ноль

Напряжение на выходе преобразователя с учетом правила 1 может принимать 5 значений: +1, +2, 0, -1, -2.

В одном из вариантов исполнения преобразователь двоичного сигнала в пятиуровневый сигнал содержит схему И 1, триггер задержки 2 счетный триггер 3, мультиплексор 4, формирователь выходного сигнала 5.

На входы преобразователя поступают тактовые импульсы (фиг.2а) и битовая последовательность (фиг.2б).

Входные данные со значением «единица» могут поступить на D-вход триггера задержки 2 только при положительном (разрешающем для схемы И 1) уровне напряжения на инверсном выходе триггера задержки 2, то есть при нулевом его состоянии. Такое состояние триггера можно назвать исходным. Триггер задержки 2 находится в режиме ожидания до момента появления в потоке входных данных комбинации 10 или 11. В момент фиксации первого (из дибита) единичного бита состояние триггера меняется на противоположное.

Перевод триггера задержки 2 в единичное состояние (текущий такт) приводит к закрытию схемы И 1 в начале текущего такта, в результате на входе (D-вход) триггера будет удерживаться нулевой уровень, но его состояние до конца текущего такта останется неизменным (единица). В начале следующего такта вход триггера задержки 2 остается в нулевом состоянии, следовательно, на очередном такте триггер задержки 2 будет переведен в состояние «ноль». С этого момента схема И 1 вновь открывается.

В результате совместной работы схемы И 1 и триггера задержки 2 появление искомой комбинации (10, 11) в потоке входных данных (фиг.2б) сопровождается формированием одиночного импульса на выходе триггера задержки 2 (фиг.2в).

С выхода триггера задержки 2 импульсы (фиг.2в) поступают на С-вход (вход) счетного триггера 3 и на вход данных (вход) мультиплексора 4. Выходной сигнал счетного триггера 3 (фиг.2г) поступает на старший (второй) адресный вход мультиплексора 4. Младший (первый) адресный вход мультиплексора 4 находится под управлением входных данных (фиг.2б). Под влиянием указанных адресных сигналов данные с входа мультиплексора 4 поступают на один из четырех его выходов. Для определенности положим, что единичное состояние счетного триггера 3 предполагает формирование на выходе преобразователя отрицательного импульса в линии, а нулевое - положительного. Исходя из сказанного, и с учетом правила №3 обозначим выходы мультиплексора 4 величинами: +1, +2, -1, -2, имея в виду то обстоятельство, что появление единичного значения на одном из выходов мультиплексора 4 предполагает посылку в линию одноименного напряжения. В таком случае формирователь выходного сигнала 5 может быть выполнен на четырех ключах с нормально разомкнутыми контактами. При наличии положительного импульса на одном из входов формирователя 5 соответствующий данному входу ключ замыкается и соответствующее данному ключу напряжение питания посылается в линию. В результате в линии формируется импульсный сигнал, изображенный на фиг.2д, содержащий пять уровней напряжений: +1V, +2V, 0, -1V, -2V.

В известных пятиуровневых преобразователях интервал (Т) между соседними импульсами в линии (тактовый интервал) обычно кратен удвоенному битовому интервалу входных данных. В предложенном преобразователе интервал между соседними импульсами будет кратен одиночному битовому интервалу, а минимальный тактовый интервал (Тмин) равен удвоенному битовому интервалу. На диаграмме (фиг.2д) интервал Тмин наблюдается между третьим и четвертым импульсами. С учетом этих особенностей стробирование сигнала на приемной стороне необходимо производить на частоте F=2/Тмин, то есть в два раза чаще, чем обычно.

На приемной стороне из сигнала (фиг.2д) частоту F можно выделить и сформировать (задержка не показана) сигнал, подобный сигналу, изображенному на фиг.2е. Для декодирования указанного сигнала (фиг.2е) следует импульсу с малой амплитудой поставить в соответствие дибит 1 0, а импульсу с большой амплитудой - дибит 11, как это изображено на фиг.2ж. Сравнение между собой исходного сигнала (фиг.2б) и декодированного сигнала (фиг.2ж) показывает их идентичность.

В иных вариантах исполнения преобразователя мультиплексор 4 может быть выполнен на отдельных логических элементах или может быть заменен на соответствующий дешифратор. Формирователь выходного сигнала 5, в свою очередь, может быть выполнен на управляемых источниках тока в виде аналоговой схемы вычитания или на четырех одновибраторах, реагирующих на фронт импульса триггера задержки и выдающих в линию импульс с нужными параметрами. В таком случае длительность выходного импульса одновибратора независимо от длительности импульса триггера задержки 2 может составлять некую долю от удвоенной величины битового интервала. Длительность импульса триггера задержки 2 может быть выбрана в пределах битового интервала.

Подобные решения позволяют строить разнообразные, например аналоговые, схемы сброса триггера задержки 2 в нулевое состояние.

Для нормальной работы предлагаемого преобразователя важно предотвратить появление ложного фронта в выходном сигнале триггера задержки 2 на границе между текущим и следующим битовыми интервалами. В то же время необходимо создать условия (ограничить длительность импульса «сброс») для проявления в выходном сигнале триггера задержки 2 нужного фронта в момент окончания следующего битового интервала. В рассматриваемом преобразователе «импульс сброс» как таковой отсутствует и правильная работа триггера задержки 2 обеспечивается коммутацией входного сигнала триггера задержки 2 с помощью схемы И 1. Это всего лишь предпочтительный вариант, который не заслуживает особого о себе упоминания в формуле.

В рассмотренном преобразователе (фиг.1) на адресных входах мультиплексора допустима частая смена уровней сигналов на границах битовых интервалов. По этой причине единичное состояние триггера задержки не должно сохраняться за пределами текущего такта, чтобы не вызвать ложное появление единичного сигнала на ином выходе мультиплексора. Следовательно, для правильной работы данного преобразователя (фиг.1) перевод триггера задержки из единичного состояния в нулевое состояние необходимо выполнить не позднее момента начала следующего такта.

Покажем, что это ограничение слишком строгое и есть простые схемные решения, которые допускают более широкое толкование условий реализации предлагаемого способа.

Пусть на входы подобного преобразователя поступают прежние данные: тактовые импульсы (фиг.3а) и битовая последовательность (фиг.3б). Сигнал триггера задержки (фиг.3в) получают любым указанным ранее образом из входных данных (фиг.3б). Сигнал, изображенный на фиг.3г, получают из сигнала (фиг.3в) путем задержки его на 0,5 битового интервала. Значение текущего бита во входных данных отображает сигнал (фиг.3д). Его получают в результате чтения входных битов (фиг.3б) в моменты времени, соответствующие фронтам сигнала (фиг.3г). Поочередная смена полярности выходного сигнала преобразователя выполняется с помощью сигнала (фиг.3е). Сигнал (фиг.3е) есть, как и ранее результат деления на два сигнала (фиг.3г) с помощью счетного триггера. Если сигнал (фиг.3д) и сигнал (фиг.3е) подать на адресные входы мультиплексора 4, а на вход данных мультиплексора сигнал, изображенный на (фиг.3г), на выходе формирователя 5 сформируется известный ранее линейный сигнал, (фиг.3ж).

Данный пример (фиг.3) показывает, что небольшое изменение схемы преобразователя (фиг.1) - оно свелось к добавлению двух D-триггеров - не меняет сущности его работы, но позволяет почти в два раза увеличить длительность единичного состояния триггера задержки (фиг.3в). На примере одного импульса подобная ситуация показана штрих-пунктирной линией на диаграммах (фиг.3в), (фиг.3г), (фиг.3ж).

Отсюда следует более широкое толкование условий реализации предлагаемого способа: «перевод триггера задержки из единичного состояние в нулевое состояние необходимо выполнить не позднее момента окончания следующего такта».

По своему виду выходной сигнал преобразователя близок к сигналу в коде AMI и во многом сохраняет его положительные качества: высокую синронизирующую способность, компактный спектр, из чего следует умеренная требовательность к качеству коррекции канала, простота схемной реализации. Полярность импульсов в линии меняется поочередно, что является важным преимуществом по сравнению с известными пятиуровневыми преобразователями, где на соседних позициях сигнала в линии допускается наличие импульсов с одинаковой полярностью. Такие нежелательные комбинации импульсов расширяют спектр сигнала в области нижних и верхних частот. Это затрудняет его коррекцию в приемнике. Как показывает практика, уверенный прием данных в таких условиях, помимо трудностей с коррекцией, обеспечивается ценой расширения полосы канала на 25% в сторону верхних частот.

Сигнал на выходе предлагаемого преобразователя почти балансный. Максимальный уровень небаланса возникает при повторении на входе комбинации 1110. Это не вызывает сбоев на приеме, но может снизить длину линии связи. При сейсмоакустических методах исследования скважин сигналы с датчиков подобны речевому сигналу с нулевым средним. В этих условиях небаланс сигнала в линии минимален, качество приема не снижается и скремблирование входных данных не требуется.

Поочередная смена полярности импульсов в линейном сигнале предполагает его хорошую синхронизирующую способность при высокой плотности единиц на входе преобразователя. Но длинный ноль на входе ведет к сбою синхронизации. Как и в коде AMI, данный недостаток устраняется добавлением в выходной сигнал преобразователя дополнительных импульсов, нарушающих правило чередования полярностей импульсов на выходе, подобно тому, как это обычно делается в кодах с «высокой плотностью единиц».

При испытаниях преобразователя на трехжильном каротажном кабеле длиной 5,3 км скорость передачи данных составила 800Кбод. То есть примерно в два раза выше, чем в коде HDB3. В обоих случаях для восстановления сигнала применялся аналоговый корректор.

Схема пятиуровневого преобразователя достаточно проста. Поэтому его термостойкость в сравнении с кодером HDB3 осталась на прежнем уровне. Она превышает 150°С и как прежде ограничивается термостойкостью выходного формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1983 |

|

SU1095397A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1981 |

|

SU987832A1 |

| Преобразователь двоичного сигнала в пятиуровневый сигнал | 1983 |

|

SU1172044A1 |

| Способ магнитной записи цифровой информации и устройство для его осуществления | 1990 |

|

SU1839269A2 |

| УСТРОЙСТВО ЗАПИСИ ЦИФРОВОГО СИГНАЛА | 1995 |

|

RU2155388C2 |

| Устройство сжатия аналоговой информации | 1988 |

|

SU1709368A1 |

| Преобразователь двоичного сигнала в квазитроичный сигнал | 1983 |

|

SU1109926A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА ДЛЯ СЕТИ SpaceWire | 2012 |

|

RU2483351C1 |

Изобретение относится к технике для промыслово-геофизических исследований скважин и предназначено для преобразования двоичного сигнала в пятиуровневый сигнал с поочередной сменой полярности импульсов в линии. Достигаемый технический результат - повышение пропускной способности канала связи. Способ преобразования двоичного сигнала в пятиуровневый сигнал заключается в том, что ноль во входных данных побитно передают в линию как ноль, а при поступлении во входных данных комбинации 10 или 11 задерживают первый единичный бит в триггере задержки и обнуляют его, задержанный бит подают на вход счетного триггера и, адресуясь значением выходного сигнала счетного триггера и значением второго бита комбинации, направляют задержанный бит на один из четырех входов пятиуровневого формирователя выходного сигнала, который при появлении на входах единичного бита выдает в линию импульсы. 3 ил.

Способ преобразования двоичного сигнала в пятиуровневый сигнал, в котором ноль во входных данных побитно передают в линию как ноль, включающий поочередную смену полярности импульсов в линии с помощью выходного сигнала счетного триггера, адресующего биты на тот или иной вход формирователя выходного сигнала, отличающийся тем, что при поступлении во входных данных комбинации 10 или 11 задерживают первый единичный бит в триггере задержки и обнуляют его не позднее момента окончания следующего такта, задержанный бит подают на вход счетного триггера и, адресуясь значением выходного сигнала счетного триггера и значением второго бита комбинации, направляют задержанный бит на один из четырех входов пятиуровневого формирователя выходного сигнала, который при появлении на входах единичного бита выдает в линию импульсы, причем значению ноль второго бита комбинации соответствует единичное значение амплитуды импульса в линии, а значению единица - удвоенное, или наоборот.

| Преобразователь двоичного сигнала в пятиуровневый сигнал | 1983 |

|

SU1172044A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Устройство для обвязки пакетов плит | 1984 |

|

SU1288114A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

Авторы

Даты

2011-09-10—Публикация

2010-02-25—Подача