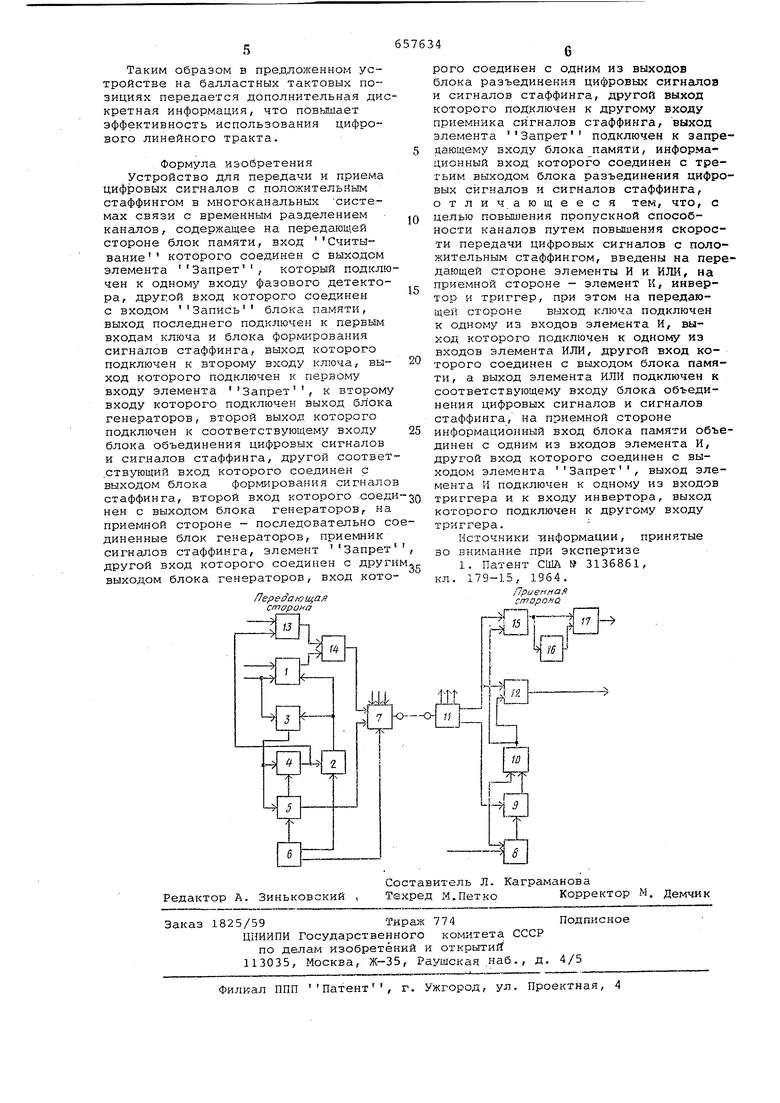

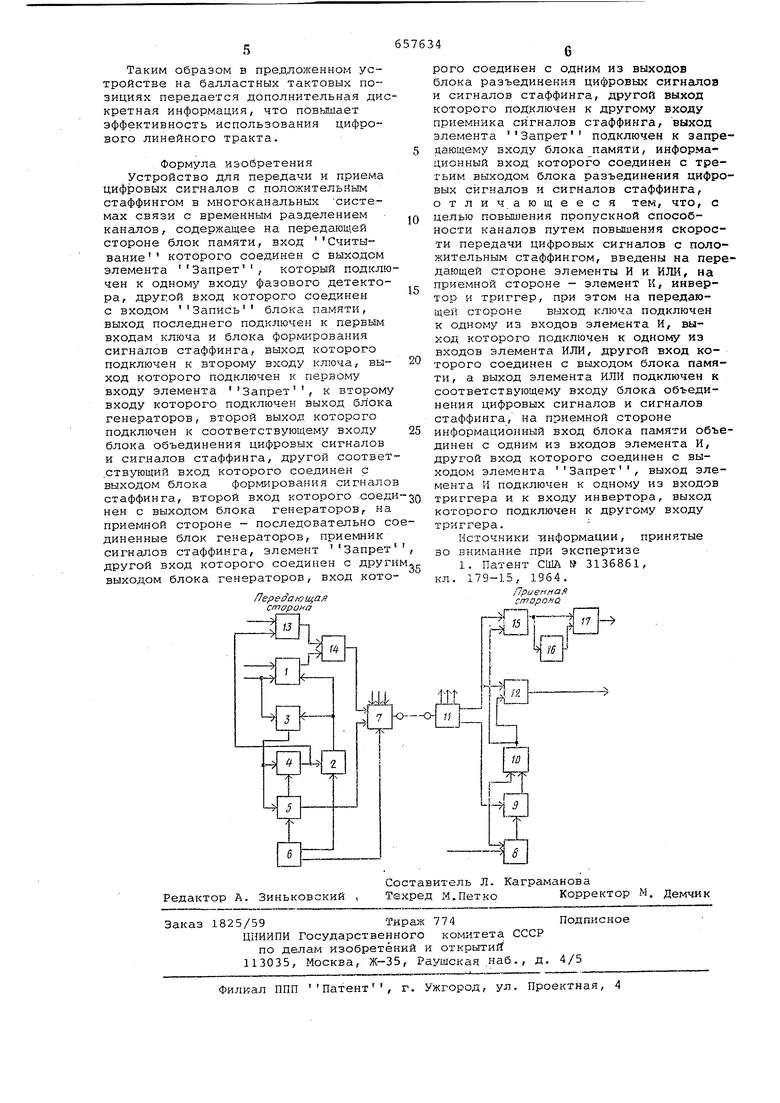

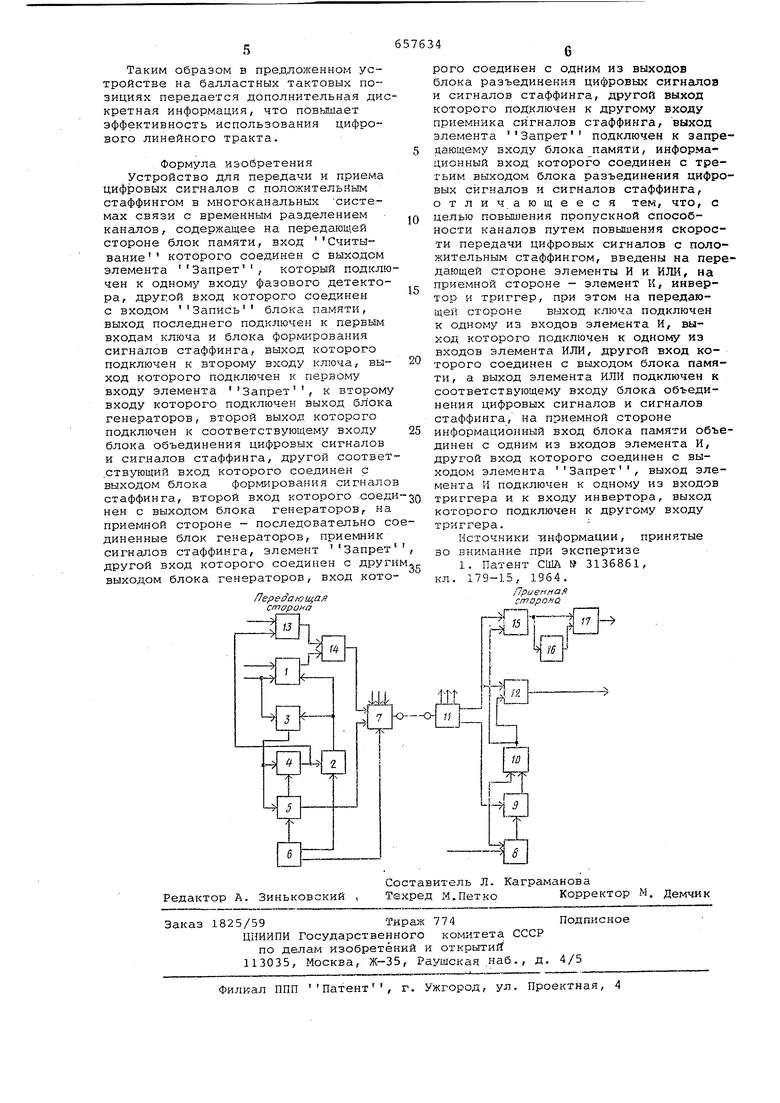

которого соединен с вы ходом элемента Запрет, который подключен к одному входу фазового детектора, другой вход которого соедине с входом Запись блока памяти, выход последнего подключая к первым вхо дам ключа и блока формирования сигна лов стаффннга, выход которого подклю .чен к ВТopoMj входу ключа, выход кото рого подключен к первому входу элемента Banpefr к второму входу которого подключен выход блока генераторов, второй выход которого подключен к соответствующему входу блока объединения цифровых сигналов и сигналов стаффинга, другой соответствующий вход которого соединен с вы ходом блока формирования сигналов стаффинга, второй вход которого соединен с выходом блока генераторов, на приемной стороне - последовательн соединенные блок генераторов, приемн сигналов стаффинга, элемент Запрет, другой вход которого соединен с другим выходом блока генераторов, вход которого соединен с одним из вы ходов блока разъединения цифровых сигналов и сигналов стаффинга, друго выход которого подключен к другому входу приемника сигналов стаффинга, выход элемента Запрет подключен к запрещающему входу блока памяти, информационный вход которого соединен с третьим выходом блока разъединения цифровых сигналов и сигналов стаффинга, введены на передающей сто роне элементы И и ИЛИ, на приемной стороне - элемент И, инвертор и триггер, при этом на передающей стор не выход ключа, подключен к одному из входов элемента И, выход которого подключен к одному из входов элемента ИЛИ, другой вход которого соедине с выходом блока памяти, а выход элемента ИЛИ подключен к соответствующему входу блока объединения цифровы сигналов и сигналов стаффинга, на приемной стороне информационный вход блока памяти объединен с одним из входов элемента И, другой вход ко торого соединен с выходом элемента Запрет, выход элемента И подключей к одному из входов триггера и к входу инвертора, выход, которого подключен к другому входу триггера. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство, для передачи и приема цифровых сигналов с положительньлм стаффингом 3 многоканальных системах связи с временным разделением канало содержит на передающей стороне бло памяти 1, элемент Запрет 2, фазо .вый детектор 3 с ключ 4, блок 5 ,цля формирования сигналов стаффинга, блок б генераторов, блок 7, предназначенный для объединения цифровых сигналов и сигналов стаффкнга, на приемной стороне - блок 8 генераторов, приемник 9 сигналов стаффинга, элемент Запрет 10, блок разъединения 11 цифровых сигналов и сигналов стаффинга, блок памяти 12, введены на передаю-, щей стороне - элемент И 13, элемент ИЛИ 14, на приемной стороне - элемент И 15, инвертор 16, триггер 17. Устройство работает следующим образом. Запись информации в блоке памяти 1 осуществляется с тактовой частотой объединяемого цифрового потока, а считывание - с частотой, превышающей частоту записи и определяемой блоком 6 генераторов. Как только разность фаз между сигналами записи и считывания достигнет порогового значения фазового детектора 3, на один вход ключа 4 с выхода фазового детектора 3 подается сигнал. На второй вход ключа 4поступает сигнал с выхода блока 5в моменты, определенные структурой объединенного цикла передачи, после чего с выхода ключа 4 на элемент Запрет 2 поступает сигнал запрета, вследствие чего будет пропущен один такт считывания из блока памяти 1 так как в объединенном цикле передачи появится балластная вставка. Для обнаружения и устранения балласт- . ных вставок при разъединении цифровых потоков из блока 5 по каналу управления стаффингом в приемник 9 передаются сигналы о наличии балластных вставок. В связи с тем, что в устройстве на тактовые позиции введены символы дополнительной информациито они поступают на вход элемента И 13. На второй вход элемента И 13 будет подаваться стробирующая импульсная последовательность с выхода ключа 4. Таким образом с помощью элемента И 13 осуществляется ввод до-, полнительной информации способом наложения. Дополнительная дискретная информация с выхода элемента И 13 через элемент ИЛИ 14 будет введена на тактовые позиции балластных вставок и через блок объединения 7 будет передана по линейному тракту в блок разъединения 11 приемной части. Из блока разъединения 11 цифровойпоток поступает в блок памяти 12. В моменты прихода балластных вставок с выхода .приемника 9 на элемент Запрет 10 поступает сигнал, запрещающий импульс записи от блока 8 на блок памяти 12. Одновременно с выхода приемника .9 на :элемент И 15 будет передан сигнал, по которому символ дополнительной информации через элемент И 15 будет поступать на один из раздельных входов триггера 17. На втоP° раздельный вход триггера 17 подается последовательность инверсных символов от инвертора 16. На выходе триггера 17 формируется огибающая пачек импульсов, соответствующая символам дополнительной дискретной информацпи на входе элемента И 13.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| УСТРОЙСТВО ДЛЯ АСИНХРОННОГО УПЛОТНЕНИЯКАНАЛОВ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМСИГНАЛОВ | 1973 |

|

SU453726A1 |

| Приемник команд стаффинга | 1982 |

|

SU1075433A1 |

| Многоканальное устройство передачи и приема асинхронных цифровых сигналов | 1988 |

|

SU1555886A1 |

| Устройство для контроля многоканальной системы связи с временным разделением каналов | 1974 |

|

SU563734A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Система для передачи и приема цифровой информации | 1981 |

|

SU1058080A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

Авторы

Даты

1979-04-15—Публикация

1975-12-30—Подача