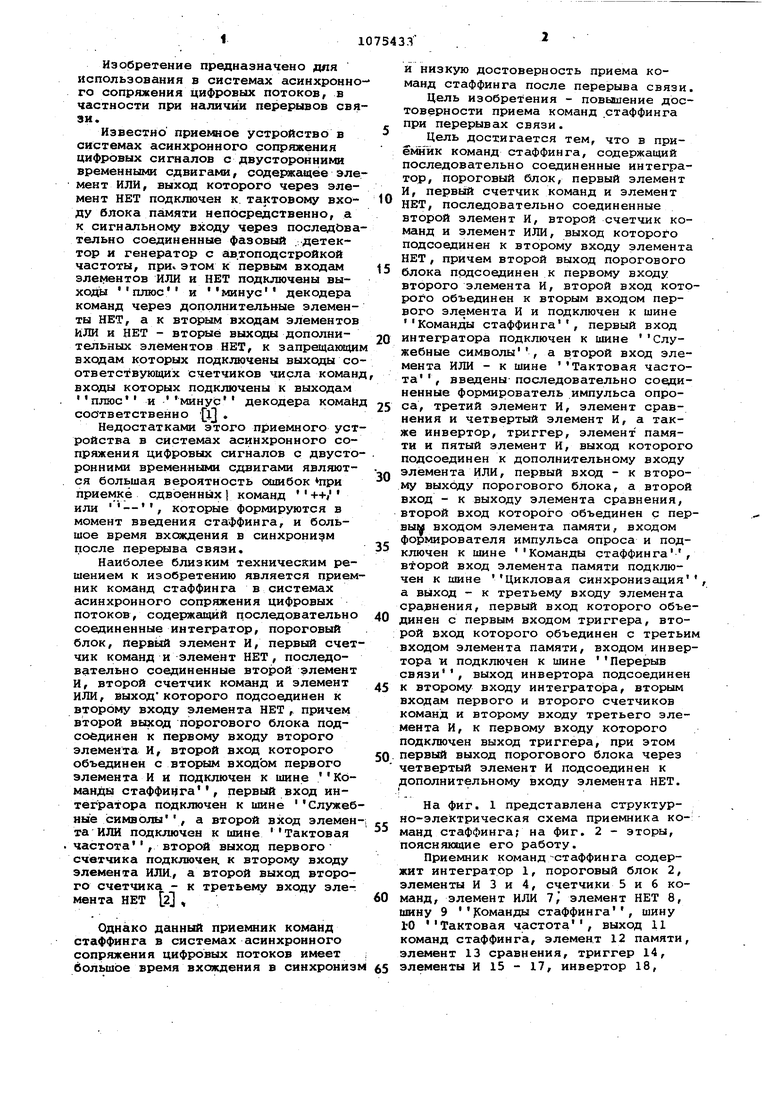

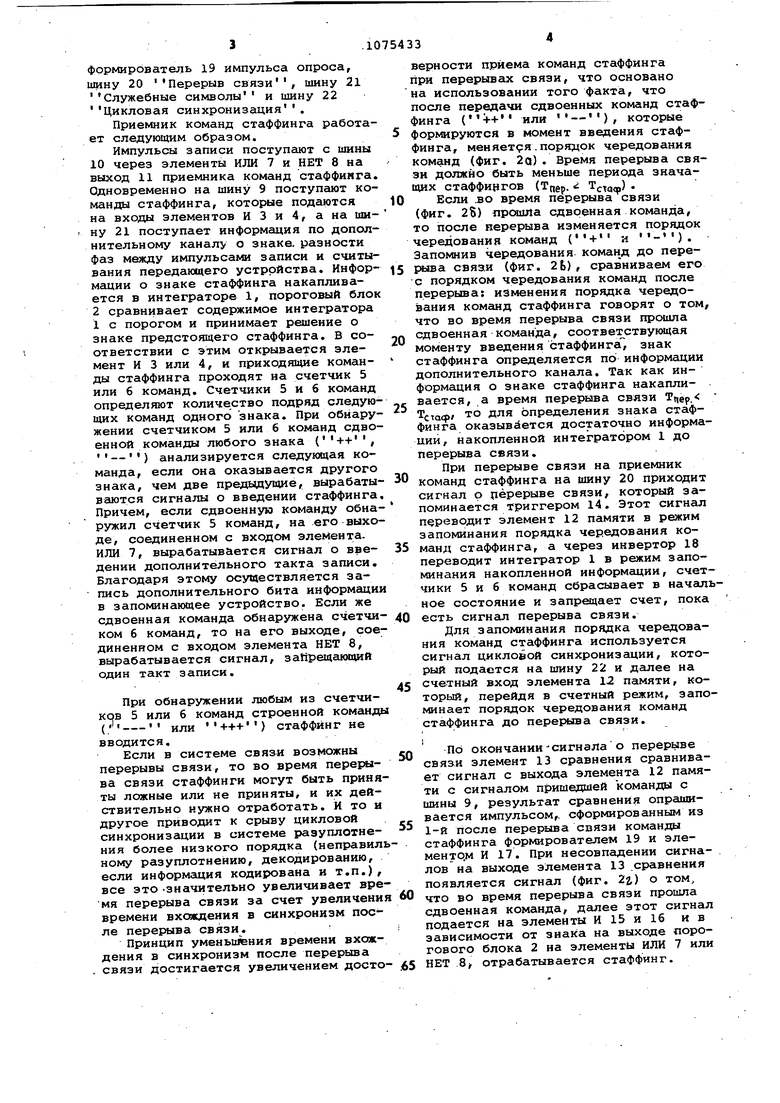

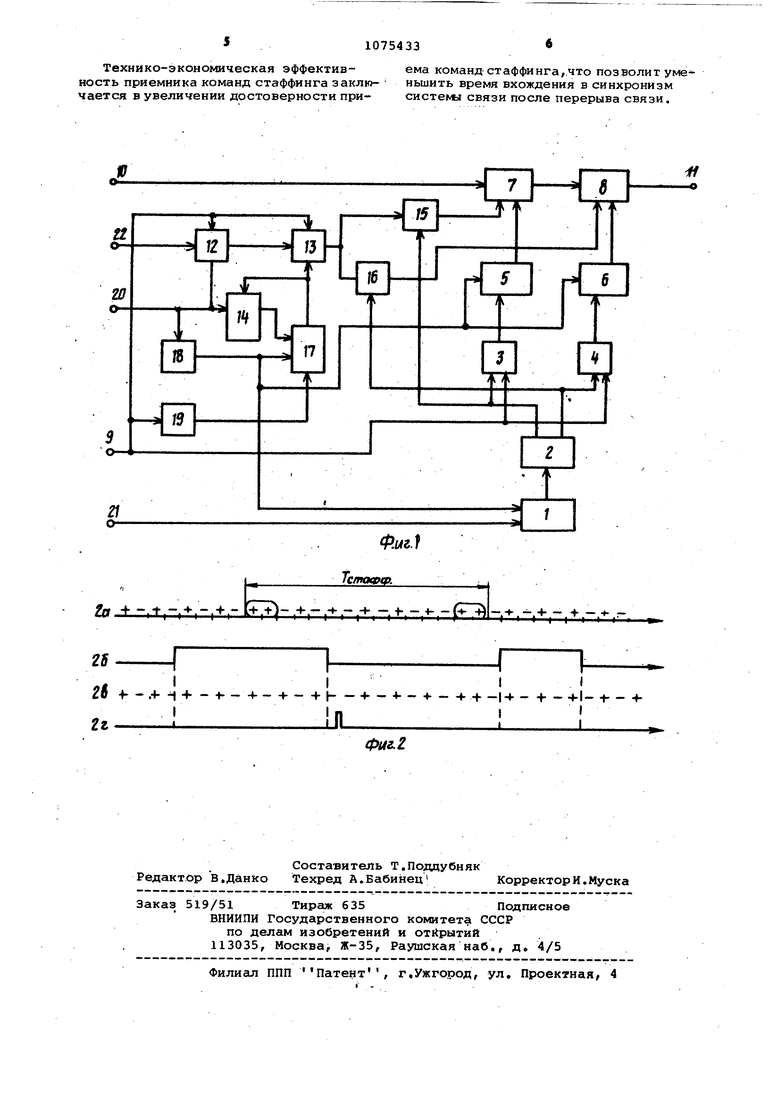

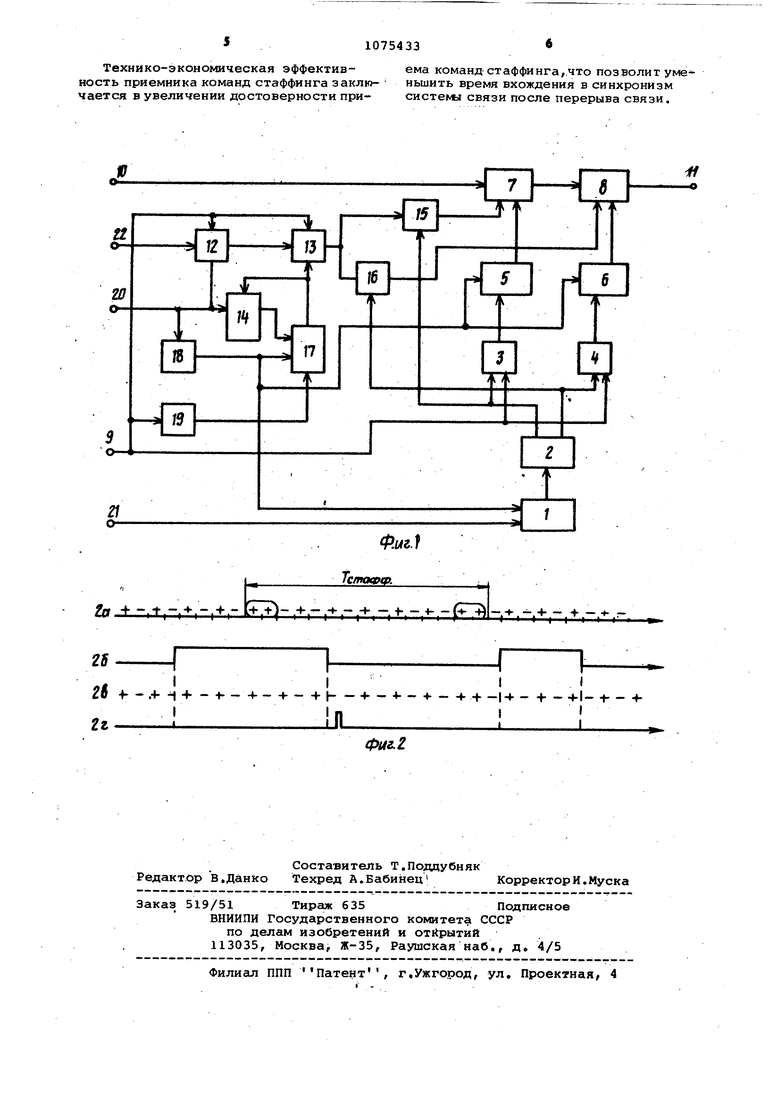

Изобретение предназначено дяя использования в системах асинхронн го сопряжения цифровых потоков, в частности при наличии перерывов св зи. Известно приемное устройство в системах асинхронного сопряжения цифровых сигналов с двусторонними временными сдвигами, содержащее эле мент ИЛИ, выход которого через элемент НЕТ подключен к тактовому входу блока памяти непосредственно, а к сигнальному входу через последЬва тельно соединенные фазовый .детектор и генератор с автоподстройкой частоты, при. этом к первым входам элементов ИЛИ и НЕТ подключены выходы плюс и минус декодера команд через дополнительные элементы НЕТ, а к вторым входам элементов ИЛИ и НЕТ - вторые выходы дополнительных элементов НЕТ, к запрещакнци входам которых подключены выхсзды со ответствующих счетчиков числа коман входы которых подключены к выходам плюс и минус декодера комай соответственно flj . Недостатками этого приемного уст ройства в системах асинхронного сопряжения цифровых сигналов с двусто ронними временными сдвигами являются большая вероятность ошибок при приемке сдвоенных команд ++/ или -, которые формируются в момент введения стаффинга, и большое время вхождения в синхронизм после перерыва связи. Наиболее близким техническим решением к изобретению является прием ник команд стаффинга в системах асинхронного сопряжения цифровых потоков, содержащий последовательно соединенные интегратор, пороговый блок, первый элемент И, первый счет чик команд и элемент НЕТ, последовательно соединенные второй элемент И, второй счетчик команд и элемент ИЛИ, выход которого подсоединен к второму входу элемента НЕТ , причем второй выход порогового блока подсоединен к первому входу второго элемента И, второй вход которого объединен с вторым входом первого элемента И и подключен к шине Команды стаффицга первый вход интегратора подключен к шине Служеб ные символы , а второй вход элемен та ИЛИ подключен к шине Тактовая частота, второй выход первого счетчика подключен, к второму входу элемента ИЛИ., а второй выход второго счетчика ;;- к третьему входу элет мента НЕТ Однако данный приемник команд стаффинга в системах асинхронного сопряжения цифровых потоков имеет большое время вхождения в синхрониз и низкую достоверность приема команд стаффинга после перерыва связи. Цель изобретения - повьлиение достоверности приема команд .стаффинга при перерывах связи. Цель достигается тем, что в приеШик команд стаффинга, содержащий последовательно соединенные интегратор, пороговый блок, первый элемент И, первьаЯ счетчик команд и элемент НЕТ, последовательно соединенные второй элемент И, второй счетчик команд и элемент ИЛИ, выход которого подсоединен к второму входу элемента НЕТ , причем второй выход порогового блока подсоединен к первому входу второго элемента И, второй вход которого объединен к вторым входом первого элемента И и подключен к шине Команды стаффинга первый вход интегратора подключен к шине Служебные символы, а второй вход элемента ИЛИ - к шине Тактовая частота , введены-последовательно соединенные формирователь импульса опроса, третий элемент И, элемент сравнения и четвертый элемент И, а также инвертор, триггер, элемент памяти и пятый элемент И, выход которого подсоединен к дополнительному входу элемента ИЛИ, первый вход - к второму выходу порогового блока, а второй вход - к выходу элемента сравнения, второй вход которого объединен с первым входом элемента памяти, входом формирователя импульса опроса и подключен к шине Команды стаффинга, второй вход элемента памяти подключен к шине Цикловая синхронизация, а выход - к третьему входу элемента сравнения, первый вход которого объединен с первым входом триггера, второй вход которого объединен с третьим входом элемента памяти, входом инверПерерывтора ти подключен к шине связи, выход инвертора подсоединен к второму входу интегратора, вторым входам первого и второго счетчиков команд и второму входу третьего элемента И, к первому входу которого подключен выход триггера, при этом первый выход порогового блока через четвертый элемент И подсоединен к дополнительному входу элемента НЕТ. На фиг. 1 представлена структурно-электрическая схема приемника команд стаффинга; на фиг. 2 - эторы, поясняющие его работу. Приемник команд-стаффинга содержит интегратор 1, пороговый блок 2, элементы И 3 и 4, счетчики 5 и 6 команд, элемент ИЛИ 7, элемент НЕТ 8, шину 9 Соманды стаффинга, шину 1-0 Тактовая частота, выход 11 команд стаффинга, элемент 12 памяти, элемент 13 сравнения, триггер 14, элементы И 15 - 17, инвертор 18, формирователь 19 импульса опроса, шину 20 Перерыв связи, шину 21 Служебные символы и шину 22 Цикловая синхронизация, Приемник команд стаффинга работает следующим образом. Импульсы записи поступают с шины 10 через элементы ИЛИ 7 и НЕТ 8 на выход 11 приемника команд стаффинга Одновременно на шину 9 поступают команды стаффинга, которые подаются на входы элементов И 3 и 4, а на шину 21 поступает информация по дополнительному каналу о знаке, разности фаз между импульсами записи и считывания передающего устройства. Информации о знаке стаффинга накапливается в интеграторе 1, пороговый блок 2 сравнивает содержимое интегратора 1 с порогом и принимает решение о знаке предстоящего стаффинга. В соответствии с этим открывается элемент И 3 или 4, и приходящие команды стаффинга проходят на счетчик 5 или 6 команд. Счетчики 5 и б команд определяют количество подряд следующих команд одного знака. При обнаружении счетчиком 5 или б команд сдвоенной команды любого знака {++, - ) анализируется следующая команда, если она оказывается другого знака, чем две предыдущие, вырабатываются сигналы о введении стаффинга Причем, если сдвоенную команду обнаружил счетчик 5 команд, на его выходе, соединенном с входом элемента. ИЛИ 7, вырабатывается сигнал о введении дополнительного такта записи. Благодаря этому осуществляется запись дополнительного бита информации в запоминающее устройство. Если же сдвоенная команда обнаружена счетчиком б команд, то на его выходе, сое диненном с входом элемента НЕТ 8, вырабатывается сигнал, заНрещающий один такт записи. При обнаружении любым из счетчиков 5 или б команд строенной команда (1 или +++) стаффйнг не вводится. Если в системе связи возможны перерывы связи, то во время перерялва связи стаффинги могут быть приняты ложные или не приняты, и их действительно нужно отработать. И то н другое приводит к срыву цикловой синхронизации в системе разуплотнения более низкого порядка (неправиль ному разуплотнению, декодированию, если информация кодирована и т.п.), все это -значительно увеличивает время перерыва связи за счет увеличения времени вхождения в синхронизм после перерыва связи. Принцип умены№ния времени вхождения в синхронизм после перерыва связи достигается увеличением достоверности приема команд стаффинга при перерывах связи, что основано на использовании того факта, что после передачи сдвоенных команд стаффинга ) , которые формируются в момент введения стаффинга, меняется.порядок чередования команд (фиг. 2а). Время перерыва связи должно быть меньше периода значащих стаффингов (Тпер. Тста) Если .во время перерыва связи (фиг. 2S) прешла сдвоенная команда, то после перерыва изменяется порядок чередования команд ( и -). Запомнив чередования команд до перерыва СВЯЗ.И (фиг. 2Ь) , сравниваем его с порядком чередования команд после перерьта: изменения порядка чередования команд стаффинга говорят о том, что во время перерыва связи прошла сдвоенная команда, соответствующая моменту введения стаффинга, знак стаффинга определяется по информации дополнительного канала. Так как информация о знаке стаффинга накапливается, .а время перерыва связи Ti,ep. ; определения знака стаффинга оказывается достаточно информации, накопленной интегратором 1 до перерыва связи. При перерыве связи на приемник команд стаффинга на шину 20 приходит сигнал о перерыве связи, который запоминается триггером 14. Этот сигнал переводит элемент 12 памяти в режим запоминания порядка чередования команд стаффинга, а через инвертор 18 переводит интегратор 1 в режим запоминания накопленной информации, счетчики 5 и б команд сбрасывает в начальное состояние и запрещает счет, пока есть сигнсш перерыва связи. Для запоминания порядка чередования команд стаффинга используется сигнал цикловой синхронизации, который подается на шину 22 и далее на счетный вход элемента 12 памяти, который, перейдя в счетный режим, запоминает порядок чередования команд стаффинга до перерыва связи. По окончании-сигнала о перерыве связи элемент 13 сравнения сравнивает сигнал с выхода элемента 12 памяти с сигналом пришедшей команды с шины 9, результат сравнения опрашивается импульсом,, сформированным из 1-й после перерыва связи команды стаффинга формирователем 19 и элементо.м И 17. При несовпадении сигналов на выходе элемента 13 .сравнения появляется сигнал (фиг. 2) о том, что во время перерыва связи прошла сдвоенная команда, дсшее этот сигнал подается на элементы И 15 и 16 ив зависимости от знака на выходе порогового блока 2 на элементы ИЛИ 7 или НЕТ .8, отрабатывается стаффйнг.

1075433

Технико-экономическая эффектив-ема команд стаффиига,что позволит уменость приемника команд стаффинга заклю- ньшить время вхождения в синхронизм чается в увеличении достоверности при- системл связи после перерыва связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для асинхронного уплотнения каналов связи с временным разделением сигналов | 1973 |

|

SU485488A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

| УСТРОЙСТВО ДЛЯ АСИНХРОННОГО УПЛОТНЕНИЯКАНАЛОВ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМСИГНАЛОВ | 1973 |

|

SU453726A1 |

| Приемник команд стаффинга в системах асинхронного сопряжения цифровых потоков | 1975 |

|

SU515300A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи | 1981 |

|

SU1083389A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Устройство для передачи и приема цифровых сигналов с положительным стаффингом | 1975 |

|

SU657634A1 |

| Многоканальное устройство передачи и приема асинхронных цифровых сигналов | 1988 |

|

SU1555886A1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

ПРИЕМНИК КОМАНД СТАФФИНГА, содержащий п:оследовательно соединённые интегратор, пороговый блок, п.ервый элемент И, первый счетчик команд и элемент НЕТ, последовательно соединенные второй элемент И, второй счетчик команд и элемент ИЛИ, выход которого подсоединен к второму входу элемента НЕТ, причем второй выход порогового блока подсоединен к первому входу второго элемента И, второй вход которого объединен с вторым входом первого элемента И и подключен к шине Команды стаффинга , первый вход интегратора подключен к шине Служебные символы, а второй вход элемента ИЛИ - к шине Тактовая частота, о т л и ч а ю щ и йс я тем, что, с целью повышения достоверности приема команд стаффинга при перерывах свяэи, в него введены последовательно соединенные фор- мирователь импульса опроса, третий элемент И, элемент сравнения и четвертый элемент И, а также инвертор, триггер, элемент памяти и пятый элемент И, вьвсод которого подсоединен к дополнительному входу элемента ИЛИ, первый вход - к второму выходу порогового блока, а второй вход - к выходу элемента сравнения, второй вход которого объединен с первым входом элемента памяти, входом формирователя импульса опроса и подключен к шине Команды стаффинга, второй вход элемента памяти подключен к шине Цикловая синхронизация, а выход - к третьему входу элемента срав-§ нения, первый вход которого объеди- (Л нён с первым входом триггера, второй вход которого объединен с третьим входом элемента памяти, входом инвертора и подключен к шине Перерыв свяэи, выход инвертора под- g соединен к второму входу интегратора, вторым входам первого и второго счетчиков команд и второму входу третьего элемента И, к первому входу которого подключен выход триггера, при этом первый выход порогового блока череэ четвертый элемент И под СП соединен к дополнительному входУ эле 4 СО СО мента НЕТ.

f + -,ч-,-,,-|-«т ),,|-,Л,Р -I лI Zb --. - --t--- --- --4|- - --Фмг. Тстхрф.

-.-..- -..-..гФ14г.г Ij -к - 4- - -t-l- -i- -

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приемное устройство в системах асинхронного сопряжения цифровых сигналов с двустронними временнными сдвигами | 1973 |

|

SU470924A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приемник команд стаффинга в системах асинхронного сопряжения цифровых потоков | 1975 |

|

SU515300A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-23—Публикация

1982-11-19—Подача