Изобретение относится к технологий изготовления кремниевых интегральных стабилитронов, входящих в состав интегральных микросхем.

Цель изобретения - повышение выхода годных интегральных стабилитронов, входящих в состав интегральных микросхем, за счет уменьшения разброса опорного напряжения.

При формировании локальной области d первого типа проводимости d 1,9Xj возрастает разброс опорного напряжения на стабилитроне и становится не менее 2%. Верхняя граница размера локальной области первого типа проводимости ограничивается технологическими размерами и качеством электрического пробоя, так как с ростом топологических размеров увеличивается вероятность пробоя по кристаллографическим дефектом.

Предлагаемый способ использования для изготовления интегральных микросхем стабилизаторов напряжения 1151ЕН1, КР1157ЕН5А, Б.В,Г, Мотор 4.

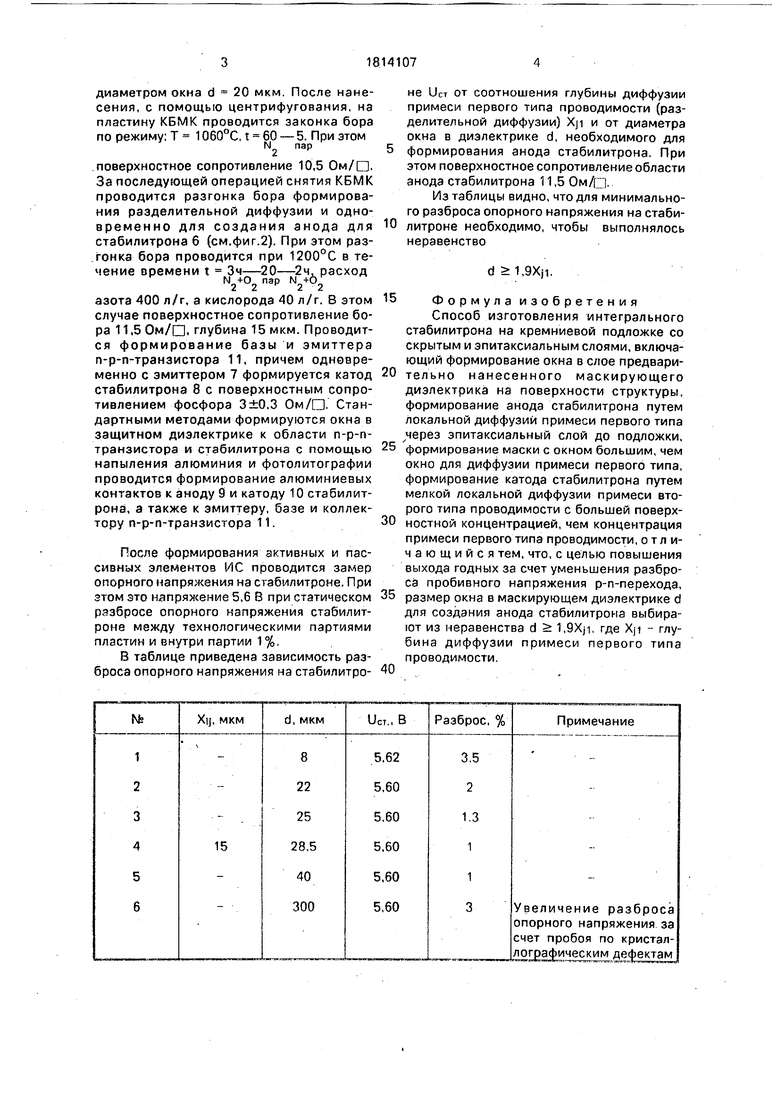

На исходной кремниевой подложке 1 (см.фиг.1), ориентированной в плоскости (ill), легированной бором до концентрации 4,5-10 , стандартными методами пленарной технологии формируют скрытый слой 2 п -типа проводимости, эпитаксиаль- Ный слой 3 n-типа проводимости с удельным сопротивлением 4 Ом;см и толщиной 14 мкм. С помощью стандартных методов фотолитографии формируются окна в маскирующем диэлектрике 4 под будущие области разделительной диффузии 3 и будущий анод стабилитрона в виде круга по топологии с

00

--ok

ь о

х|

диаметром окна d 20 мкм. После нанесения, с помощью центрифугования, на пластину КБМК проводится законна бора по режиму: Т 1060°С, t 60 - 5. При этом

N.

пар

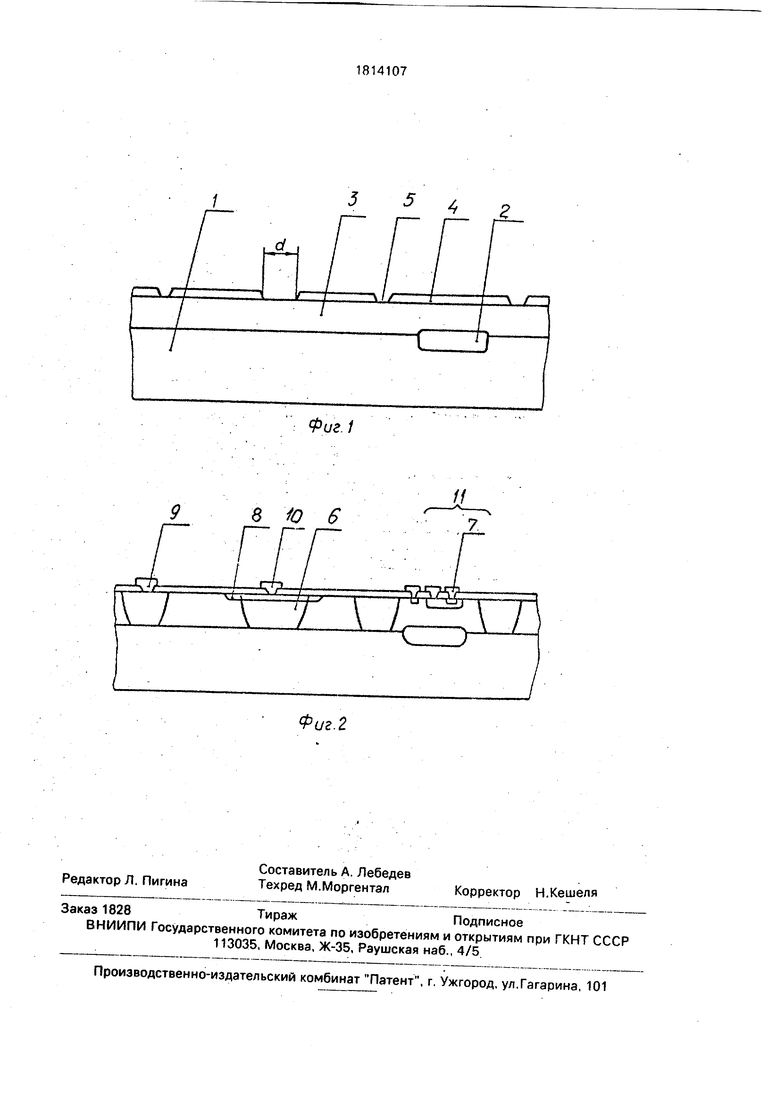

поверхностное сопротивление 10,5 Ом/П. За последующей операцией снятия КБМК проводится разгонка бора формирования разделительной диффузии и одновременно для создания анода для стабилитрона 6 (см.фиг.2). При этом разгонка бора проводится при 1200°С в течение времени t Зч-20-2ч, расход

N2+02 пар N2+62

азота 400 л/г, а кислорода 40 л/г. В этом случае поверхностное сопротивление бора 11.5 Ом/П. глубина 15 мкм. Проводится формирование базы и эмиттера п-р-п-транзистора 11, причем одновременно с эмиттером 7 формируется катод стабилитрона 8 с поверхностным сопротивлением фосфора 3±0.3 Ом/П. Стандартными методами формируются окна в защитном диэлектрике к области п-р-п- транзистора и стабилитрона с помощью напыления алюминия и фотолитографии проводится формирование алюминиевых контактов к аноду 9 и катоду 10 стабилитрона, а также к эмиттеру, базе и коллектору п-р-п-транзистора 11.

После формирования активных и пассивных элементов ИС проводится замер опорного напряжения на стабилитроне. При этом это напряжение 5,6 8 при статическом разбросе опорного напряжения стабилитроне между технологическими партиями пластин и внутри партии 1%,

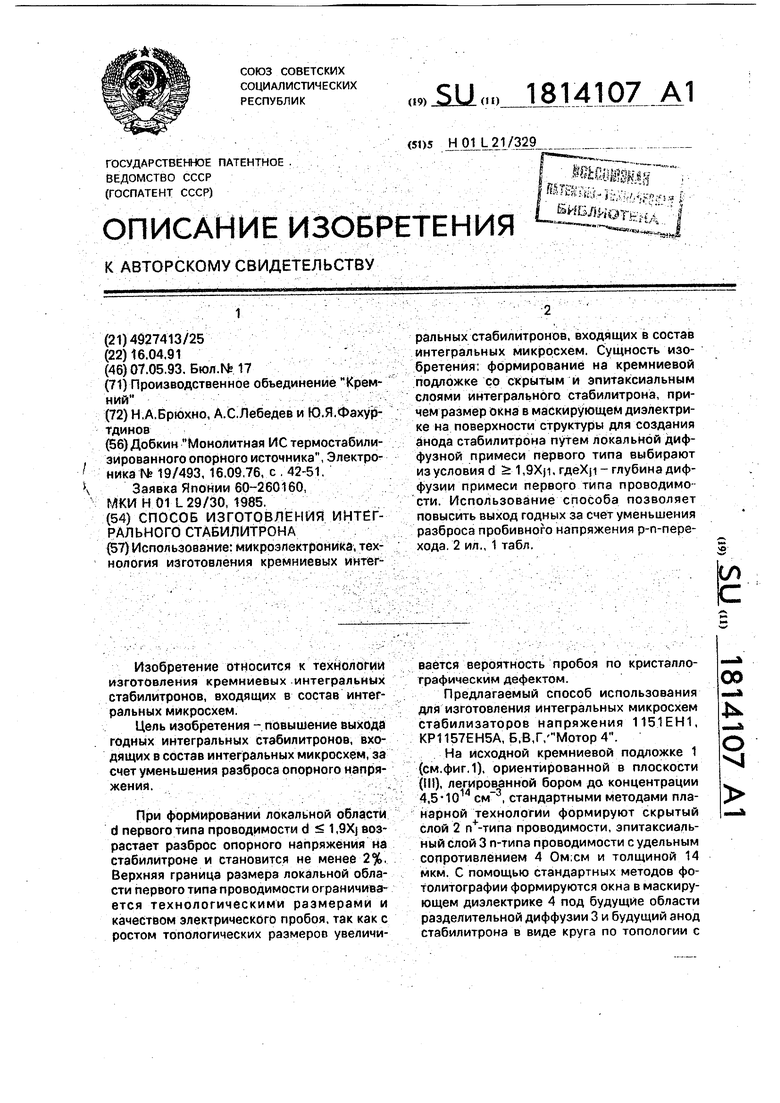

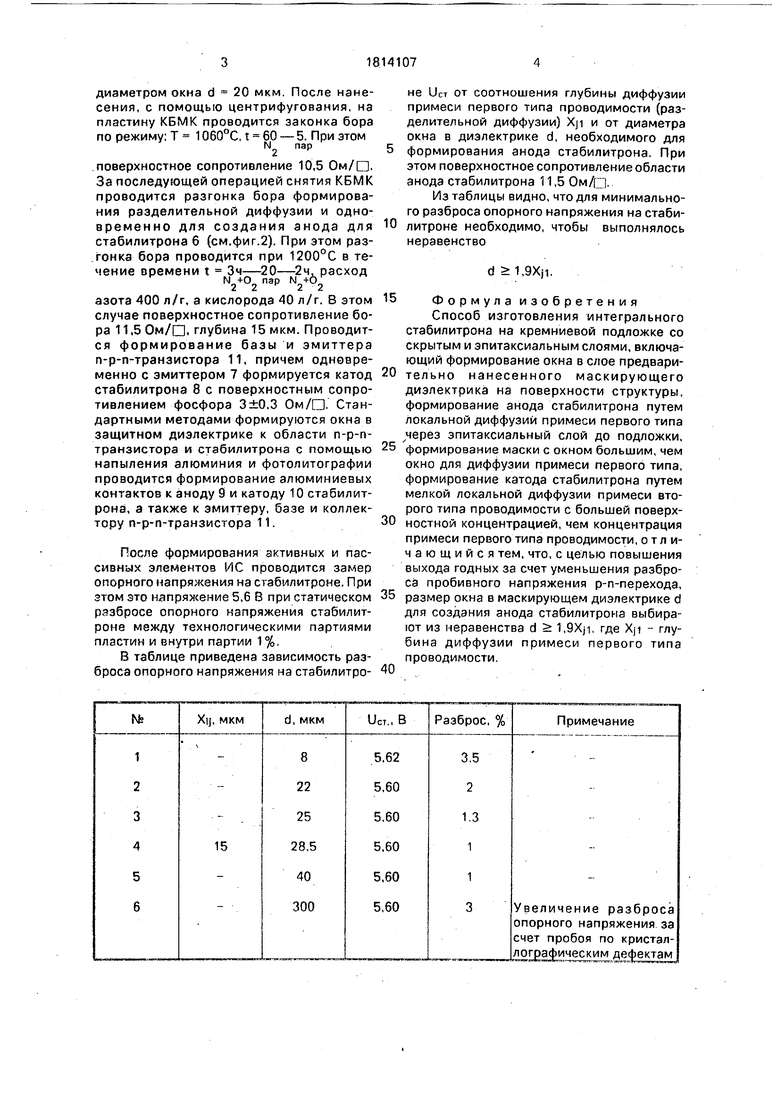

В таблице приведена зависимость разброса опорного напряжения на стабилитроне UCT от соотношения глубины диффузии примеси первого типа проводимости (разделительной диффузии) Xji и от диаметра окна в диэлектрике d, необходимого для

формирования анода стабилитрона. При этом поверхностное сопротивление области анода стабилитрона 11,5 Ом/п.

Из таблицы видно, что для минимального разброса опорного напряжения на стабилитроне необходимо, чтобы выполнялось неравенство

d

1.9Xji.

Формула изобретения Способ изготовления интегрального стабилитрона на кремниевой подложке со скрытым и эпитаксиальным слоями, включающий формирование окна в слое предвари- тельно нанесенного маскирующего диэлектрика на поверхности структуры, формирование анода стабилитрона путем локальной диффузии примеси первого типа через эпитаксиальный слой до подложки, формирование маски с окном большим, чем окно для диффузии примеси первого типа, формирование катода стабилитрона путем мелкой локальной диффузии примеси второго типа проводимости с большей поверхностной концентрацией,чем концентрация примеси первого типа проводимости, отличающийся тем, что, с целью повышения выхода годных за счет уменьшения разброса пробивного напряжения р-п-перехода, размер окна в маскирующем диэлектрике d для создания анода стабилитрона выбирают из неравенства d 1,9Xji, где Xji - глубина диффузии примеси первого типа проводимости.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ПОЛИКРЕМНИЕВЫМ РЕЗИСТОРОМ | 1990 |

|

SU1819070A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ СВЧ ПРИБОРОВ | 2013 |

|

RU2546856C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИОННОГО ЛЕГИРОВАНИЯ БОРОМ ОБЛАСТЕЙ p-n ПЕРЕХОДА ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ И ИНТЕГРАЛЬНЫХ СХЕМ | 2009 |

|

RU2399115C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1979 |

|

SU760837A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОСЛОЙНЫХ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1980 |

|

SU880167A1 |

| НИЗКОВОЛЬТНЫЙ ТЕРМОКОМПЕНСИРОВАННЫЙ СТАБИЛИТРОН И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1999 |

|

RU2162622C1 |

Использование: микроэлектроника, технология изготовления кремниевых интегральных стабилитронов, входящих в состав интегральных микросхем. Сущность изобретения: формирование на кремниевой подложке со скрытым и эпитаксиальным слоями интегрального стабилитрона, причем размер окна в маскирующем диэлектрике на поверхности структуры для создания анода стабилитрона путем локальной диффузной примеси первого типа выбирают из условия d 1,9Xji, глубина диффузии примеси первого типа проводимости. Использование способа позволяет повысить выход годных за счёт уменьшения разброса пробивного напряжения р-п-пере- хода. 2 ил., 1 табл.

Фиг.2

| Добкин Монолитная ИС термостабили- зированного опорного источника, Электроника № 19/493, 16.09.76, с .42-51 | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

Авторы

Даты

1993-05-07—Публикация

1991-04-16—Подача