J

00

00

XJ

о

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазирования дискретных сигналов | 1980 |

|

SU896780A2 |

| Устройство фазирования дискретных сигналов | 1978 |

|

SU681570A1 |

| Способ фазирования приемников дискретных сигналов | 1975 |

|

SU614545A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1986 |

|

SU1389005A2 |

| Устройство фазирования | 1976 |

|

SU604172A2 |

| Способ совместной передачи и приема цифровых и аналоговых данных | 1988 |

|

SU1644395A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1990 |

|

SU1732466A1 |

| Устройство фазирования регенераторов цифрового сигнала | 1978 |

|

SU786036A1 |

Изобретение относится к радиотехнике и может быть использовано в системах передачи данных. Цель - повышение помехоустойчивости фазирования приемников фазоманипулированйых сигналов. Устройство содержит задающий генератор 1, управляемый делитель 2 частоты, селектор 3 опережения, селектор 4 отставания, блок 5 выделения значащих моментов, блок 6 добавления, блок 7 вычитания, первый и второй сдвиговые регистры 8, 9, блок 10 предварительного усиления и селекции, приемник 11 фазоманипулированных сигналов, первый и второй мультипликаторы 12, 13, ключ 14, элемент задержки 15, детектор 16 огибающей, первый и второй компараторы 17, 18, элемент ИЛИ 19, инвертор 20, первый и второй триггеры 21, 22. В устройстве при низком качестве принимаемого сигнала, т.е. когда огибающая попадает в зоны стирания, в качестве корректирующего сигнала используется предварительно за- пол ненный корректирующий сигнал, сформированный при удовлетворительном качестве принимаемого сигнала. 2 ил. ел С

Vvz. i

Изобретение относится к радиотехнике и может быть использовано в системах передачи данных.

Цель изобретения - повышение помехоустойчивости фазирования приемников фазоманипулированных сигналов.

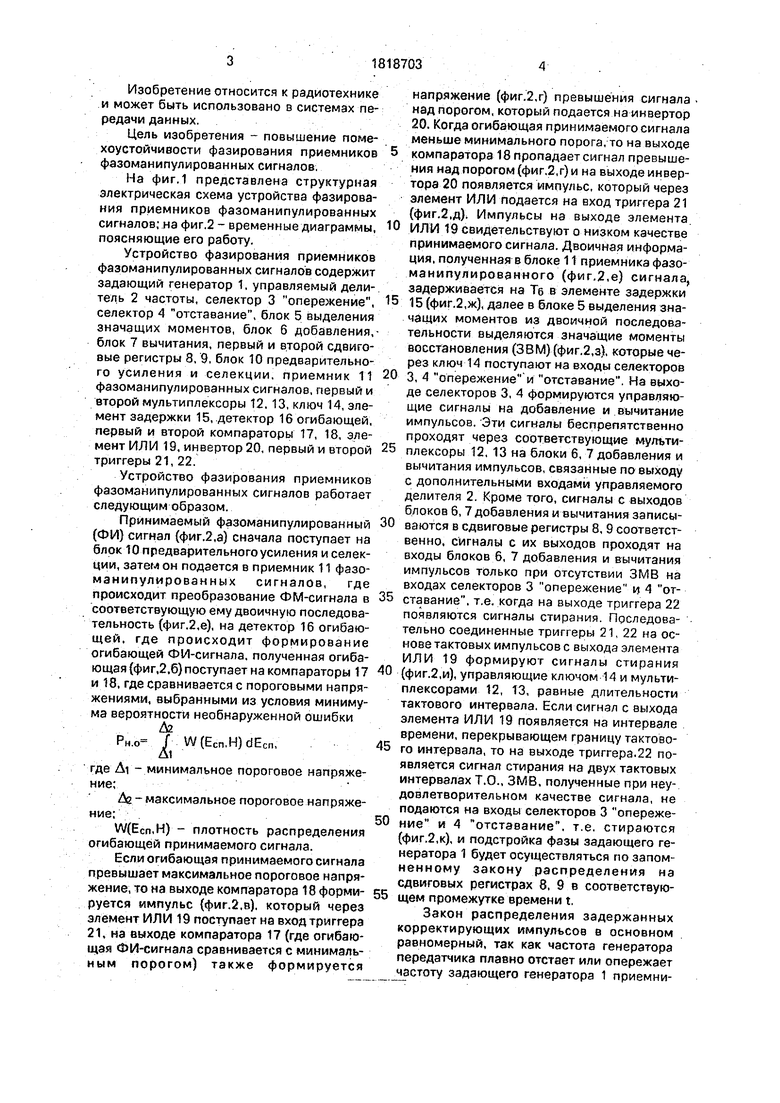

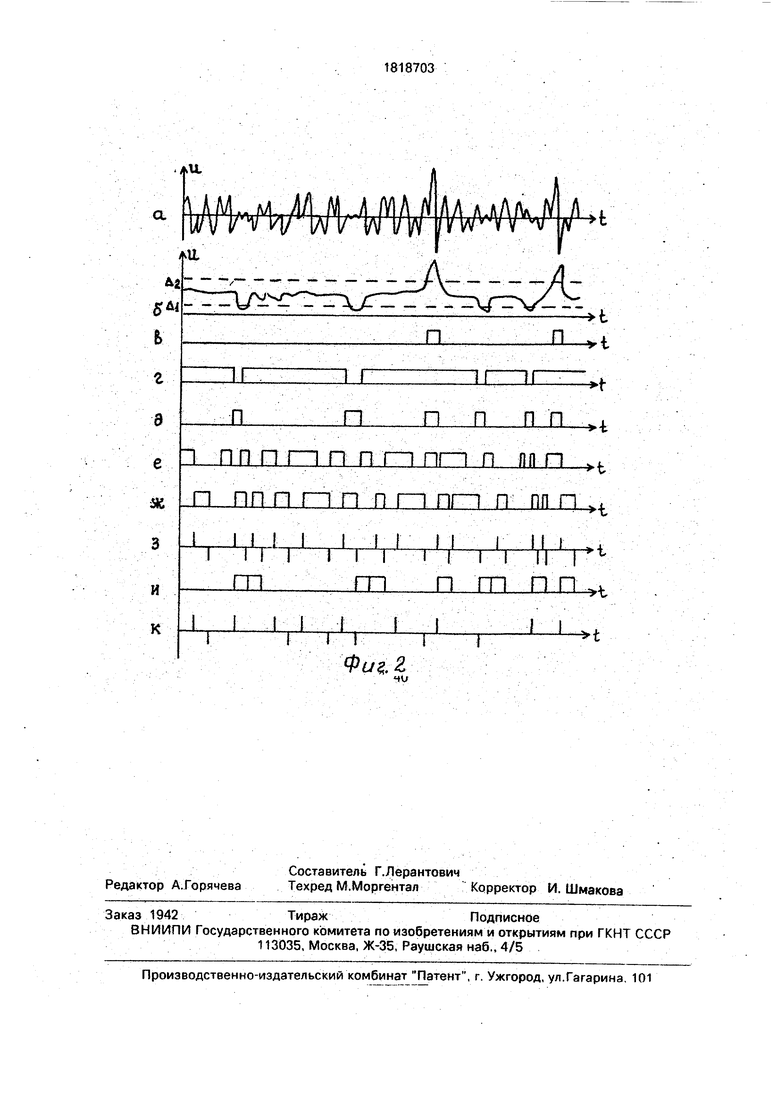

На фиг.1 представлена структурная электрическая схема устройства фазирования приемников фазоманипулированных сигналов; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство фазирования приемников фазоманипулированных сигналов содержит задающий генератор 1. управляемый дели-, тедь 2 частоты, селектор 3 опережение, селектор 4 отставание, блок 5 выделения значащих моментов, блок 6 добавления,- блок 7 вычитания, первый и второй сдвиговые регистры 8, 9, блок 10 предварительного усиления и селекции, приемник 11 фазоманипулированных сигналов, первый и второй мультиплексоры 12. 13, ключ 14, элемент задержки 15, детектор 16 огибающей, первый и второй компараторы 17, 18, элемент ИЛИ 19, инвертор 20, первый и второй триггеры 21, 22.

Устройство фазирования приемников фазоманипулированных сигналов работает следующим образом.

Принимаемый фазоманипулированный (ФИ) сигнал (фиг.2,а) сначала поступает на блок 10 предварительного усиления и селекции, затем он подается в приемник 11 фазо- манипулированных сигналов, где происходит преобразование ФМ-сигнэла в соответствующую ему двоичную последовательность (фиг,2,е), на детектор 16 огибающей, где происходит формирование огибающей ФИ-сигнала, полученная огибающая (фиг,2,б) поступает на компараторы 17 и 18, где сравнивается с пороговыми напряжениями, выбранными из условия минимума вероятности необнаруженной ошибки Дг

Рн.о Г W(Ecn,H)dEcn,

где Ai - минимальное пороговое напряжение;

As.-максимальное пороговое напряжение; .

W(Ecn.H) - плотность распределения огибающей принимаемого сигнала.

Если огибающая принимаемого сигнала превышает максимальное пороговое напряжение, то на выходе компаратора 18 формируется импульс (фиг.2,в), который через элемент ИЛИ 19 поступает на вход триггера 21, на выходе компаратора 17 (где огибающая ФИ-сигнала сравнивается с минималь- ным порогом) также формируется

напряжение (фиг.2,г) превышения сигнала - над порогом, который подается на инвертор 20. Когда огибающая принимаемого сигнала меньше минимального порога, то на выходе

компаратора 18 пропадает сигнал превышения над порогом (фиг.2,г) и на выходе инвертора 20 появляется импульс, который через элемент ИЛИ подается на вход триггера 21 (фиг.2.д) Импульсы на выходе элемента

ИЛИ 19 свидетельствуют о низком качестве принимаемого сигнала. Двоичная информация, полученная в блоке 11 приемника фазо- манипулированного (фиг.2,е) сигнала, задерживается на Те в элементе задержки

5 15 (фиг.2,ж), далее в блоке 5 выделения значащих моментов из двоичной последовательности выделяются значащие моменты восстановления (38М)(фиг.2,з), которые через ключ 14 поступают на входы селекторов

0 3, 4 опережение и отставание. На выходе селекторов 3, 4 формируются управляющие сигналы на добавление и вычитание импульсов. Эти сигналы беспрепятственно проходят через соответствующие муяьти5 плексоры 12, 13 на блоки 6, 7 добавления и вычитания импульсов, связанные по выходу с дополнительными входами управляемого делителя 2. Кроме того, сигналы с выходов блоков 6, 7 добавления и вычитания записы0 ваются в сдвиговые регистры 8, 9 соответственно, сигналы с их выходов проходят на входы блоков 6, 7 добавления и вычитания импульсов только при отсутствии ЗМВ на входах селекторов 3 опережение и 4 от5 ставание, т.е. когда на выходе триггера 22 появляются сигналы стирания. Последовательно соединенные триггеры 21, 22 на основе тактовых импульсов с выхода элемента ИЛИ 19 формируют сигналы стирания

0 (фиг.2,и), управляющие ключом 14 и мультиплексорами 12, ТЗ, равные длительности тактового интервала. Если сигнал с выхода элемента ИЛИ 19 появляется на интервале времени, перекрывающем границу тактово5 го интервала, то на выходе триггера.22 появляется сигнал стирания на двух тактовых интервалах Т.О., ЗМВ, полученные при неудовлетворительном качестве сигнала, не подаются на входы селекторов 3 опереже0 ние и 4 отставание, т.е. стираются (фиг.2,к), и подстройка фазы задающего генератора 1 будет осуществляться по запом- ненному закону распределения на сдвиговых регистрах 8, 9 в соответстаую5 щем промежутке времени t,

Закон распределения задержанных корректирующих импульсов в основном равномерный, так как частота генератора передатчика плавно отстает или опережает частоту задающего генератора 1 приемкика. В целом временное распределение импульсов, поступающих с выходов сдвиговых регистров 8, 9, в достаточной степени правильно отражает реальную скорость и направление расхождения фаз генератора передатчика и задающего генератора 1 приемника, что позволяет использовать эти импульсы для поддержания синфазности указанных генераторов при неудовлетворительном качестве принимаемого сигнала в каком-то промежутке времени. В предлагаемом устройстве корректировка фазы задающего генератора 1 осуществляется по ЗВМ, полученным при удовлетворительном качестве принимаемого колебания (фиг.2к), при низком качестве принимаемого колебания корректировка фазы задающего генератора 1 осуществляется по предварительно запомненным корректирующим импульсам, полученным при удовлетворительном каче- стве принимаемое колебания. Исходя из этого предлагаемое устройство позволяет повысить помехоустойчивость фазирова- ния приемников фазоманипулированных сигналов. Формула из обретения Устройство фазировэния приемников фазоманипулированных сигналов, содержащее задающий генератор, выход которого подключен к счетному входу управляемого делителя частоты, первый и второй сдвиговые регистры, блок выделения значащих моментов, селектор Опережение и селектор Отставание, первые входы которых соединены, и последовательно соединенные блок предварительного усиления и селекции и приемник фазоманипулированных сигналов, а также блок добавления и блок вычитания, выход которого подключен к первому дополнительному входу управляемого дели- ;теля частоты и входу второго сдвигового регистра, а выход блока добавления подключен к входу первого сдвигового регистра и второму дополнительному входу управляемого делителя частоты, первый

выход которого подключен к тактирующему входу первого сдвигового регистра и второму входу селектора Опережение, а второй выход управляемого делителя частоты подключен к тактирующему входу сдвигового регистра и второму входу селектора Отста- .вание, отличающееся тем, что, с целью повышения помехоустойчивости фазирова- ния приемников фазоманипулированных сигналов, введены первый и второй мультиплексоры, ключ, элемент задержки, детектор огибающей, первый и второй компараторы, инвертор, элемент ИЛИ и последовательно соединенные первый триггер и второй триггер, выход которого подсоединен к управляющему входу ключа, к информационному входу которого через последовательно соединенные элемент задержки и блок выделения значащих моментов подключен выход приемника фазоманипулированных сигналов, вход которого присоединен к входам детектора оги- бающей, выход которого подключен к входам первого и второго компаратора, при этом выход первого компаратора непосредственно, а выход второго компаратора через инвертор подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к входу первого триггера, к тактирующему входу которого и тактирующему входу второго триггера подключен второй вы ход управляемого делителя частоты, а выход второго триггера подсоединен к управляющим входам первого и второго мультиплексоров и ключа, выход которого подсоединен к первым входам селектора Опережение и селектора Отставание, выходы которых подключены к первым входам соответственно первого и второго мультиплексоров, к вторым входам которых подключены выходы соответственно первого и второго сдвиговых ре/истров, а выходы первого и второго мультиплексоров подключены к входам соответственно блока добавления и блока вычитания.

| Способ фазирования приемников дискретных сигналов | 1975 |

|

SU614545A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-05-30—Публикация

1991-06-04—Подача