1

Изобретение относится к технике связи и может быть использовано в приемных устройствах систем передачи дискретной информации.

Цель изобретения - повышение достоверности передачи информации.

На фиг. 1 представлена структурная схема буферного запоминающего устройствaj на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - схема адресного мультиплексора-, на фиг. 4 - схема блока управления; на фиг. 5 - пример реализации блока анализа буферной зоны} на фиг. 6 - пример реализации арифметико-логического блока.

автоподстройки, вый компаратор

Запоминающее устройство (фиг. 1) содержит блок 1 памяти, информационный вход 2, информационный выход 3, узел 4 фазовой

включающий фазо- 5, переключатель 6 режима и подстраиваемый генератор 7, счетчик 8 адресов чтения, счетчик 9 адресов записи, вход 10 синхронизации, вход 11 управления, селектор 12 буферной зоны, делитель 13 частоты, адресный мультиплексор 14, блок 15. управления, вход 16 синхронизации, вход 17 синхронизации цикла, блок 18 анализа буферной зоны, арифметико- логический блок 19 и регистр 20.

Ј

Од

сл

W 6

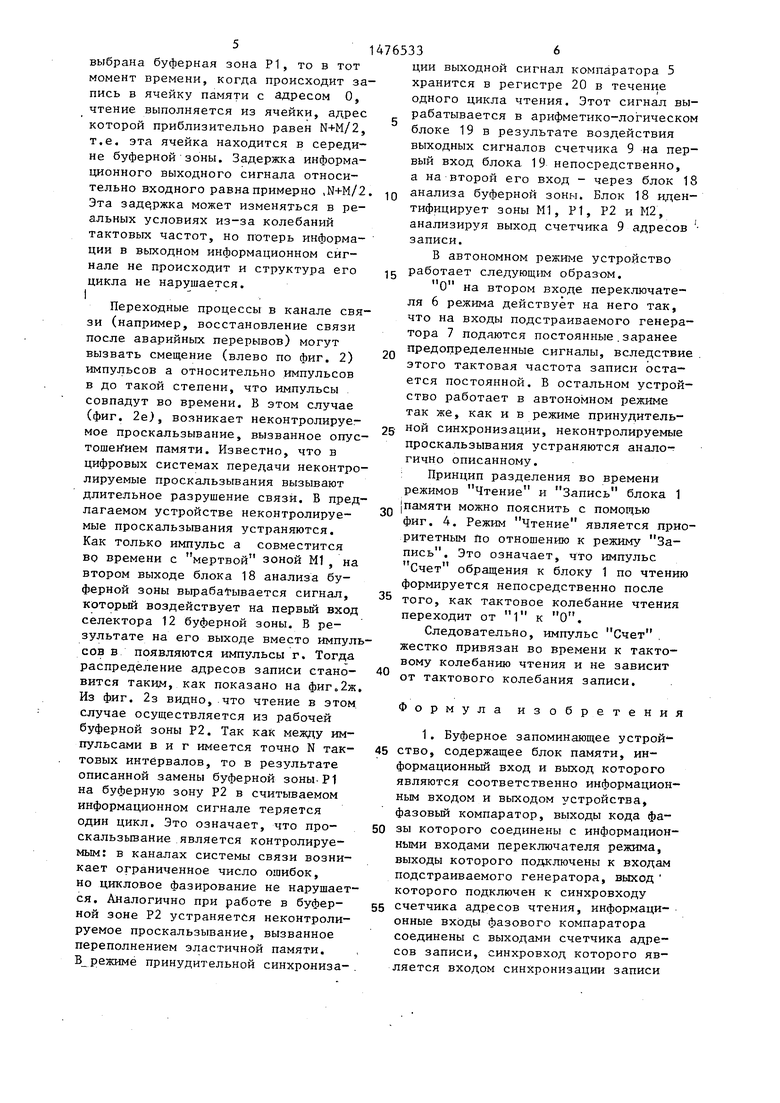

На фиг. 2 обозначены: а - импульсы на выходе делителя 13 частоты, период следования которых равен 2N тактовых интервалов чте- ния, где N - число бит в цикле информационного сигнала;

б - импульсы на входе 17 синхронизации цикла, период следования которых равен N тактовых интервалов записи j(

в - импульсы на выходе селектора 12, период следования которых равен 2N тактовых интервалов записи, при условии, что выбрана буферная зона Р1 запоминающего устройства ,

г - то же, при условии, что выбрана другая буферная зона Р2д - распределение адресов записи на выходах счетчика 9 относительно импульсов с при условии, что выбрана буферная зона Р1,

е - распределение буферных зон в запоминающем устройстве относительно адресов записи при условии, что выбрана буферная зона Р 1, где М1 и М2 - первая и вторая нерабочие (мертвые) зоны соответственно, Р1 и Р2 - соответственно первая и вторая рабочие зоны, причем для зо- ны М1 отведены ячейки блока 1 памяти с адресами от 0 до М-го, для зоны Р1 отведены ячейки блока 1 памяти с адресами от (М+1)-го до N-го1, для зоны Р2 отведены ячейки блока 1 памяти с адресами от (N+1)-ro до (2N-M)-ro для М2 отведены ячейки блока 1 памяти с адресами от

(2N-M+1)-ro до 2N-ro;

ж - то же, что ид, но при условии, что выбрана буферная зона Р2 ,

з - то же, что и е, но при условии, что выбрана буферная зона Р2.

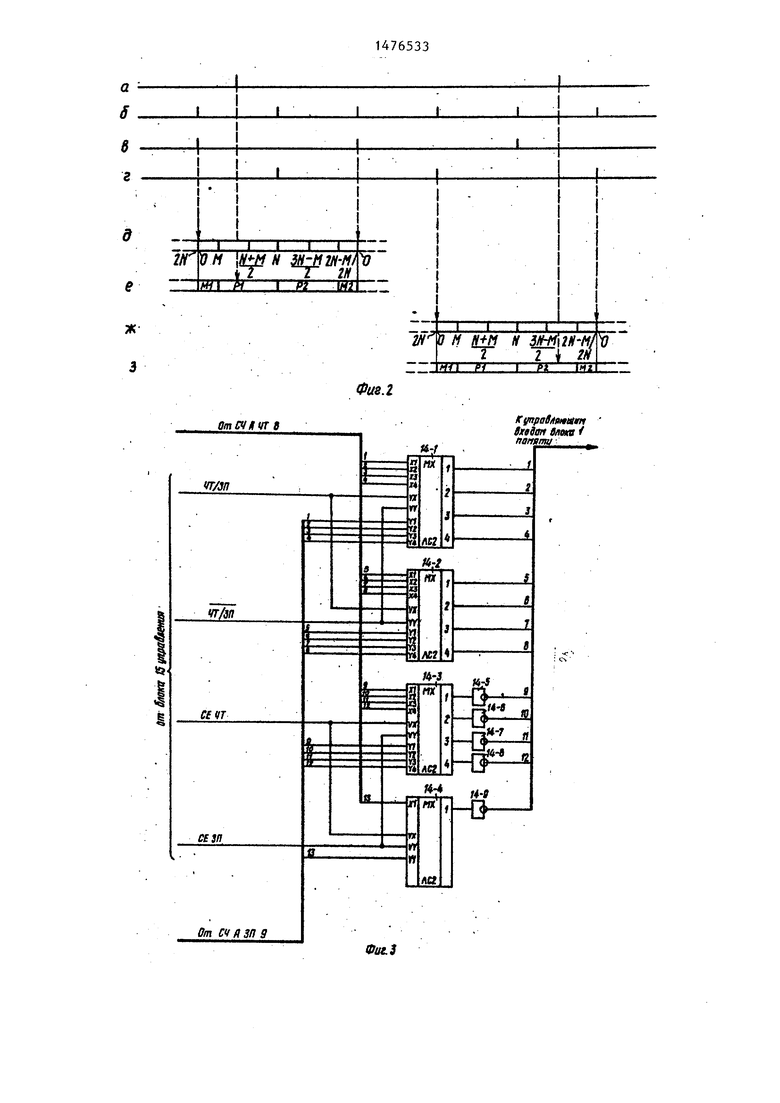

Адресный мультиплексор (фиг. 3) содержит мультиплексоры 14-1-14-4 и элементы НЕ 14-5-14-9.

Блок управления (фиг. 4) образуют JK-триггеры 15-1 и 15-2, элементы НЕ 15-3 и 15-4, D-триггеры 15-5 и 15-Ь, элементы ИЛИ-НЕ 15-7 и счетчики 15-8 и 15-9.

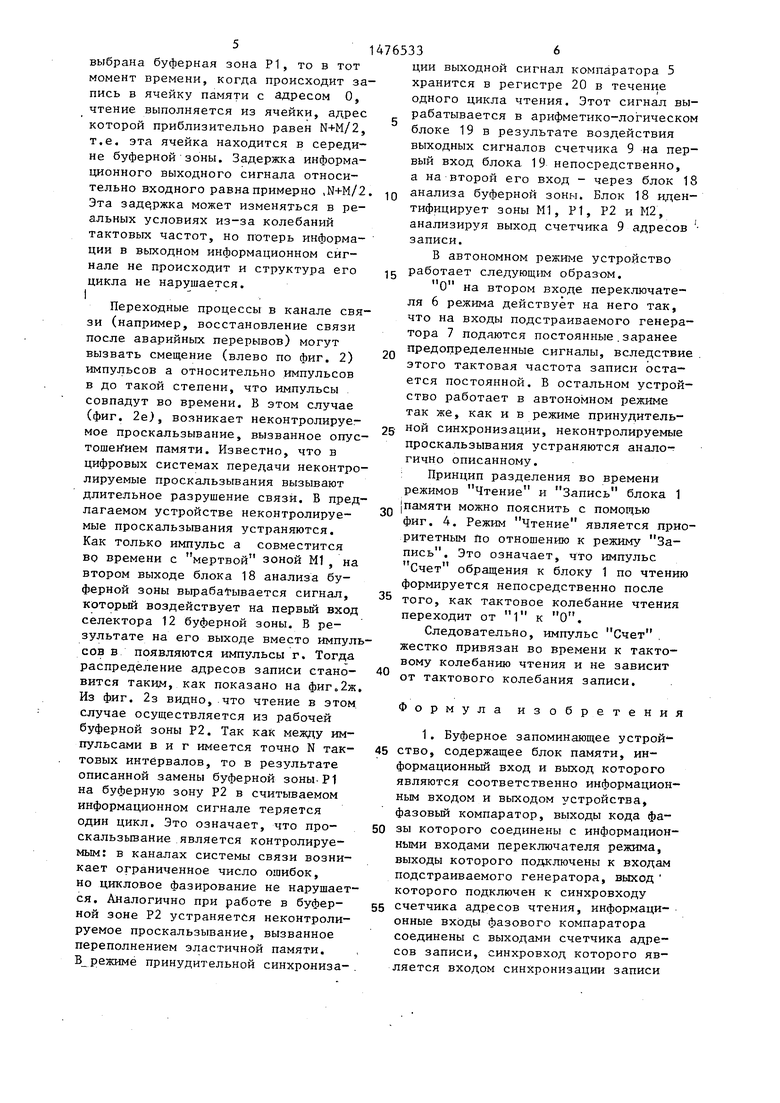

Блок анализа буферной зоны (фиг. 5 включает элементы И 18-1 - 18-8, элемент И-НЕ 18-9, элементы ИЛИ 18-10 - 18-15, элементы 18-16 и 18-17 равно- значности и элементы 18-18 и 18-19 неравнозначности.

Арифметико-логический блок (фиг.6 содержит БИС АЛУ 19-1 и 19-2, элемент ИЛИ 19-3., элементы И 19-4 и 19-5, элементы ИЛИ 19-6 и 19-7, элемент ИЛИ-НЕ 19-8 и элемент ИЛИ 19-9

Устройство предназначено для работы в двух режимах: в режиме принудительной синхронизации (на входе 11 управления имеет место высокий логический уровень управляющего сигнала - 1); в автономном режиме (на входе 11 управления имеет место низкий логический уровень управляющего сигнала - О).

В режиме принудительной синхронизации устройство работает следующим образом.

1 на втором входе переключателя 6 режима действует на него так, что выходные сигналы регистра 20 непосредственно подаются на входы подстраиваемого генератора 7 для управления его частотой.

Входной информационный сигнал, в каждом цикле которого содержится N бит, поступает через вход 2 в блок 1 памяти. Каждый бит входного сигнала записывается в ячейку памяти блока 1, адрес которой определяется выходными сигналами счетчика 9 На первый (счетный) вход этого счетчика по шине 10 поступает тактовый синхросигнал с частотой записи, а на второй его вход (Установка О импульс с выхода селектора 12 буферной зоны. Период следования этих импульсов равен 2N тактовых интервалов записи, поэтому модуль счета счетчика 9 равен 2N,

В установившихся условиях работы устройства фазовый компаратор 5 через переключатель режима 6 так управляет частотой генератора 7, что она равна частоте записи. Блок 15 управления воздействует на блок 1 памяти и адресный мультиплексор 14 так, что режим Чтение имеет место только в пределах первой четверти каждого тактового интервала чтения, а запись осуществляется в пределах каждого тактового интервала записи, свободного от режима чтения. Сигналы, которые обеспечивают чередование режимов Чтение и Запись, вырабатываются в блоке 15 управления под воздействием сигналов тактовой частоты записи, тактовой частоты чтения и высокой частоты,

Как показано на фиг. 2а-е, если в установившихся условиях работы

выбрана буферная зона Р1, то в тот момент времени, когда происходит запись в ячейку памяти с адресом О, чтение выполняется из ячейки, адрес которой приблизительно равен N+M/2, т.е. эта ячейка находится в середине буферной зоны. Задержка информационного выходного сигнала относительно входного равна примерно ,N+M/2 Эта задержка может изменяться в реальных условиях из-за колебаний тактовых частот, но потерь информации в выходном информационном сигнале не происходит и структура его цикла не нарушается. I

Переходные процессы в канале связи (например, восстановление связи после аварийных перерывов) могут вызвать смещение (влево по фиг. 2) импульсов а относительно импульсов в до такой степени, что импульсы совпадут во времени. В этом случае (фиг. 2е), возникает неконтролируемое проскальзывание, вызванное опустошением памяти. Известно, что в цифровых системах передачи неконтролируемые проскальзывания вызывают длительное разрушение связи. В предлагаемом устройстве неконтролируемые проскальзывания устраняются. Как только импульс а совместится во времени с мертвой зоной Ml , на втором выходе блока 18 анализа буферной зоны вырабатывается сигнал, который воздействует на первый вход селектора 12 буферной зоны. В результате на его выходе вместо импулсов в появляются импульсы г. Тогда распределение адресов записи становится таким, как показано на фиг„2ж Из фиг. 2з видно, что чтение в этом случае осуществляется из рабочей буферной зоны Р2. Так как между импульсами виг имеется точно N тактовых интервалов, то в результате описанной замены буферной зоны-Р1 на буферную зону Р2 в считываемом информационном сигнале теряется один цикл. Это означает, что проскальзывание является контролируемым: в каналах системы связи возникает ограниченное число ошибок, но цикловое фазирование не нарушается. Аналогично при работе в буферной зоне Р2 устраняется неконтролируемое проскальзывание, вызванное переполнением эластичной памяти. В режиме принудительной синхрониза

ции выходной сигнал компаратора 5 хранится в регистре 20 в течение одного цикла чтения. Этот сигнал вырабатывается в арифметико-логическом блоке 19 в результате воздействия выходных сигналов счетчика 9 на первый вход блока 19 непосредственно, а на второй его вход - через блок 18 анализа буферной зоны. Блок 18 идентифицирует зоны М1, Р1, Р2 и М2, анализируя выход счетчика 9 адресов записи.

В автономном режиме устройство работает следующим образом.

О на втором входе переключателя 6 режима действует на него так, что на входы подстраиваемого генератора 7 подаются постоянные.заранее предопределенные сигналы, вследствие этого тактовая частота записи остается постоянной. В остальном устройство работает в автономном режиме так же, как и в режиме принудитель- 5 ной синхронизации, неконтролируемые проскальзывания устраняются аналогично описанному.

Принцип разделения во времени

5

0

режимов Чтение и Запись блока 1

|памяти можно пояснить с помощью фиг. 4. Режим Чтение является приоритетным йо отношению к режиму Запись. Это означает, что импульс Счет обращения к блоку 1 по чтению формируется непосредственно после того, как тактовое колебание чтения переходит от 1 к О.

Следовательно, импульс Счет . жестко привязан во времени к тактовому колебанию чтения и не зависит от тактового колебания записи.

Формула изобретения

1. Буферное запоминающее устрой- ство, содержащее блок памяти, информационный вход и выход которого являются соответственно информационным входом и выходом устройства, фазовый компаратор, выходы кода фазы которого соединены с информационными входами переключателя режима, выходы которого подключены к входам подстраиваемого генератора, выход которого подключен к синхровходу счетчика адресов чтения, информационные входы фазового компаратора соединены с выходами счетчика адресов записи, синхровход которого является входом синхронизации записи

устройства, управляющий вход переключателя режима является входом управления устройства, отличающееся тем, что, с целью повышения достоверности передачи информации, в устройство введены селектор буферной зоны, делитель частоты, адресный мультиплексор и блок управления, причем первый вход блока управления является входом синхронизации устройства, второй вход блока управления соединен с входом синхронизации записи устройства, третий вход блока управления подключен к вы ходу подстраиваемого генератора и к входу делителя частоты, выход которого соединен с входом сброса

входом селектора буферной зоны и с синхровходом фазового компаратора, выход признака зоны которого подключен к одноименному входу селектора буферной зоны, вход стробирова- пия которого является входом синхронизации цикла устройства, выход селектора буферной зоны соединен с входом сброса счетчика адресов записи, выходы которого подключены к информационным входам первой группы адресного мультиплексора, информационные входы второй группы которого соединены с выходами счетчика адресов чтения, адресного мультиплексора

с

0

5

0

выходы которого подключены к адресным входам блока памяти, вход записи-чтения которого соединен с одноименным выходом блока управления и с первым управляющим входом адресного мультиплексора, второй, третий и четвертый управляющий входы которого подключены соответственно к инверсному выходу записи-чтения и к выходам выборки записи и чтения блока управления.

2. Устройство по п. 1, отличающееся тем, что фазовый компаратор содержит блок анализа буферной зоны, арифметико-логический блок и регистр, причем входы блока анализа буферной зоны соединены с входами первой группы арифметико-логического блока и -являются информационными входами фазового компаратора, выходы группы блока анализа буферной зоны подключены к входам второй группы арифметико-логического блока, выходы которого соединены с информационными входами регистра, выходы которого явля- ются информационными выходами фазового компаратора, выход блока анализа буферной зоны и синхровход регистра являются соответственно выходом признака зоны и синхровходом фазового компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

Изобретение относится к технике связи и может быть использовано в приемных устройствах систем передачи дискретной информации. Целью изобретения является повышение достоверности передачи информации. Устройство содержит блок памяти, адресный мультиплексор, блок управления, счетчик адресов чтения, счетчик адресов записи, селектор буферной зоны, переключатель режима, подстраиваемый генератор, делитель частоты и фазовый компаратор, содержащий блок анализа буферной зоны, арифметико-логический блок и регистр. Цель изобретения достигается увеличением информационной емкости блока памяти в два раза до 2N ячеек (N-число бит в цикле группового сигнала) и автоматическим выбором буферной зоны, благодаря чему допускаются только "проскальзывания" в форме повторения или удаления точно одного цикла группового сигнала. В результате "проскальзывание" не вызывает потери циклового фазирования на всей сети, а приводит лишь к случайным ошибкам в каналах многоканальных систем. 1 з.п. ф-лы, 6 ил.

11 Управление

7)

tfr ЈЈ, JtrdU

5

м

II вход (шит высокая частота)

о

tf-5

cff.

ffi

с

г

Фиг. 5

/5-У

-ОУГ/5/7

да

frf ГЈУГ

(Ш

Э:

I:

15-8 f

-Рй

«ш

I

3

V:

18-9

16-15 Ь

От мётчика

Задресоб

записи

Фиг. 6

| Буферное запоминающее устройство | 1977 |

|

SU705517A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Системы передачи сообщений | |||

| М.: Связь, 1976, с | |||

| Прибор для вычерчивания конических сечений | 1922 |

|

SU457A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1989-04-30—Публикация

1987-06-26—Подача