(54) УСТРОЙСТВО ФАЗИРОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазирования дискретных сигналов | 1978 |

|

SU681570A1 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1981 |

|

SU1040616A1 |

| Способ фазирования приемников дискретных сигналов | 1975 |

|

SU614545A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации сигналов времени | 1984 |

|

SU1167577A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1983 |

|

SU1104679A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| Устройство для цикловой синхронизации | 1976 |

|

SU640439A1 |

1

Изобретение относится к электросвязи и может быть использовано в телеграфии и передаче данных, а также в контрольно-измерительной аппаратуре.

По основному авт. св.,№ 681570 известно устройство фазирования дискретных сигналов, содержащее последовательно соединенные задающий генератор, делитель частоты и блок управления, другой вход которого соединен с выходом приемника и входом датчика перерывов, регистр сдвига, вход которого соединен с выходом делителя частоты, а также триггер, первый и второй элементы И, первый, второй и третий элементы ИЛИ, при этом выходы блока управления подключены соответственно к входам первого элемента ИЛИ, второго элемента ИЛИ и к входам триггера, выходы которого через элементы И подключены соответственно к другим входам первых двух элементов ИЛИ, выходы ко торых подключены к соответствукяг.м входам делителя частоты и третьего элемента ИЛИ, выход которого подключен к другому входу регистра сдвига, выход которого подключен к вторым входам первого и второго элементов И, третьи входы которых соединены с выходом датчика перерывов 1 Т.

10

Однако известное устройство обладает невысокой точностью фазирования при помехах типа перерывов.

Цель изобретения - повьппение точности фазирования.

15

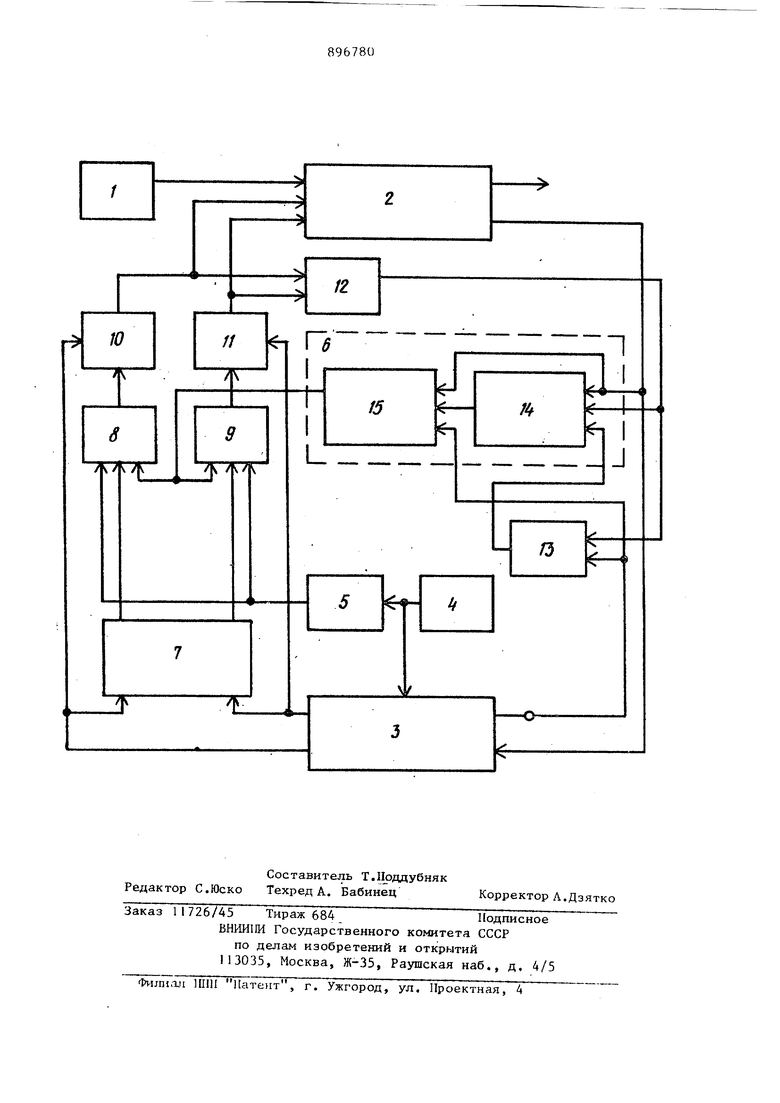

Для достижения цели в устройство фазирования дискретных сигналов введен дополнительный элемент ИЛИ, установочный вход которого подсоединен к установочному выходу блока уп20равления и установочному входу регистра сдвига, другой вход которого соединен с другим входом дополнитель наго элемента ШШ, выход которого подключен к дополнительному установочному входу регистра сдвига. Причем регистр сдвига выполнен в виде двух последовательно соединен ных подрегйстров сдвига, при этом вход первого подрегистра сдвига со цинен с входом второго подрегистра сдвига и является входом регистра сдвига, другой вход первого подрегистра сдвига является другим входом регистра сдвига, дополнительный установочнь1й вход которого является дополнительным входом первого подрегистра сдвига, выход которого подключен к другому входу второгоподрегистра сдвига, установочный вход которого является установочным входом регистра сдвига. На чертеже представлена структур но-электрическая схема устройства. Устройство фазирования дискретных сигналов содержит задающий гене ратор 1, делитель 2 частоты, блок 3 управления, приемник 4, датчик 5 перерывов, регистр 6 сдвига, триг гер 7, первый элемент И 8, второй элемент И 9., первый элемент ИЛИ 10 второй элемент ИЛИ 11, третий элемент ШМ 12, дополнительный элемент ШШ 13, первый подрегистр 14 сдвига и второй подрегистр 15 сдвига, составляющие регистр 6 сдвига. Устройство работает следующим об разом. Путем деления частоты следования импульсов от задающего генератора на выходе управляемого делителя 2 фор шруется опорный сигнал, период следования которого соответствует скорости передачи, т.е. равен длительности элементарной посылки вход ного сигнала, снимаемого с выхода приемника 4. В блоке 3 управления с помощью селекторов опережения- и отставания, управляемых соответству ющими полупериодами опорного сигнала (называемыми зонами опережения и отставания), производится сравнен опорного и входного сигналов и определяется расхождение по фазе меж. ду ними и знак этого расхождения. Блок 3 производит также обработку (усреднение) результатов фазового сравнения и выдает через элемент HJM 10 или через элемент ИЛИ 11 соответствуклций корректируюпщй сигнал на добавление в делитель 2 к поступающим от генератора 1 одного импульса (когда опорный сигнал отста04ет по фазе от входного) или на вычитание одного импульса (когда опорный сигнал опережает входной сигнал) . При отсутствии перерыва в канапе связи импульсы от блока 3 корректируют фазу опорного сигнала на выходе делителя 2 и одновременно через элемент ИЛИ 12 поступают на информационный вход регистра 6, тактирующий вход которого подключен к выходу делителя 2. Кроме того, эти импульсы поступают на соответствующие раздельные входы триггера 7, осуществляющего по ним коммутацию выхода регистра 6 на соответствующий управляемый вход- делителя 2 с автономном режиме коррекции. При появлении.в канале связи перерыва, т.е. при пропадании входного сигнала, устройство переходит в автономный режим работы коррекции фазы опорного сигнала в соответствии с откидаемой фазой входного сигнала. В этом случае датчиком 5 перерывов, связанным по входу с выходом приемника 4, вырабатывается сигнал управления, разрешаюищй работу элемента И 8 и элемента И 9, связанных по другим входам с выходом регистра 6 (запоминающего частоту следования корректирующих импульсов) и с соответствующими выходами три1- гера 7. В соответствии с состоянием триггера 7 (запоминанлдего, по существу, знак фазового расхояадения, предшествующий данному перерыву) в рабочем Состоянии находится элемент И 8 или элемент И 9. Следовательно, корректирукхцие импульсы от регистра 6 через один из этих элементов и соответствующий элемент ИЛИ 10 или П поступают на нухшый управляемый вход делителя 2, а через элемент ШМ 12 - на вход регистра 6, обеспечивая, темсамым, их циклическое повторение при длительном перерыве и непрерывную коррекцию в автономном р ежиме. При появлении входного сигнала устройство переходит из автономного в обычный режим работы. Если перед появлением входного сигнала произошла коррекция по импульсу от регистра 6 и этот импульс находится в одном из разрядов первого подрегистра 14, то корректирующий импульс, сформированный по фронту входного сигнала, по информационному Bxofty

устанавливают первый триггер под- регистра 4 в единицу, а остальные его разряды через элемент ИЛИ 13в ноль. Следовательно, на стыке перерыв-сигнал, если импульсы на регистре 6 оказываются слишком близкими, то один из них исключается, обеспечивая,тем самым пpaктичecки их равномерное распределение вдоль регистра 6. При этом допустимое расстояние (временной интервал) между импульсами определяется количеством разрядов подрегистра 14, подключенного последовательно ко второй части регистра б, т.е; ко второму подрегистру 15, В начале работы устройства подрегистр 15 приводится в исходное состояние установочным сигналом с выхода блока 3 управления непосредственно, а подрегистр 14 приводится в исходное состояние этим же сигналом через элемент ИЛИ 13.

Предлагаемое устройство отличается от аналоговых известных устройств повышенной точностью фазирования в условиях работы по каналу, для которого характерно частое появление помех типа перерывов.

Повышенная точность коррекции приводит к повышению достоверности принимаемых данных, особенно, при высокой скорости их передачи, к уменьшению времени вхождения аппаратуры в синхронизм после длительного перерыва в канале связи, уменьшая при этом и время занятия канала под передачу определенного объема информации.

Формула изобретения

Устройство фазирования дискретных сигналов по авт. св. № 68157 отличающееся тем, что, с целью повьшения точности фазирования, введен дополнительный элемент ИЛИ, установочный вход которого подсоединен к установочному выходу блока управления и установочному входу регистра сдвига, другой вход которого соединен с другим входом дополнительного элемента ИЛИ,

выход которого подключен к ДОПОЛ1Штельному установочному входу : регистра сдвига.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-01-07—Публикация

1980-03-24—Подача