Изобретение относится к цифровой автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки цифровой информации.

Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности реализации любой из мажаритарных функций "М или более из N", где М < N, a M, N любые целые числа.

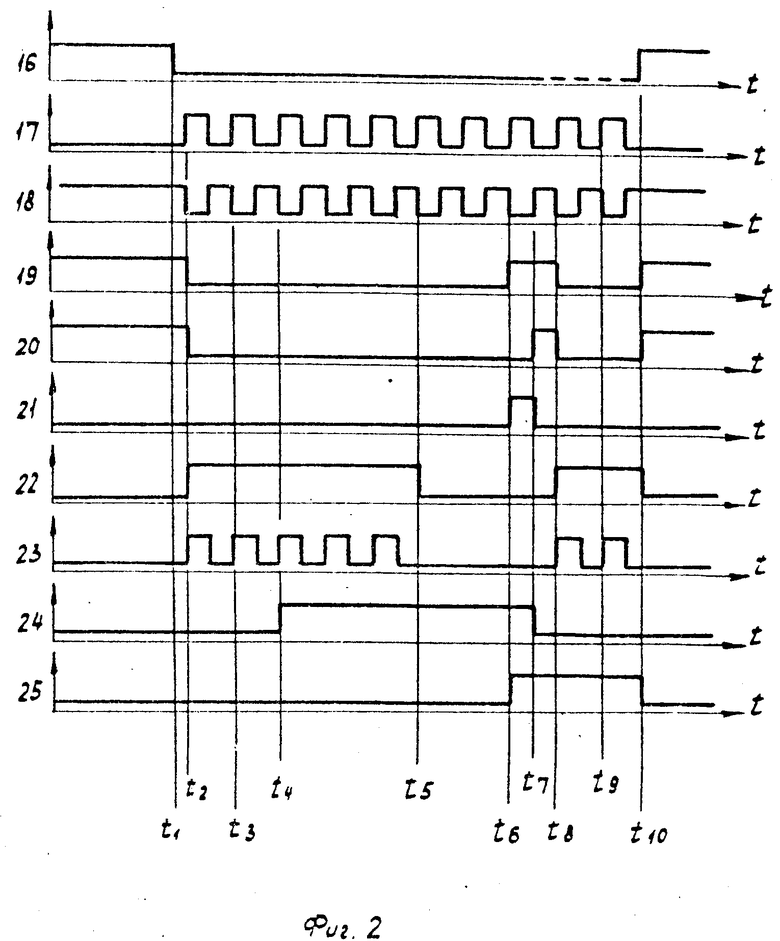

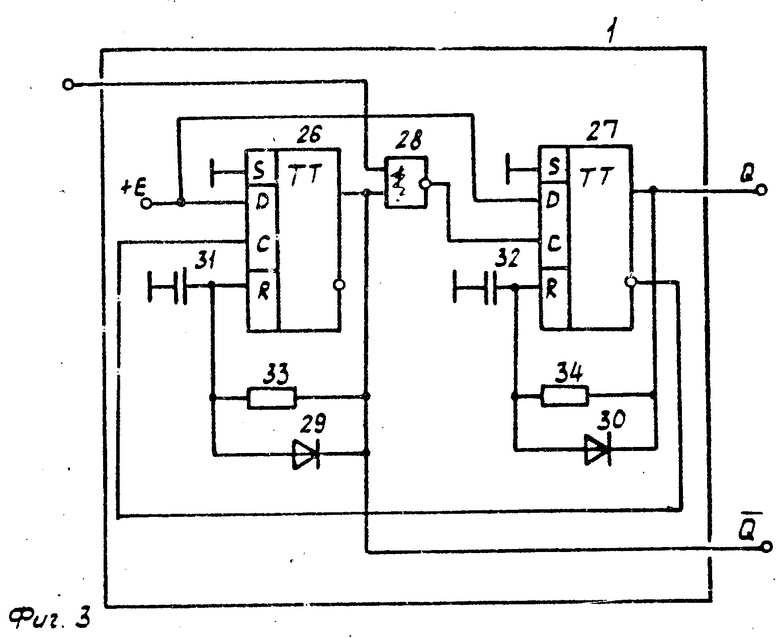

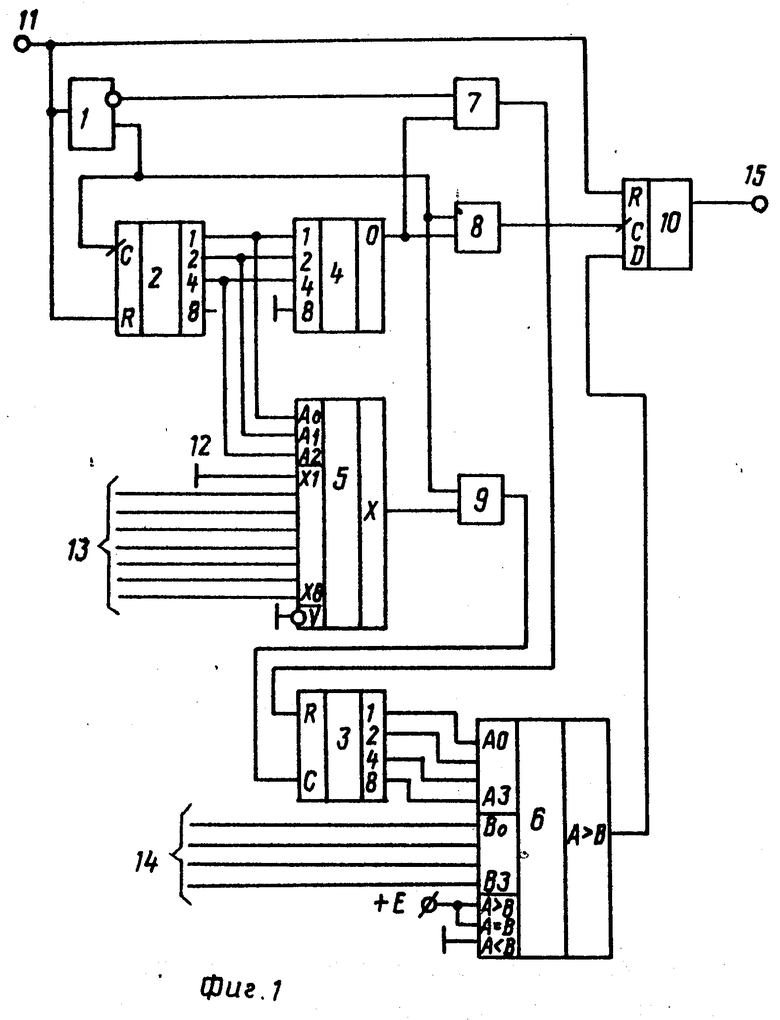

На фиг.1 приведена схема заявляемого мажоритарного элемента для 2≅ N ≅7; на фиг.2 временные диаграммы его работы; на фиг.3,4 схемы возможных вариантов выполнения управляемого генератора импульсов и коммутатора соответственно, причем на фиг.2: 16 уровни сигналов на шине 11 управления; 17, 18 уровни сигналов на прямом и инверсном выходах генератора 1; 19.25 уровни сигналов на выходах соответственно дешифратора 4, элементов И7, И8, коммутатора 5, элемента И9, коммутатора 6 и D-триггера 10.

Мажоритарный элемент содержит управляемый генератор импульсов 1, первый 2 и второй 3 счетчики, дешифратор 4, коммутатор 5, цифровой компаратор 6, первый 7, второй 8 и третий 9 элементы И, D-триггер 10, шину 11 управления, шину 12 нулевого логического сигнала, шины 13 переменных, дополнительные шины 14 переменных и выходную шину 15. Шина 11 управления соединена с входом управления генератора 1 и входами сброса счетчика 2 и D-триггера 10. Прямой выход генератора 1 соединен с тактовым входом счетчика 2, первым входом элемента И9 и с вторым входом элемента И8, инверсный выход с первым входом элемента И7. Второй вход элемента И7 соединен с первым входом элемента И8, выход с входом сброса счетчика 3. Разрядные выходы счетчика 2 соединены с соответствующими разрядными входами дешифратора 4 и адресными входами коммутатора 5, информационные входы которого, начиная с второго, соединены с соответствующими шинами 13 переменных, первый информационный вход соединен с шиной 12 нулевого логического сигнала, а выход с вторым входом элемента И9. Выход элемента И9 соединен с тактовым входом счетчика 3, разрядные выходы которого соединены с соответствующими входами числа А компаратора 6, входы числа В которого соединены с соответствующими шинами 14 переменных. Выход "А > В" компаратора 6 соединен с информационным входом D-триггера 10, тактовый вход которого соединен с выходом элемента И8, а выход с выходной шиной 15.

Мажоритарный элемент (фиг. 1) выполнен на базе интегральных микросхем серии 564. При этом генератор 1 выполнен по схеме фиг.3 (на D-триггерах 26 и 27, элементе ИЛИ-НЕ 28, диодах 29 и 30, конденсаторах 31 и 32, резисторах 33 и 34), может выполняться и по другим аналогичным схемам. Счетчики 2 и 3 выполнены на двоичных четырехразрядных счетчиках микросхемы 564 ИЕ10. Дешифратор 4 выполнен на двоично-десятичном дешифраторе 564 ИД1, может быть выполнен на элементе 3 ИЛИ-НЕ микросхемы 564 ЛЕ10 с последующей инверсией его выходного сигнала, D-триггер 10 выполнен на D-триггере микросхемы 564 ТМ2, коммутатор 5 на восьмиканальном мультиплексоре 564 КП2, компаратор 6 на цифровом четырехразрядном компараторе 564 ИП2, элементы И7, И8, И9 на элементах И-НЕ микросхемы 564 ЛА7 с последующей инверсией их выходных сигналов на таких же элементах.

Для выполнения мажоритарных функций "М или более из N" для N > 7, т.е. для большего количества шин 13 переменных, чем показано на фиг.1, достаточно увеличить количество информационных входов и соответственно количество адресных входов коммутатора, количество разрядов двоичных счетчиков 2 и 3, количество входов дешифратора 4 и компаратора 6. Например, для увеличения N для 15 у мажоритарного элемента на фиг. 1 достаточно выход старшего разряда двоичного счетчика 2 соединить с входом старшего разряда дешифратора 4, выполнить дешифратор 4 на элементе 4 ИЛИ (на микросхеме 564 ЛЕ6 с последующей инверсией) и увеличить количество информационных входов коммутатора 5 од 16, количество его адресных входов до 4. Последнее может быть реализовано, например, на базе двух коммутаторов 35, 36 (типа 564 КП2) с тремя адресными входами, элемента ИЛИ-НЕ 37, инвертора 38 и резисторов 39, 40, по схеме фиг. 4.

Для реализации мажоритарных функций "М или более из N" для 15 < N < 31 разрядность счетчиков 2 и 3, дешифратора 4, компаратора 6 и адресных входов коммутатора 5 должно быть увеличено до 5, а количество информационных входов коммутатора 5 до 32. В любом случае принцип работы мажоритарного элемента остается неизменным.

Работает мажоритарный элемент, приведенный на фиг.1, следующим образом. Рассмотрим его работу при выполнении конкретной мажоритарной функции, например, функции "3 или более из 5".

В исходом состоянии на шине 11 управления поддерживается уровень логической "1", а на шинах 13, 14 переменных- уровень логического "0". При этом генератор 1 не работает, на его прямом выходе уровень логического "0", на инверсном выходе уровень логической "1", счетчик 2 и D-триггер 10 принудительно удерживаются в нулевом состоянии уровнем логической "1" на шине 11 управления. На выходах счетчика 2, D-триггера И и элемента И 8 уровень логического "0". Поскольку на всех адресных входах коммутатора 5 уровни логического "0", то на его выход выдается уровень логического "0" с его первого (Х1) входа). На выходе элемента И9 уровень логического "0", на выходе элемента И7 уровень логической "1", чем счетчик 3 принудительно удерживается в нулевом состоянии. На всех входах чисел А и В и, следовательно, на выходе компаратора 6 уровень логического "0". Указанное исходное состояние мажоритарного элемента сохраняется до подачи разрешающего работу сигнала (уровня логического "0") по шине 11 управления.

Для нормальной работы устройства необходимо до подачи указанного разрешающего сигнала выбрать мажоритарную функцию, которую устройство должно выполнять. Выбор конкретной функции из совокупности мажоритарных функций "М или более из N" заключается в выборе чисел N и М. Выбор числа N заключается, в свою очередь, в выборе для контроля количества шин из шин 13 переменных (лишние из этих шин постоянно подключаются к шине логического "0"), а выбор числа М заключается в задании по шинам 14 переменных двоичного кода числа М.

В рассматриваемом нашем случае М 3. Но поскольку в мажоритарном элементе (фиг. 1) у компаратора 6 используется выход А > В, то на входы числа В компаратора 6 нужно подавать двоичный код числа М-1, в нашем случае код числа 2. Следовательно, на информационные входы В0, В2 и В3 компаратора 6 по шинам 14 переменных должен быть подан уровень логического "0", на информационный вход В1 уровень логической "1". Выберем для контроля подряд первые пять из шин 13 переменных, то есть шины, соединенные с информационными ходами Х2.Х6 коммутатора 5, и подадим по ним уровни логической "1".

Из схемы мажоритарного элемента (фиг.1) видно, что при вводе числа М и "выборе" числа N уровни сигналов на выходах его составных функциональных элементов остаются неизменными, т.е. исходное состояние мажоритарного элемента сохраняется.

При подаче по шине 11 управления разрешающего сигнала уровня логического "0" (фиг. 2, поз.16, t1) снимается "запрет" с входов сброса счетчика 2, D-триггера 10, с входа управления генератора 1, и последний запускается начинает формировать синфазные тактовые импульсы на своих выходах (фиг.2, поз. 17, 18).

По фронту (положительному перепаду) первого же тактового импульса с прямого выхода генератора 1 счетчик 2 переключается в состояние, соответствующее числу 1. При этом на выходе дешифратора 4 устанавливается уровень логического "0" (фиг.2, 19, t2), что приводит к установлению уровня логического "0" на выходе элемента И7, т.е. к снятию запрета с R-входа счетчика 3. Одновременно на выход коммутатора 5 выдается информация с его второго (Х2) информационного входа. В нашем случае это уровень логической "1" (фиг.2, 22, t2). При этом на первом входе элемента И9 присутствует первый импульс с прямого выхода генератора 1, поэтому он проходит через элемент И7 на тактовый вход счетчика 3 (фиг.2, 23, t2), последний переключается в состояние, соответствующее числу 1, и с его выходов двоичный код числа 1 поступает на разрядные входы числа А компаратора 6. Однако это не приводит к изменению исходного уровня сигнала логического "0" на выходе компаратора 6.

При поступлении второго импульса с прямого выхода генератора 1 (фиг.2, 17, t3) счетчик 2 переключается в состояние, соответствующее числу 2, с его выходов двоичный код числа 2 поступает на входы дешифратора 4 и на адресные входы коммутатора 5. При этом уровень логического "0" на выходе дешифратора 4 сохраняется, на выход коммутатора 5 выдается информация с его третьего (Х3) информационного входа также уровень логической "1", т.е. уровень логической "1" на выходе коммутатора сохраняется. Это приводит к тому, что указанный второй импульс с прямого выхода генератора 1 также проходит через элемент И9 (фиг.2, 23, t3) на тактовый вход счетчика 3. При этом счетчик 3 переключается в состояние, соответствующее числу 2, и с его выходов двоичный код числа 2 поступает на разрядные входы числа А компаратора 6. Однако это также не приводит к изменению уровня логического "0" на выходе компаратора 6.

При поступлении третьего импульса с прямого выхода генератора 1 (фиг.2, 17, t4) счетчик 2 переключается в состояние, соответствующее числу 3, и с его выходов двоичный код числа 3 поступает на входы дешифратора 4 и на адресные входы коммутатора 5. При этом уровень логического "0" на выходе дешифратора 4 сохраняется, на выход коммутатора 5 выдается информация с его четвертого (Х4) информационного входа в нашем случае также уровень логической "1". Следовательно, уровень логической "1" на выходе коммутатора 5 также сохраняется. Это приводит к прохождению и третьего импульса с прямого выхода генератора 1 через элемент И9 (фиг.2, 23, t4) на тактовый вход счетчика 3. При этом счетчик 3 переключается в состояние, соответствующее числу 3, и двоичный код числа 3 поступает на разрядные входы числа А компаратора 6, что приводит к появлению на его выходе уровня логической "1" (фиг.2, 24, t4), который поступает на информационный вход D-триггера 10. Однако это не приводит к изменению состояния D-триггера 10, поскольку на его тактовом входе с выхода дешифратора 4 через элемент И8 все еще поддерживается исходный уровень логического "0".

При поступлении четвертого и пятого импульсов с прямого выхода генератора 1 счетчики 2, 3 переключаются аналогично в состояния, соответствующие числам 4 и 5. При этом уровень логического "0" на выходе дешифратора 4 и уровень логической "1" на выходах коммутатора 5 и компаратора 6 сохраняются, поскольку на пяти информационных входах подряд (Х2.Х6) последнего в нашем случае подана логическая "1".

При поступлении шестого импульса с прямого выхода генератора 1 (фиг.2, поз. 17, t5) счетчик 2 переключается в состояние, соответствующее числу 6, и с его выходов двоичный код числа 6 поступает на входы дешифратора 4 и адресные входы коммутатора 5. При этом уровень логического "0" на выходе дешифратора 4 сохраняется, а на выход коммутатора 5 выдается информация с его седьмого (Х7) информационного входа, в нашем случае это уровень логического "0" (фиг. 2, поз.22, t5). Это приводит к тому, что шестой импульс с прямого выхода генератора 1 через элемент И9 не проходит (возможный короткий "пичок" напряжения на выходе элемента И9, обусловленный задержкой сигнала на выходе коммутатора 5, может быть устранен, при необходимости, известными способами, например, подключением к выходу элемента И9 небольшой емкости).

При поступлении седьмого импульса с прямого выхода генератора 1 счетчик 2 переключается в состояние, соответствующее числу 7. Однако это не приводит к изменению уровня логического "0" на выходе дешифратора 4, а также коммутатора 5, поскольку на его восьмом (Х8) входе в нашем случае имеется уровень логического "0". Следовательно, указанный седьмой импульс генератора 1 через элемент И9 на тактовый вход счетчика 3 так же, как и шестой импульс, не проходит. На выходе компаратора 6 сохраняется уровень логической "1". D-триггер 10 также остается в исходном состоянии, поскольку на его тактовом входе сохраняется уровень логического "0".

При поступлении восьмого импульса с прямого выхода генератора 1 (фиг.2, 2, t6) счетчик 2 по фронту этого импульса переключается в свое исходное нулевое состояние, при этом на всех его разрядных выходах устанавливается уровень логического "0". Это приводит к тому, что на выходе дешифратора 4 восстанавливается исходный уровень уровень логического "0" (фиг.2, 19, t6), и указанный восьмой импульс проходит через элемент И8 (фиг.2, 21, t6) и переключает D-триггер 10 в единичное состояние, поскольку на информационном входе последнего присутствует уровень логической "1". В результате на выходной шине 15 появляется уровень логической "1" выходной сигнал (фиг.2, 25, t6), свидетельствующий о том, что мажоритарная функция "3 или более из 5" выполнена. В дальнейшем уровень логической "1" на выходе D-триггера 10, т.е. выходной сигнал мажоритарного элемента сохраняется, независимо от количества формируемых генератором 1 импульсов, до снятия разрешающего сигнала (уровня логического "0") с шины 11 управления. При этом в интервале между восьмым и девятым импульсами с прямого выхода генератора 1 на выходе элемента И7 устанавливается уровень логической "1" (фиг.2, 20, t8-t7), который сбрасывает счетчик 3 в исходное нулевое состояние, что приводит к восстановлению уровня логического "0" на выходе компаратора 6 (фиг.2, 24, t7).

При поступлении девятого и последующих импульсов с прямого выхода генератора 1 счетчики 2 и 3 работают так же, как работали при поступлении первого и последующих импульсов генератора 1, но при этом уровень логического "0" на выходе компаратора 6 и уровень логической "1" на выходе D-триггера 10 (выходной сигнал) сохраняются.

При снятии с шины 11 управления разрешающего сигнала (фиг.2, 16, t10 ) D-триггер 10 устанавливается в нулевое состояние, тем самым снимается выходной сигнал (фиг.2, 25, t10). Одновременно генератор 1 прекращает формирование импульсов, счетчики 2, 3 сбрасываются в исходное нулевое состояние. При этом на выходах дешифратора 4 и элемента И7 восстанавливается исходный уровень логической "1", на выходе коммутатора 5 уровень логического "0". Таким образом, мажоритарный элемент после снятия разрешающего сигнала с шины 11 управления сам устанавливается в исходное состояние и готов к работе.

При выполнении остальных мажоритарных функций из совокупности "М или более из N" мажоритарный элемент (фиг.1) работает аналогично. Всего мажоритарный элемент (фиг. 1) может выполнять следующую совокупность мажоритарных функций:

"1 или более из 7 (6, 5, 4, 3, 2)",

"2 или более из 7 (6, 5, 4, 3)",

"3 или более из 7 (6, 5, 4)",

"4 или более из 7 (6, 5)",

"5 или более из 7 (6)",

"6 или более из 7"

Для реализации любой из указанных мажоритарных функций "М или более из N" достаточно задействовать нужное количество из шин 13 переменных (N), остальные из этих шин подключить к общей шине (с уровнем логического "0"), а по шинам 14 переменных подать двоичный код соответствующего числа М-1. Например, для выполнения мажоритарной функции "4 или более из 6" одну из шин 13 переменных необходимо подключить к шине с уровнем логического "0", по любым четырем или более из остальных шести указанных шин подать уровень логической "1", а по шинам 14 переменных двоичных код числа М 1 3. Тогда после подачи разрешающего сигнала по шине 11 управления по фронту четвертого импульса, поступившего на тактовый вход счетчика 3, на выходной шине 15 появится выходной сигнал, который сохранится до снятия разрешающего сигнала с шины 11 управления. При этом фронт выходного сигнала совпадет с фронтом четвертого импульса генератора 1 только в том случае, если уровень логической "1" будет подан по первым четырем или более шинам подряд из шин 13 переменных. Если на одну из первых четырех из задействованных в нашем случае шести шин 13 переменных, соединенных с информационными входами Х2.Х4 коммутатора 5, подан уровень логического "0", например, по шине, соединенной с входом Х3 коммутатора 5, то фронт выходного сигнала устройства совпадает с фронтом пятого импульса генератора 1. Это обусловлено тем, что второй импульс генератора 1 через элемент И9 на тактовый вход счетчика 3 не пройдет, так как при втором импульсе генератора 1 (и после него до фронта третьего импульса) на второй вход элемента И9 с выхода коммутатора 5 будет выдан уровень логического "0" с информационного входа Х3 последнего.

Из описания работы заявляемого мажоритарного элемента видно, что oн обладает более широкими функциональными возможностями, является универсальным, поскольку позволяет выполнить все мажоритарные функции "М или более из N" при M < N, где M, N любые целые числа, без дополнительных аппаратных затрат. Изменение выполняемой функции устройства осуществляется только выбором нужного количества из шин 13 переменных (N) и подачей кода числа М-1 по шинам 14 переменных.

В институте собран и испытан макет заявляемого мажоритарного элемента. Макет был выполнен на базе микросхем серии 564 в соответствии с фиг.1 и 2, при этом длительность импульсов генератора 1 была выбрана равной 1 мс при скважности 2.

Испытания макета показали реализуемость и работоспособность заявляемого устройства, подтвердили достижение поставленной цели.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2239037C1 |

| Способ обнаружения дефектов обмоток якоря электрической машины и устройство для его осуществления | 1989 |

|

SU1698846A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345203C2 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для многоканальной магнитной записи и воспроизведения последовательности импульсов | 1987 |

|

SU1483482A1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное устройство контроля температурных режимов инкубаторов | 1983 |

|

SU1157528A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

Использование: изобретение относится к цифровой автоматике и вычислительной технике и позволяет расширить функциональные возможности мажоритарного элемента. Сущность изобретения: мажоритарный элемент содержит управляемый генератор импульсов (1), 2 счетчика (2,3); дешифратор (4), коммутатор (5), цифровой компаратор (6), 3 элемента И (7 - 9) и D-триггер (10). 4 ил.

МАЖОРИТАРНЫЙ ЭЛЕМЕНТ, содержащий коммутатор, три элемента И, шины переменных, шину нулевого логического сигнала, соединенную с первым информационным входом коммутатора, дешифратор, выход которого соединен с первым входом второго элемента И, и выходную шину, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности реализации любой из мажоритарных функций "М или более из N", где М < N, а М, N целые числа, в него введены генератор импульсов, два счетчика, цифровой компаратор, D триггер и шину управления, соединенная с входом управления генератора импульсов и входами сброса первого счетчика и D триггера, прямой выход генератора импульсов соединен с тактовым входом первого счетчика, первым входом первого элемента И и с вторым входом второго элемента И, инверсный выход с первым входом третьего элемента И, второй вход которого соединен с первым входом второго элемента И, выход с входом сброса второго счетчика, разрядные выходы первого счетчика соединены с соответствующими разрядными входами дешифратора и адресными входами коммутатора, информационные входы которого, начиная с второго, соединены с соответствующими шинами переменных, выход с вторым входом первого элемента И, выход которого соединен с тактовым входом второго счетчика, разрядные выходы которого соединены с соответствующими входами числа А цифрового компаратора, входы числа В которого являются дополнительными шинами переменных, а выход "А > В" соединен с информационным входом D триггера, тактовый вход которого соединен с выходом второго элемента И, а выход с выходной шиной.

| Мажоритарный элемент | 1988 |

|

SU1538249A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-05-27—Публикация

1991-04-04—Подача