Изобретение относится к цифровой вычислительной технике и предназначено для использования в однородных вычислительных структурах для реализации нечетких алгоритмов.

Целью изобретения является повышение быстродействия ячейки.

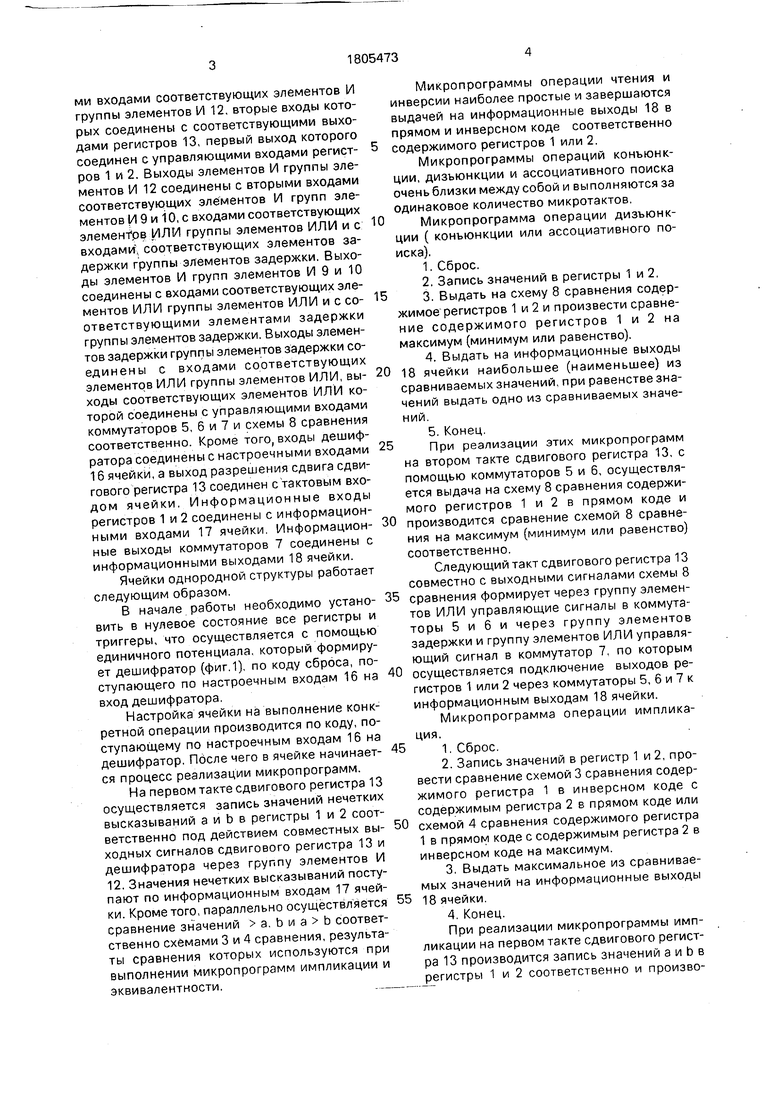

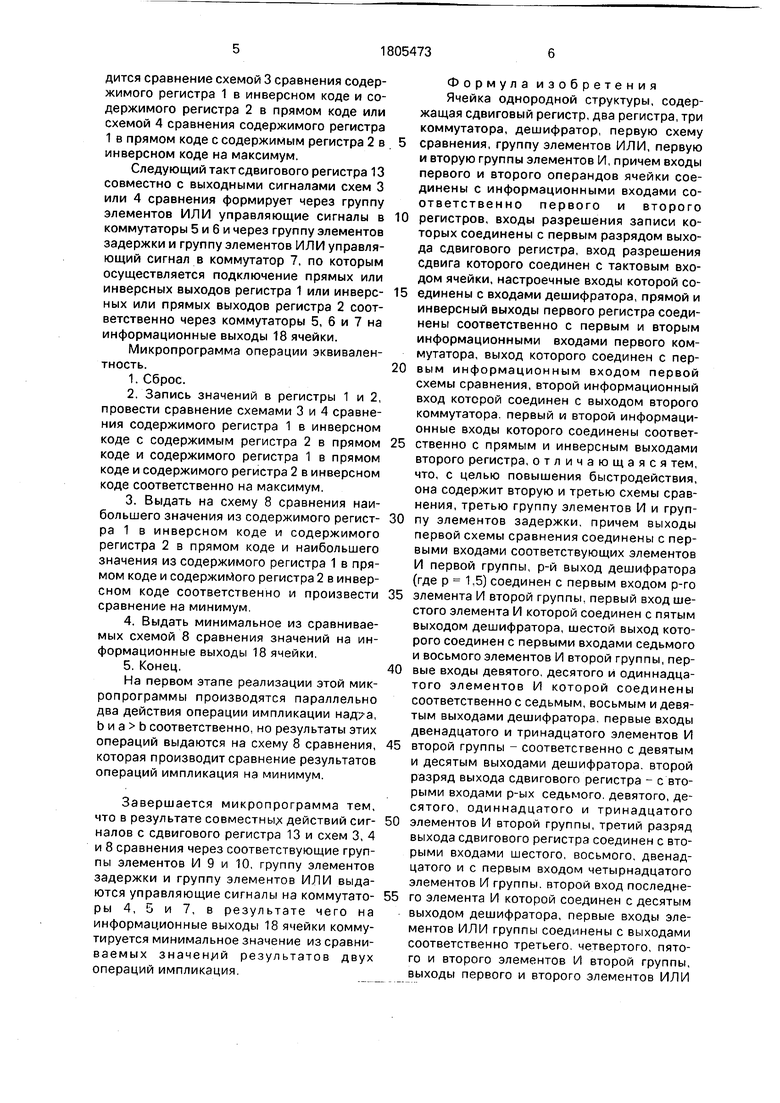

На фиг. 1 показана функциональная схема ячейки однородной структуры; на фиг.2 - часть однородной структуры, состоящая из ячеек.

Ячейка содержит (фиг. 1) регистр 1, регистр 2, схему 3 сравнения,схему 4 сравнения, коммутатор 5, коммутатор 6, коммутатор 7, схему 8 сравнения, группу элементов И 9, группу элементов И 10, дешифратор 11, группу элементов И 12, сдвиговый регистр 13, группу элементов 14 задержки, группу элементов ИЛИ 15, настроечные входы 16, информационные входы 17, информационные выходы 18, тактовый вход 19.

Выходы прямого кода регистра 1 соединены с первыми группами информационных входов схемы 4 сравнения и коммутатора 5,

выходы инверсного кода регистра 1 соединены с первой группой информационных входов схемы 3 сравнения и с второй группой информационных входов коммутатора 5 соответственно. Выходы прямого кода регистра 2 соединены с второй группой информационных входов схемы 3 сравнения и с первой группой информационных входов коммутатора 6, выходы инверсного кода регистра 2 соединены с вторыми группами входов схемы 4 сравнения и коммутатора 6 соответственно. Выходы коммутатора 5 соединены с первыми группами информационных входов коммутатора 7 и схемы 8 сравнения соответственно, выходы коммутатора 6 соединены с вторыми группами информационных входов коммутатора 7 и схемы 8 сравнения соответственно. Выходы схем 3 и 4 сравнения соединены с первыми входами соответствующих элементов И группы элементов И 9. выходы схемы 8 сравнения соедины с первыми входами соответ- свющих элементов И группы элементов И 9. Выходы дешифратора соединены с первы(Л

С

со

о ел

.N VI

GJ

ми входами соответствующих элементов И группы элементов И 12, вторые входы которых соединены с соответствующими выходами регистров 13, первый выход которого соединен с управляющими входами регистров 1 и 2. Выходы элементов И группы элементов И 12 соединены с вторыми входами соответствующих элементов И групп элементов И 9 и 10, с входами соответствующих элементов ИЛИ группы элементов ИЛИ и с входами, соответствующих элементов задержки группы элементов задержки. Выходы элементов И групп элементов И 9 и 10 соединены с входами соответствующих элементов ИЛИ группы элементов ИЛИ и с соответствующими элементами задержки группы элементов задержки. Выходы элементов задержки группы элементов задержки со- единены с входами соответствующих элементов ИЛИ группы элементов ИЛИ, выходы соответствующих элементов ИЛИ которой соединены с управляющими входами коммутаторов 5, б и 7 и схемы 8 сравнения соответственно. Кроме того, входы дешифратора соединены с настроечными входами 16 ячейки, а выход разрешения сдвига сдвигового регистра 13 соединен с тактовым входом ячейки, Информационные входы регистров 1 и 2 соединены с информационными входами 17 ячейки. Информационные выходы коммутаторов 7 соединены с информационными выходами 18 ячейки.

Ячейки однородной структуры работает следующим образом.

В начале работы необходимо установить в нулевое состояние все регистры и триггеры, что осуществляется с помощью единичного потенциала, который формирует дешифратор (фиг.1), по коду сброса, поступающего по настроечным входам 16 на вход дешифратора.

Настройка ячейки на выполнение конкретной операции производится по коду, поступающему по настроечным входам 16 на дешифратор. После чего в ячейке начинается процесс реализации микропрограмм.

На первом такте сдвигового регистра 13 осуществляется запись значений нечетких высказываний а и b в регистры 1 и 2 соответственно под действием совместных выходных сигналов сдвигового регистра 13 и дешифратора через группу элементов И 12. Значения нечетких высказываний поступают по информационным входам 17 ячейки. Кроме того, параллельно осуществляется сравнение значений a. b и а b соответственно схемами 3 и 4 сравнения, результаты сравнения которых используются при выполнении микропрограмм импликации и эквивалентности.

Микропрограммы операции чтения и

инверсии наиболее простые и завершаются

выдачей на информационные выходы 18 в

прямом и инверсном коде соответственно

содержимого регистров 1 или 2.

Микропрограммы операций конъюнкции, дизъюнкции и ассоциативного поиска очень близки между собой и выполняются за одинаковое количество микротактов. 0Микропрограмма операции дизъюнкции ( конъюнкции или ассоциативного поиска).

1. Сброс.

2. Запись значений в регистры 1 и 2, 5 з. Выдать на схему 8 сравнения содержимое регистров 1 и 2 и произвести сравнение содержимого регистров 1 и 2 на максимум (минимум или равенство).

4. Выдать на информационные выходы 0 18 ячейки наибольшее (наименьшее) из сравниваемых значений, при равенстве значений выдать одно из сравниваемых значений.

5. Конец.

5при реализации этих микропрограмм на втором такте сдвигового регистра 13, с помощью коммутаторов 5 и 6, осуществляется выдача на схему 8 сравнения содержимого регистров 1 и 2 в прямом коде и

0 производится сравнение схемой 8 сравнения на максимум (минимум или равенство) соответственно.

Следующий такт сдвигового регистра 13 совместно с выходными сигналами схемы 8

5 сравнения формирует через группу элементов ИЛИ управляющие сигналы в коммутаторы 5 и 6 и через группу элементов задержки и группу элементов ИЛИ управляющий сигнал в коммутатор 7, по которым

0 осуществляется подключение выходов регистров 1 или 2 через коммутаторы 5, 6 и 7 к информационным выходам 18 ячейки.

Микропрограмма операции импликация.

51. Сброс.

2. Запись значений в регистр 1 и 2, провести сравнение схемой 3 сравнения содержимого регистра 1 в инверсном коде с содержимым регистра 2 в прямом коде или 0 схемой 4 сравнения содержимого регистра 1 в прямом коде с содержимым регистра 2 в инверсном коде на максимум.

3. Выдать максимальное из сравниваемых значений на информационные выходы 5 18 ячейки.

4. Конец.

При реализации микропрограммы импликации на первом такте сдвигового регистра 13 производится запись значений а и b в регистры 1 и 2 соответственно и производится сравнение схемой 3 сравнения содержимого регистра 1 в инверсном коде и содержимого регистра 2 в прямом коде или схемой 4 сравнения содержимого регистра 1 в прямом коде с содержимым регистра 2 в инверсном коде на максимум.

Следующий такт сдвигового регистра 13 совместно с выходными сигналами схем 3 или 4 сравнения формирует через группу элементов ИЛИ управляющие сигналы в коммутаторы 5 и 6 и через группу элементов задержки и группу элементов ИЛИ управляющий сигнал в коммутатор 7, по которым осуществляется подключение прямых или инверсных выходов регистра 1 или инверсных или прямых выходов регистра 2 соответственно через коммутаторы 5, 6 и 7 на информационные выходы 18 ячейки.

Микропрограмма операции эквивалентность.

1. Сброс.

2. Запись значений в регистры 1 и 2, провести сравнение схемами 3 и 4 сравнения содержимого регистра 1 в инверсном коде с содержимым регистра 2 в прямом коде и содержимого регистра 1 в прямом коде и содержимого регистра 2 в инверсном коде соответственно на максимум.

3. Выдать на схему 8 сравнения наибольшего значения из содержимого регистра 1 в инверсном коде и содержимого регистра 2 в прямом коде и наибольшего значения из содержимого регистра 1 в прямом коде и содержимого регистра 2 в инверсном коде соответственно и произвести сравнение на минимум.

4. Выдать минимальное из сравниваемых схемой 8 сравнения значений на информационные выходы 18 ячейки.

5. Конец.

На первом этапе реализации этой микропрограммы производятся параллельно два действия операции импликации , b и а b соответственно, но результаты этих операций выдаются на схему 8 сравнения, которая производит сравнение результатов операций импликация на минимум.

Завершается микропрограмма тем, что в результате совместны/ действий сигналов с сдвигового регистра 13 и схем 3, 4 и 8 сравнения через соответствующие группы элементов И 9 и 10, группу элементов задержки и группу элементов ИЛИ выдаются управляющие сигналы на коммутаторы 4, 5 и 7, в результате чего на информационные выходы 18 ячейки коммутируется минимальное значение из сравниваемых значений результатов двух операций импликация.

Формула изобретения Ячейка однородной структуры, содержащая сдвиговый регистр, два регистра, три коммутатора, дешифратор, первую схему

сравнения, группу элементов ИЛИ, первую и вторую группы элементов И, причем входы первого и второго операндов ячейки соединены с информационными входами соответственно первого и второго

0 регистров, входы разрешения записи которых соединены с первым разрядом выхода сдвигового регистра, вход разрешения сдвига которого соединен с тактовым входом ячейки, настроечные входы которой со5 единены с входами дешифратора, прямой и инверсный выходы первого регистра соединены соответственно с первым и вторым информационными входами первого коммутатора, выход которого соединен с пер0 вым информационным входом первой схемы сравнения, второй информационный вход которой соединен с выходом второго коммутатора, первый и второй информационные входы которого соединены соответ5 ственно с прямым и инверсным выходами второго регистра, отличающаяся тем, что, с целью повышения быстродействия, она содержит вторую и третью схемы сравнения, третью группу элементов И и груп0 пу элементов задержки, причем выходы первой схемы сравнения соединены с первыми входами соответствующих элементов И первой группы, р-й выход дешифратора (где р 1,5) соединен с первым входом р-го

5 элемента И второй группы, первый вход шестого элемента И которой соединен с пятым выходом дешифратора, шестой выход которого соединен с первыми входами седьмого и восьмого элементов И второй группы, пер0 вые входы девятого, десятого и одиннадцатого элементов И которой соединены соответственно с седьмым, восьмым и девятым выходами дешифратора, первые входы двенадцатого и тринадцатого элементов И

5 второй группы - соответственно с девятым и десятым выходами дешифратора, второй разряд выхода сдвигового регистра - с вторыми входами р-ых седьмого, девятого, десятого, одиннадцатого и тринадцатого

0 элементов И второй группы, третий разряд выхода сдвигового регистра соединен с вторыми входами шестого, восьмого, двенадцатого и с первым входом четырнадцатого элементов И группы, второй вход последне5 го элемента И которой соединен с десятым выходом дешифратора, первые входы элементов ИЛИ группы соединены с выходами соответственно третьего, четвертого, пятого и второго элементов И второй группы, выходы первого и второго элементов ИЛИ

группы - с управляющими входами соответственно первого и второго коммутаторов, вход разрешения записи первой схемы сравнения и управляющий вход третьего коммутатора - с выходами соответственно третьего и четвертого элементов ИЛИ, вторые входы первого, второго и третьего элементов И первой группы соединены с выходами соответственно шестого, восьмого и двенадцатого элементов И второй груп- пы, выход четырнадцатого элемента которой соединен с вторыми входами четвертого и пятого элементов И первой группы, п -и выход второй схемы сравнения соединен с первым входом n-го элемента И (где п 1,4) третьей группы, второй вход которого соединен с выходом девятого элемента И второй группы, выход десятого элемента И кот орой соединен с первым входом (п+4)-го элемента И третьей группы, второй, вход которого соединен с n-м выходом третьей схемы сравнения, первый вход (п+8)-го элемента И третьей группы соединен с выходом одиннадцатого элемента И второй группы, вторые входы девятого и десятого элементов И третьей группы соединены соответственно с первым и вторым выходами второй схемы сравнения, первый и второй выходы третьей схемы сравнения - с вторыми входами одиннадцатого и двенадцатого элементов И третьей группы, первые входы тринадцатого и четырнадцатого элементов И третьей группы - с выходами двенадцатого элемента И второй группы, первый выход второй схемы сравнения - с вторым входом тринадцатого элемента И третьей группы, второй вход четырнадцатого элемента И которой соединен с вторым выходом третьей схемы сравнения, первый и второй входы которой соединены соответственно с прямым выходом первого регистра и инверсным выходом второго регистра, прямой выход последнего и инверсный выход первого регистра соединен соответственно с вторым и первым входами второй схемы сравнения, выходы первого и второго коммутаторов - соответственно с первым и вторым информационными входами третьего коммутатора, выход которого является выходом ячейки, с первого по шестой входы элементов задержки группы соединены соответственно с выходами элементов И с третьего по восьмой третьей группы, выход девятого элемента И которой соединен с входами седьмого и восьмого элементов задержки группы, вход девятого элемента задержки которой соединен с выходом одиннадцатого элемента И третьей группы, выход двенадцатого элемента И которой соединен с входами десятого и одиннадцатого элементов задержки группы, входы двенадцатого и тринадцатого элементов задержки которой соединены с выходами соответственно тринадцатого и

четырнадцатого элементов И третьей группы, выходы с первого по третий элементов И первой группы соединены с выходами соответственно четырнадцатого, пятнадцатого и шестнадцатого элементов задержки

группы, входы (16+п)-х элементов задержки группы соединены с выходами соответственно первого, четвертого, седьмого и тринадцатого элементов И второй группы, выходы первого, второго седьмого и двенадцатого элементов задержки группы соединены по схеме монтажное ИЛИ группы, выходы третьего, пятого, шестого, десятого, тринадцатого и семнадцатого элементов задержки группы соединены по схеме монтажное ИЛИ с вторым входом второго элемента ИЛИ группы, выходы восьмого, девятого, одиннадцатого, девятнадцатого и двадцатого элементов задержки группы соединены по схеме монтажное ИЛИ с вторым входом третьего элемента ИЛИ группы, выходы четвертого, четырнадцатого, пятнадцатого, шестнадцатого и восемнадцатого элементов задержки группы соединены по схеме монтажное ИЛИ с вторым входом

четвертого элемента ИЛИ группы, третьи входы первого и второго элементов ИЛИ которой соединены с выходами соответственно первого и четвертого элементов И первой группы, выход пятого элемента И которой соединен с третьими входами третьего и четвертого элементов ИЛИ группы, четвертые входы с первого по четвертый элементов ИЛИ которой соединены с выходами соответственно первого и шестого, десятого

и второго элементов И третьей группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной структуры | 1990 |

|

SU1789977A1 |

| Ячейка однородной структуры | 1980 |

|

SU941994A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1524061A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Устройство для сопряжения | 1977 |

|

SU739516A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в однородных вычислительных структурах для реализации нечетких алгоритмов. Целью изобретения является повышение быстродействия ячейки. Ячейка однородной структуры содержит сдвиговый регистр, два регистра, три коммутатора, три схемы сравнения, дешифратор, три группы элементов И, группу элементов ИЛИ и группу элементов задержки. Введение новых блоков и функциональных связей позволяет на базе этой ячейки создать быстродействующую однородную вычислительную структуру для реализации нечетких алгоритмов. 2 ил.

| Элемент ассоциативной матрицы | 1973 |

|

SU478297A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ячейка однородной структуры | 1980 |

|

SU941994A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-30—Публикация

1990-06-19—Подача