4 4: ||(аь Ч 4 О

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| Ячейка однородной структуры | 1980 |

|

SU941994A1 |

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1993 |

|

RU2040038C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЛОГИЧЕСКОЙ ИНФОРМАЦИИ | 1988 |

|

SU1826784A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805473A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Процессор для реализации операций над элементами расплывчатых множеств | 1985 |

|

SU1256010A1 |

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

Изобретение относится к цифровой вычислительной технике и может быть использована для создания однородной структуры, позволяющей выполнять операции записи, чтения и ассоциативного поиска информации, а также обработку составных нечетких высказываний. Целью изобретения является понышение быстродействия ячейки за счет выполнения любой операции над нечеткими высказываниями за один такт. Ячейка однородной структуры содержит три регистра 1, 2, 9, информационные 11, 12 и управляющие 13, 14 входы, информационный выход 7, две схемы 3, 4 сравнения, коммутатор 6, дешифратор 10, элемент И 8, шифратор 5 управления коммутатором. На информационные входы ячейки подаются коды степеней истинности обрабатываемых нечетких высказываний, на управляющие входы подается код выполняемой операции, а на выходе ячейки формируется прямой или инверсньй код степени истинности одного из нечетких высйазы- ваний, являющегося результатом выполняемой операции. 3 ил., 2 табл. § (Л

cpuz.t

Изобретение относится к цифровой вычислительной технике и может быть использовано в однородных вычислительных структурах для обработки распльт- чатых (нечетких) логических формул (составных нечетких высказываний),

Цель изобретения - повьшение быстродействия ячейки однородной структуры за счет выполнения любой операции над нечеткими высказываниями за один такт.

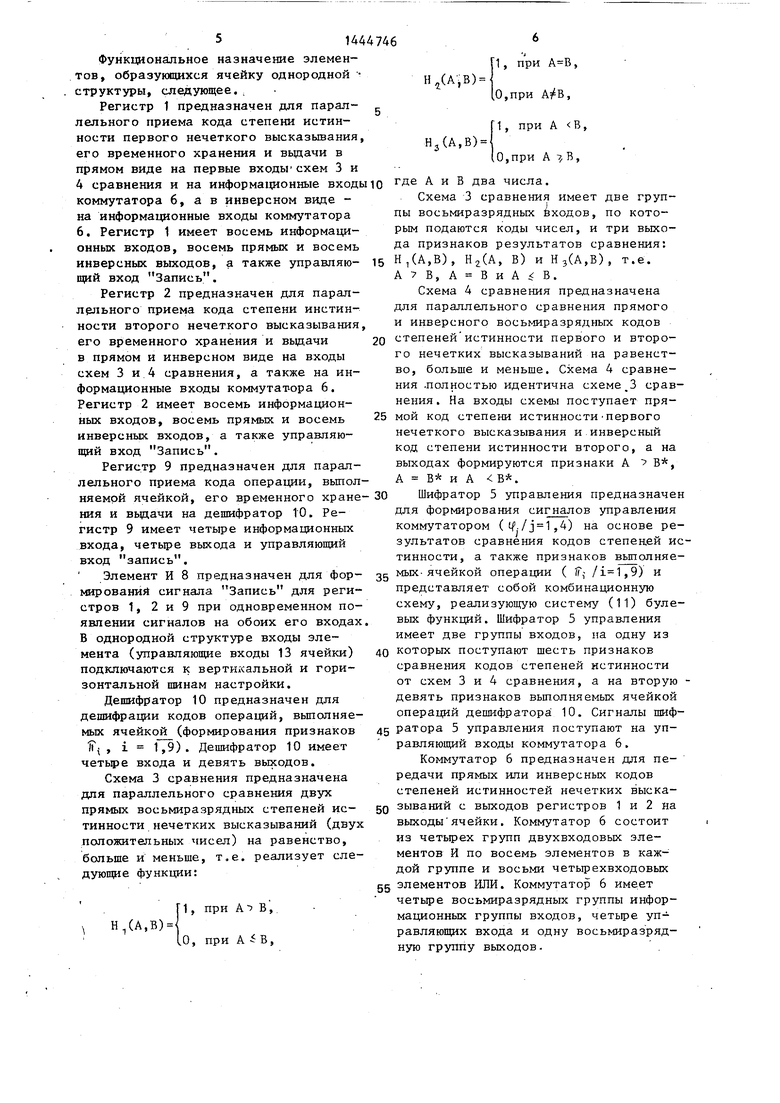

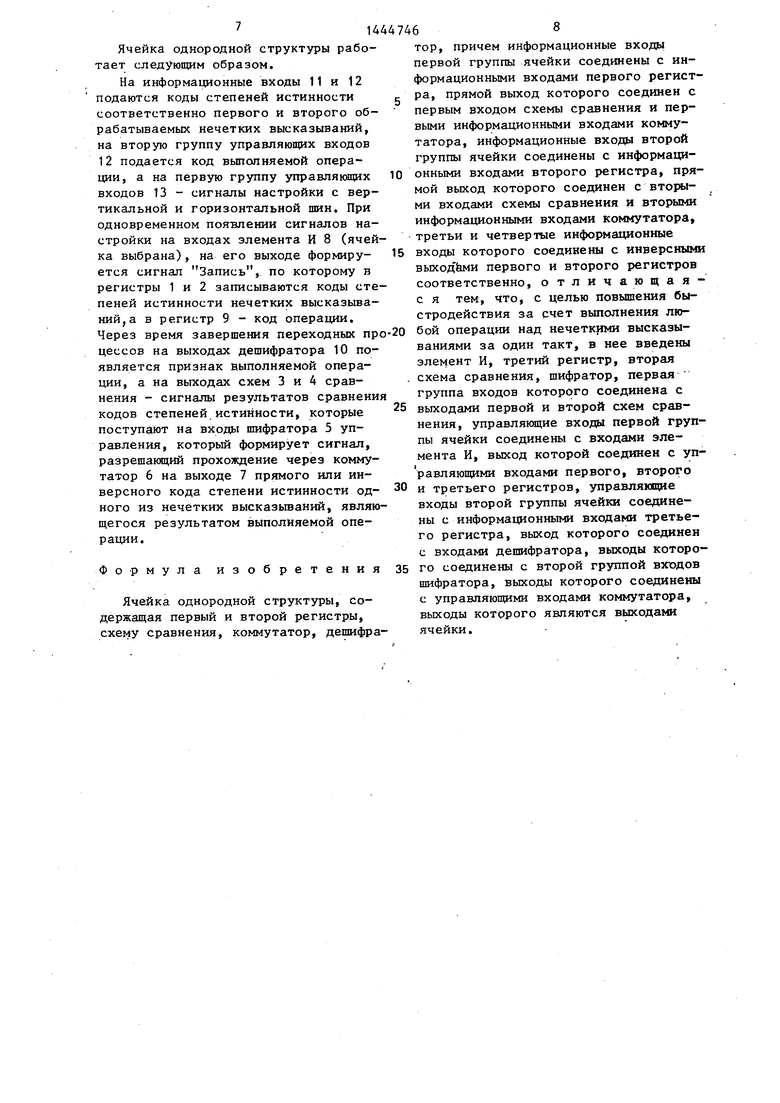

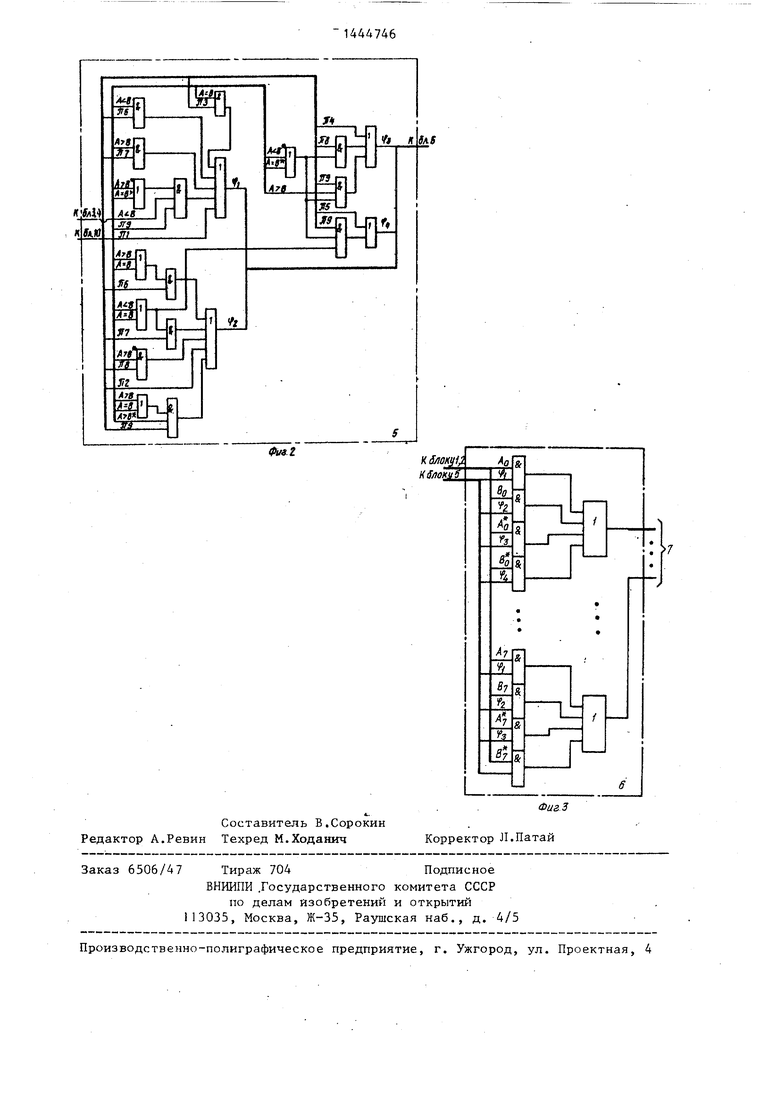

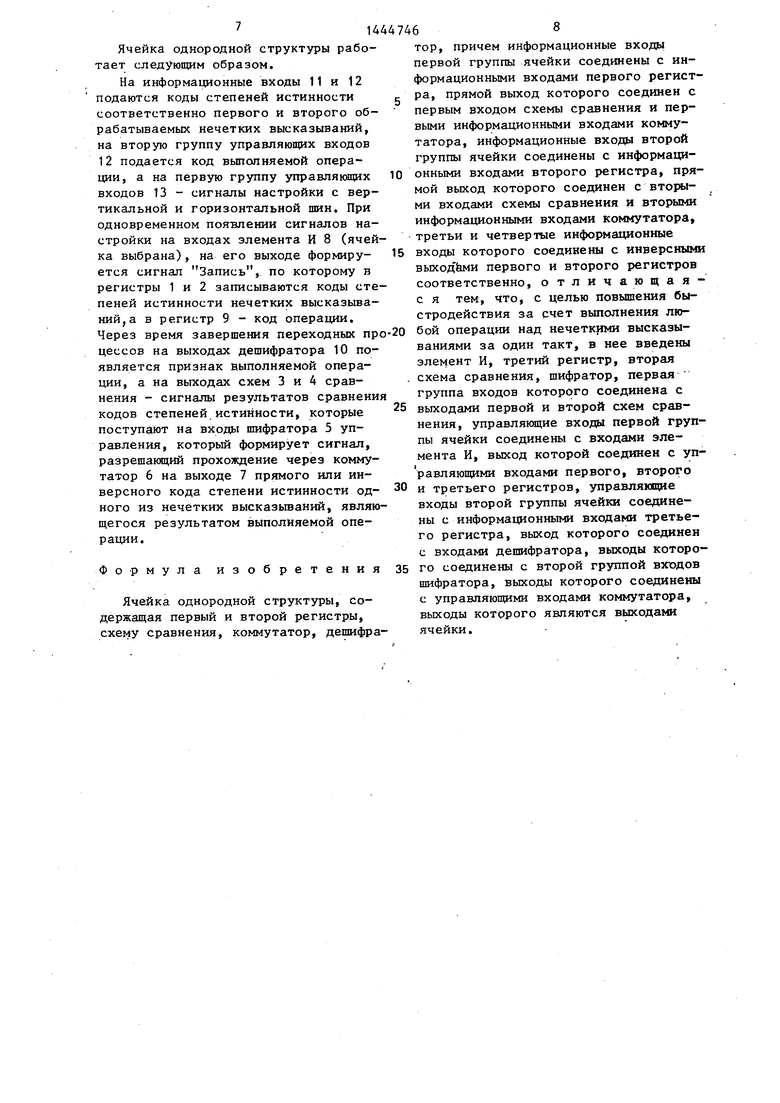

На фиг. 1 показана функциональная схема ячейки однородной структуры; на фиг. 2 - функциональная схема шифратора управленияi на фиг. 3 - функциональная схема коммутатора.

Каждая ячейка однородной структуры связана с соседними ячейками четьфьмя восьмизарядными информационными шинами, из которых две являются входными (информационные входы) и две выходными для данной ячейки. Выходные шины создаются из одной ответвлением сигналов Кроме того, имеются горизонтальные и вертикальные шины настройки (управляющие входы), которые соединены со всеми ячейками параллельно.

Ячейка однородной структуры содержит регистры 1 и 2, схемы 3 и 4 сравнения, шифратор 5 управления, коммутатор 6, выходы 7, элемент И 8, регистр 9, дешифратор 10, первую группу информационных входов 11, вторую группу информационных входов 12, первую группу управляющих входов 13 и вторую группу управляющих входов 14

Ячейка однородной структуры предназначена для обработки простых нечетких высказываний и может быть использована для создания однородной .структуры, позволяющей вьшолнять операции записи, чтения и ассоциативного поиска информации, а также ббработ- ку нечетких составных высказываний.

Нечетким высказыванием называют предложение, относительно- которого можно судить о степени его истинности. При этом степень истинности любого нечеткого высказывания принимает значения на интервале Г0,1.

Пусть а и b - нечеткие высказывания.

Наиболее распространенными логическими операциями, которые выполняются над нечеткими высказываниями являются следующие:

отрицание -а;

конъюкция а b;

дизъюнкция а V Б;

импликация а - Ь;

эквивалентность а b .

Множество этих операций образует- функционально полный избыточный базис, позволяющий получать с их помощью любые составные нечеткие высказывания из простых.

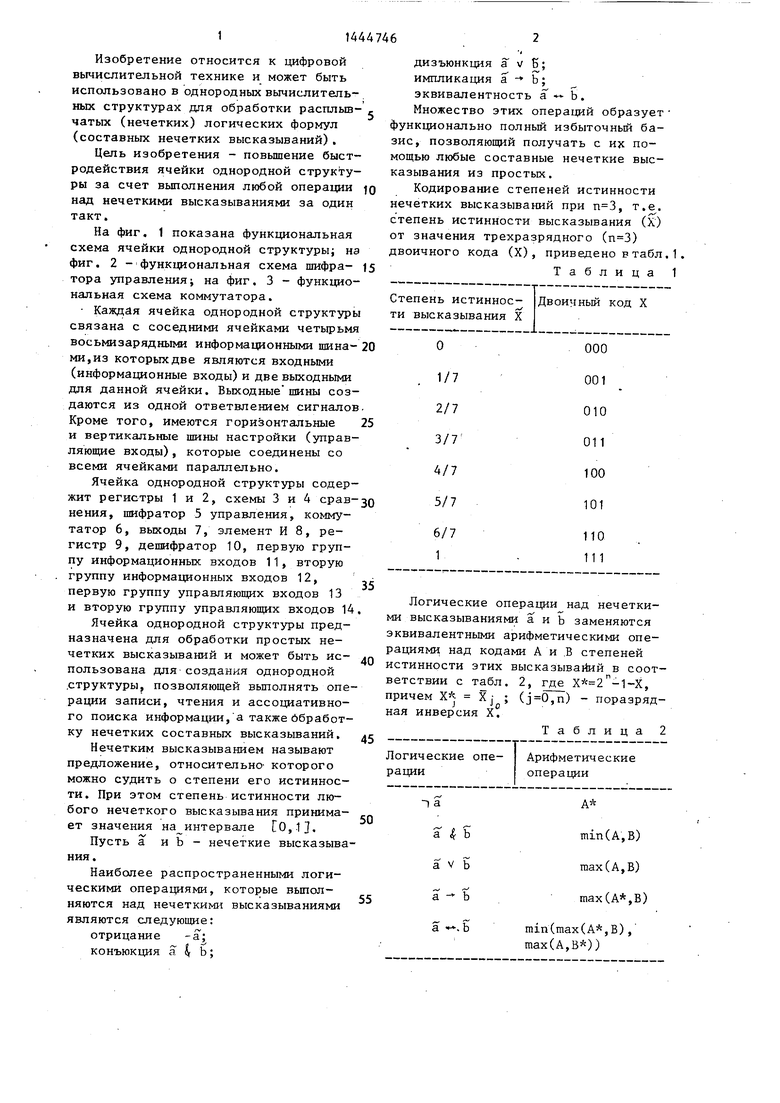

Кодирование степеней истинности нечетких высказываний при , т.е. степень истинности высказывания (X) от значения трехразрядного () двоичного кода (X), приведено в табл. 1

Таблица 1

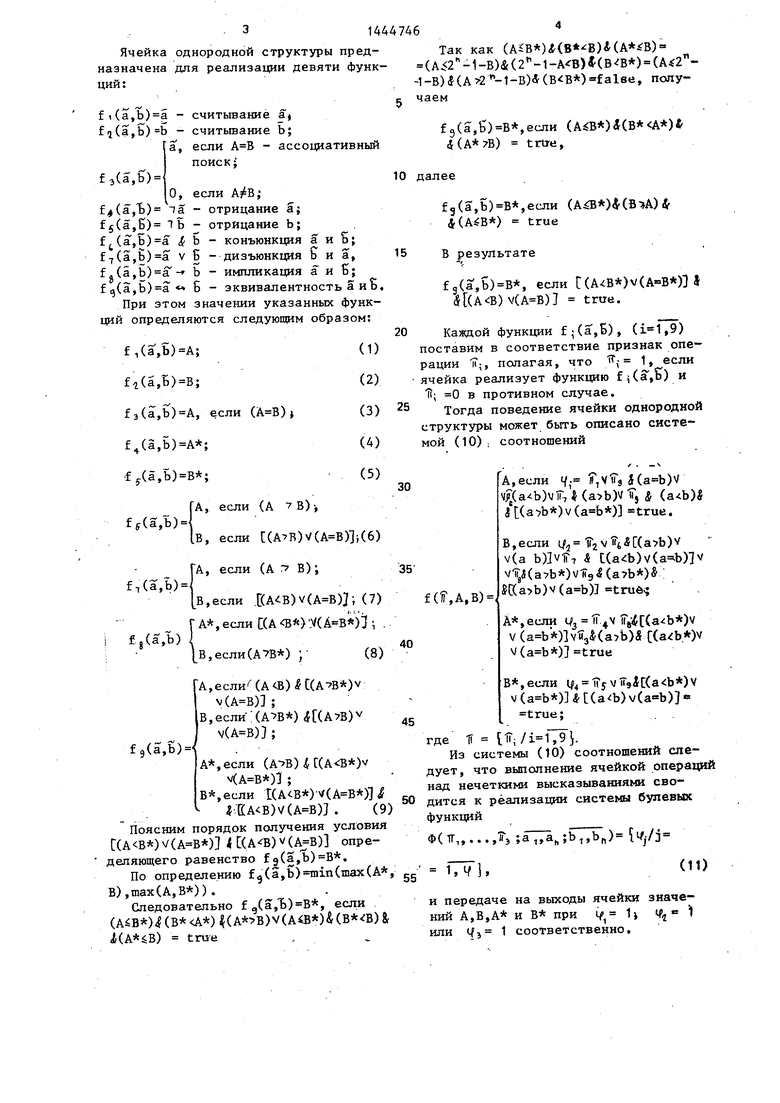

Логические операции над нечеткими высказываниями а н Ъ заменяются эквивалентньми арифметическими операциями над кодами А и .В степеней истинности этих высказывайий в соответствии с табл. 2, где , причем ХЛ Xj ; (,n) - поразрядная инверсия X.

45

Таблица 2

ai .bmin(max(A,B),

max(A,BA))

314АА746

Ячейка однородной структуры пред-Так как (AiB))A()

назначена для реализации девяти функ- (А 2 -1-В)(Ь(2 -1-А В)() ( Ций:-1-B)if(A 2 -1-B)4()falee, полу 5 чаем

fi(a,b)i - считьшаниё a j

f7{a,b)b - считьшаниё b;f 3(3,б)В,если ()(В А)4

а, если - ассоциативныйi() trtre,

поискi э(а,Ь)10 далее

О, если

(а,Ъ) та отрицание а; 5(3,6) тЬ - отрицание Ь; f(a,b)a f b - конъюнкция а и Б; f-,(ai,b)a V Б - дизъюнкция 6 и а, 15 fa(a,b)a - b - импликация а и 6; f е(а. fb) а 6 - эквивалентность а и S. При этом значении указанных функций определяются следующим образом:

20 Кавдой функции f-(а.Б), (,9)

(1)поставим в соответствие признак операции и, полагая, что ,- 1, если

(2)ячейка реализует функцию f ((а ,о) и

if; 0 в противном случае.

(3)2 Тогда поведение ячейки однородной

структуры может быть описано систе д(а:,Ь)В,если (А:)() 4() true

В результате

,

fg(a ,b)B, если t()v() 4() v() true.

f/a,b)A;

f7.(a,b)B;

з(а,Ь)А, если ()j

f(a,b)

fy(a,b)

fA, если (A 7 B)v

(4) (5)

мой (10); соотношений

/ ...н

30

f(r(a,b)

IB, если (A7B)V()li(6)

A,если t/. VITs J()V V() i ()V fj g, ()« Jt(a 7b)v() «true.

В,если i/j 2v i i5(a7b)v v(a b)lvir S t()v()lv irji(a7b)v-((9l (a7b) : )v() tru6

35

1A, если (A B); - В,если I(AiB)V()}i (7)

Г A, если К A Bft) .V( ):i; ..

В,если(А7В) ;(8)

А,если (A B) I C(A7B)v

v() ; В,если-;() f()v

v()};

f 9(S,b)

45

В,если l|i4 iT5V H9it()V v()()v()}« true;

где 11 t1ii/i lT9 i.

Из системы (10) соотношений следует, что выполнение ячейкой операц над нечеткими высказываниями сво- 50 дится к реализации системы булевых функций

А,если () i C()v

)1 ;

В,если 1() V()1 f )V()J . (9)

Поясним порядок получения условия

C()V() U()v()l опре- Ф( ТГ,,...,, ;а ,,а, ;b,bn)

деляющего равенство з(а,Ь)В.

По определению fg(a,b)min(inax(A, 1, Ч , В), max (А, В) ).

Следовательно f д(а,Ъ)В, если и передаче на выходы ячейки значе- (AiB)()JJ()V(AiB)&()& ний А,В,А и В при i/ U Ч, I i() true или tf3 1 соответственно.

(1

д(а:,Ь)В,если (А:)() 4() true

В результате

,

fg(a ,b)B, если t()v() 4() v() true.

мой (10); соотношений

/ ...н

30

35

40

f(,A,B),

45

A,если t/. VITs J()V V() i ()V fj g, ()« Jt(a 7b)v() «true.

В,если i/j 2v i i5(a7b)v v(a b)lvir S t()v()lv irji(a7b)v-((9l (a7b) : )v() tru6

А,если 1/3 |Г4У ji()v V ()1у(з&(а7Ь)« C()v v()true

В,если l|i4 iT5V H9it()V v()()v()}« true;

где 11 t1ii/i lT9 i.

Из системы (10) соотношений следует, что выполнение ячейкой операций над нечеткими высказываниями сво- 50 дится к реализации системы булевых функций

(11)

51444746

Функциональное назначение элементов, образующихся ячейку однородной структуры, следующее.,

Регистр 1 предназначен для парал- g лельного приема кода степени истинности первого нечеткого высказывания, его временного хранения и вьщачи в прямом виде на первые входы схем 3 и 4 сравнения и на информациюнные входыiо Д А и В два числа.

H(AjB)

НЛА,В) |

1, при А О,при А Г1, при 1о,при А

Схема 3 сравнения пы восьмиразрядных в рым подаются коды чи да признаков результ

коммутатора 6, а в инверсном виде - на информационные входы коммутатора 6. Регистр 1 имеет восемь информационных входов, восемь прямых и восемь инверсных выходов, а также управляющий вход Запись.

Регистр 2 предназначен для параллельного приема кода степени инстин- ности второго нечеткого высказывания его временного хранения и вьщачи в прямом и инверсном виде на входы схем 3 и 4 сравнения, а также на информационные входы коммутатора 6. Регистр 2 имеет восемь информахщон- ных входов, восемь прямых и восемь инверсных входов, а также управляющий вход Запись.

Регистр 9 предназначен для параллельного приема кода операции, выполняемой ячейкой, его временного хране ния и вьдачи на дешифратор 10. Регистр 9 имеет четыре информационных

входа, II

вход запись

четьфе выхода и управляющий II

Шифратор 5 управления предназнач для формирования сигналов управлени коммутатором (4./j 1,4) на основе р зультатов сравнения кодов степен,ей тинности, а также признаков выполня

Элемент И 8 предназначен для фор- 35 мых-ячейкой операции ( ff,- ,9) и

мированиЯ сигнала Запись для регистров 1, 2 и 9 при одновременном появлении сигналов на обоих его входах В однородной структуре входы элемента (управляющие входы 13 ячейки) подключаются к вертикальной и горизонтальной шинам настройки.

Дешифратор 10 предназначен для дешифрации кодов операций, вьшолняе- мых ячейко (формирования признаков 1Г , i 1,9). Дешифратор 10 имеет четь1ре входа и девять выходов.

Схема 3 сравнения предназначена дпя параллельного сравнения двух прямых восьмиразрядных степеней истинности нечетких высказываний (двух положительных чисел) на равенство, больше и меньше, т.е. реализует сле- дуюпще функции:

Н(А,В)

1, при В, ,0, при А В,

А и В два числа.

H(AjB)

НЛА,В) |

1, при , О,при , Г1, при А В, 1о,при А 7, В,

Схема 3 сравнения имеет две группы восьмиразрядных входов, по которым подаются коды чисел, и три выхода признаков результатов сравнения:

Н,(А,В), , В) и НЗ(А,В), т.е. А7В, .

Схема 4 сравнения предназначена для параллельного сравнения прямого и инверсного восьмиразрядных кодов

степеней истинности первого и второго нечетких высказываний на равенство, больше и меньше. Схема 4 сравнения .полностью идентична схеме,3 сравнения. На входы схемы поступает пря-

мой код степени истинностипервого нечеткого высказывания и инверсный код степени истинности второго, а на выходах формируются признаки А В, А В и А В.

Шифратор 5 управления предназначен для формирования сигналов управления коммутатором (4./j 1,4) на основе результатов сравнения кодов степен,ей истинности, а также признаков выполняе35 мых-ячейкой операции ( ff,- ,9) и

представляет собой комбинационную схему, реализующую систему (11) булевых функций. Шифратор 5 управления имеет две группы входов, па одну из

40 которых поступают шесть признаков сравнения кодов степеней истинности от схем 3 и 4 сравнения, а на вторую девять признаков выполняемых ячейкой операций дешифратора 10. Сигналы шиф45 ратора 5 управления поступают на управляющий входы коммутатора 6.

Коммутатор 6 предназначен для передачи прямых или инверсных кодов степеней истинностей нечетких высказываний с выходов регистров 1 и 2 на выходы ячейки. Коммутатор 6 состоит из четырех групп двухвходовых элементов И по восемь элементов в каждой группе и восьми четырехвходовьк

gg элементов ИЛИ. Коммутатор 6 имеет четыре восьмиразрядных группы информационных группы входов, четыре управляющих входа и одну восьмиразрядную группу выходов.

50

Ячейка однородной структуры работает следующим образом.

На информационные входы 11 и 12 подаются коды степеней истинности соответственно первого и второго обрабатываемых нечетких высказываний, на вторую группу управляющих входов 12 подается код вьшопняемой операции, а на первую группу управлякнцих

тор, причем информационные входы первой группы ячейки соединены с информационными входами первого регис ра, прямой выход которого соединен с первым входом схемы сравнения и первыми информационными входами коммутатора, информационные входы второй группы ячейки соединены с информационными входами второго регистра, пря мой выход которого соединен с ми входами схемы сравнения и вторыми информационными входами коммутатора третьи и четвертые информационные 15 входы которого соединены с инверсным выходами первого и второго регистров соответственно, отличающая с я тем, что, с целью повышения быстродействия за счет вьшолнения лювходов 13 - сигналы настройки с вертикальной и горизонтальной шин. При одновременном появлении сигналов настройки на входах элемента И 8 (ячейка выбрана), на его выходе формируется сигнал Запись, по которому в регистры 1 и 2 записываются коды степеней истинности нечетких высказываний, а в регистр 9 - код операции. Через время завершения переходных про-20 бой операции над нечеткими высказы- цессов на выходах дешифратора 10 по- ваниями за один такт, в нее введены является признак выполняемой опера- элемент И, третий регистр, вторая ции, а на выходах схем 3 и 4 сравнения - сигналы результатов сравнения кодов степеней истинности, которые поступают на входы шифратора 5 управления, который формирует сигнал, разрешающий прохождение через коммутатор 6 на выходе 7 прямого или инверсного кода степени истинности од- и третьего регистров, управляющие ного из нечетких высказьшаний, являю- входы второй группы ячейки соедине. схема сравнения, шифратор, первая

группа входов которого соединена с 25 выходами первой и второй схем сравнения, управляющие входы первой груп пы ячейки соединены с входами элемента И, выход которой соединен с уп равляющими входами первого, второго

щегося результатом выполняемой операции.

Формула изобретения

Ячейка однородной структуры, содержащая первый и второй регистры, схему сравнения, коммутатор, дешифра

тор, причем информационные входы первой группы ячейки соединены с информационными входами первого регистра, прямой выход которого соединен с первым входом схемы сравнения и первыми информационными входами коммутатора, информационные входы второй группы ячейки соединены с информационными входами второго регистра, прямой выход которого соединен с ми входами схемы сравнения и вторыми информационными входами коммутатора, третьи и четвертые информационные входы которого соединены с инверсными выходами первого и второго регистров соответственно, отличающая- с я тем, что, с целью повышения быстродействия за счет вьшолнения любой операции над нечеткими высказы- ваниями за один такт, в нее введены элемент И, третий регистр, вторая и третьего регистров, управляющие входы второй группы ячейки соединебой операции над нечеткими высказы- ваниями за один такт, в нее введены элемент И, третий регистр, вторая и третьего регистров, управляющие входы второй группы ячейки соединесхема сравнения, шифратор, первая

группа входов которого соединена с выходами первой и второй схем сравнения, управляющие входы первой группы ячейки соединены с входами элемента И, выход которой соединен с управляющими входами первого, второго

ны с информационными входами третьего регистра, выход которого соединен с входами дешифратора, выходы которо- го соединены с второй группой входов шифратора, выходы которого соединены с управляющими входами коммутатора, выходы которого являются выходами ячейки.

| Ячейка однородной среды | 1984 |

|

SU1218378A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ячейка однородной структуры | 1980 |

|

SU941994A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-09—Подача