Изобретение относится к области радиолокации, а именно к радиолокационным системам движущихся целей, и может также использоваться в гидролокации.

Цель предлагаемого технического решения - увеличение числа доплеровских каналов при фиксированном аппаратурном объеме поточного процессора БПФ.

Таким образом, существенными отли- чительными признаками заявляемого устройства являются блок коммутации информационных сигналов, блок перестановки отсчетов, коммутатор перезаписи и выходной коммутатор, управляемые соответствующими управляющими сигналами, формируемыми в блоке управления.

При этом цифровое устройство допле- ровской фдильтрэции перестраивается с режима выполнения поточным процессором БПФ NI МА( - точечного ДПФ на режим выполнения с помощью того же процессора

заданного N - М - точечного ДПФ (Я AI), что эквивалентно увеличению числа доплеровских каналов с NI до N.

Увеличение разрешающей способности по скорости происходит за счет сокращения размера стробируемого участия дальности.

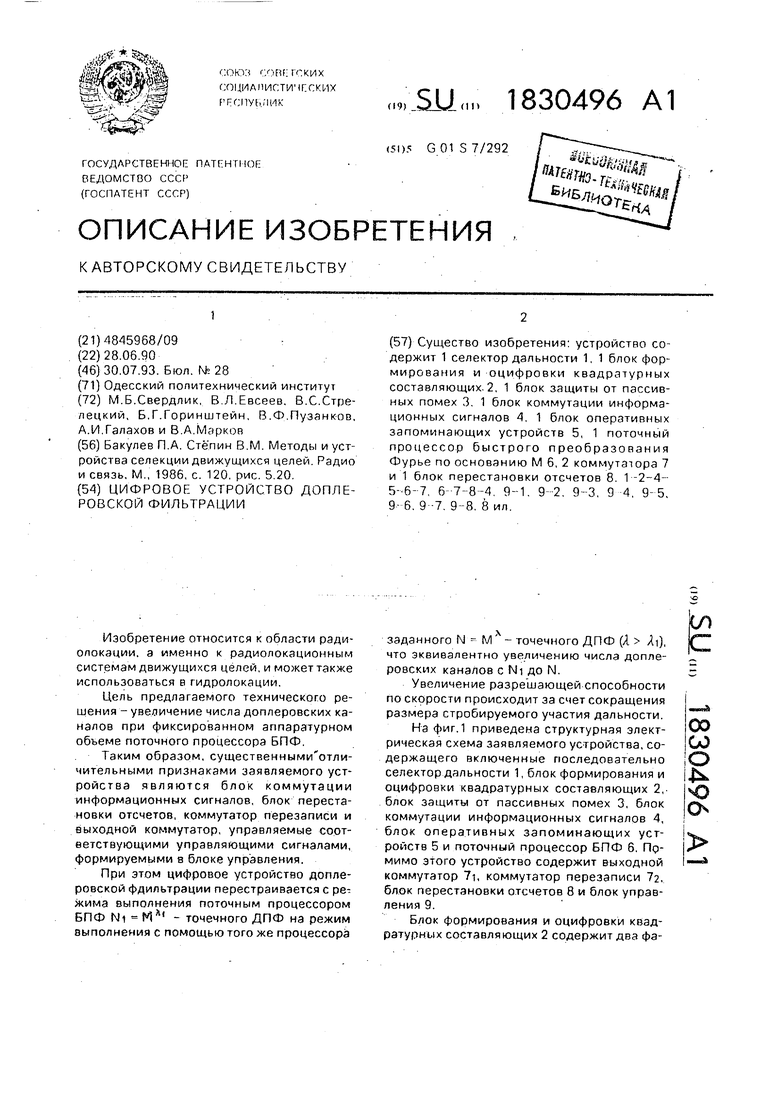

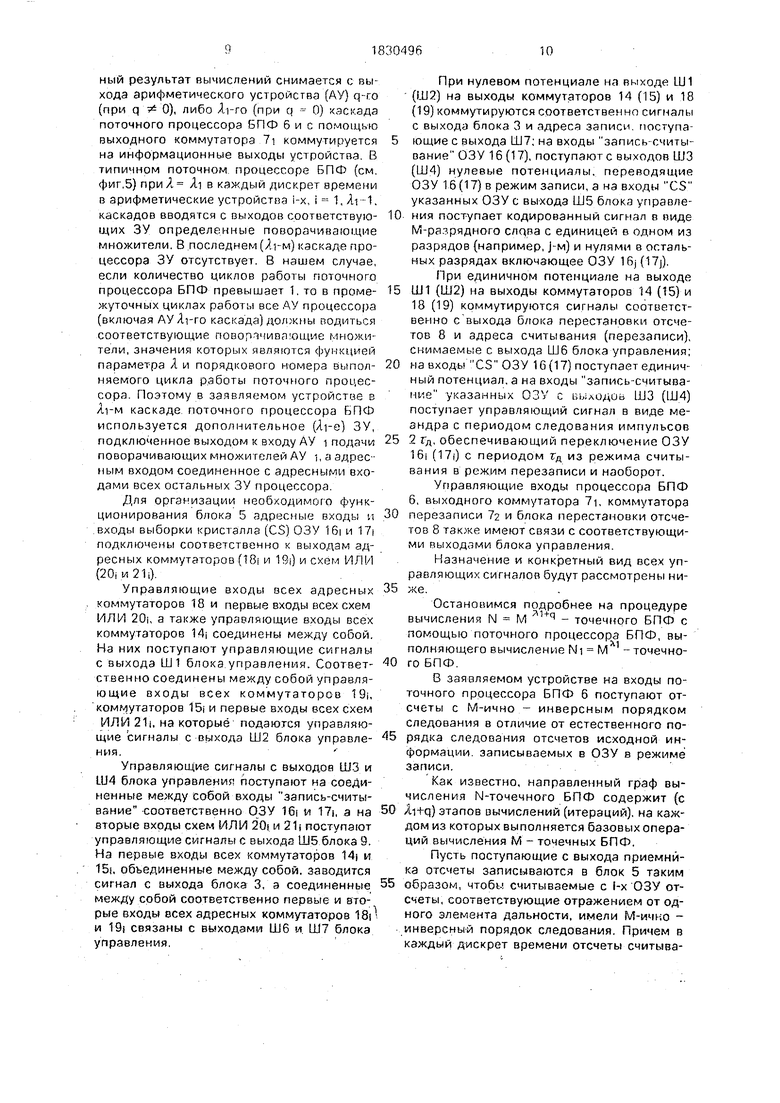

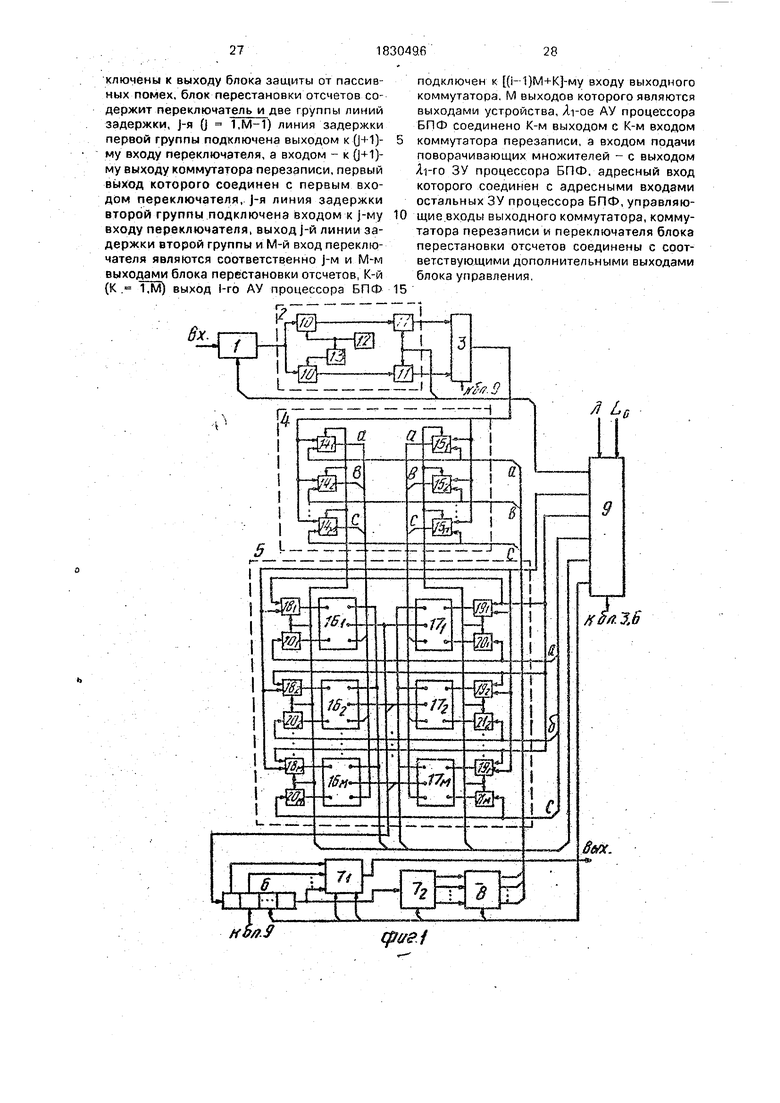

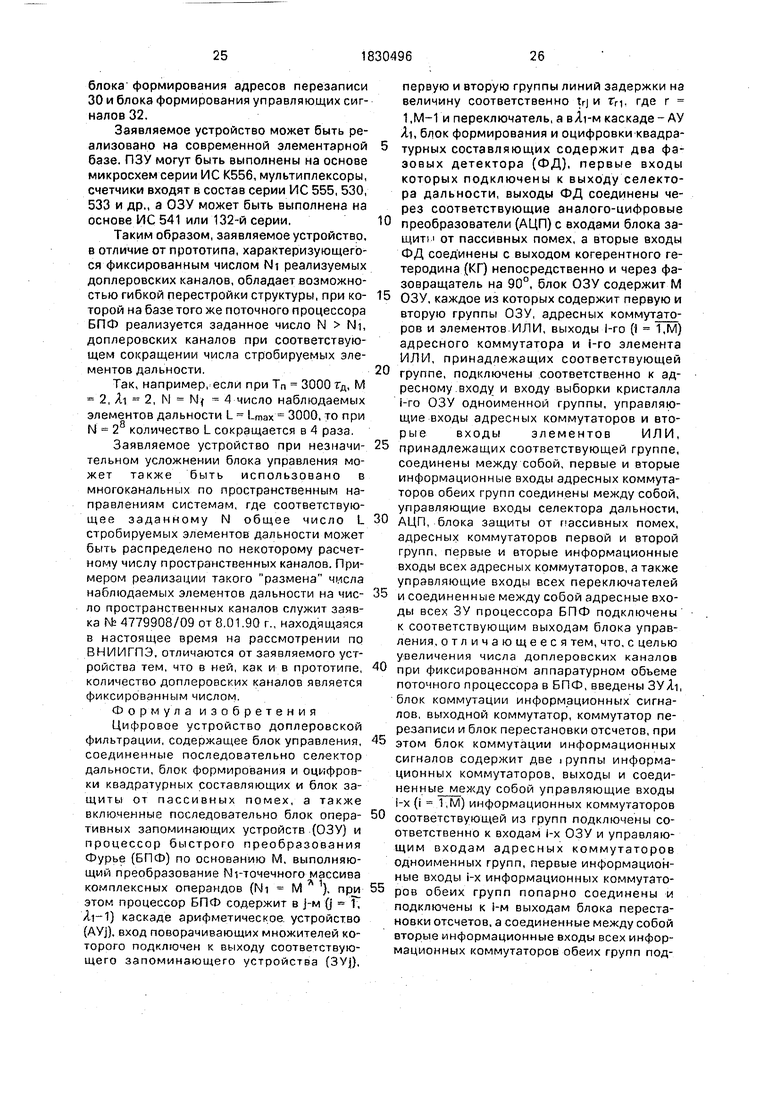

На фиг.1 приведена структурная электрическая схема заявляемого устройства, содержащего включенные последовательно селектор дальности 1, блок формирования и оцифровки квадратурных составляющих 2,- блок защиты от пассивных помех 3, блок коммутации информационных сигналов 4, блок оперативных запоминающих устройств 5 и поточный процессор БПФ 6. Помимо этого устройство содержит выходной коммутатор 7i, коммутатор перезаписи 7з, блок перестановки отсчетов 8 и блок управления 9.

Блок формирования и оцифровки квадратурных составляющих 2 содержит два фа(/ С

00

W

о ю о

зовых детектора 10, первые входы которых подключены к выходу селектора дальности 1, выходы через соответствующие АЦП 11 связаны со входами блока защиты от пассивных помех 3, а вторые входы соединены .соответственно с -выходами когерентного гетеродина (КГ) 12 и фазовращателя на 90° (13), подключенного входом к выходу КГ 12.

Блок коммутации информационных сигналов 4 содержит две группы информационных коммутаторов 14| и 15j, i 1 ,М, типа 2/1.

Блок ОЗУ 5 содержит две группы ОЗУ (16| и 17|), две группы адресных коммутаторов типа 2/1 (18i и 19i) и Д8е группы схем ИЛИ(20|и210.

Выходы адресного коммутатора 18i (19i) и схемы ИЛИ 20i (210 подключены соответственно к адресному входу и входу выборки кристалла (CS) ОЗУ 16i (170. Управляющие входы всех адресных коммутаторов 18j (190 и вторые входы всех схем .ИЛИ 20г(21|) соединены с управляющими входами информационных коммутаторов 14i (15j).:

Соединены между собой соответственно первые и вторые информационные входы всех адресных коммутаторов 18i.n 19i, а также входы запись-считывание ОЗУ 16s и ГЛ.

Выходы информационных коммутаторов 14| (150 подключены к входам ОЗУ 16i

(по.. :

Первые входы информационных коммутаторов 14; и 15i попарно соединены между собой и подключены к i-м выходам блока перестановки отсчетов 8, а вторые входы всех информационных коммутаторов 14| и 15i соединены между собой и подключены, к выходу блока защитькгг пассивных помех 3.

Выходы j-x, j - i, Ai, каскадов поточного процессора БПФ 6 подключены ко входам выходного коммутатора 7i, выходы которого являются выходами устройства, а входы Ai-ro каскада связаны со входами коммутатора перезаписи 7..

Управляющие входы.адресных коммутаторов 18, 19, входы запись-считывание ОЗУ 16, 17, первые входы схем ИЛИ 20 и 21, первые и вторые информационные входы всех адресных коммутаторов 18 и 19, управляющие входы селектора дальности 1 АЦП 11, коммутатора перезаписи 7а, два управляющих входа выходного коммутатора 7i и управляющий вход блока .перестановки отсчетов подключены соответственно к выходам Ш1-Ш13 блока управления, связанного также выходной шиной (обозначена стрелкой) соуправляющими входами блоков 3 и 6 (эта связь на фиг. 1 не показана).

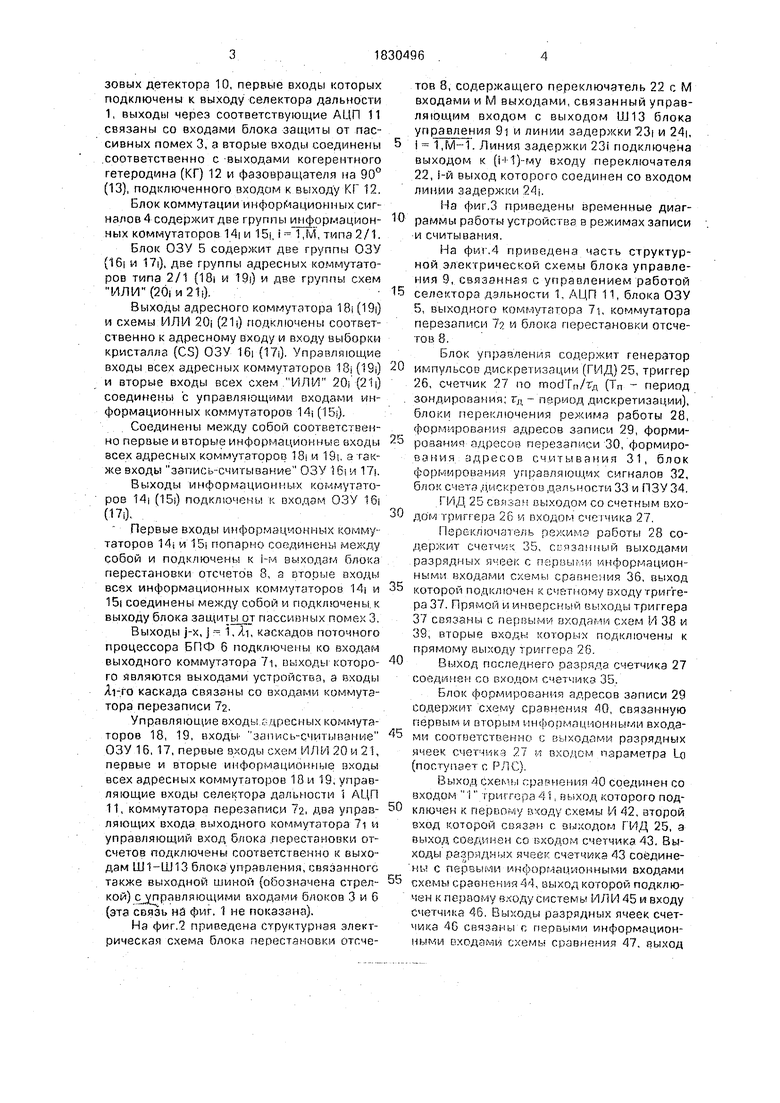

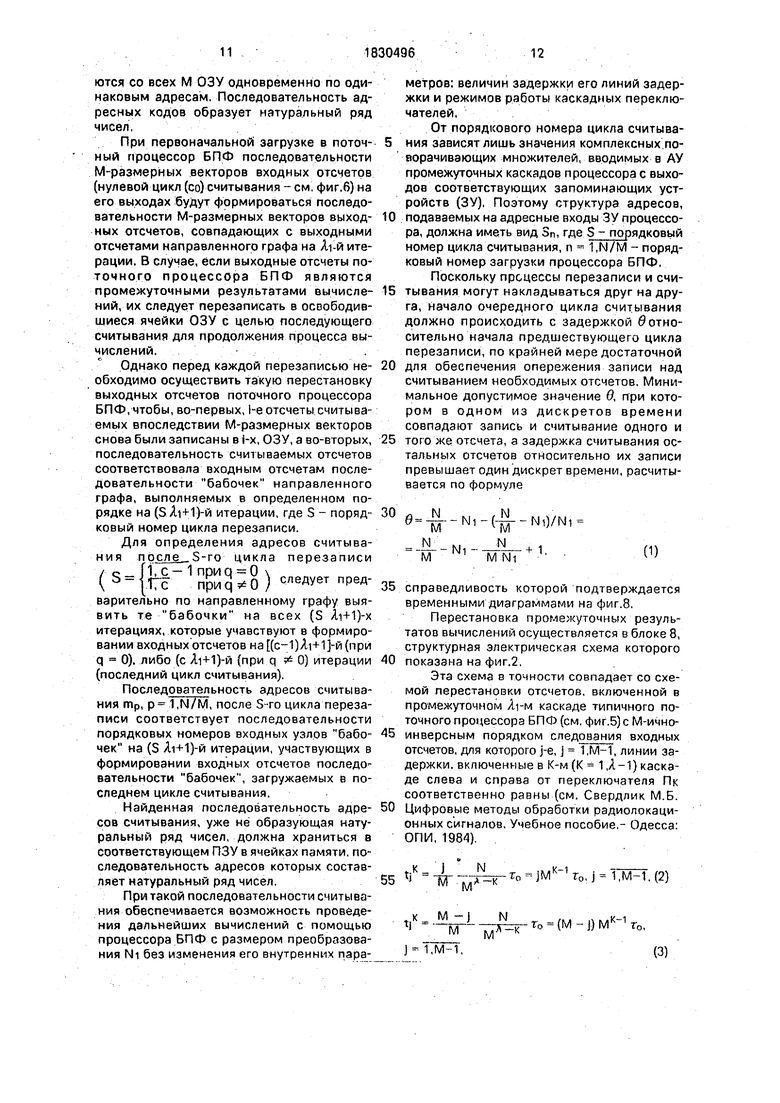

На фиг.2 приведена структурная электрическая схема блока перестановки отсчетов 8, содержащего переключатель 22 с М входами и М выходами, связанный управляющим входом с выходом LU13 блока управления 9i и линии задержки .3 и 24|,

i 1.M-1. Линия задержки 23i подключена выходом к (i-i-l)-My входу переключателя 22, i-й выход которого соединен со входом линии задержки 24|.

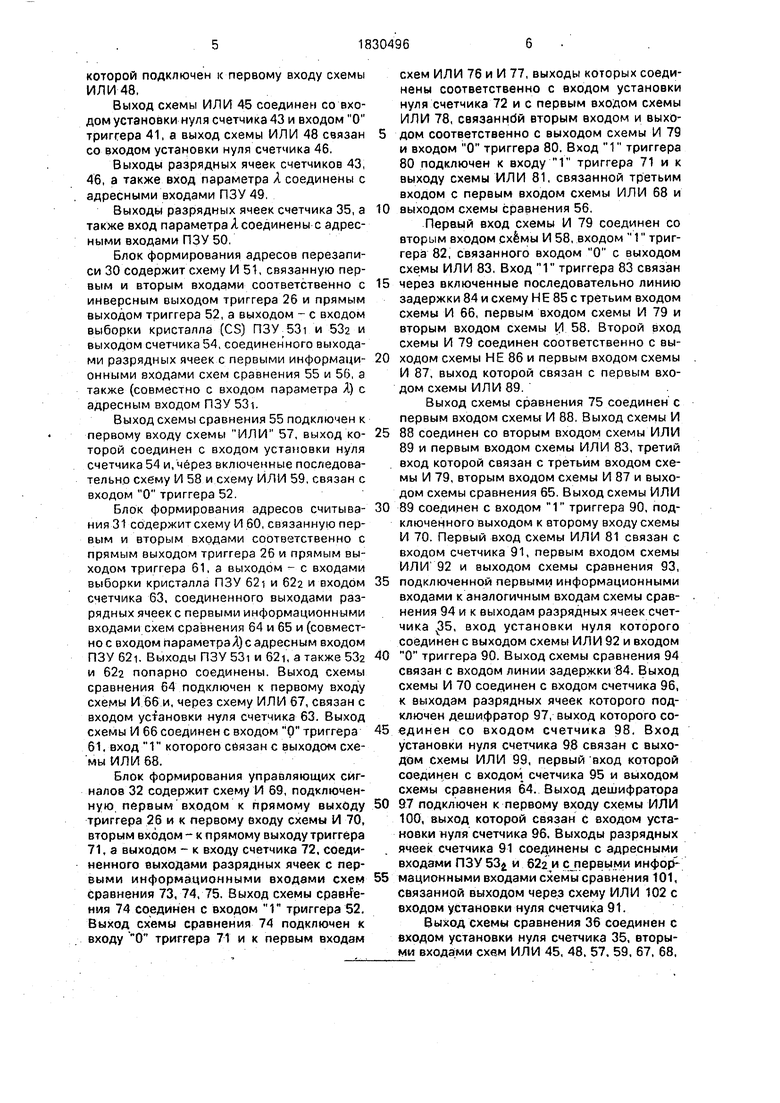

На фиг.З приведены временные диаграммы работы устройства в режимах записи -и считывания.

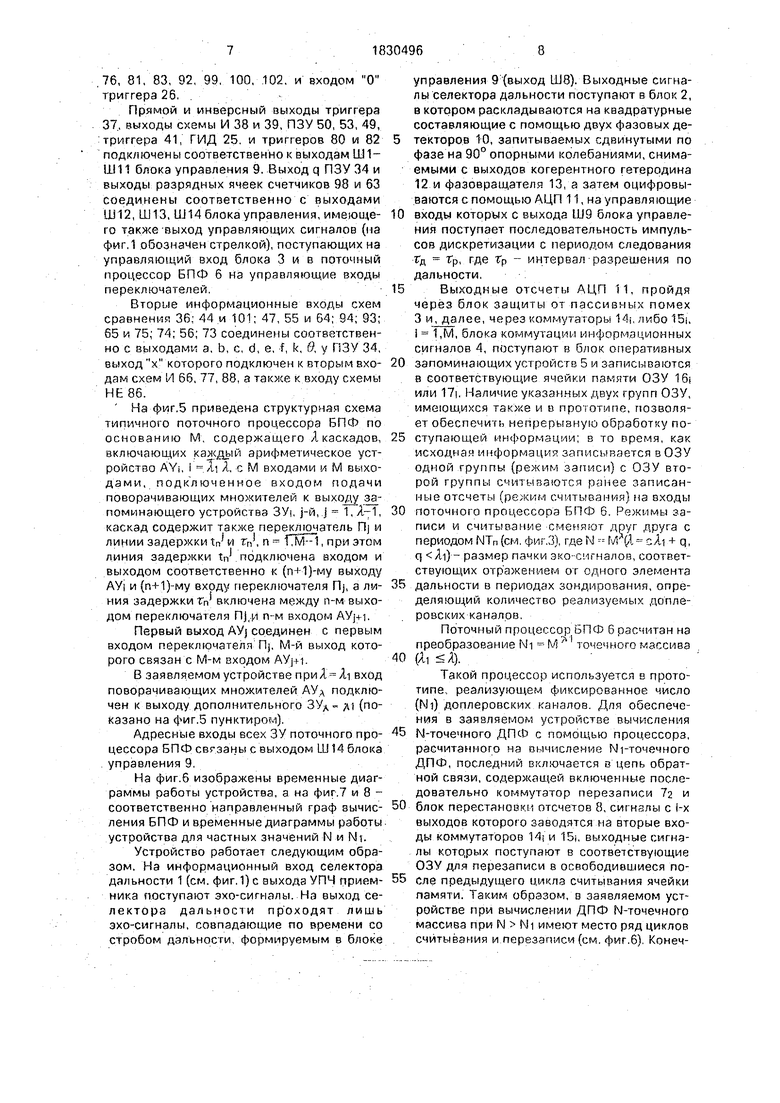

На фи.г.4 приведена часть структурной электрической схемы блока управления 9, связанная с управлением работой

5 селектора дальности 1, АЦП 11, блока ОЗУ 5, выходного коммутатора 7i, коммутатора перезаписи 7 и блока перестановки отсчетов 8.

Блок управления содержит генер-атор

0 импульсов дискретизации (ГИД) 25, триггер

26, счетчик 27 по modTn/Тд (Тп - период

. зондирования; Гд - период дискретизации),

блоки переключения режима работы 28,

Формирования адресов записи 29, форми5 роаания адресов перезаписи 30, формирования адресов считывания 31, блок формирования управляющих сигналов 32, блок счета дискретов дальности 33 и ПЗУ 34. ГИД 25 связан выходом со счетным вхо0 дОМ триггера 26 и входом счетчика 27.

Переключатель режима работы 28 содержит счетчик 35, связанный выходами разрядных ячеек с первыми информационными входами схемы сравнения 36, выход

5

которой подключен к счетному входу триггера 37. Прямой и инверсный выходы триггера 37 связаны с первыми входами схем И 38 и 39, вторые входы которых подключены к прямому выходу триггера 28.

0 Выход последнего разряда счетчика 27 соединен со входом счетчика 35.

Блок формирования адресов записи 29 содержит схему сравнения 40, связанную первым и вторым информационными входа5 ми соответственно с выходами разрядных ячеек счетчика 27 ь входом параметра LO (поступает с РЛС).

Выход схемы сравнения 40 соединен со входом 1 триггера 41, выход которого под0 ключей к первому входу схемы Л 42, второй вход которой связан с выходом ГИД 25, а выход соединен со входом счетчика 43. Выходы разрядных ячеек счетчика 43 соедине- ны с первыми информационными входами

5 схемы сравнения 44, выход которой подключен к первому входу системы ИЛ И 45 и входу счетчика 46. Выходы разрядных ячеек счетчика 46 связаны с первыми информационными входами схемы сравнения 47. аыход

которой подключен к первому входу схемы ИЛИ48,

Выход схемы ИЛИ 45 соединен со входом установки нуля счетчика 43 и входом О триггера 41, а выход схемы ИЛИ 48 связан со входом установки нуля счетчика 46.

Выходы разрядных ячеек счетчиков 43, 46, а также вход параметра А соединены с адресными входами ПЗУ 49.

Выходы разрядных ячеек счетчика 35, а также вход параметра А соединены с адресными входами ПЗУ 50.

Блок формирования адресов перезаписи 30 содержит схему И 51, связанную первым и вторым входами соответственно с инверсным выходом триггера 26 и прямым выходом триггера 52, а выходом - с входом выборки кристалла (CS) и 53а и выходом счетчика 54, соединенного выходами разрядных ячеек с первыми информационными входами схем сравнения 55 и 5f5, a также (совместно с входом параметра А) с адресным входом ПЗУ 531.

Выход схемы сравнения 55 подключен к первому входу схемы ИЛИ 57, выход которой соединен с входом установки нуля счетчика 54 и, через включенные последовательно схему И 58 и схему ИЛИ 59, связан с входом О триггера 52.

Блок формирования адресов считывания 31 содержит схему И 60, связанную первым и вторым входами соответственно с прямым выходом триггера 26 и прямым выходом триггера 61, а выходом - с входами выборки кристалла ПЗУ 621 и 62а и входом счетчика 63, соединенного выходами разрядных ячеек с первыми информационными входами схем сравнения 64 и 65 и (совместно с входом параметра А) с адресным входом ПЗУ 621. Выходы ПЗУ531 и 621, а также 532 и 622 попарно соединены. Выход схемы сравнения 64 подключен к первому входу схемы И 66 и, через схему ИЛИ 67, связан с входом установки нуля Счетчика 63. Выход схемы И 66 соединен с входом О триггера 61. вход 1 которого связан с выходом схемы ИЛИ 68.

Блок формирования управляющих сигналов 32 содержит схему И 69, подключенную первым входом к прямому выходу триггера 26 и к первому входу схемы И 70, вторым входом - к прямому выходу триггера 71, а выходом - к входу счетчика 72, соединенного выходами разрядных ячеек с первыми информационными входами схем сравнения 73, 74, 75, Выход схемы cpaeriV нмя 74 соединен с входом Г триггера 52, Выход схемы сравнения 74 подключен к входу О триггера 71 и к первым входам

схем ИЛИ 76 и И 77, выходы которых соединены соответственно с входом установки нуля счетчика 72 и с первым входом схемы ИЛИ 78, связанней вторым входом и выхо5 дом соответственно с выходом схемы И 79 и входом О триггера 80. Вход 1 триггера 80 подключен к входу 1 триггера 71 и к выходу схемы ИЛИ 81, связанной третьим входом с первым входом схемы ИЛИ 68 и

0 выходом схемы сравнения 56.

Первый вход схемы И 79 соединен со вторым входом схемы И 58, входом 1 триггера 82, связанного входом О с выходом схемы ИЛИ 83, Вход 1 триггера 83 связан

5 через включенные последовательно линию задержки 84 и схему НЕ 85 с третьим входом схемы И 66, первым входом схемы И 79 и вторым входом схемы И 58. Второй вход схемы И 79 соединен соответственно с вы0 ходом схемы НЕ 86 и первым входом схемы И 87, выход которой связан с первым входом схемы ИЛИ 89.

Выход схемы сравнения 75 соединен с первым входом схемы И 88. Выход схемы И

5 88 соединен со вторым входом схемы ИЛИ 89 и первым входом схемы ИЛИ 83, третий вход которой связан с третьим входом схемы И 79, вторым входом схемы И 87 и выходом схемы сравнения 65. Выход схемы ИЛИ

0 89 соединен с входом 1 триггера 90, подключенного выходом к второму входу схемы И 70. Первый вход схемы ИЛИ 81 связан с входом счетчика 91, первым входом схемы ИЛИ 92 и выходом схемы сравнения 93,

5 подключенной первыми информационными входами к аналогичным входам схемы сравнения 94 и к выходам разрядных ячеек счетчика V35, вход установки нуля которого соединен с выходом схемы ИЛИ 92 и входом

0 О триггера 90. Выход схемы сравнения 94 связан с входом линии задержки 84. Выход схемы И 70 соединен с входом счетчика 96, к выходам разрядных ячеек которого подключен дешифратор 97, выход которого со5 единен со входом счетчика 98. Вход установки нуля счетчика 9.8 связан с выходом схемы ИЛИ 99, первый вход которой соединен с входом счетчика 95 и выходом схемы сравнения 64. Выход дешифратора

0 9.7 подключен к первому входу схемы ИЛИ 100, выход которой связан с входом установки нуля счетчика 96. Выходы разрядных ячеек счетчика 91 соединены с адресными входами ПЗУ 53$ и 62а и с первыми инфор5 мационными входами схемы сравнения 101, связанной выходом через схему ИЛИ 102 с входом установки нуля счетчика 91.

Выход схемы сравнения 36 соединен с входом установки нуля счетчика 35, вторыми входами схем ИЛИ 45, 48. 57, 59, 67, 68,

6, 81, 83, 92, 99, 100, .102, и входом О риггера 26. . -:

Прямой и инверсный выходы триггера 7, выходы схемы И 38 и 39, ПЗУ 50, 53, 49, риггера 41, ГИД 25. и триггеров 80 и 82 подключены соответственно к выходам НИ- НИ 1 блока управления 9. Выход q ПЗУ 34 и выходы разрядных ячеек счетчиков 98 и 63 оединены соответственно с выходами П2, НИЗ, Ш14 блока управления, имеющего также выход управляющих сигналов (на фиг.1 обозначен стрелкой), поступающих на управляющий вход блока 3 и в поточный процессор БПФ б на управляющие входы переключателей.

Вторые информационные входы схем сравнения 36; 44 и 101; 47, 55 и 64; 94; 93; 65 и 75; 74; 56; 73 соединены соответственно с выходами а, Ь, с, d, e, -f, k, ft, у ПЗУ 34, выход х которого подключен к вторым входам схем И 66, 77, 88, а также к входу схемы НЕ 86.

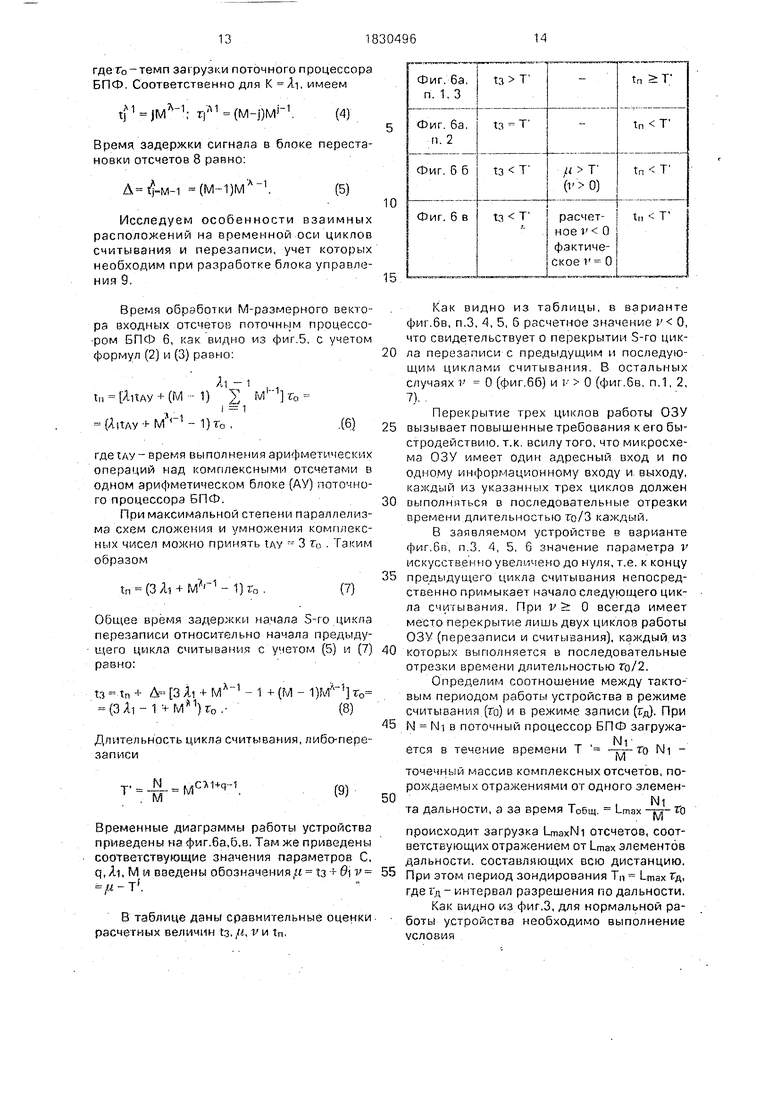

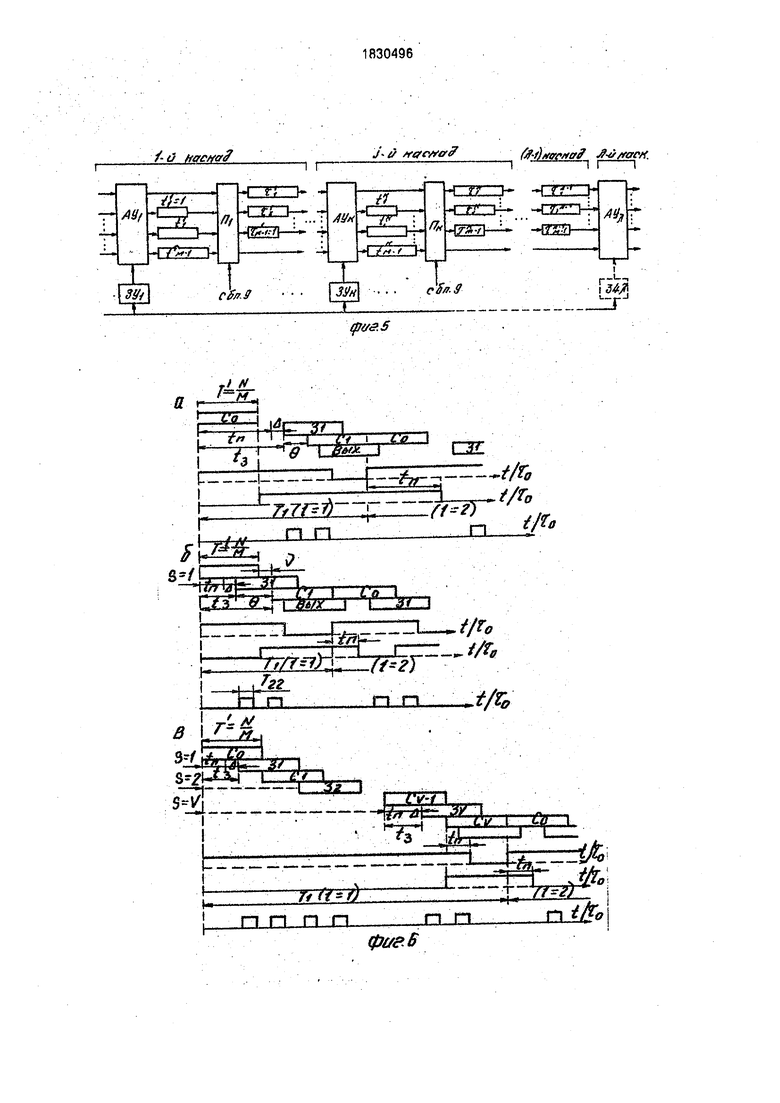

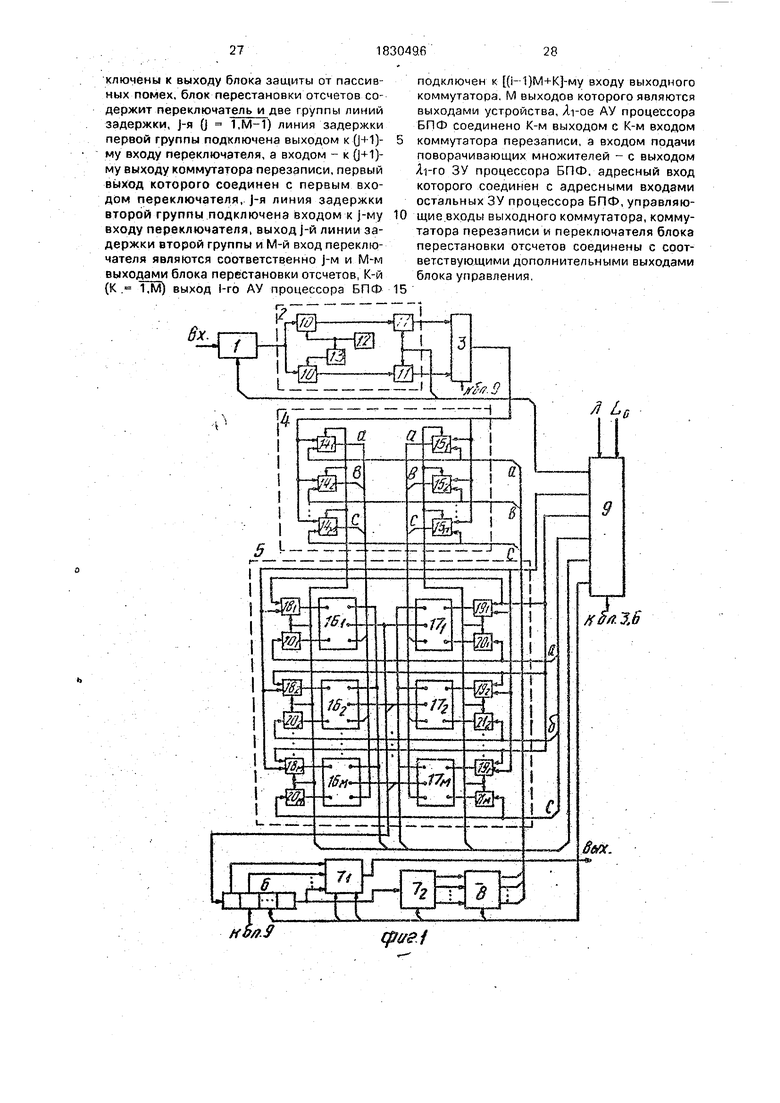

На фиг.5 приведена структурная схема типичного поточного процессора БПФ по основанию М, содержащего А каскадов, включающих каждый арифметическое устройство AYj, i Я, с М входами и М выходами, подключенное входом подачи поворачивающих множителей к выходу запоминающего устройства ЗУ|, j-й, j 1, А-1, каскад содержит также переключатель П и линии задержки tn и ТгА n O/F-1, при этом линия задержки tn подключена входом и выходом соответственно к (п+1)-му выходу АУ| и {п-Н)-му входу переключателя П, а линия задержки rj включена между n-м выходом переключателя Hj.-i/i n-м входом

Первый выход АУ соединен с первым входом переключателя П), М-й выход которого связан с М-м входом .

В заявляемом устройстве при А AI вход поворачивающих множителей АУд подключен к выходу дополнительного ЗУд- Д1 (показано на фиг.5 пунктиром).

Адресные входы всех ЗУ поточного процессора БПФ свгзаны с выходом Ш14 блока управления 9.

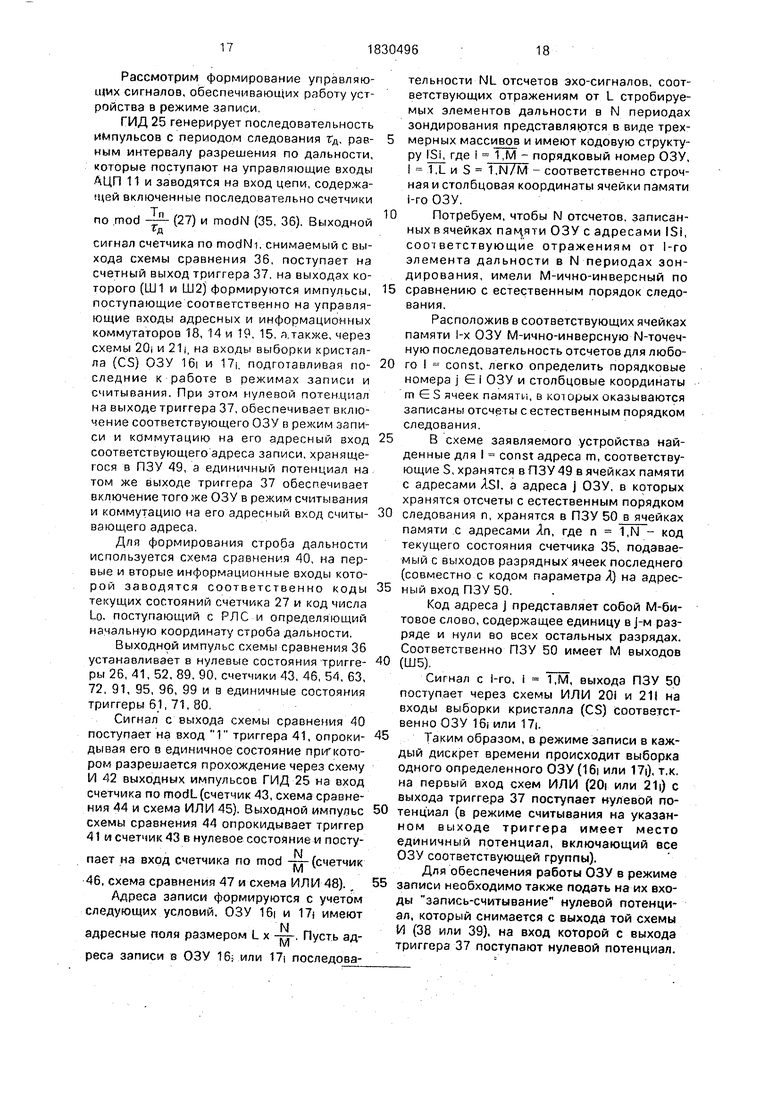

На фиг.б изображены временные диаграммы работы устройства, а на фиг.7 и 8 - соответственно направленный граф вычисления БПФ и временные диаграммы работы устройства для частных значений N и Nt.

Устройство работает следующим образом. На информационный вход селектора дальности 1 (см. фиг. 1) с выхода УПЧ приемника поступают эхо-сигналы. На выход селектора дальности проходят лишь эхо-сигналы, совпадающие по времени со стробом дальности, формируемым в блоке

управления 9 (выход Ш8). Выходные сигналы селектора дальности поступают в блок 2, в котором раскладываются на квадратурные составляющие с помощью двух фазовых дете кторо.в 10, засчитываемых сдвинутыми по фазе на 90° опорными колебаниями, снимаемыми с выходов когерентного гетеродина 12 и фазовращателя 13, а затем оцифровываются с помощью АЦП 11, на управляющие

входы которых с выхода Ш9 блока управления поступает последовательность импульсов дискретизации с периодом следования тд Тр, где Тр - интервал-разрешения по дальности,

Выходные отсчеты АЦП 11, пройдя через блок защиты от пассивных помех 3 и, далее, через коммутаторы 14j, либо 15|, I 1,M, блока коммутации информационных сигналов 4, поступают в блок оперативных

запоминающих устройств 5 и записываются в соответствующие ячейки памяти ОЗУ 16 или 17|. Наличие указанных двух групп ОЗУ, имеющихся также и в прототипе, позволяет обеспечить непрерывную обработку поступающей информации; в то время, как исходная информация записывается в ОЗУ одной группы (режим записи) с ОЗУ второй группы считываются ранее записанные отсчеты (режим считывания) на входы

поточного процессора БПФ 6. Режимы записи и считывание сменяют друг друга с периодом NTn (см. фиг.З), где N г М (Я cAi + q, q Ai)- размер пачки эко-сигналов, соответствующих отражением от одного элемента

дальности в периодах зондирования, определяющий количество реализуемых до плё- ровских каналов.

Поточный процессор БПФ 6 расчмтан на преобразование Ni - М А точечного массива

(Ai A).

Такой процессор используется в прототипе, реализующем фиксированное число (IMi) доплеровских. каналов. Для обеспечения в заявляемом устройстве вычисления

N-точечного ДПФ с помощью процессора, расчитанного на вычисление Ni-точечного ДПФ, последний включается в цепь обратной связи, содержащей включенные последовательно коммутатор перезаписи 1г и

блок перестановки отсчетов 8, сигналы с 1-х выходов которого заводятся на вторые входы коммутаторов 14i и 15i, выходные сигналы которых поступают в соответствующие ОЗУ для перезаписи в освободившиеся поеле предыдущего цикла считывания ячейки памяти. Таким образом, в заявляемом устройстве при вычислении ДПФ N-точечного массива при N имеют место ряд циклов считывания и.перезаписи (см. фиг.б). Конечный результат вычислений снимается с выхода арифметического устройства (АУ) q-ro (при ), либо Агго (при q 0) каскада поточного процессора БПФ бис помощью выходного коммутатора 1 коммутируется на информационные выходы устройства. В типичном поточном процессоре БПФ (см. фит,5) приА AI в каждый дискрет времени в арифметические устройства i-x, i 1, Ar-1, каскадов вводятся с выходов соответствую- щих ЗУ определенные поворачивающие множители. В последнем (Ai-м) каскаде процессора ЗУ отсутствует. В нашем случае, если количество циклов работы поточного процессора БПФ превышает 1. то в проме- жуточных циклах работы все АУ процессора (включая АУАгго каскада) должны водиться соответствующие поворачивающие множители, значения которых являются функцией параметра А и порядкового номера выпол- няемого цикла работы поточного процессора. Поэтому в заявляемом устройстве в Ai-м каскаде поточного процессора БПФ используется дополнительное (Ai-е) ЗУ, подключенное выходом к входу АУ 1 подачи поворачивающих множителей АУ 1, а адресным входом соединенное с адресными входами всех остальных ЗУ процессора.

Для организации необходимого функционирования блока 5 адресные входы и .входы выборки кристалла (CS) ОЗУ 16i и 17i подключены соответственно к выходам адресных коммутаторов (18i и 190 и схем ИЛИ (20in21i).

Управляющие входы всех адресных коммутаторов 18 и первые входы всех схем ИЛИ 20к а также управляющие входы всех коммутаторов 14j соединены между собой. На них поступают управляющие сигналы с выхода Ш1 блока управления. Соответ- ственно соединены между собой управляющие входы всех коммутаторов 19i, коммутаторов 15j и первые входы есех схем ИЛИ 21|, на которые подаются управляющие сигналы с выхода Ш2 блока упрэвле- ния.

Управляющие сигналы с выходов ШЗ и Ш4 блока управления поступают на соединенные между собой входы запись-считывание соответственно ОЗУ 16i и 17i, а на вторые входы схем ИЛИ 20i и 21j поступают управляющие сигналы с выхода Ш5 блока 9. На первые входы всех коммутаторов 14) и 15i, объединенные между собой, заводится сигнал с выхода блока 3, а соединенные между собой соответственно первые и вторые входы есех адресных коммутаторов 18р и 19i связаны с выходами Ш6 и. LU7 блока управления,

При нулевом потенциале на выходе Ш1 (Ш2) на выходы коммутаторов 14 (15) и 18 (19) коммутируются соответственно сигналы с выхода блока 3 и адреса записи, поступающие с выхода Ш7; на входы запись-считывание ОЗУ 16 (17), поступают с выходов ШЗ (Ш4) нулевые потенциалы, переводящие ОЗУ 16(17) в режим записи, а на входы CS указанных ОЗУ с вы-ходз Ш5 блока управления поступает кодированный сигнал в виде М-разрядного слова с единицей в одном из разрядов (например, j-м) и нулями в остальных разрядах включающее ОЗУ 16j (17j).

При единичном потенциале на выходе Ш1 (Ш2) на выходы коммутаторов 14 (15) и 18 (19) коммутируются сигналы соответственно с выхода блока перестановки отсчетов 8 и адреса считывания (перезаписи), снимаемые с выхода Ш6 блока управления; на входы CS ОЗУ 16(17) поступает единичный потенциал, а на входы запись-считывание указанных ОЗУ с выходов ШЗ (Ш4) поступает управляющий сигнал в виде меандра с периодом следования импульсов 2 гд, обеспечивающий переключение ОЗУ 16i (17i) с периодом гд из режима считывания в режим перезаписи и наоборот.

Управляющие входы процессора БПФ 6, выходного коммутатора 7i, коммутатора перезаписи 72 и блока перестановки отсчетов 8 также имеют связи с соответствующими выходами блока управления.

Назначение и конкретный вид всех управляющих сигналов будут рассмотрены ниже.

Остановимся подробнее на процедуре вычисления N М - точечного БПФ с помощью поточного процессора БПФ, выполняющего вычисление NI М - точечного БПФ.

В заявляемом устройстве на входы поточного процессора БПФ 6 поступают отсчеты с М-ично инверсным порядком следования в отличие от естественного порядка следования отсчетов исходной информации, записываемых в ОЗУ в режиме записи..

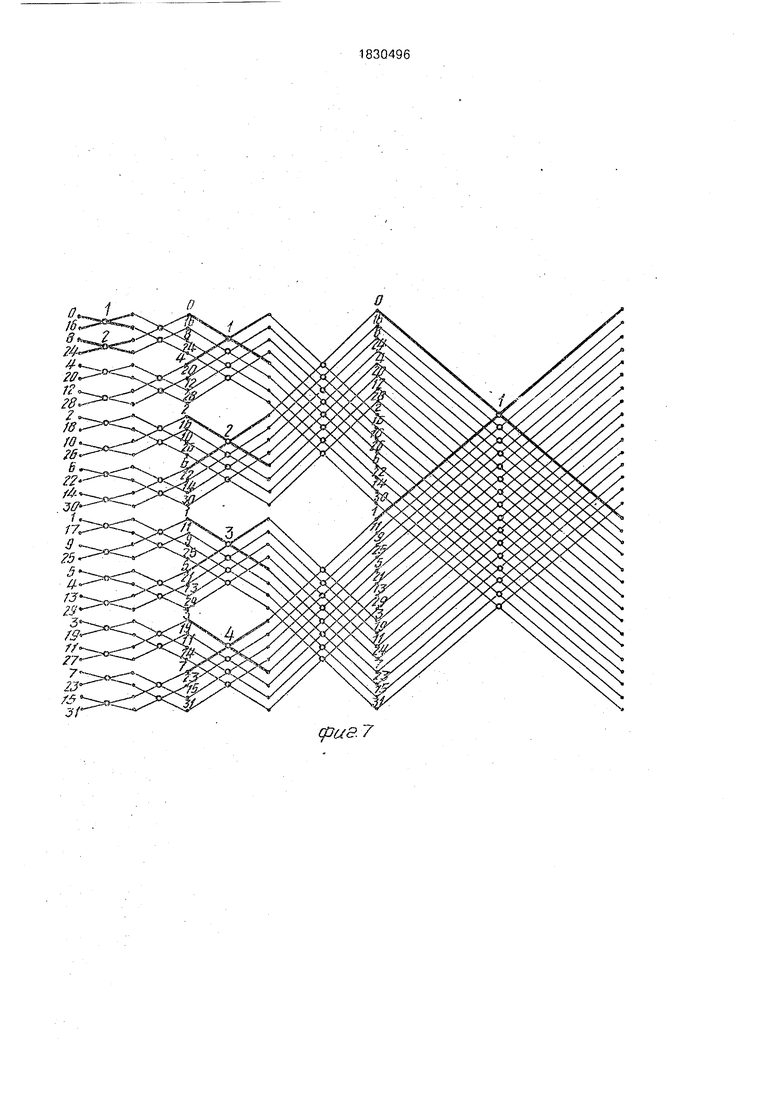

Как известно, направленный граф вычисления N-точечного БПФ содержит (с Aitq) этапов вычислений (итераций), на каждом из которых выполняется базовых операций вычисления М - точечных БПФ,

Пусть поступающие с выхода приемника отсчеты записываются в блок 5 таким образом, чтобы считываемые с 1-х ОЗУ отсчеты, соответствующие отражением от одного элемента дальности, имели М-ично - инверсный порядок следования. Причем в каждый дискрет времени отсчеты считываются со всех М ОЗУ одновременно по одинаковым адресам. Последовательность адресных кодов образует натуральный ряд чисел,

При первоначальной загрузке в поточный процессор БПФ последовательности М-размерных векторов входных отсчетов (нулевой цикл (со) считывания - см, фиг.6) на его выходах будут формироваться последовательности М-размерных векторов выходных отсчетов, совпадающих с выходными отсчетами направленного графа на Ai-й итерации, В случае, если выходные отсчеты поточного процессора БПФ являются промежуточными результатами вычислений, их следует перезаписать в освободившиеся ячейки ОЗУ с целью последующего считывания для продолжения процесса вычислений.

Однако перед каждой перезаписью необходимо осуществить такую перестановку выходных отсчетов поточного процессора БПФ, чтобы, во-первых, 1-е отсчеты считываемых впоследствии М-размерных векторов снова были записаны в 1-х, ОЗУ, а во-вторых, последовательность считываемых отсчетов соответствовала входным отсчетам последовательности бабочек направленного графа, выполняемых в определенном порядке на (S А1+1)-й итерации, где S - порядковый номер цикла перезаписи.

Для определения адресов считывания nojcj e -S-ro цикла перезаписи

(5 {1;Г1Д:о) р

варительно по направленному графу выявить те бабочки на всех (S Ai+1)-x итерациях, которые учавствуют в формировании входных отсчетов на(с-1)(прй q 0), либо (с А1+1)-й (при q & 0) итерации (последний цикл считывания).

Последовательность адресов считывания Гор, р 1.N/M, после S-ro цикла перезаписи соответствует последовательности порядковых номеров входных узлов бабочек на (S Ai+1)-n итерации, участвующих в формировании входных отсчетов последовательности бабочек, загружаемых в последнем цикле считывания.

Найденная последовательность адресов считывания, уже не образующая натуральный ряд чисел, должна храниться в соответствующем ПЗУ в ячейках памяти, последовательность адресов которых составляет натуральный ряд чисел.

При такой последовательности считывания обеспечивается возможность проведения дальнейших вычислений с помощью процессора БПФ с размером преобразования Ni без изменения его внутренних параметров: величин задержки его линий задержки и режимов работы каскадных переключателей,

От порядкового номера цикла считывания зависят лишь значения комплексных поворачивающих множителей, вводимых в АУ промежуточных каскадов процессора с выходов соответствующих запоминающих устройств (ЗУ), Поэтому структура адресов,

подаваемых на адресные входы ЗУ процессора, должна иметь вид Зп, где 5 - порядковый номер цикла считывания, п 1.N/M - порядковый номер загрузки процессора БПФ, Поскольку процессы перезаписи и считывания могут накладываться друг на друга, начало очередного цикла считывания должно происходить с задержкой в относительно начала предшествующего цикла перезаписи, по крайней мере достаточной

для обеспечения опережения записи над считыванием необходимых отсчетов. Минимальное допустимое значение в, при котором в одном из дискретов времени совпадают запись и считывание одного и

того же отсчета, а задержка считывания остальных отсчетов относительно их записи превышает один дискрет времени, расчитывается по формуле

0

0

N М

Ni-(- }--Ni)/Ni

-Ј-N,

М

ы

М Ni

+ 1,

(D

справедливость которой подтверждается временными диаграммами на фиг.8.

Перестановка промежуточных результатов вычислений осуществляется в блоке 8, структурная электрическая схема которого

показана на фиг.2.

Эта схема в точности совпадает со схемой перестановки отсчетов, включенной в промежуточном Ai-м каскаде типичного поточного процессора БПФ (см, фиг .5) с М-ичноинверсным порядком следования входных отсчетов, для которого j-e, j 1,М-1, линии задержки, включенные в К-м(К 1,А- каскаде слева и справа от переключателя Пк соответственно равны (см. Свердлик М.Б.

Цифровые методы обработки радиолокационных сигналов. Учебное пособие,- Одесса: ОПИ, 1984).

Ч

N

Ж .МА«К-1

То-ЧМ 4 r0, j 1,M-1,(2)

,

М

1.М-1,

(3)

где TO - темп загрузки поточного процессора БПФ. Соответственно для К AI, имеем

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1277135A1 |

Существо изобретения: устройство содержит 1 селектор дальности 1, 1 блок формирования и оцифровки квадратурных составляющих. 2, 1 блок защиты от пассивных помех 3. 1 блок коммутации информационных сигналов 4. 1 блок оперативных запоминающих устройств 5, 1 поточный процессор быстрого преобразования Фурье по основанию М 6, 2 коммутатора 7 и 1 блок перестановки отсчетов 8. 1-2-4- 5-6-7, 6-7-8-4, 9-1. 9-2. 9-3, 94, 9-5. 9-6. 9-7. . 8 ил.

Л1

rjrtl(M-j)M

яН

(4)

Время задержки сигнала в блоке перестановки отсчетов 8 равно:

А 4-м-1 (М-1)м А 1.

(5)

Исследуем особенности взаимных расположений на временной оси циклов считывания и перезаписи, учет которых необходим при разработке блока управления 9.15.

Время обработки М-размерного вектора входных отсчетов поточным процессо- ром БПФ 6, как видно из фиг.5, с учетом формул (2) и (3) равно:

At - 1 1 t,, AitAy + (M-1) 2

л 1

САплу + 1)т0,

где ГАУ - время выпол нения арифметических операций над комплексными отсчетами в одном арифметическом блоке (АУ) поточного процессора БПФ.

При максимальной степени параллелизма схем сложения и умножения комплексных чисел можно принять r- 3 т0 . Таким образом

tn (3Ai + 1)г„,

(7)

Общее время задержки начала 3-го цикла перезаписи относительно начала предыдущего цикла считывания с учетом (5) и (7) равно:

т.3 tn + Д- 3 Ai + - 1 + (М - г0 (3Ai- I )Го.-(8)

Длительность цикла считывания, либопере- записи

T -N- .

(9)

Временные диаграммы работы устройства приведены на фиг.6а,б,в. Там же приведены соответствующие значения параметров С, q,Ai, М и введены обозначения/.t т.з + 0i v- -Т .

В таблице даны сравнительные оценки расчетных величин 1з,/м, vw tn.

0

5

0

5

0

5

Как видно из таблицы, в варианте фиг.бв, п.З, 4, 5, 6 расчетное значение v О, что свидетельствует о перекрытии S-го цикла перезаписи с. предыдущим и последующим циклами считывания. В остальных случаях v 0 (фиг.66) и v 0 (фиг.бв, п.1, 2, 7). .

Перекрытие трех циклов работы ОЗУ вызывает повышенные требования к его быстродействию, т.к. всилутого, что микросхема ОЗУ имеет один адресный вход и по одному информационному входу и. выходу, каждый из указанных трех циклов должен выполняться в последовательные отрезки времени длительностью то/3 каждый,

В заявляемом устройстве в варианте фиг.бв, п.З. 4, 5, 6 значение параметра ; искусственно увеличено до нуля, т.е. к концу предыдущего цикла считывания непосредственно примыкает начало следующего цикла считывания. При v 0 всегда имеет место перекрытие лишь двух циклов работы ОЗУ (перезаписи и считывания), каждый, из которых выполняется в последовательные отрезки времени длительностью Го/2.

Определим соотношение между тактовым периодом работы устройства в режиме считывания.(го) и в режиме записи (Гд). При N NI в поточный процессор БПФ загружается в течение времени

т NI T

т -м-То

NI

точечный массив комплексных отсчетов, порождаемых отражениями от одного элемента дальности, а за время Т0бщ. Lmax

Nj

М

Го

происходит загрузка LmaxNi отсчетов, соответствующих отражением от Lmax элементов дальности, составляющих всю дистанцию. При этом период зондирования Tn Lmax % где г д - интервал разрешения по дальности. Как видно из фиг.З, для нормальной работы устройства необходимо выполнение условия

N,

Т06щ. Lmax -jyj TO N1 TO NlLmaxrA, (10)

откуда находим

Тд.

Пусть быстродействие поточного процессора БПФ определяется величиной TO 2 тд, соответствующей значению М 2.

Тогда при выполнении устройством N- точечного БПФ, где N NI, переключение ОЗУ с режима считывания в режим перезаписи и обратно должно происходить с пери одом то/2 Тд, т.е. быстродействие ОЗУ должно вдвое превышать быстродействие поточного процессора БПФ. Выпускаемые промышленностью микросхемы ОЗУ для большинства используемых на практике значений интервалов разрешения по дальности обладаю требуемым быстродействием.

Как видно из фиг.6, время затрачиваемое на преобразование N-точечного массива операнд, соответствующих отражением от одного элемента дальности, равно:

IT +13+ бдля фиг.ба, б (у+1)Г для фиг.бв, Г С- 1 при q 0 с прид 0.

Общее время, затрачиваемое на преобразование массива, операнд, соответствующих отражением от L элементов дальности, равно

Т0г,щ. LTi NT,,.

(12)

из (12) находим допустимое число обрабатываемых элементов дальности

I -ИТл | L- Tl J(13)

где - целая часть b, а значение Ti рассчитывается по формулам (1), (8), (9), (11).

Таким образом, при увеличений требуемого числа доплеровских каналов с NI до N, количество стробируемых элементов дальности сокращается с Lmax до величины L, расчитываемой по формуле (13).

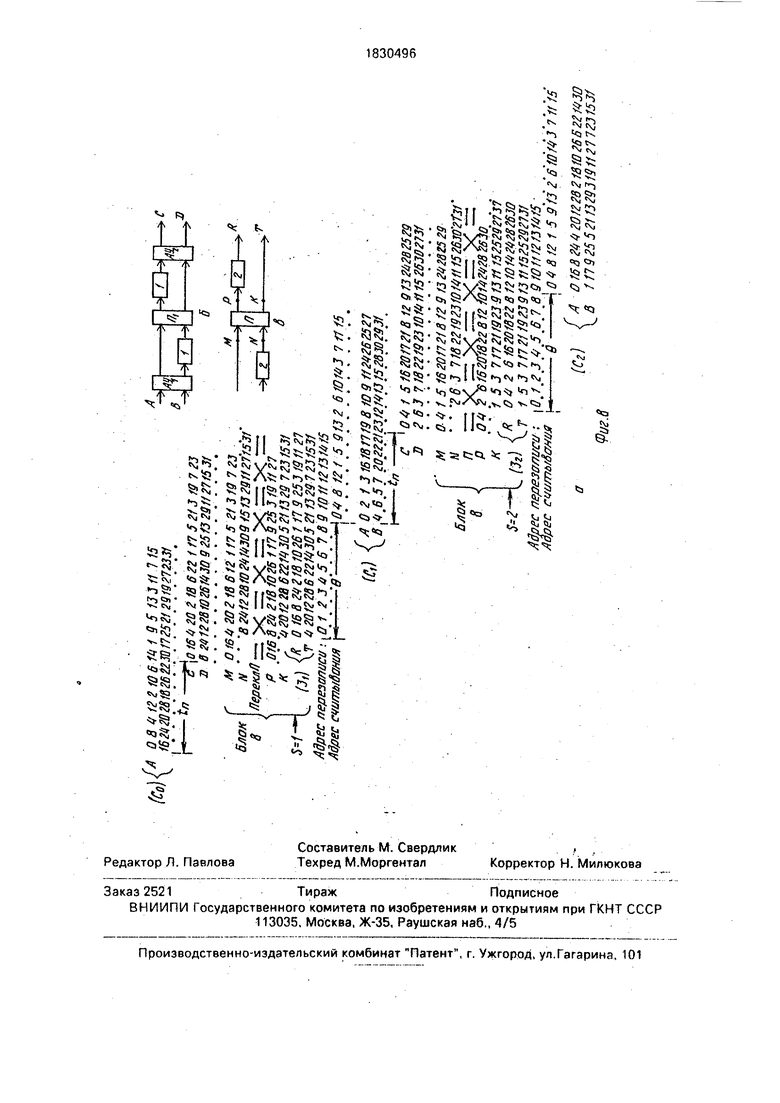

На фиг.7 и 8а приведены соответственно направленный граф и временные диаграммы работы устройства для зна

чений N 25 и Ni 22 (А 1 2, С - 2, q 1, М 2), позволяющие проследить формирование циклов считывания и перезаписи. Жирными линиями на фиг.7 очерчены ветви

5 бабочек, участвующих в формировании входных отсчетов бабочек на последней итерации.

На фиг.8,б и 8,в изображены соответственно структурные электрические схемы

10 поточного процессора БПФ и блока перестановки отсчетов с указанием величин задержек, включенных слева и справа от переключателей П. Выходные отсчеты устройства снимаются после начала цикла счи15 тывания (С2 с выходов первого каскада (AVi) поточного процессора БПФ.

Рассмотрим работу блока управления 9, структурная электрическая схема которого приведена на фмг.4,

25 Схема блока управления содержит ряд счетчиков числа импульсов, работающих по moda, где а - один из переменных параметров, известный заранее для каждого заданного значения N М А , А С Ai+ q,

30 хранящийся а ПЗУ 34. Адресным кодом для ПЗУ 34 служит значение параметра А, а в ячейках памяти для каждого заданного А хранятся следующие константы (значения a): qiNiT (вычисляется по ф.9), L (см. ф. 13)/

35

f С - 1 при q О

(14) .

С при q 0, .

40 u у + 1, tn (см. ф.7), t.3 (см. ф.8), в (см. ф.1), . у tn + Г ,

45

11 для фиг.ба, б О для фиг.бв,

(15)

. Принципиальная схема счетчика по переменному moda содержит собственно счетчик импульсов, текущие состояния А ко-.

торого сравниваются в схеме сравнения с кодом числа а, поступающим на ее второй информационный -вход с соответствующего выхода ПЗУ 34. При А а на выходе схемы сравнения формируется выходной сигнал

счетчика no rnoda, который сбрасывает последний э нулевое состояние, после чего его цикл работы повторяется.

Рассмотрим формирование управляющих сигналов, обеспечивающих работу устройства в режиме записи.

ГИД 25 генерирует последовательность импульсов с периодом следования гд, равным интервалу разрешения по дальности, которые поступают на управляющие входы АЦП 11 и заводятся на вход цепи, содержащей включенные последовательно счетчики

по mod (27) и modN (35, 36). Выходной

Гд

сигнал счетчика по modNi, снимаемый с выхода схемы сравнения 36, поступает на счетный выход триггера 37, на выходах которого (LU1 и Ш2) формируются импульсы, поступающие соответственно на управляющие входы адресных и информационных коммутаторов 18, 14 и 19, 15, л.также, через схемы 20; и 21j, на входы выборки кристалла (CS) ОЗУ 16i и 17|. подготавливая последние к работе в режимах записи и считывания. При этом нулевой потенциал на выходе триггера 37, обеспечивает включение соответствующего ОЗУ в режим записи и коммутацию на его адресный вход соответствующего адреса записи, хранящегося в ПЗУ 49, а единичный потенциал на том же выходе триггера 37 обеспечивает включение того же ОЗУ в режим считывания и коммутацию на его адресный вход считывающего адреса.

Для формирования строба дальности используется схема сравнения 40, на первые и вторые информационные входы которой заводятся соответственно коды текущих состояний счетчика 27 и код числа LO, поступающий с РЛС и определяющий начальную координату строба дальности.

Выходной импульс схемы сравнения 36 устанавливает в нулевые состояния триггеры 26, 41, 52, 89. 90, счетчики 43, 46, 54, 63, 72, 91, 95, 96, 99 и в единичные состояния триггеры 61,71, 80.

Сигнал с выхода схемы сравнения 40 поступает на вход 1 триггера 41, опрокидывая его в единичное состояние npwкотором разрешается прохождение через схему И 42 выходных импульсов ГИД 25 на вход счетчика по modL (счетчик 43, схема сравнения 44 и схема ИЛИ 45). Выходной импульс схемы сравнения 44 опрокидывает триггер 41 и счетчик 43 в нулевое состояние и поступает на вход счетчика по mod -j-jr (счетчик

46, схема сравнения 47 и схема ИЛИ 48). г

Адреса записи формируются с учетом следующих условий. ОЗУ 16i и 17i имеют

N

адресные поля размером L х -г-р Пусть адреса записи в ОЗУ 16; или 17| последовательности NL отсчетов эхо-сигналов, соответствующих отражениям от L стробируе- мых элементов дальности в N периодах зондирования представляются в виде трех- 5 мерных массивов и имеют кодовую структуру ISi, где I 1,М - порядковый номер ОЗУ, I 1,1 и S 1.N/M - соответственно строчная и столбцовая координаты ячейки памяти i-ro ОЗУ.

0 Потребуем, чтобы N отсчетов, записанных в ячейках памяти ОЗУ с адресами ISi, соответствующие отражениям от 1-го элемента дальности в N периодах зондирования, имели М-ично-инверсный по

5 сравнению с естественным порядок следования.

Расположив в соответствующих ячейках памяти 1-х ОЗУ М-ично-инверсную N-точеч- ную последовательность отсчетов для любо0 го I const, легко определить порядковые номера j €E i ОЗУ и столбцовые координаты m G S ячеек памяти, в которых оказываются записаны отсчеты с естественным порядком следования.

5В схеме заявляемого устройства найденные для I const адреса т, соответствующие S, хранятся в ПЗУ 49 в ячейках памяти с адресами ASI, а адреса j ОЗУ, в которых хранятся отсчеты с естественным порядком

0 следования п, хранятся в ПЗУ 50 в ячейках памяти с адресами An, где n 1,N - код текущего состояния счетчика 35, подаваемый с выходов разрядных ячеек последнего (совместно с кодом параметра А) на адрес5 ный вход ПЗУ 50.

Код адреса j представляет собой М-би- товое слово, содержащее единицу в j-м разряде и нули во всех остальных разрядах. Соответственно ПЗУ 50 имеет М выходов

0 (QJ5).

Сигнал с i-го, i 1,M, выхода ПЗУ 50 поступает через схемы ИЛИ 201 и 211 на входы выборки кристалла (CS) Соответственно ОЗУ 16i или 17|.

5 Таким образом, в режиме записи в каждый дискрет времени происходит выборка одного определенного ОЗУ (16i или 17i), т.к. на первый вход схем ИЛИ (20i или 21|) с выхода триггера 37 поступает нулевой по0 тенциал (в режиме считывания на указанном выходе триггера имеет место единичный потенциал, включающий все ОЗУ соответствующей группы).

Для обеспечения работы ОЗУ в режиме

5 записи необходимо также подать на их входы запись-считывание нулевой потенциал, который снимается с выхода той схемы И (38 или 39). на вход которой с выхода триггера 37 поступают нулевой потенциал.

В режиме считывания потенциал на выходе той схемы И (38 или 39), на которую с триггера 37 поступает единичный потенциал, определяется уровнем сигнала, подаваемым на второй ее вход с выхода триггера 26. Этим обеспечивается в режиме считывания переключение ОЗУ в режим перезаписи.

Рассмотрим работу блока управления в режиме считывания. Как отмечалось выше, в этом режиме в зависимости от задаваемого значения возможны три варианта временных диаграмм работы устройства, изображенные на фиг,ба,б,в.

Импульсы с выходов триггера 26, сдвинутые друг относительно другз на время Го/2 Гц, поступают в блоки 30 и 31 формирования адресов перезаписи и считывания на первые входы схем И 51 и 60. Рассмотрим сначала формирование циклов считывания и перезаписи в вариантах фиг,бз и б.

В .исходный момент времени, определяемый формированием импульса на выходе схемы сравнения 36, триггер 52 сбрасывается в нуль, запрещая при этом схему И 51. а триггеры 61 и 71 устанавливаются в единичные состояния, разрешая прохождение тактовых импульсов, снимаемых с прямого выхода триггера 26, через схемы И 60 и 69 на счетные входы счетчиков 63 м 72, работающих соответственно по mod гт- и mocl(tn+T ).Выходы разрядных ячеек счетчика 72 нагружены на информационные входы схем сравнения 73, 74, 75, на вторые информационные входы которых с выходов ПЗУ 34 поступают коды чисел (tn+T J, ta и tn. а выходы разрядных ячеек счетчика 63 нагружены на схемы сравнения 64 и 65, на вторые информационные входы которых с выходов ПЗУ 34

поступают коды чисел Т - -г-г- и tn. Просчитав -гт- импульсов, счетчик 63 сбрасывается

нуль выходным импульсом схемы сразне- ния 64. На этом завершается нулевой цикл считывания (Со).

Импульс с выхода схемы сравнения 64 поступает на первый аход схемы И 66 и на счетчик 95, нагруженный на схемы сравнения 94 и. 93, на вторые информационные входы которых с соответствующих выходов ПЗУ 34 поступают коды чисел v (см. ф,14) и

V-M.

Для данных фиг.ба, б 1. После просчета счетчиком 95 первого входного импульса, формируется импульс на выходе схемы сравнения 94, который, будучи задержан линией задержки 84 на время тъ и инвертирован схемой НЕ 85, поступает на третий.вход

схемы И 66, на второй вход которой с выхода X ПЗУ 34 .подается единичный потенциал. В момент появления импульса на выходе схемы сравнения 64 на третьем входе схемы

И-присутствует единичный потенциал. Поэтому указанный импульс проходит через схему И 66 и опрокидывает триггер 61 в нулевое состояние, при котором схема И 60 запирается.

После просчета счетчиком 72 t3 импульсов на выходе схемы сравнения 74 формируется импульс, который опрокидывает триггер 52 в единичное состояние, разрешая прохождение тактовых импульсов через схему И 51 на вход счетчика 54, Выходы счетчика 54 нагружены на схемы сравнения 55 и 56, на вторые информационные входы которых с выходов ПЗУ 34 поступают коды

чисел -vr- и 0. После подсчета счетчиком М

54 в импульсов формируется импульс на выходе схемы сравнения 56, который перебрасывает триггер 51 из нулевого состояния в вдиничное, после чего.начинается следующий цикл (С1) считывания, в конце которого на выходе схемы сравнения 64 появляется второй импульс, Однако этим импульсом триггер 61 не будет сброшен в нуль, т.к. к моменту его появления схема И

66 будет запрещена нулевым потенциал-ом на выходе схемы НЕ 85 и счетчик 63

N

выполн1/гг очередной цикл счета по mod

М

(цикл Со для I 2). После просчета счетчиком 95 второго импульса формируется импульс на выходе схемы сравнения 93, который перебрасывает о единичное состояние триггер 71, до зтого сброшенный в нуль выходным импульсом схемы сравнения 73,

после чего описанный процесс работы блока управления повторится. Выходной импульс схемы сравнения 73 сбрасывает также в нуль счетчик 72.

При описаний работы блока формирования циклов перезаписи 30 мы остановились на момента просчета счетчиком 54 0 импульсов. После просчета N/M импульсов на вы- ходе.схемы сравнения 55 появится импульс, который опрокинет счетчик 54 в нулевое состояние, завершив формирование первого цикла перезаписи (3i), а пройдя через схему И 58, которая.к этому моменту разрешена выходным потенциалом схемы сравнения 94, опрокинет в нуль триггер 52, прервав тем

самым-повторный цикл счета счетчика 54, который возобновится после поступления на вход Г. триггера 52 импульса с выхода схемы сравнения 74.

Рассмотрим теперь формирование -циклов считывания и-перезаписи для фиг.бв.

В этом случае, в отличие от фиг.6а,б, каждый из указанных циклов на интервале TI следуют непрерывно один за другим с задержкой циклов перезаписи относительно циклов считывания на время t3, причем на интервале Ti формируется (V + 1) циклов считывания и V циклов перезаписи.

В варианте фиг.бэ счетчики 63 и 72-одновременно начинают свою работу, поскольку в исходный момент времени триггеры 61 и 71 устанавливаются выходным импульсом схемы сравнения 36 в единичное состояние, а на схему И 66 с выхода X ПЗУ 34 подан нулевой потенциал. Поэтому выходной импульс схемы сравнения 64 сбросит, как и прежде, счетчик 63.в нулевое состояние, но на вход О триггера 61 не пройдет и, следовательно, счетчик 63 будет продолжать циклически работать по moclN/M,

Счетчик 72 после просчета (tn + Т)-импульсов сбрасывается в нуль выходным импульсом схемы сравнения 73, который также сбрасывает в нуль триггер 71, а до этого, после просчета счетчиком 72 ts импульсов выходным импульсом схемы сравнения 74 опрокинется в единичное состояние триггер 52, запустив в работу счетчик 54, который теперь циклически будет работать no modlM/M, т.к. схема И 58 в течение (V - 1) циклов работы счетчика 63) заперта нулевым потенциалом на выходе схемы сравнения 94.

После просчета счетчиком 95 V-ro импульса на выходе схемы, сравнения 94 устанавливается единичные потенциал, разрешающий прохождение через схему И 58 V-ro.выходного импульса схемы сравнения 55, который опрокидывает триггер 52 и счетчик 54 в нулевое состояние. При этом схема И 51 запрещается и счетчик 5.4 в дальнейшем остается в нулевом состоянии.

Очередной цикл работы счетчика 54 начинается после повторного опрокидывания триггера 52 в единичное состояние выходным импульсом схемы сравнения 74гпояв- лению которого предшествует просчет счетчиком 95 (V+1)-ro импульса, после чего на выходе схемы сравнения 93 формируется импульс, опрокидывающий триггер 71 в единичное состояние, при котором возобновляется работа счетчика 72.

Выходные импульсы схемы сравнения 93 заводятся на вход счетчика по modL (счетчик 91, схема сравнения 101 и схема ИЛИ 102).

Структура кодов адресов перезаписи имеет вид )п, где i 1,L и n 1.N/M соответственно коды текущих состояний счетчиков 91 и 54. Составляющие i и п адресов перезэ0

5

писи хранятся соответственно в ПЗУ 53а и 53i по адресам и А п.

Структура кодов адресов считывания имеет вид lmgp.

где I 1,L - составляющая адреса считывания (код текущего состояния счетчика 91), хранящаяся в ПЗУ 62г по адресу I;

Р 1.N/M - код текущего состояния счетчика 63...

-р ет8-« ™«

состояния счетчика 95, соответствующий порядковому номеру выполняемого цикла считывания.

msp-составляющая адреса считывания, найденная по направленному графу, хранящаяся в ПЗУ 62i по адресу A SP.

Адресный кодАЗР, поступающий на адресный вход ПЗУ 62i, подается также (с зы- 0 хода Ш14 блока уп р авления) на адресные входы всех ЗУ1, I 1, AI поточного процессо- ра БПФ 6, в ячейках оюрого для каждого цикла S работы процессора хранятся соответствующие поворачивающие множители. В случае q 0 поворачивающие множители, соответствующие последнему циклу считывания, хранящиеся в ЗУл1 Ai-ro каскада поточного процессора БПФ равны 1 для любых значений AI и С.

Входы CS ПЗУ 531 и 53а подключены к выходу схемы И 51, а входы CS ПЗУ 62i и 62з подключены к выходу схемы И 60.

На выход Ш6 соответственно с попарно объединенных входов ПЗУ 531 и 62i, а-также 5 532 и 622 поступают коды адресов записи in и адресов считывания msp, имеющие каждый длительность г0/2 и сдвинутые друг относительно друга на время г0/2.

Перейдем теперь к рассмотрению режимов работы выходного коммутатора 7i и коммутатора перезаписи 72.

Пусть при подаче на управляющие входы указанных коммутаторов единичных потенциалов их информационные входы коммутируются на соответствующие выходы.

Для перезаписи в промежуточных результатов вычислений во всех V (см. 14) циклах перезаписи достаточно, чтобы передний фронт импульса управления работой 0 коммутатора 72 (см. фиг.6 - Ш 1.0) совпадал с началом нулевого цикла считывания (Со), а задний фронт был задержан относительно конца предпоследнего ((V-1)-ro) цикла считывания на время tn г0 (см. ф.7). : В вариантах фиг.6а,б V - 1. О, поэтому задержка из tn to относительно конца нулевого цикла считывания эквивалентна задержке относительно его начала на время (tn + Т ) г0.

5

0

0

5

5

Передний фронт управляющего импульса, воздействующего на коммутатор 71 см. фиг,6 - Ш11 должен совпадать с моментом окончания предпоследнего цикла считывания, а задний фронт должен быть задержан на время tn относительно момента окончания последнего (V-ro) цикла считывания.

Для формирования импульса, управляющего работой коммутатора 1г в вариан- тах фиг.ба ,6. триггер 80 устанавливается выходными-импульсами схем сравнения 36 или 93 в единичное состояние, а выходным импульсом схемы сравнения 73, прошедшим через схемы И 77 и ИЛИ 78, сбрасывается в нуль.

В варианте фиг.6в, когда схема И 77 заперта нулевым потенциалом на выходе X ПЗУ 34, выходной импульс схемы сравнения 73 не проходит на вход О триггера 80. Для сброса триггера 80 в нулевое состояние в этом случае используется схема сравнения 65, периодически формирующая на выходе импульс в момент накопления в счетчике 63 числа т.п. Этот импульс проходит через схему И 79, разрешенную по второму входу единичным потенциалом на выходе схемы НЕ 86, лишь после просчета счетчиком 95 V (см. 14) импульсов, когда на выходе схемы сравнений 94 появится единичный потенциал, разрешающий схему И 79 по первому, входу.

Импульс с выхода схемы И 79, пройдя через схему ИЛИ 78, опрокинет триггер 80 в нулевое состояние.

Сформированный на прямом выходе триггера 80 импульс является искомым управляющим сигналом, поступающим на выход Ш10 блока управления (см. фиг,6 - Ш10).

Для формирования импульса, управля- ющего работой коммутатора 7i, используется триггер 82, который в вариантах фиг.ба, б устанавливается в нулевое состояние выходным импульсом схемы сравнения 75, формируемым в момент накопления в счет- чике 72 числа tn (схема И 88 при этом разрешена единичным потенциалом на выходе X ПЗУ 34), а в единичном состоянии - выходным импульсом схемы сравнения 94. В варианте фиг.ба нулевое состояние триг- гера 82 периодически подтверждается выходным импульсом схемы сравнения 65.

Сигнал, формируемый на прямом выходе триггера 82 (фиг.6 - Ш11), поступает с выхода Ш11 блока управления на управля- ющий вход коммутатора 7i.

В заключение рассмотрим процесс формирования управляющих импульсов, обеспечивающих необходимый режим переключений переключателя 22 блока перестановки отсчетов 8.

Режим работы этого переключателя повторяет режим работы аналогичного переключателя промежуточного Ai-ro каскада типичного поточного процессора БПФ с М- ично-инверсной индексацией входных отсчетов, т.е. его период переключений равен (см. ф.2 при j 1, K Ai):

t22 M Vlr0.

Для частного примера, приведенного на фиг.8,

Т22 2.Г0.

Искомые управляющие импульсы формируются следующим образом.

В варианте фиг,.6а, б выходной импульс схемы И 88, задержанный на время tn T0 относительно начала нулевого цикла считывания, проходит через схему ИЛ И 89 на вход 1 триггера 90. Триггер 90 устанавливается в единичное состояние, разрешая прохождение через схему И 70 на счетный вход счетчика 96 тактовых импульсов, формируемых на прямом выходе триггера 26.

Счетчик 96 работает по modT22, что достигается путем дешифрации дешифратором 97 кода числа Таз и сбросом выходным импульсом последнего счетчика 96 а нулевое состояние.

Повторное опрокидывание триггера 30 в единичное состояние произойдет при повторном цикле работы счетчика 72.

. В варианте фиг.бв схема И 87 разрешена единичным потенциалом на выходе схемы НЕ 86 и через нее проходит на вход 1 триггера 90 импульс с выхода схемы сравнения 65, задержанный нэ время tn TO от- носительно начала нулевого цикла считывания. .

Выходные сигналы дешифратора 97 поступают на счетчик 98, первоначально сброшенный в нуль выходным импульсом схемы сравнения 36 и в дальнейшем обнуляемый выходными сигналами схемы сравнения 64.

Коды текущих состояний счетчика 98 поступают с выхода Ш13 блока управления на управляющий вход переключателя 22 блока перестановки отсчетов 8 и на адресные входы запоминающих устройств процессора БПФ 6,

Рассмотренная схема блока управления, в отличие от блока управления, используемого в прототипе, отличается, в основном, дополнительным включением

блока формирования адресов перезаписи 30 и блока формирования управляющих сигналов 32.

Заявляемое устройство может быть реализовано на современной элементарной базе. ПЗУ могут быть выполнены на основе микросхем серии НС К556, мультиплексоры, счетчики входят в состав серии НС 555, 530, 533 и др., а ОЗУ может быть выполнена на основе НС 541 или 132-й серии,

Таким образом, заявляемое устройство, в отличие от прототипа, характеризующегося фиксированным числом NI реализуемых доплеровских каналов, обладает возможностью гибкой перестройки структуры, при которой на базе того же поточного процессора БПФ реализуется заданное число N NI, доплеровских каналов при соответствующем сокращении числа стробируемых элементов дальности.

Так, например,если при Тп 3000 тл, М 2, AI 2, N N4 4 число наблюдаемых элементов дальности L Lmax 3000, то при N 28 количество L сокращается в 4 раза.

Заявляемое устройство при незначительном усложнении блока управления может также быть использовано в многоканальных по пространственным направлениям системам, где соответствующее заданному N общее число L стробируемых элементов дальности может быть распределено по некоторому расчетному числу пространственных каналов. Примером реализации такого размена числа наблюдаемых элементов дальности на число пространственных каналов служит заявка № 4779908/09 от 8.01.90 г., находящаяся в настоящее время на рассмотрении по ВНИИГПЭ, отличаются от заявляемого устройства тем, что в ней, как и в прототипе, количество доплеровских каналов является фиксированным числом.

Формула изобретения

Цифровое устройство доплеровской фильтрации, содержащее блок управления, соединенные последовательно селектор дальности, блок формирования и оцифровки квадратурных составляющих и блок защиты от пассивных помех, а также включенные последовательно блок оперативных запоминающих устройств (ОЗУ) и процессор быстрого преобразования Фурье (БПФ) по основанию М, выполняющий преобразование N 1-точечного массива комплексных операндов (IMi М ), при этом процессор БПФ содержит в j-м (j Т; Ai-1) каскаде арифметическое, устройство (AVj), вход поворачивающих множителей которого подключен к выходу соответствующего запоминающего устройства (3Vj),

первую и вторую группы линий задержки на величину соответственно trj и ТГ, где г 1 ,М-1 и переключатель, а eAi-м каскаде - АУ Аь блок формирования и оцифровки квадратурных составляющих содержит два фазовых детектора (ФД), первые входы которых подключены к выходу селектора дальности, выходы ФД соединены через соответствующие аналого-цифровые

преобразователи (АЦП) с входами блока за- щит1 от пассивных помех, а вторые входы ФД соединены с выходом когерентного гетеродина (КГ) непосредственно и через фазовращатель на 90°, блок ОЗУ содержит М

ОЗУ, каждое из которых содержит первую и вторую группы ОЗУ, адресных коммутаторов и элементов ИЛИ, выходы 1-го (1 1.М) адресного коммутатора и i-ro элемента ИЛИ, принадлежащих соответствующей

группе, подключены соответственно к адресному .входу и входу выборки кристалла i-ro ОЗУ одноименной группы, управляющие входы адресных коммутаторов и вторые входы элементов ИЛИ, принадлежащих соответствующей группе,

соединены между собой, первые и вторые информационные входы адресных коммутаторов обеих групп соединены между собой, управляющие входы селектора дальности,

АЦП, блока защиты от пассивных помех, адресных коммутаторов первой и второй групп, первые и вторые информационные входы всех адресных коммутаторов, а также управляющие входы всех переключателей

ц соединенные между собой адресные входы всех ЗУ процессора БПФ подключены к соответствующим выходам блока управления, отличающееся тем, что, с целью увеличения числа доплеровских каналов

при фиксированном аппаратурном объеме поточного процессора в БПФ, введены ЗУАч, блок коммутации информационных сигналов, выходной коммутатор, коммутатор перезаписи и блок перестановки отсчетов, при

этом блок коммутации информационных сигналов содержит две ipynnbi информационных коммутаторов, выходы и соединенные между собой управляющие входы 1-х (i .1 ,М) информационных коммутаторов

соответствующей из групп подключены соответственно к входам 1-х ОЗУ и управляющим входам адресных коммутаторов одноименных групп, первые информационные входы i-x информационных коммутаторов обеих групп попарно соединены и подключены к i-м выходам блока перестановки отсчетов, а соединенные между собой вторые информационные входы всех информационных коммутаторов обеих групп подключены к выходу блока защиты от пассивных помех, блок перестановки отсчетов содержит переключатель и две группы линий задержки, J-я О 1.М-1) линия задержки первой группы подключена выходом к (J+1)- му входу переключателя, а входом - к (J+1)- му выходу коммутатора перезаписи, первый выход которого соединен с первым входом переключателя, j-я линия задержки второй группы подключена входом к j-му входу переключателя, выход j-й линии задержки второй группы и М-й вход переключателя являются соответственно J-м и М-м выходами блока перестановки отсчетов, К-й (К .« Т,М) выход 1-го АУ процессора БПФ

tfbff.9

5

подключен к (i-1) входу выходного коммутатора. М выходов которого являются выходами устройства, Ягое АУ процессора БПФ соединено К-м выходом с К-м входом коммутатора перезаписи, а входом подачи поворачивающих множителей - с выходом Ач-го ЗУ процессора БПФ, адресный вход которого соединен с адресными входами остальных ЗУ процессора БПФ, управляю- щие.вхрды выходного коммутатора, коммутатора перезаписи и переключателя блока перестановки отсчетов соединены с соответствующими дополнительными выходами блока управления.

JILK

cpt/e.1

2 зпф У/Л- Б У23

-Ч

-#зл$

-.

96frOe8l

тшг

; --

Эй

i jjiti. //11

47Гтг1 %

9 ЗЛф

u u u u

(

1

И-S

/v г

-« В

9 б wee L

фи&7

.55

в

| Бакулев П.А | |||

| Стё лин В.М | |||

| Методы и устройства селекции движущихся целей | |||

| Радио и связь, М., 1986, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

| рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-07-30—Публикация

1990-06-28—Подача