Изобретение относится к автоматизированным системам управления, в частности к устройствам для приема и передачи информации территориально-распределенным объектам, и может быть использовано в сложных АСУ для решения задач управления, а также для автоматического контроля выполнения функций АСУ, заданных кортежами команд с указанием фиксированных моментов времени, когда эти команды должны исполняться.

Цель изобретения - повышение надежности устройства путем адаптации его функций к циклам работы объектов управления.

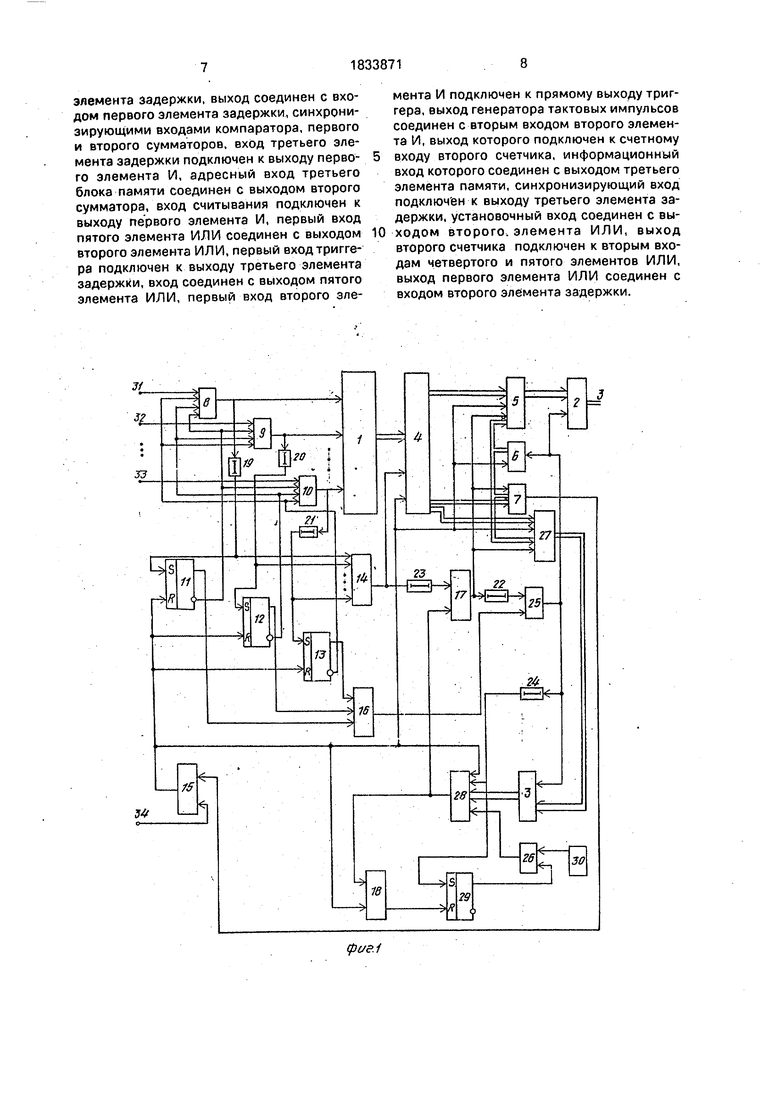

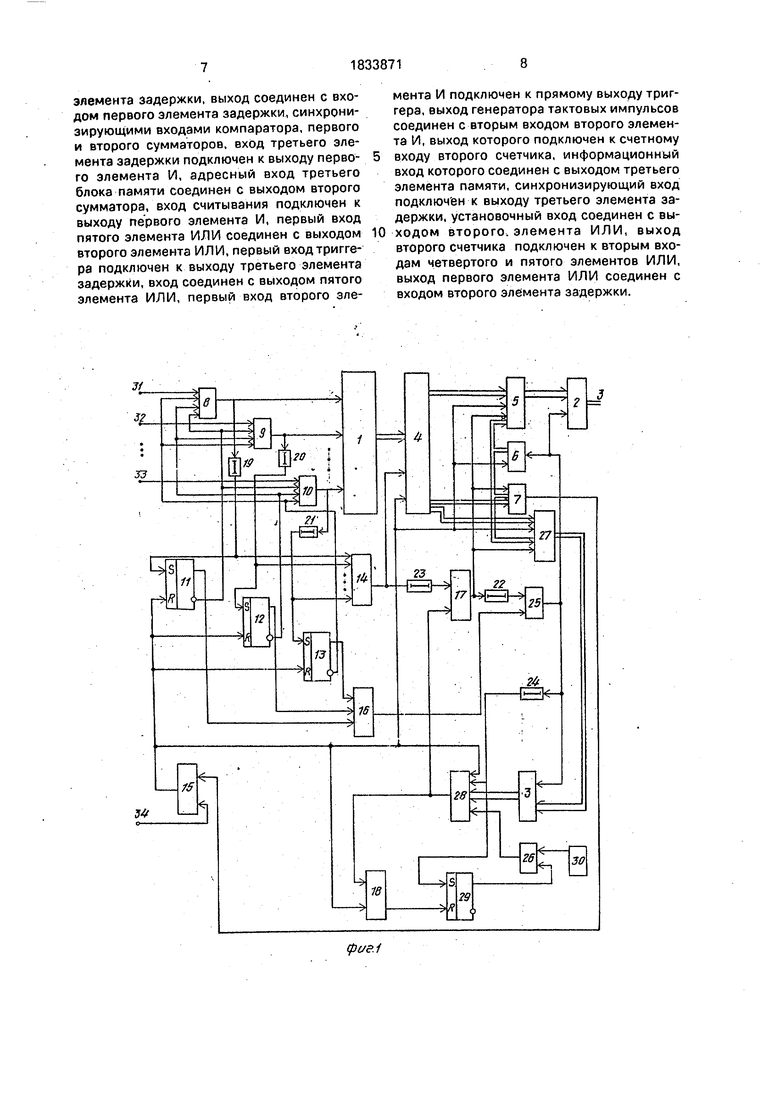

На фиг,1 представлена блок-схема устройства; на фиг.2 приведена структура кодового слова, хранимого в ячейках памяти блока; на фиг.З - представлена временная диаграмма работы устройства.

Устройство включает первый блок 1 памяти, выполненный в виде постоянного запоминающего устройства, в фиксированных ячейках которого хранятся (защиты) базовые адреса массивов команд управления, .второй блок 2 памяти, выполненный в виде оперативного запоминающего устройства, третий блок 3 памяти, выполненный в виде ОЗУ, регистр 4, первый сумматор 5, первый сумматор 5, первый счетчик 6, компаратор 7, первую группу элементов 8-10 И, группу триггеров 11-13, первый 14, второй 15, третий 16, четвертый 17 и пятый 18 элементы ИЛИ, группу элементов задержки 19-21, первый 22, второй 23, третий 24 элементы задержки, первый 25 и второй 26 элементы И, второй 27 сумматор, второй счетчик 28, триггер 29 и генератор 30.

В основу построения устройства положены следующие соображения.

Как и а известном устройстве, все кортежи (последовательности) команд заранее сгруппированы е том порядке, в котором они необходимы объектам управления.

CJ

со

00

xs

™«й

Каждому такому кортежу команд присваивается идентификатор Режим с соответствующим номером. В результате этого на пульте управления оператора вместо командной фиксированной клавиатуры будут клавиши с надписями Режим № 1, Режим № 2, Режим Ns 3 и т.д. (см. фиг.2 прототипа).

Кортежи команд заранее записываются в оперативное запоминающее устройство 2, а их базовые адреса, т.е. адреса записи первых команд в каждом из кортежей, фиксируются в ячейках ПЗУ 1.

Вместе с тем, в отличие от прототипа, кроме базового адреса первой команды кортежа, и количества команд в данном кортеже в ячейке памяти указывается и базовый адрес временного интервала, отделяющего каждую последующую команду от предыдущей.

Длительность каждого из указанных временных интервалов определяется временем, необходимым управляемому объекту для отработки полученной команды до получения следующей.

Структура кодового слова, хранимого в фиксированных ячейках блока 1, приведена на фиг,2.

Устройство работает следующим образом. Допустим, оператор нажал клавишу Режим N 1 и сигнал от нажатой клавиши поступил на один из входов 31-33 устройства, например, вход 31, оттуда он подается на импульсный вход элемента 8 И, имеющего еще три потенциальных входа, соединенных с нулевыми выходами соответствующих триггеров 11-13.

В исходном состоянии все триггеры 11- 13, а также регистр 4, сумматор 5, счетчик 6 и сумматор 27 сброшены в О сигналом Установка О с входа 34,

Поскольку все триггеры 11 + 13 находятся в нулевом состоянии, то с их нулевых выходов на входы элемента 8 И будут поданы высокие потенциалы и элемент 8 И будет открыт по всем входам. В результате этого входной импульс с входа 31 проходит сразу же на вход считывания соответствующей фиксированной ячейки памяти блока 1 и считывает ее содержимое в регистр 4. Причем часть разрядов ячейки (старших), где хранится базовый адрес команды, записывается в одни разряды регистра 4, другая часть ячейки, где хранится код числа, подлежащих выдаче команд в этом режиме, записывается в другие разряды регистра, а третья часть, где хранится базовый адрес временного интервала, записывается в оставшиеся разряды регистра 4.

Занесение информации в регистр 4 осуществляется тем же импульсом с входа элемента 8 И, задержанным соответствующим элементом задержки 19 группы на время

считывания данных из блока 1 и через элемент 14 ИЛИ, поступающий на синхронизирующий вход регистра 4д.

Этим же импульсом синхронизации с выхода элемента 19 задержки, поступающим на единичный вход триггера 11, последний переводится в единичное состояние и отрицательный потенциал с его нулевого выхода блокирует по соответствующему входу не только элемент 8 И, но

5 также элементы 9 и 10. Поэтому последующее случайное нажатие любой из клавиш Режим NS ни к чему не приведет. Наоборот, высокий положительный потенциал с единичного входа этого триггера 11 через

0 элемент 16 ИЛИ поступает на потенциальный вход элемента 25 И и открывает его, подготавливая цепь для прохождения импульсов считывания с выхода элемента задержки 22 через элемент 25 И на вход

5 считывания блока 2.

С информационных выходов регистра 4 базовый адрес подлежащего выдаче кортежа команд поступает на одни информацион- ные входы сумматора 5, на другие

0 информационные входы которого поступает содержимое счетчика 6. По импульсу с выхода элемента задержки 23, задерживающему импульс на время переходных процессов в регистре 4, поступающему через элемент 17

5 ИЛ И на синхронизирующий вход сумматора 5, последний суммирует код базового адреса с кодом счетчика 6. Учитывая, что к этому моменту времени в счетчике хранятся одни нули (он сброшен), то в сумматоре будет

0 зафиксирован адрес, который с информационных выходов сумматора будет подан на адресный вход блока памяти 2. Тот же импульс с выхода элемента 23 задержки, задержанный элемент 22 на время

5 срабатывания сумматора 5, в качестве импульса считывания через элемент 25 И поступает на вход считывания содержимого ячейки по указанному базовому адресу. В результате этого на информационном выхо0 де блока 2 памяти появляется код команды, который через информационный выход 35 устройства передается на объекты управления.

Таким образом, первая команда корте5 жа выдана. Для выдачи следующей за первой команды, импульс считывания с выхода элемента задержки, во-первых, поступает на счетный вход счетчика 6. фиксируя единицу в счетчике, а, во-вторых, поступает на вход считывания третьего блока памяти 3,

на адресном входе которого установлен код с выхода второго сумматора 27, и считывает код временного интервала в виде обратного кода на вход счетчика 28, куда он заносится импульсом синхронизации с выхода элемента задержки 24. Этот же импульс синхронизации поступает на единичный вход триггера 29 и устанавливает его в единичное состояние, при котором.последний высоким потенциалом открывает элемент 26 И и генератор 30 через него подключается к счетному входу счетчика 28.

Как только счетчик 28 переполнится числом импульсов, количество которых равно временному интервалу, на его выходе появляется импульс переноса, который, во- первых, через элемент 18 ИЛИ срабатывает триггер 29 в исходное состояние, а, во-вторых, через элемент 17 ИЛИ поступает на синхронизирующие входы сумматора 5, суммирующего базовый адрес регистра 4 с единицей, зафиксированной в счетчике 6, и сумматора 27, суммирующего базовый адрес временного интервала с единицей счетчика 6.

Тот же импульс, задержанный элемен- то м 22 задержки на время суммирования кодов и прошедший элемент 25 И, поступает на вход считывания блока памяти 2 и считывает очередную команду на выход 35.

Процесс выдачи команд (одна задругой) с заданными интервалами, продолжается описанным выше образом до тех пор, пока компаратор 7 не зафиксирует равенство кодов в счетчике 6 и регистре 4, что свидетельствует о том, что весь перечень команд, составляющих кортеж Режим № 1, на выход устройства выдан.

Равенство кодов счетчика 6 и регистра 4 фиксируется в момент подачи на синхронизирующий вход компаратора 7 импульса с выхода элемента 17 ИЛИ. Выходной импульс компаратора 7 через элемент 15 ИЛИ поступает на установочные входы регистра 4, сумматора 5, счетчиков 6, 27 и триггеров 11-13, возвращая триггер 11 из единичного в нулевое состояние и подтверждая нулевое состояние триггеров 12, 13. Триггер 11, возвращаясь в исходное состояние, снимает с единичного выхода высокий потенциал, поддерживающий элемент 25 И в открытом состоянии, и последний блокирует цепь прохождения импульсов считывания на вход считывания блока 2 памяти. После этого устройство готово к выдаче команд управления в других режимах.

Таким образом, введение новых узлов и элементов позволило существенно повысить надежность функционирования устройства.

Формула изобретения Устройство для приема и передачи информации, содержащее группы триггеров, инверсные выходы которых соединены с 5 объединенными соответствующими управляющими входами элементов И группы, информационные входы которых являются информационными входами устройства, выходы элементов И группы подключены к со0 ответствующим входам считывания первого блока памяти и к входам соответствующих элементов задержки группы, выходы которых соединены с первыми вхо- дами соответствующих триггеров группы и

5с соответствующими входами первого элемента ИЛИ, регистр, информационный вход которого подключен к выходу первого блока памяти, синхронизирующий вход соединен с выходом первого элемента ИЛИ, первый

0 сумматор, входы первой и второй группы которого подключены соответственно к первой группе регистра и выходам первого счетчика, установочный вход первого сумматора соединен с выходом второго элемен5 та ИЛИ, выход первого сумматора подключен к адресному входу второго блока памяти, выход которого является информационным выходом устройства, первый элемент И, первый вход которого соединен с

0 выходом первого элемента задержки, выход подключен к входу считывания второго блока памяти и счетному входу первого счетчика, установочный вход которого соединен с выходом второго элемента ИЛИ, выход под5 ключей к первым информационным входам компаратора, вторые информационные входы которого соединены с выходами второй группы регистра, выход подключен к первому входу второго элемента ИЛИ, второй

0 вход которого является установочным входом устройства, выход подключен к вторым входам триггеров группы, прямые выходы которых соединены с соответствующими входами третьего элемента ИЛИ, выход ко-.

5 торого подключен к второму входу первого элемента И, второй элемент задержки и четвертый элемент ИЛИ, отличающееся тем, что, с целью повышения надежности устройства, в него введены генератор такто0 вых импульсов, третий элемент задержки и блок памяти, пятый элемент ИЛИ, триггер, второй элемент И, второй сумматор, информационные входы первой и второй группы которого соединены соответственно с выхо5 дом первого счетчика и с выходами третьей группы регистра, установочный вход подключен к выходу второго элемента ИЛИ, синхронизирующий вход соединен с выходами четвертого элемента ИЛИ, первый вход которого подключен к выходу второго

элемента задержки, выход соединен с входом первого элемента задержки, синхронизирующими входами компаратора, первого и второго сумматоров, вход третьего элемента задержки подключен к выходу первого элемента И, адресный вход третьего блока памяти соединен с выходом второго сумматора, вход считывания подключен к выходу первого элемента И, первый вход пятого элемента ИЛИ соединен с выходом второго элемента ИЛИ, первый вход триггера подключен к выходу третьего элемента задержки, вход соединен с выходом пятого элемента ИЛИ, первый вход второго зле

мента И подключен к прямому выходу триггера, выход генератора тактовых импульсов соединен с вторым входом второго элемента И, выход которого подключен к счетному входу второго счетчика, информационный вход которого соединен с выходом третьего элемента памяти, синхронизирующий вход подключен к выходу третьего элемента задержки, установочный вход соединен с выходом второго, элемента ИЛИ, выход второго счетчика подключен к вторым входам четвертого и пятого элементов ИЛИ, выход первого элемента ИЛИ соединен с входом второго элемента задержки.

tf0s)-ffff f 0#aw# ff #e/#t/0/ ffa/t/newe

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПОДДЕРЖКИ ПРИНЯТИЯ РЕШЕНИЙ ПО ПОВЫШЕНИЮ РЕНТАБЕЛЬНОСТИ АВИАПЕРЕВОЗОК | 2005 |

|

RU2294013C2 |

| Устройство для считывания и обработки информации | 1988 |

|

SU1585813A1 |

| АНАЛИТИЧЕСКАЯ СИСТЕМА ИНФОРМАЦИОННО-МАРКЕТИНГОВОГО ЦЕНТРА | 2004 |

|

RU2274895C1 |

| Устройство для распознавания подвижных объектов | 1989 |

|

SU1649575A1 |

| Устройство для идентификации объектов | 1988 |

|

SU1647605A1 |

| ИНФОРМАЦИОННО-АНАЛИТИЧЕСКАЯ СИСТЕМА ПРОГНОЗИРОВАНИЯ ЭКОНОМИЧЕСКИХ ПОКАЗАТЕЛЕЙ ПАССАЖИРСКИХ АВИАПЕРЕВОЗОК | 2005 |

|

RU2289160C1 |

| Устройство для обмена информацией | 1989 |

|

SU1644149A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2023295C1 |

| Устройство для селекции признаков объектов | 1990 |

|

SU1725237A1 |

| СИСТЕМА УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ДОКУМЕНТООБОРОТОМ ИНФОРМАЦИОННО-МАРКЕТИНГОВОГО ЦЕНТРА | 2004 |

|

RU2260843C1 |

Изобретение относится к автоматизированным системам управления, в частности к устройствам для приема и передачи информации территориально-распределенным объектам. Цель изобретения состоит в повышении надежности устройства. Поставленная цель достигается путем временной адаптации устройства к временным параметрам управляемых объектов. Устройство содержит сумматоры 5,27 элементы 22, 23, 24 задержки, блоки 1,2,3 памяти, элементы ИЛИ 14, 15, 16, 17, 18 триггер 29, элементы И 25, 26 генератор тактовых импульсов 30, группу триггеров 11, 12, 13, группу элементов И 8, 9, 10, группу элементов задержки 19, 20, 21 регистр 4. 3 ил.

Редактор

Составитель Р. Исаенко

Техред М.МоргенталКорректор М. Керецман

Ф#г.З

2

| Устройство для приема и передачи информации | 1984 |

|

SU1203569A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство программного управления | 1988 |

|

SU1587504A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-15—Публикация

1991-03-18—Подача