Изобретение относится к области вычислительной техники и может быть исполь- зованоприпостроении

специализированных и проблемно-ориентированных процессоров для решения диф- ференциальных уравнений в частных производных эллиптического типа.

Цель изобретения - сокращение аппаратурных затрат за счет увеличения шага дискретизации при заданной точности вычислений.

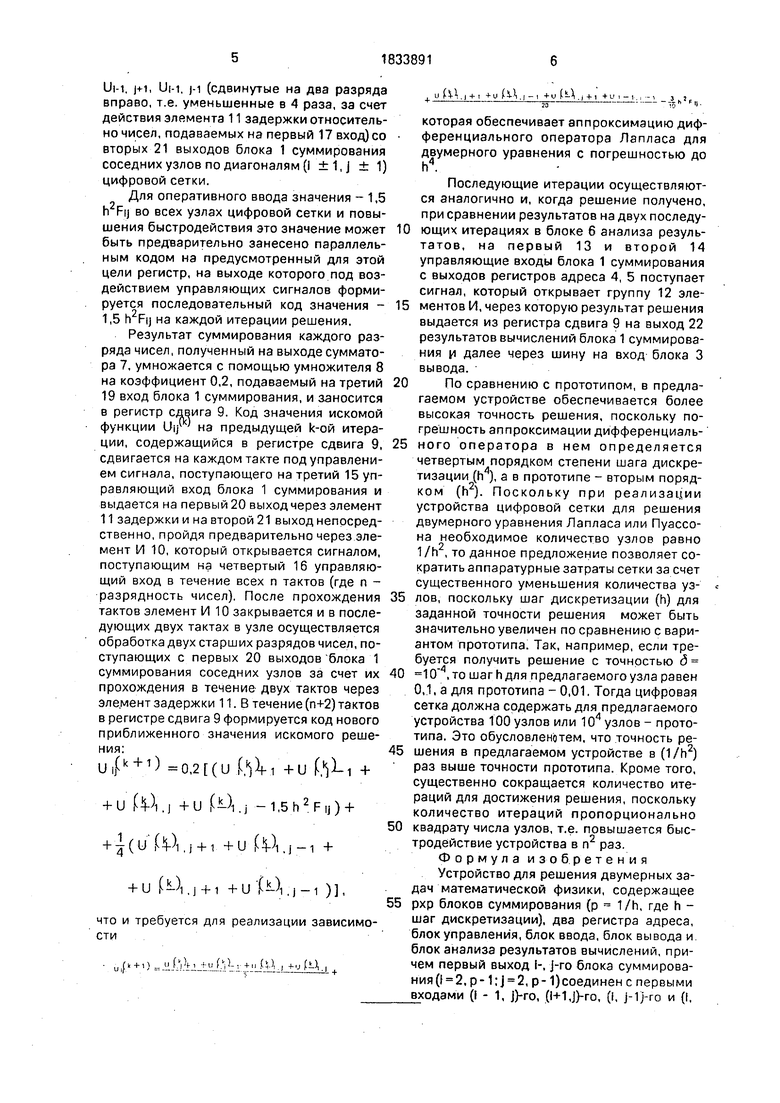

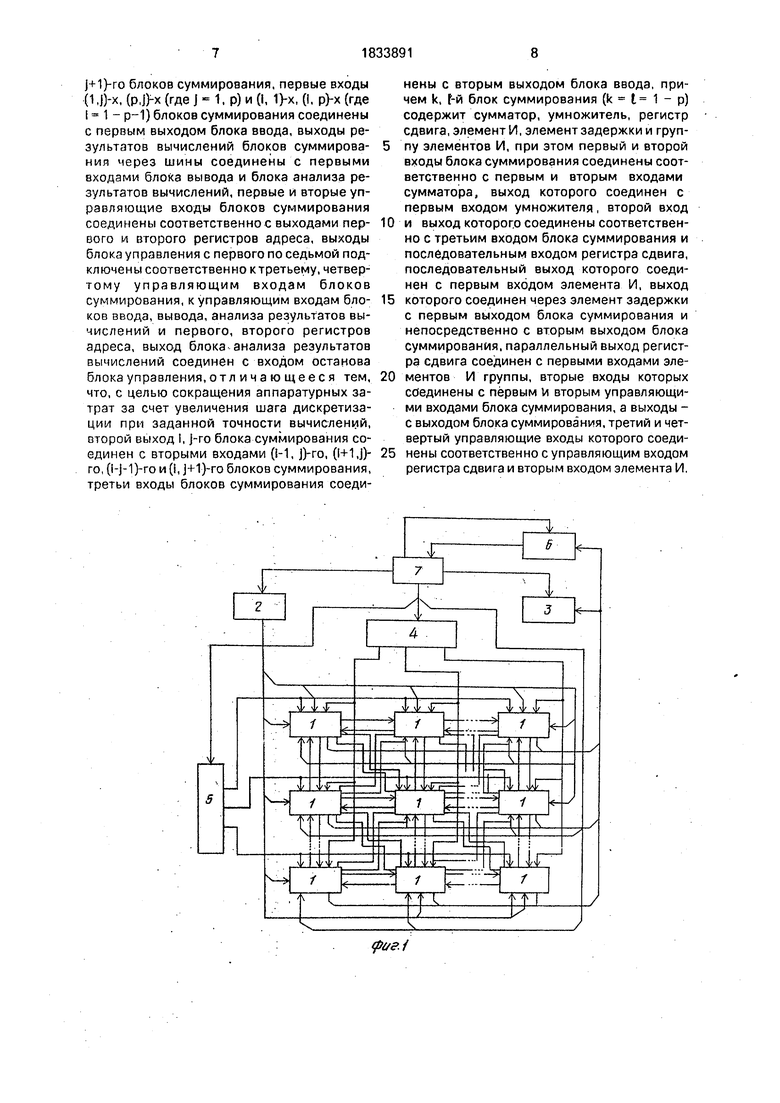

Блок-схема предлагаемого устройства представлена на фиг, 1 и содержит рхр блоков 1 суммирования (р 1/h , где h - шаг дискретизации), блок 2 ввода, блок 3 вывода, регистры 4 и 5 адреса, блок 6 анализа результатов вычислений и блок 7 управления.

Первый выход I, j-ro блока суммирования 1 (i 2, р-1, j 2, р-1) соединен с первыми входами (i-1,j)-ro, (i+1,j)-ro, (i,j-1)-ro n(i,j+1)-ro блоков суммирования 1, первые входы (1,J)- ых, (pj)-bix, где J 1,р, и (М)-ых, (,р)-ых, где 1 2-р-1, блоков суммирования 1 соединены с первым выходом блока ввода 2, выходы результатов вычислений блоков суммирования через шины соединены с первыми входами блока вывода 3 и блока анализа результатов вычислений б, первые и вторые управляющие входы блоков суммирования

со

00

со

00

чэ

1 соединены соответственно с выходами первого -1 и второго 5 регистров адреса, выходы блока управления 7 с первого по седьмой подключены .соответственно к третьему, четвертому управляющим входам блоков суммирования 1, к управляющим входам блоков ввода 2, вывода 3, анализа результатов вычислений 6 и первого 4, второго Б регистров адреса, выход блока анализа результатов вычислений 6 соединен с входом останова блока управления 7, второй выход i, j-ro блока суммирования 1 соединен о вторыми входами (1-1, j-1)-ro (i+ l, j-;-1}-ro, (i+i, j-1)-ro и (i-1, j-H}-ro-блоков суммирования 1, третьи входы блоков суммировании 1 соединены с вторым выходом блока «вода 2.

Блок управления 7 имеет типовую структуру на базе генератора импульсов, элементов И и элементов задержки. Он обеспечивает выдачу последовательности управляющих сигналов на:

входы блока 2 ввода для обеспечения ввода е блоки 1 суммирования кодов правых частой в точение птактов;

третьи и четвертые управляющие входы блоков 1 суммирования в течение соответственно (гН-2) и п тактов;

на входы регистров 4 и 5 адреса для йыбсра одного или нескольких (в зависимости от реализуемого алгоритма проверки на окончание итерационного процесса) блоков 1 суммирования и считывания из них результатов для выдачи в блок 6 анализа результатов или блок 3 вывода; .

на вход блока 6 анализа результатов для сравнения результатов вычислений на двух последовательных итерациях для одного или (нескольких узлов;

на управляющий вход блока 3 вывода для выдачи результата решения,

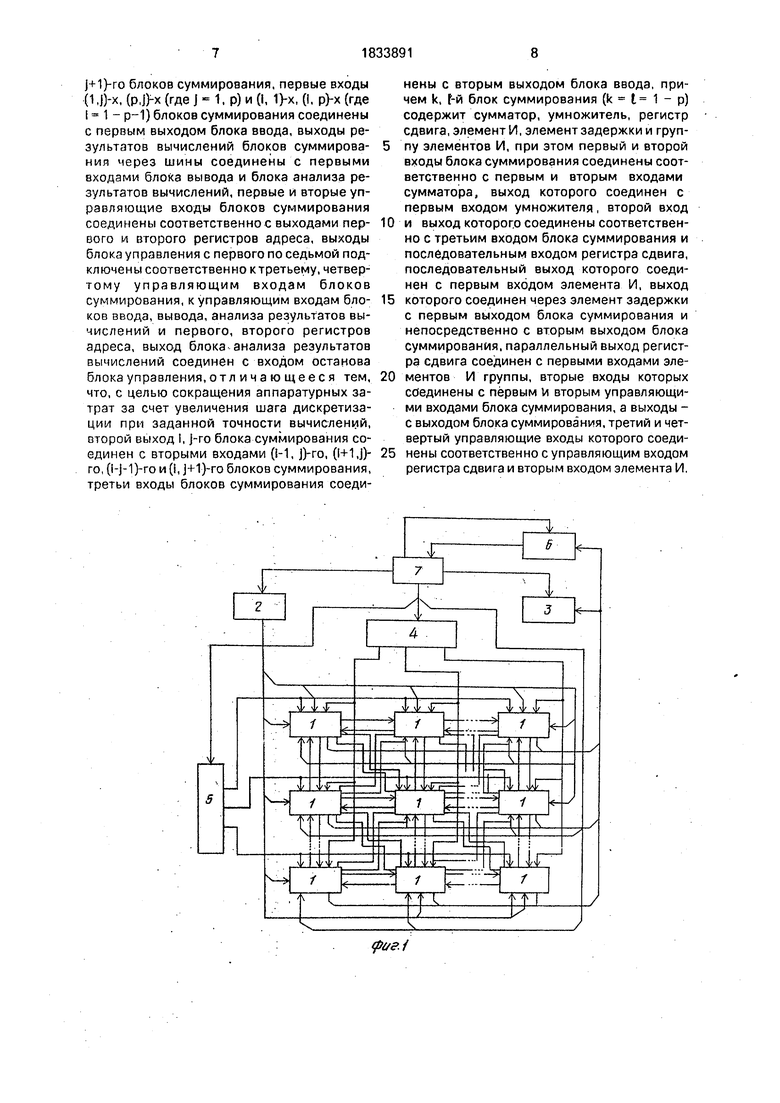

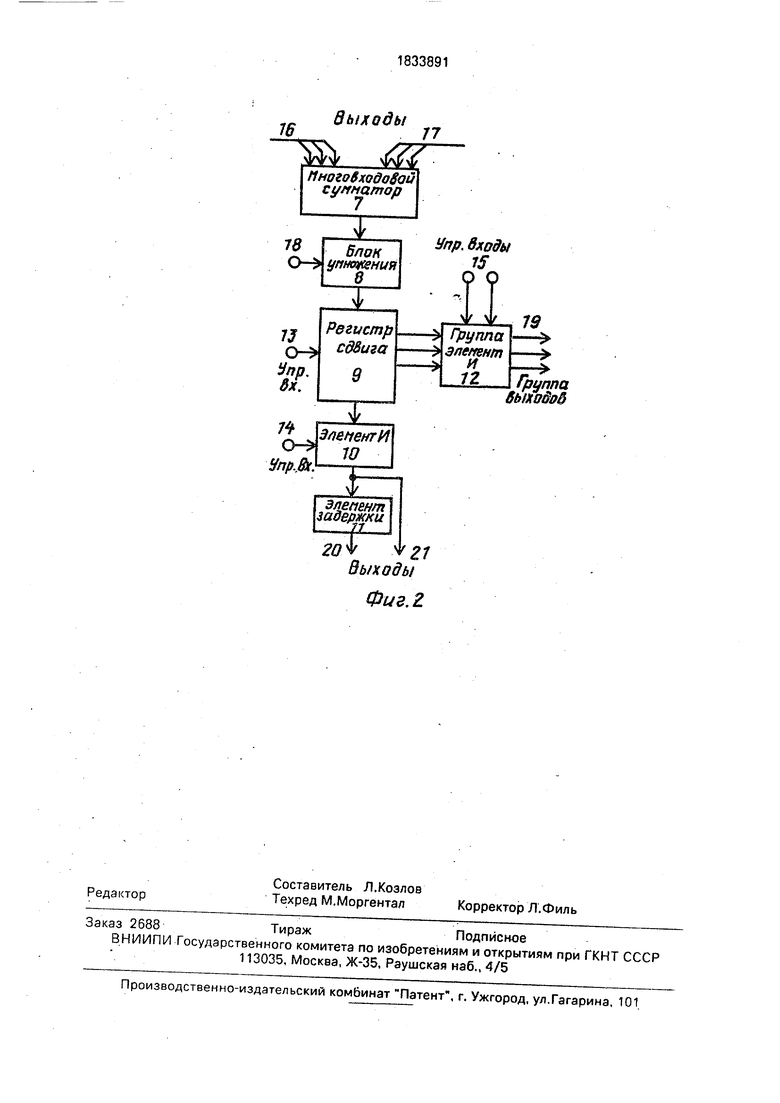

На фиг. 2 представлена схема блока 1 суммирования. Он содержит сумматор 7, умножитель 8, регистр сдвига 9, элемент И 10, элемент задержки 11, группу 12 элементов И, управляющие входы 13-16, входы 17-19, выходы 20, 21 и выход результатов вычислений 22 блока 1,

Первый 17 и второй 18 входы блока 1 суммирования соединены соответственно с первый и вторым входами сумматора 7, вы-. ход которого соединен с первым входом умножителя 8, второй вход и выход которого соединены соответственно с третьим 19 входом блока 1 суммирования и последовательным входом регистра сдвига 9, последовательный выход которого соединен с первым входом зле :1ента И 10, выход кото- j-.uro соединен через элемент задержки 11 с первым выходом 20 блока суммирования 1

и непосредственно с вторым выходом 21 блока суммирования 1, параллельный выход регистра сдвига 9 соединен с первыми входами элементов И группы 12, вторые входы

которых соединены с первым 13 и вторым 14 управляющими входами блока суммирования 1, а выходы - с выходом 22 результатов вычислений блока суммирования 1, третий 15 и четвертый 16 управляющие входы кото0 рого соединены соответственно с управляющим входом регистра сдвига 9 и вторым входом элемента И 10.

Предлагаемое устройство работает следующим образом.

5 Под воздействием сигналов с выхода блока 7 управления, блок 2 ввода выдает в последовательном коде, начиная с младшего разряда, значения кодов граничных условий на первые входы 17 внешних (1,J)-bix,

0 (р,)-ых, где j 1,р и (И)-ых, (,р)-ых, где I 2-р-1) блоков 1 суммирования и кодов правых частей (для уравнения Пуассона) на первые входы 17 всех блоков 1 суммирования, на другие шины входов 17 внутрен5 них (IJ-ых, где i 2, р-1, j 2, р-1) блоков 1 суммирования поступает последовательный код с четырех соседних слева и справа блоков 1 суммирования. На входы 18 (ij)-bix, где i 2 р-1, j 2, р-1, блоков 1

0 суммирования поступает последовательный код с вторых выходов четырех соседних по диагонали слева (i-1, j+1) и справа (i+1, j-1), сверху (i+1, j+1) и снизу (i-1, j-1) блоков 1 суммирования,

5На первый 17 вход блока 1 суммирования подается последовательный код четырех (для уравнения Лапласа) или пяти (для уравнения Пуассона) чисел младшими разрядами вперед. На второй 18 вход блока 1

.0 суммирования подается последовательный код четырех чисел младшими разрядами вперед, Каждый очередной разряд этих чисел поступает на входы сумматора 7, на выходе которого формируется результат

5 суммирования, Переносы в следующие разряды запоминаются на соответствующих элементах памяти (не показаны) сумматора 7 и используются в следующих тактах при суммировании следующих (1+1 и т.д.) разря0 дов чисел. При решении уравнения Пуассона на один их первый 17 вход подается последовательный код значения - 1,5 h FIJ, где FIJ - значение правой части уравнения. Кроме того, на первый 17 вход подаются

5 (синхронно с разрядами правой части) разряды значений Uij-м, Uij-1, UH-IJ Ui-i,j с пер- вого 20 выхода блока 1 суммирования соседних узлов по столбцу и строке (i,j) цифровой модели-сетки. На второй 18 вход подаются разряды значений Ui+i, J-H, DM. j-1,

Ui-1, j+i, Ui-i. j-1 (сдвинутые на два разряда вправо, т.е. уменьшенные в 4 раза, за счет действия элемента 11 задержки относительно чисел, подаваемых на первый 17 вход) со вторых 21 выходов блока 1 суммирования соседних узлов по диагоналям (i ±1,j ± 1) цифровой сетки.

Для оперативного ввода значения -1,5 h FIJ во всех узлах цифровой сетки и повышения быстродействия это значение может быть предварительно занесено параллельным кодом на предусмотренный для этой цели регистр, на выходе которого под воздействием управляющих сигналов формируется последовательный код значения - 1,5 h FIJ на каждой итерации решения.

Результат суммирования каждого разряда чисел, полученный на выходе сумматора 7, умножается с помощью умножителя 8 на коэффициент 0,2, подаваемый на третий 19 вход блока 1 суммирования, и заносится в регистр сдвига 9. Код значения искомой функции Ui/ на предыдущей k-ой итерации, содержащийся в регистре сдвига 9, сдвигается на каждом такте под управлением сигнала, поступающего на третий 15 управляющий вход блока 1 суммирования и выдается на первый 20 выход через элемент 11 задержки и на второй 21 выход непосредственно, пройдя предварительно через элемент И 10, который открывается сигналом, поступающим на четвертый 16 управляющий вход в течение всех п тактов (где п - разрядность чисел). После прохождения тактов элемент И 10 закрывается и в последующих двух тактах в узле осуществляется обработка двух старших разрядов чисел, поступающих с первых 20 выходов блока 1 суммирования соседних узлов за счет их прохождения в течение двух тактов через элемент задержки 11. В течение (п+2) тактов в регистре сдвига 9 формируется код нового приближенного значения искомого решения:

Uifk + 1) 0,2(uMW + U fol-i + + U ,Фи +U Щ. 1.5h2Fij) +

+ |(U PPi.J + 1 +U Wi.j-1 +

+ U Щ.Л-1 +U W.,-1 ),

что и требуется для реализации зависимости

+) ,lil hi-iiddki.±иШ i + ЛЦ.| +

и Ј$Л J-M + и ЈЦ.| - i +о l- .i + 1 +u i - I-., i з г,

+ -.. -... пц,.

которая обеспечивает аппроксимацию дифференциального оператора Лапласа для двумерного уравнения с погрешностью до h4.

Последующие итерации осуществляются аналогично и, когда решение получено, при сравнении результатов на двух последу0 ющих итерациях в блоке 6 анализа результатов, на первый 13 и второй 14 управляющие входы блока 1 суммирования с выходов регистров адреса 4, 5 поступает сигнал, который открывает группу 12 эле5 ментов И, через которую результат решения выдается из регистра сдвига 9 на выход 22 результатов вычислений блока 1 суммирования р далее через шину на вход блока 3 вывода.

0 По сравнению с прототипом, в предлагаемом устройстве обеспечивается более высокая точность решения, поскольку погрешность аппроксимации дифференциаль5 ного оператора в нем определяется четвертым порядком степени шага дискретизации (h ), а в прототипе - вторым порядком (h2). Поскольку при реализации устройства цифровой сетки для решения двумерного уравнения Лапласа или Пуассона необходимое количество узлов равно 1/h2, то данное предложение позволяет сократить аппаратурные затраты сетки за счет существенного уменьшения количества уз5 лов, поскольку шаг дискретизации (h) для заданной точности решения может быть значительно увеличен по сравнению с вариантом прототипа. Так, например, если требуется получить решение с точностью б

0 ,то шаг h для предлагаемого узла равен 0,1, а для прототипа - 0,01. Тогда цифровая сетка должна содержать для предлагаемого устройства 100 узлов или 104 узлов - прототипа. Это обусловлено тем, что точность ре5 шения в предлагаемом устройстве в (1/h ) раз выше точности прототипа. Кроме того, существенно сокращается количество итераций для достижения решения, поскольку количество итераций пропорционально

0 квадрату числа узлов, т.е. повышается быстродействие устройства в п2 раз. Формула изобретения Устройство для решения двумерных задач математической физики, содержащее

5 рхр блоков суммирования (р 1/h, где h - шаг дискретизации), два регистра адреса, блок управления, блок ввода, блок вывода и. блок анализа результатов вычислений, причем первый выход К j-ro блока суммирования 0 2, р- 1;j 2, р-1)соединен с первыми входами (I - 1, j)-ro, (i+1,J)-ro, (i, j-1)-ro и (i,

j+1)-ro блоков суммирования, первые входы (1 ,})-х, (pj)-x (где J - 1, р) и (I, , (I, р)-х (где р-1) блоков суммирования соединены с первым выходом блока ввода, выходы результатов вычислений блоков суммирова- нип через шины соединены с первыми входами блока вывода и блока анализа результатов вычислений, первые и вторые управляющие входы блоков суммирования соединены соответственное выходами пер- вого и второго регистров адреса, выходы блока управления с первого по седьмой подключены соответственно к третьему, четвертому управляющим входам блоков суммирования, к управляющим входам бло- ков ввода, вывода, анализа результатов вычислений и первого, второго регистров адреса, выход блока анализа результатов вычислений соединен с входом останова блока управления, от л ича ю щееся тем, что, с целью сокращения аппаратурных затрат за счет увеличения шага дискретизации при заданной точности вычислений, второй выход I, j-ro блока суммирования соединен с вторыми входами (1-1, j)-ro, (I+1J)- го, (i-j-l)-ro и (i, +1)-ro блоков суммирования, третьи входы блоков суммирования соединены с вторым выходом блока ввода, причем k, t-й блок суммирования (k 1 1 - р) содержит сумматор, умножитель, регистр сдвига, элемент И, элемент задержки и группу элементов И, при этом первый и второй входы блока суммирования соединены соответственно с первым и вторым входами сумматора, выход которого соединен с первым входом умножителя, второй вход и выход которого соединены соответственно с третьим входом блока суммирования и последовательным входом регистра сдвига, последовательный выход которого соединен с первым входом элемента И, выход которого соединен через элемент задержки с первым выходом блока суммирования и непосредственно с вторым выходом блока суммирования, параллельный выход регистра сдвига соединен с первыми входами элементов И группы, вторые входы которых соединены с первым и вторым управляющими входами блока суммирования, а выходы - с выходом блока суммирования, третий и четвертый управляющие входы которого соединены соответственно с управляющим входом регистра сдвига и вторым входом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ТРЕХМЕРНЫХ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 1991 |

|

RU2051411C1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Вычислительный узел устройства для решения уравнений в частных производных | 1991 |

|

SU1833892A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для вычисления логарифма | 1979 |

|

SU783798A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных и лроблемно-ориентированных процессоров для решения дифференциальных уравнений в частных производных эллиптического типа. Цель изобретения - сокращение аппаратурных затрат за счет увеличения шага дискретизации при заданной точности вычислений. Устройство содержит матрицу блоков суммирования, блок анализа результатов вычислений, блок ввода, блок вывода, блок управления, два регистра адреса, причем блок суммирования содержит многовхо- довый сумматор, блок умножения, регистр сдвига, элемент И, элемент задержки и группу элементов И. Предназначено для решения двумерных задач математической физики, отличается от известных высоким быстродействием и точностью решения и позволяет сократить количество узлов цифровой сетки.2 ил. (Л С

w

Выходы

лИ

77

| Математическое моделирование | |||

| Теория и методы гибридных вычислений | |||

| VI Всесоюзное совещание, Таллинн,апрель 1973, рефераты докладов | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

| Устройство для решения двумерных задач математической физики | 1975 |

|

SU610116A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-15—Публикация

1991-04-15—Подача