Изобретение относится к области вычислительной техники и может быть использовано в быстродействующих универсальных машинах. Известны устройства для вычисления функций табличным методом. Вычисление элементарной функции В таких устройствах сводится к выбору результата из блока постоянной памяти по значению аргумента ). . Недостатком таких устройств является большой объем постоянной памяти при вычислениях. Известны устройства для вычисления логарифма итерационным методом 2. Недостатком устройства является относительно большой объем постоянной памяти и низкое быстродействие. Наиболее близкое .к изобретению техническое ращение - устройство для вычисления логарифма со знакопеременными шагами итераций, с параллельной реализацией этапов вычислений. Устройство содержит регистр аргумента, регистр дополнительной переменной, регистр результата, блок сдвига, сумматор аргумента, сумматор дополнитель ной переменной, сумматор результата, блок постоянной памяти. Вычисление логарифма в устройстве представляет собой итерационный процесс. На первом этапе вычислений производится представление аргумента X функции в виде произведения (,..5.-); (,) где - номер итерации; п - разрядность устройства; - управляющие операторы, Ц,е -1, -н1. Результатом первого этапа вычислений является набор операторов i. На втором этапе вычислений по найденным значениям операторов i производится вычисление значения функции путем суммирования логарифмических констант, храняшихся в блоке постоянной памяти (l- -2--) - (2) Вычисления по формулам (1) и (2) представляются следующими рекуррентными уравнениями: Чм Ч- с ОСХ;., 2--Х./ 1-й этап U-SigrnY,.

г-й этап, (,)

де i 1, 1, 2, 2,..., п-1, л-1.

ачальные условия; Х Х, У, 1-Х,

.

езультат 9п tnX.

Недостатком устройства является изкое быстродействие, так как время ычисления логарифма, выраженное в единицах времени срабатывания элемента схемы, пропорционально п, Это объясняется тем, что последующий шаг итерации не может быть выполнен до тех пор, пока не будет определено значение оператора - в результате . Выполнения предыдущего шага итерации, который определяет направление послеующего вычисления.

Цель изобретения, - увеличение быстродействия устройства, путем уменьения времени вычисления на каждом этапе,

Поставленная цель достигается тем, что в устройство для вычисления логарифма, содержащее регистр аргумента, сумматор результата, регистр результата, блок сдвига, блоки постоянной памяти, причем выходы i-х блоков

постоянной памяти (i 1, 2п,

где п - разрядность устройства).подключены к i-м выходам сумматора результата, введены регистры разрядных цифр, сумматоры разрядных цифр, счетчики положительных единиц и счетчики отрицательных единиц, причем выход регистра аргумента соединен с входами младших разрядов регистров разрядных цифр, выходы i-X регистров разрядных цифр соединены с первыми входами i-х и вторыми входами (i-l)-x блоков постоянной памяти и с i-ми входами блока сдвига. Выход блока сдвига соединен с первыми входами счетчиков положительных и отрицательных единиц первые выходы i-X счетчиков положительных единиц соединены с первьоми входами i-X сумматоров разрядных .цифр, вторые выходы i-х счетчиков положительных единиц соединены с вторыми входами (i-l)-x счетчиков положительных единиц. Первые выходы i-х счетчиков отрицательных единиц соединены с вторыми входами i-х сумматоров разрядных цифр, вторые выходы i-x счетчиков отрицательных единиц соединены с вторыми входами (i-l)-x счетчиков отрицательных единиц. Выходы сумматоров разрядных цифр соединены с входами соответствующих регистров разрядных .цифр.

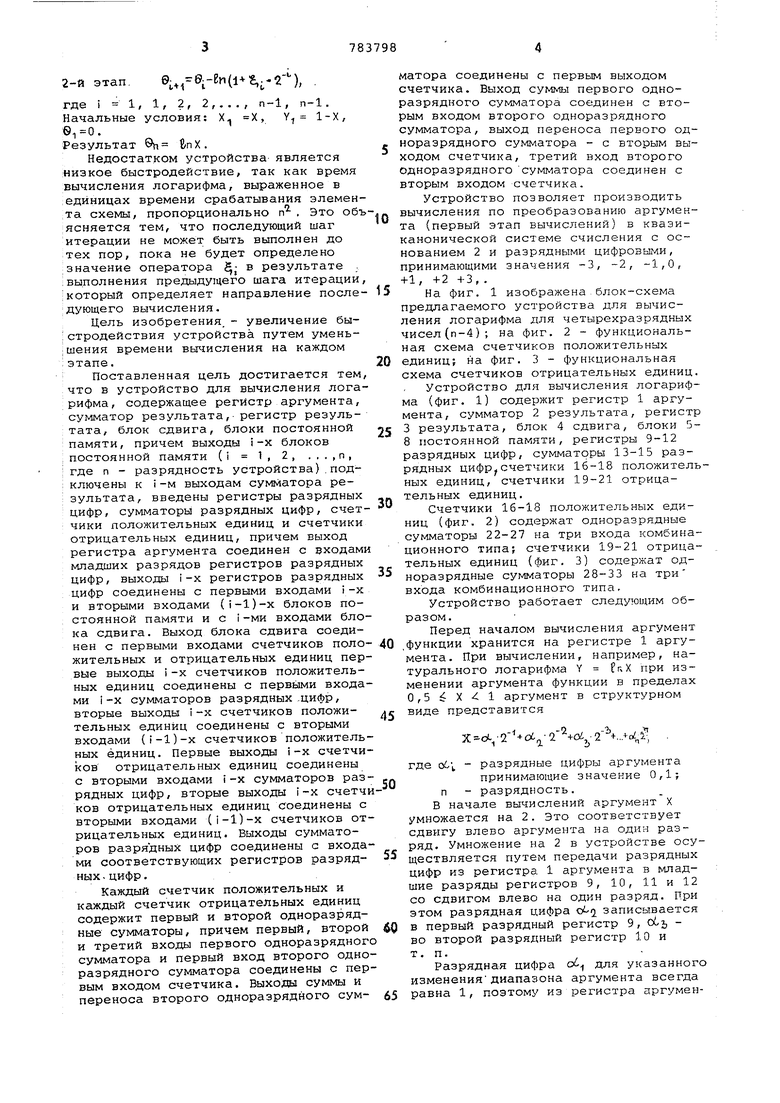

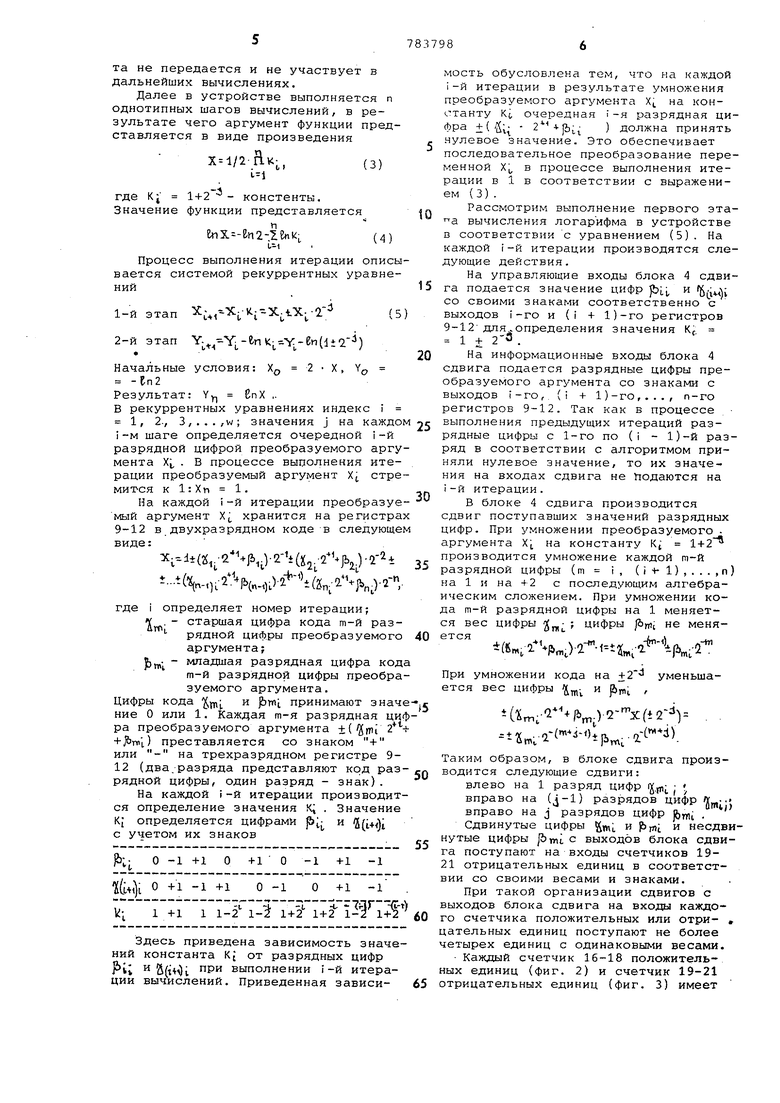

Каждый счетчик положительных и каждый счетчик отрицательных единиц содержит первый и второй одноразрядные сумматоры, причем первый, второй и третий входы первого одноразрядного сумматора и первый вход второго одноразрядного сумматора соединены с первым входом счетчика. Выходы суммы и переноса второго одноразрядного сумматора соединены с первым выходом счетчика. Выход суммы первого одноразрядного сумматора соединен с вторым входом второго одноразрядного сумматора, выход переноса первого одноразрядного сумматора - с вторым выходом счетчика, третий вход второго одноразрядного сумматора соединен с вторым входом счетчика.

Устройство позволяет производить вычисления по преобразованию аргумента (первый этап вычислений) в кваэиканонической системе счисления с основанием 2 и разрядными цифровыми, принимающими значения -3, -2, -1,0, +1, +2 +3, .

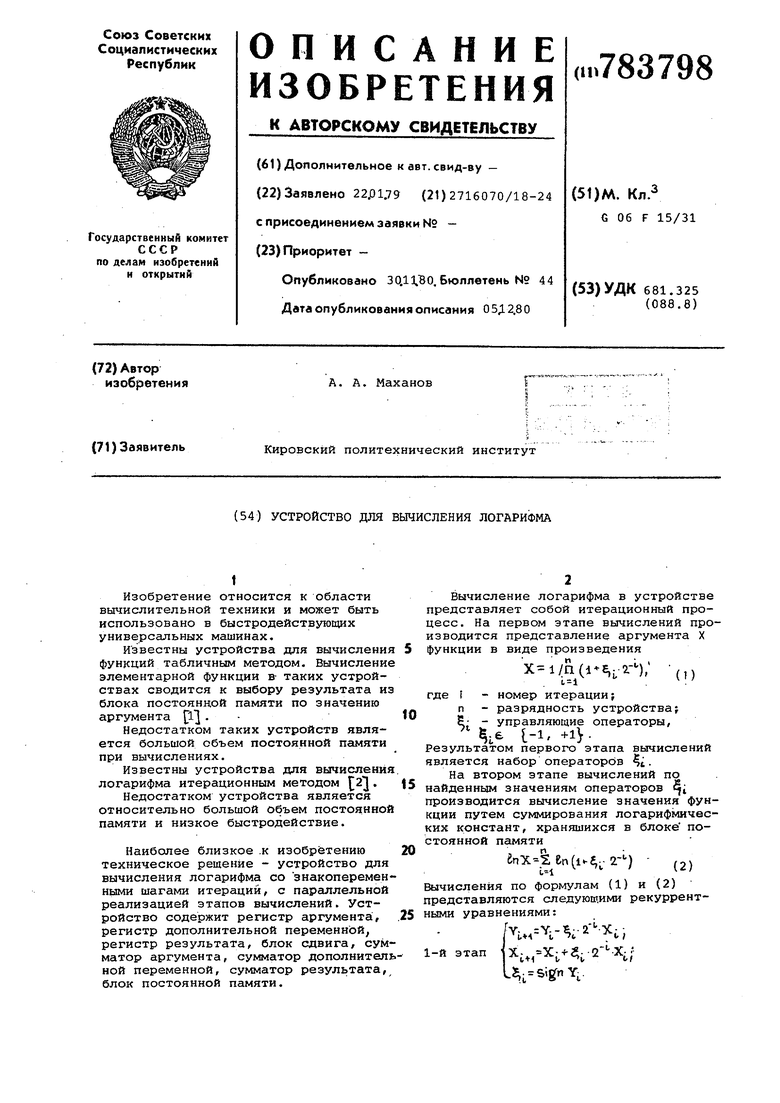

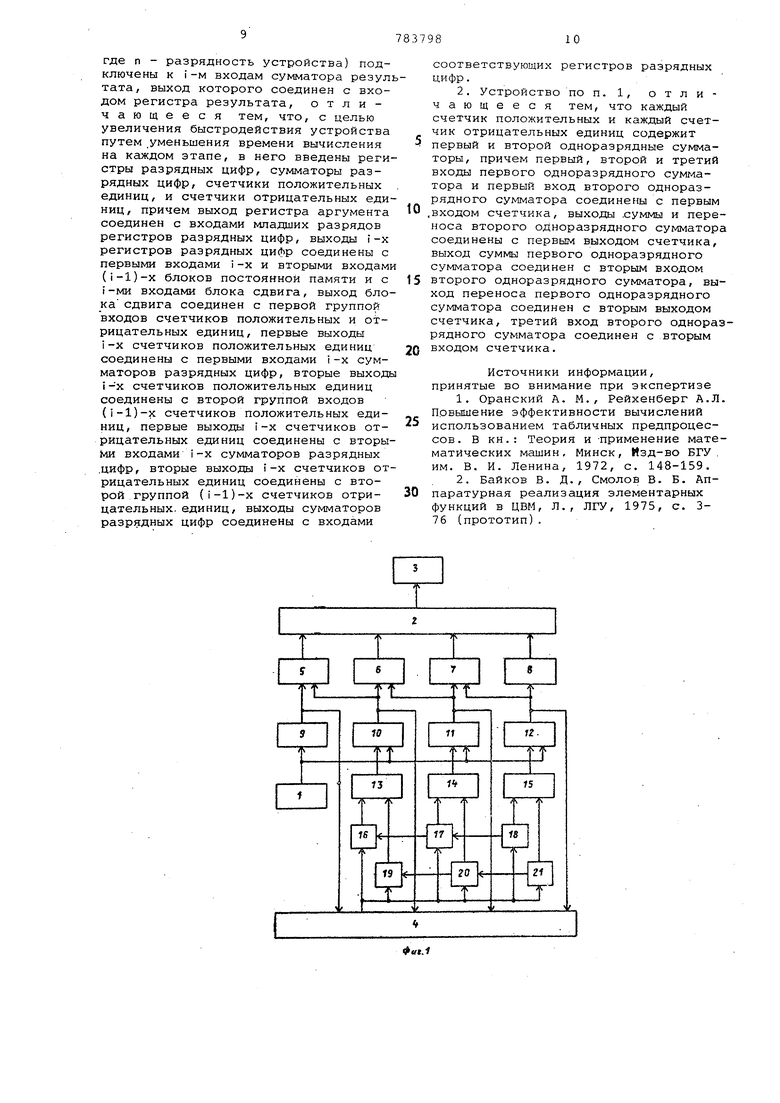

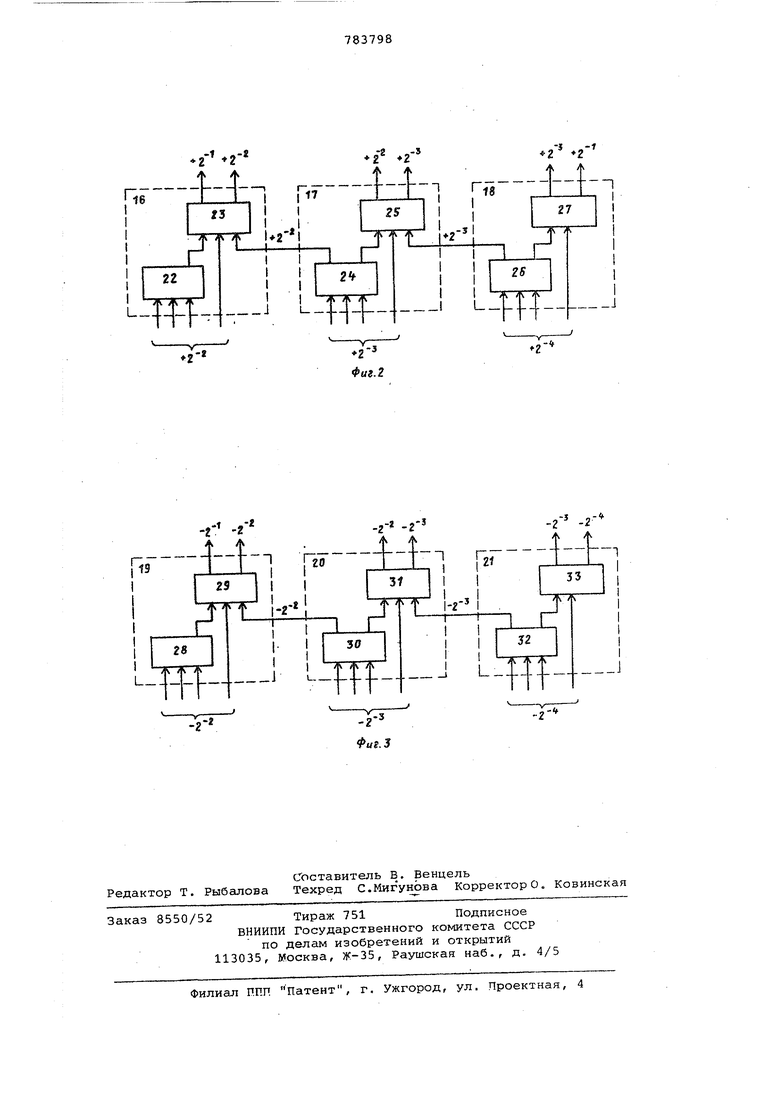

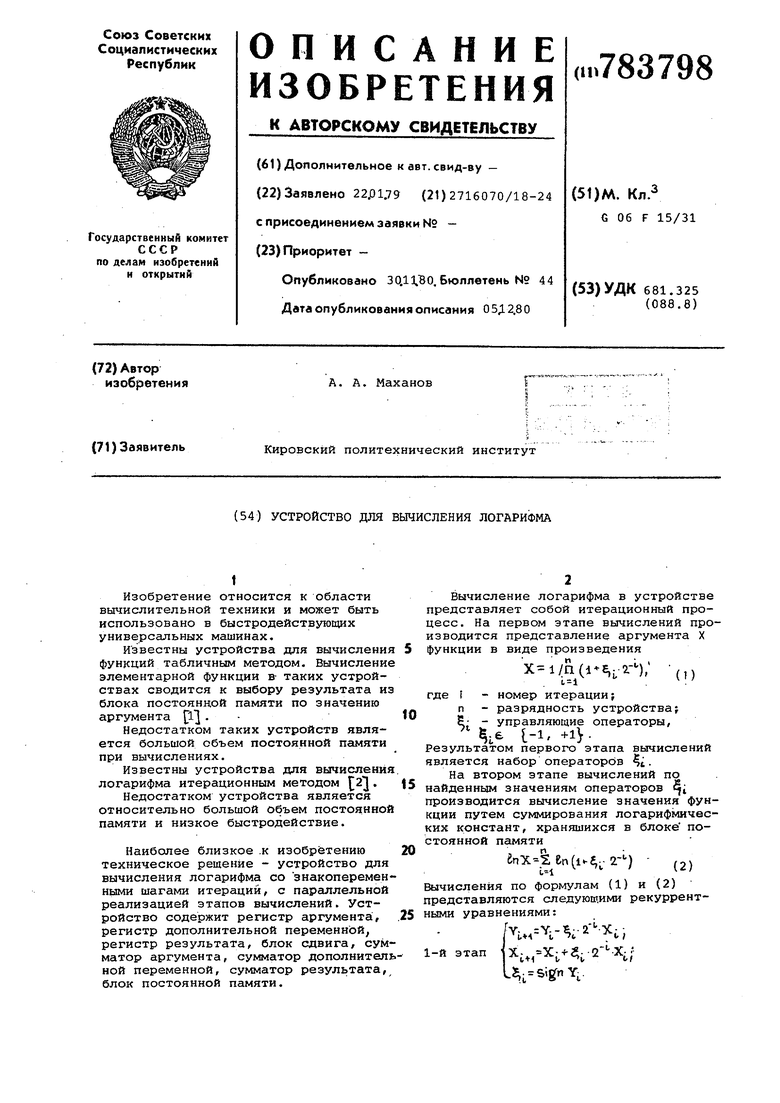

На фиг. 1 изображена.блок-схема предлагаемого устройства для вычисления логарифма для четырехразрядных чисел (п-4); на фиг. 2 - функциональная схема счетчиков положительных единиц; на фиг. 3 - функциональная схема счетчиков отрицательных единиц

Устройство для вычисления логарифма (фиг. 1) содержит регистр 1 аргумента, сумматор 2 результата, регист 3 результата, блок 4 сдвига, блоки 58 постоянной памяти, регистры 9-12 разрядных цифр, сумматоры 13-15 разрядных цифр счетчики 16-18 положителных единиц, счетчики 19-21 отрицательных единиц.

Счетчики 16-18 положительных единиц (фиг. 2) содержат одноразрядные сумматоры 22-27 на три входа комбинационного типа; счетчики 19-21 отрицательных единиц (фиг. 3) содержат одноразрядные сумматоры 28-33 на три входа комбинационного типа.

Устройство работает следующим образом.

Перед началом вычисления аргумент .функции хранится на регистре 1 аргумента. При вычислении, например, натурального логарифма Y fnX при изменении аргумента функции в пределах 0,5 X 1 аргумент в структурном виде представится

+ ,..., .

где oCj, - разрядные цифры аргумента принимающие значение 0,1; п - разрядность.

В начале вычислений аргумент X умножается на 2. Это соответствует сдвигу влево аргумента на один разряд. Умножение на 2 в устройстве осуществляется путем передачи разрядных цифр из регистра 1 аргумента в младшие разряды регистров 9, 10, 11 и 12 со сдвигом влево на один разряд. При этом разрядная цифра записывается в первый разрядный регистр 9, oLj, во второй разрядный регистр 10 и т.п.

Разрядная цифра с для указанног изменениядиапазона аргумента всегда равна 1, поэтому из регистра аргумента не передается и не участвует в дальнейших вычислениях. Далее в устройстве выполняется п однотипных шагов вычислений, в результате чего аргумент функции представляется в виде произведения Х-1/2 В.К; где К; 1+2 -- констенты. Значение функции представляется .--Bn2-ienk, L-1 Процесс выполнения итерации описы вается системой рекуррентных уравнений1-й этап X;,,-X.-i4.--X.tX.-2.2-й этап Y Y-enK -Y -entlt-z) Начальные условия: Х 2 X, Y, -1п2 Результат: Y бпХ ,. В рекуррентных уравнениях индекс i 1, 2; 3,...,w; значения j на каждо 1-м шаге определяется очередной i-и разрядной цифрой преобразуемого аргу мента KI . В процессе выполнения итерации преобразуемый аргумент Х стре мится к 1:Хп 1. На каждой i-и итерации преобразуе мый аргумент Х; хранится на регистра 9-12 в двухразрядном коде в следующе виде: X.-dt(2$,..Jb,(X.j,.,,.)-2-n t...t(V..-2.V(«.,).(2n,-k.)-2 где i определяет номер итерации; V .- старшая цифра кода т-й раз рядной цифры преобразуемого аргумента; - младшая разрядная цифра код т-й разрядной цифры преобра зуемого аргумента. Цифры кода (, и rni принимают знач ние О или 1, Каждая т-я разрядная ци ра преобразуемого аргумента ±( 2 + JbriiL) преставляется со знаком + или - на трехразрядном регистре 912 (два.разряда представляют код раз рядной цифры, один разряд - знак). На каждой i-и итерации производит ся определение значения к; . Значение к; определяется цифрами |Ьц и 2(t-n)i с учетом их знаков &: 0-1+1 О +1 О -1 +1 -1 t 1Ц о +1 -1 +1 0-1 о +1 -i T+rn-Fi-rr+FI+i-i3Fi+1 Здесь приведена зависимость значе ний константа KJ от разрядных цифр jbi; и й/ при выполнении i-и итерации вычислений. Приведенная зависимость обусловлена тем, что на каждой i-и итерации в результате умножения преобразуемого аргумента х;. на константу К{, очередная i -я разрядная цифра + (Xi 2 -vfbv{ ) должна принять нулевое значение. Это обеспечивает последовательное преобразование переменной Х в процессе выполнения итерации в 1 в соответствии с выражением ( 3) . Рассмотрим выполнение первого вычисления логарифма в устройстве в соответствии с уравнением (5). На каждой i-и итерации производятся следующие действия. На управляющие входы блока 4 сдвига подается значение цифр рц и со своими знаками соответственно с выходов i-ro и (i + 1)-го регистров 9-12для.определения значения К 1 + 23 . На информационные входы блока 4 сдвига подается разрядные цифры преобразуемого аргумента со знаками с выходов i-ro,, (i + 1)-го,..., п-го регистров 9-12. Так как в процессе выполнения предыдущих итераций разрядные цифры с 1-го по (i - 1)-и разряд в соответствии с алгоритмом приняли нулевое значение, то их значения на входах сдвига не подаются на i-й итерации. В блоке 4 сдвига производится сдвиг поступавших значений разрядных цифр. При умножении преобразуемого аргумента Х|. на константу Kj 1 + производится умножение каждой т-й разрядной цифры (т i, (i+-l),...,n) на 1 и на +2 с последующим алгебраическим сложением. При умножении кода т-й разрядной цифры на 1 меняется вес цифры 25f цифры не меня «.,.-,)-2--г- 21.,,-2- При умножении кода на ±2 уменьшается вес цифры и jbnii , HU-2 )(t2-) . ..) ..) umt - -Pwi Таким образом, в блоке сдвига производится следующие сдвиги: влево на 1 разряд цифр i.i вправо на (j-1) разрядов цифр вправо на j разрядов цифр . Сдвинутые цифры 1. и и несдвинутые цифры /bmi, с выходов блока сдвига поступают на входы счетчиков 1921 отрицательных единиц в соответствии со своими весами и знаками. При такой организации сдвигов с выходов блока сдвига на входы каждого счетчика положительных или отри- , цательных единиц поступают не более четырех единиц с одинаковыми весами. Каждый счетчик 16-18 положительных единиц (фиг. 2) и счетчик 19-21 отрицательных единиц (фиг. 3) имеет

четыре выхода, соединенных с выходами блока 4 сдвига и один вход, соединённый с выходом последующего счетчика. Все счетчики выполняют одинаковые функции. Каждый р-й счетчик (р 2, 3,.... п) осуществляется преобразование числа единиц с одинаковыми весами, поступающими на его входы, в тоехразрядный код с весами разрядов 2Чг-) , ) . Макс 1мальнре представи-мое число в таком коде 5, что соответствует максимальному числу единиц на вхоДЕл счетчиков.

При поступлении единиц с выходов блока 4 сдвига на входы счетчиков 1621 значения суммы с выходов суммы первых одноразрядных сумматоров 22, 24, 26 и 28, 30, 32 поступают соотвфтственно на первые входы одноразр дных сумматоров 23, 25, 27 и 29, 3J., 33. Значение переносов с выходов переноса указанных первых одноразрядных сумматоров поступают на третьи входы вторых одноразрядных сумматоров предыдущих счетчиков. Значения суммы и переносов с выходов вторых одноразррдных сумматоров 23, 25, 27 поступают на первые входы соотвтствующих cyrviMaTopoB 13-15 разрядных цифр, значрния сумм и переносов с выходов вторых одноразрядных сумматоров 29, 31, 3:3 поступают на вторые входы соответствующих сумматоров 13-15 разрядных цифр.

В сумматорах 13, 14, 15 производится алгебраическое сложение двухразрядных чисел, поступающих с выходов соответствующих счетчиков положительных единиц, с отрицательными двухразрядными числами, поступающими с выходов соответствующих счетчиков отрицательных единиц.

Значение сумм с выходов сумматоров 13, 14,, 15 записывается в регистры 10, 11, 12. Эти суммы представляют новое - значение разрядных цифр преобразуемого аргумента Х и используются при выполнении следующей итерации

После выполнения п итергщий процесс вычисления первого этапа заканчивается.

На втором этапе вычислений коды разрядов преобразованного аргумента с выходов регистров 9-12 подаются со своими знаками на входы соответствующих им блоков 5-8 постоянной памяти. На выходах i-х блоков постоянной памяти формируются соответствующие кодам преобразованного аргумента логарифмическое константы SnKi, Указанные константы с выходов блоков постоянной памяти поступают на входы сумматора 2 результата, где производится алгебраическое сумг ирование. Результат сум1 гирования с выхода сумматора 2 записывается в регистр 3 результата. Содержимое регистра 3 результата представляет результат

вычисления логарифма в предлагаемом устройстве.

Для уменьшения времени выполнения второго .этапа вычислений в предлагаемом устройстве рационально применять в качестве суг/1матора 2 результата матрический сумматор, обеспечивающий одновременное суммирование п + + 1 логарифмических констант.

Выполнение второго этапа вычислений в устройстве может быть совмеще-Ф но во времени с первым этапом вычис-У лений, так как после выполнения очередной i-й итерации на первом этапе значение кодов старших регистров разрядных цифр с 1-го по i-й сформиро.ваны и в дальнейшем не. изме няются. .

Кыстродействие устройства может быть увеличено за счет уменьшения числа выполнения итераций на первом этапе.

В этом случае процесс вычисления логарифма в устройстве заключается R-следующем. Производится выполнение n/2+l итерации первого этапа. Затем на входы сумматора 2 результата постпают константы К (i 1, 2, .,., п/1+2) с выходов соответствующих блоков постоянной памяти. Одновременно на другие входы сумматора результата поступает значение величин с выходов j X (j n/2+2, n/2+3, ,., . , n) регистров разрядных цифр. Эти величины представляются двумя (п/2-1)-разряднми двоичными числами. В сумматоре результата производится суммирование {n/2+l)-разрядных констант К- и двух (n/2-l)-разрядных чисел. Результат суммирования записывается в регистр результата.

В прототипе на каждой итерации производится суммирование п-разряд.ных чисел на п-разрядном сумматоре с распространением переноса через все п разрядов с общим временем вычисления логарифма, выраженное в единицах задержки на элементе, пропорционально nZ-.

Эффективность изобретения заключается в сокращении времени вычисления логарифма за счет распространения переносов при сумг-гаровании на первом этапе только в один соседний слева разряд и одновременного cyMMiipoBaния всех логарифмических констант на сумматоре результата на втором этапе вычислений. Суммарное время вычисления логарифма в предлагаемом устройстве, выраженное в единицах задержки на элементе, пропорционально п.

Формула Р 3обретения

1,Устройство для вычисления логарима, содержащее регистр аргумента, сумматор результата, регистр результата, блок сдвига, блоки постоянной памяти, причем выходы i-х блоков постоянной памяти (i 1, 2,.,,, п, где n - разрядность устройства) подключены к i-M входам сумматора резул тата, выход которого соединен с входом регистра результата, отличающееся тем, что, с целью увеличения быстродействия устройства путем .уменьшения времени вычисления на каждом этапе, в него введены реги стры разрядных цифр, сумматоры разрядных цифр, счетчики положительных единиц, и счетчики отрицательных еди ниц, причем выход регистра аргумента соединен с входами младших разрядов регистров разрядных цифр, выходы i-х регистров разрядных цифр соединены с первыми входами i-х и вторыми входами (i-l)-x блоков постоянной памяти и с i-ми входами блока сдвига, выход блока сдвига соединен с первой группой входов счетчиков положительных и отрицательных единиц, первые выходы 1-х счетчиков положительных единиц соединены с первыми входами i-х сумматоров разрядных цифр, вторые выходы i-х счетчиков положительных единиц соединены с второй группой входов (i-l)-x счетчиков положительных единиц, первые выходы i-х счетчиков отрицательных единиц соединены с вторыми входами i-X сумматоров разрядных .цифр, вторые выходы i-х счетчиков от рицательных единиц соединены с второй группой (i-l)-x счетчиков отрицательных, единиц, выходы сумматоров разрядных цифр соединены с входами соответствующих регистров разрядных цифр. 2. Устройство по п. 1, отличающееся тем, что каждый счетчик положительных и каждый счетчик отрицательных единиц содержит первый и второй одноразрядные сумматоры, причем первый, второй и третий входы первого одноразрядного сумматора и первый вход второго одноразрядного cy 1мaтopa соединерш с первым входом счетчика, выходы .суммы и переноса второго одноразрядного сумматора соединены с первым выходом счетчика, выход суммы первого одноразрядного сумматора соединен с вторым входом второго одноразрядного сумматора, выход переноса первого одноразрядного сумматора соединен с вторым выходом счетчика, третий вход второго одноразрядного сумматора соединен с вторым входом счетчика. Источники информации, принятые во внимание при экспертизе 1,Оранский А. М., Рейхенберг А.Л. Повышение эффективности вычислений использованием табличных предпроцессов. В кн.: Теория и -применение математических машин, Минск, Изд-во БГУ . им. В. И. Ленина, 1972, с. 148-159. 2.Байков В. Д., Смолов В. Б. Аппаратурная реализация элементарных функций в ЦВМ, Л., ЛГУ, 1975, с. 376 (прототип). -2- 2- пг-44: 7Г Г WfH Lqq:|:.

-г

2 2 21

-If

2

2 Фаг. 2 2- 18IL г Ljppf |J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифма | 1984 |

|

SU1262489A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

.г-t .2-

.4-4--, i4-t--i ,4-t

19 1LT R Т т 1 Гг лL

-2- -2л

-if

-2

Авторы

Даты

1980-11-30—Публикация

1979-01-22—Подача