11

Изобретение относится к вычисли- тельной технике и предназначено для решения интегральных уравнений Фред- гольма второго рода.

Цель изобретения - повьшение быст родействия устройства.

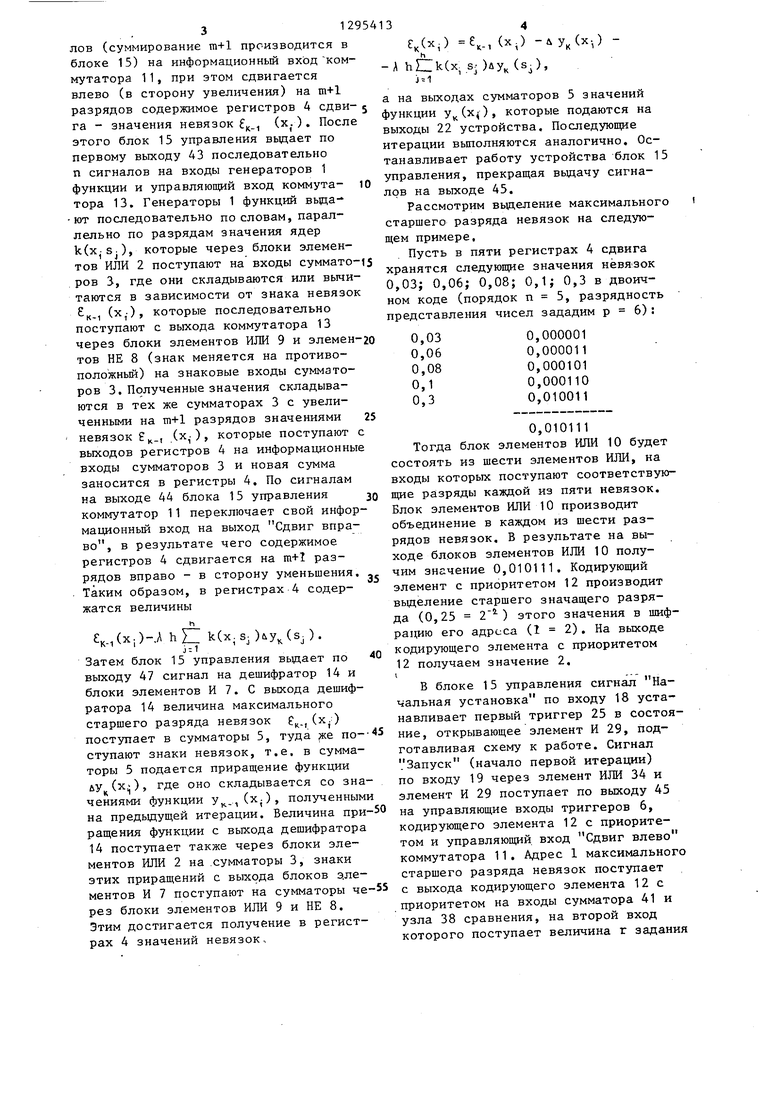

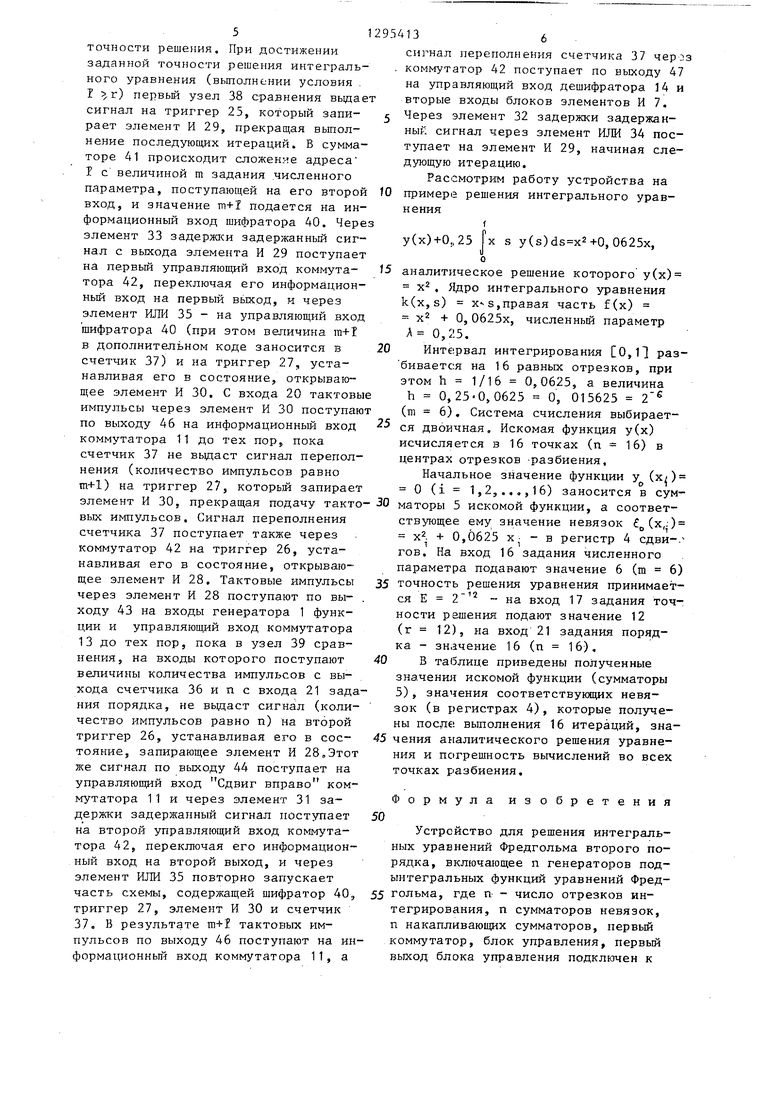

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема блока управления,

Устройство содержит п генераторов подынтегральных функций уравнений Фредгольма 1, п блоков элементов ИЛИ 2 первой группы, п сумматоров невязок 3, п сдвигающих регистров 4, п накапливающих сумматоров 5, п триггеров 6, п блоков элементов И 7, п блоков элементов НЕ 8, р блоков эле- . ментов ИЛИ 9 второй группы, п блоков элементов ИЛИ 10 третьей группы, пер вьй коммутатор 11, кодирующий элемент 12 (пгифратор приоритов) с приоритетом, второй коммутатор 13, дешифратор 14, блок 15 управления,вход 16 численного параметра, вход 17 задания точности, вход 18 начальной установки, вход 19 запуска, вход 20 тактовых импульсов, вход 21 задания порядка, п выходов 22 устройства, вход 23 начального значения невязки, вход 24 начального значения итерации, первый 25, второй 26 и третий 27 триггеры, первый 28, второй 29 и третий 30 элементы И, первый 31, вто рой 32 и третий 33 элементы задерж

ки, -первый 34 и второй 35 элементы

ИЛИ, первьш 36 и второй 37 счетчики, , первый 38 и второй 39 узлы сравнения, шифратор 40, сумматор 41, коммутатор 42, первый 43, второй 44, третий 45, четвертый 46, и пятый 47 выходы блока управленкя, седьмой вход 48 блока управления,

В устройстве реализуется модифицированный метод последовательных приближений, согласно которому прира- щение искомой функции вычисляется по формуле

а У,

К+1

Cx.)

xsign(x.) ,

Приращение искомой функции на каждой итерации во всех точках имеет одинаковую величину, равную максимальному старшему разряду (обозна чен его адрес через 1) невязок, по

132

лученных на предьщущей итерации, а знак приращения определяется знаком невязки в той же точке, т.е. ь.Укч.1 (xj) q (x; ) .

Итерационный процесс решения ин- техрального уравнения заканчивается при выполнении условия

-г

Uy,(x.)l q Е,

15

0

25

30

35

0

50

55

где Е - заданная точность решения интегрального уравнения, Представляя Е q J получаем условие окончания итерационного процесса

1 /г ,

Устройство работает следующ1 м образом.

Перед началом работы начальное приблшкение искомой функции )0 заносится в сумматоры искомой функции 5, соответствующее ему значение невязок fo(x,.) f (х.-)/f (х,- ) правая часть интегрального уравнения (известная функция) - в регистры 4, На вход 16 задания численного параметра подается значение т, определяемое из соотношения Ah , на вход 17 задания точности решения подается значение г, на вход 20 тактовых импульсов поступают тактовые импульсы, на вход, 21 Задания порядка подается значение порядка П-,

Затем на вход 18 начальной установки подается сигнал Начальная установка, а на вход 19 запуска подается сигнал Запуск, после чего начинается работа устройства.

При вьтолнении очередной k-й итерации по сигналу на выходе 45 блока 15 управления происходит следующее: шифратор 12 приоритета выделяет адрес 1 максимального старшего разряда невязок, вычисленных на (k-1)-й итерации и поступающих с регистров 4 сдвига на элемент 12 через блок элементов ИЛИ lOj который поступает на информационный вход дешифратора 14 и вход 48 блока 15 управления; триггеры 6 вьщелягот знаки тех же невязок, которые поступают на группу коммутатора 13 знаков невязок и на информа- ционны€; входы блока элементов И 7j коммутатор 11 переключает свой информационный вход на выход Сдвиг влево.

Затем блок 15 управления вьщает по выходу 46 последовательно ш+1 сигна312954134

лов (суммирование m+1 производится в к-i i У (х-,) - блоке 15) на информационньш вход ком- А hlllkCx s/)йу (sj), Ы

мутатора 11, при этом сдвигается влево (в сторону увеличения) на m+1 разрядов содержимое регистров 4 сдвига - значения невязок .. , (х. ) , После

л,-1 1

этого блок 15 управления выдает по первому выходу 43 последовательно п сигналов на входы генераторов 1 функции и управляющий вход коммута- тора 13, Генераторы 1 функций ньща- ют последовательно по словам, параллельно по разрядам значения ядер k(.), которые через блоки элементов ИЛИ 2 поступают на входы сумматоров 3, где они складываются или вычитаются в зависимости от знака невязок к-1 () которые последовательно поступают с выхода коммутатора 13 через блоки элементов ИЛИ 9 и элементов НЕ 8 (знак меняется на противо- положньш) на знаковые входы сумматоров 3. Полученные значения складываются в тех же сумматорах 3 с увеличенными на тп+1 разрядов значениями невязок е, .(,-) , которые поступают с выходов регистров 4 на информационные входы сумматоров 3 и новая сумма заносится в регистры 4. По сигналам на выходе 44 блока 15 управления коммутатор 11 переключает свой информационный вход на выход Сдвиг вправо

в результате чего содержимое

регистров 4 сдвигается на m+1 разрядов вправо - в сторону уменьшения. Таким образом, в регистрах 4 содержатся величины

Тогда блок элементов ИЛИ 10 будет состоять из шести элементов ИЛИ, на входы которых поступают соответствую щие разряды каждой из пяти невязок, Блок элементов ИЛИ 10 производит объединение в каждом из шести разрядов невязок, В результате на выходе блоков элементов ИЛИ 10 получим значение 0,010111, Кодирующий элемент с приоритетом 12 производит выделение старшего значащего разряда (0,25 2 -} этого значения в шиф рацию его адреса (1 2), На выходе кодирующего элемента с приоритетом 12 получаем значение 2,

к-Дх-,)- h IZ k(x. s. )y. (s; ) ,

J-1 Затем блок 15 управления вьщает по 0

выходу 47 сигнал на дешифратор 14 и блоки элементов И 7, С выхода дешифратора 14 величина максимального старшего разряда невязок f., (х.О поступает в сумматоры 5, туда ;же по-- ступают знаки невязок, т,е. в сумматоры 5 подается приращение функции ЬУ (х,;) где оно складывается со значениями функции у., (Xj), полученными на предыдущей итерации. Величина при-50 на управляющие входы триггеров 6, ращения функции с выхода дешифратора кодирующего элемента 12 с приорите- 14 поступает также через блоки элементов ИЛИ 2 на .сумматоры 3, знаки этих приращений с выхода блоков э.ле- ментов И 7 поступают на сумматоры че-55 с выхода кодирующего элемента 12с рез блоки элементов ИЛИ 9 и НЕ 8, приоритетом на входы сумматора 41 и Этим достигается получение в регистрах 4 значений невязок.

В блоке 15 управления сигнал Начальная установка по входу 18 устанавливает первый триггер 25 в состоя ние, открывающее элемент И 29, подготавливая схему к работе. Сигнал Запуск (начало первой итерации) по входу 19 через элемент ИЛИ 34 и элемент И 29 поступает по выходу 45

том и yпpaвляюшJ й вход Сдвиг влево коммутатора 11, Адрес 1 максимальног старшего разряда невязок поступает

узла 38 сравнения, на второй вход которого поступает величина г задани

к-i i У (х-,) -

- А hlllkCx s/)йу (sj), Ы

а на выходах сумматоров 5 значений функции у(х(), которые подаются на выходы 22 устройства. Последующие итерации выполняются аналогично. Останавливает работу устройства блок 15 управления, прекращая выдачу сигналов на выходе 45,

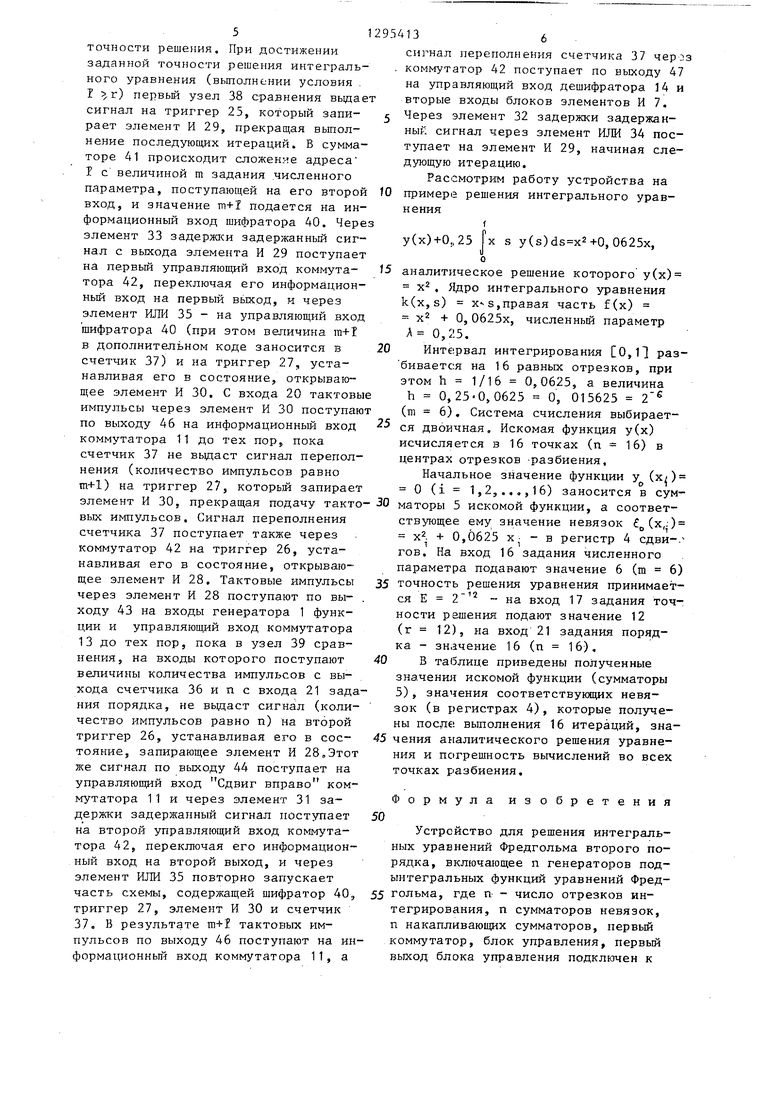

Рассмотрим вьиеление максимального старшего разряда невязок на следующем примере.

Пусть в пяти регистрах 4 сдвига хранятся следующие значения невязок 0,03; 0,06; 0,08; 0,1; 0,3 в двоичном коде (порядок п 5, разрядность представления чисел зададим р 6):

0,000001 0,000011 0,000101 0,000110 0,010011

0,010111

Тогда блок элементов ИЛИ 10 будет состоять из шести элементов ИЛИ, на входы которых поступают соответствующие разряды каждой из пяти невязок, Блок элементов ИЛИ 10 производит объединение в каждом из шести разрядов невязок, В результате на выходе блоков элементов ИЛИ 10 получим значение 0,010111, Кодирующий элемент с приоритетом 12 производит выделение старшего значащего разряда (0,25 2 -} этого значения в шиф- рацию его адреса (1 2), На выходе кодирующего элемента с приоритетом 12 получаем значение 2,

на управляющие входы триггеров 6, кодирующего элемента 12 с приорите- с выхода кодирующего элемента 12с приоритетом на входы сумматора 41 и

на управляющие входы триггеров 6, кодирующего элемента 12 с приорите- с выхода кодирующего элемента 12с приоритетом на входы сумматора 41 и

В блоке 15 управления сигнал Начальная установка по входу 18 устанавливает первый триггер 25 в состояние, открывающее элемент И 29, подготавливая схему к работе. Сигнал Запуск (начало первой итерации) по входу 19 через элемент ИЛИ 34 и элемент И 29 поступает по выходу 45

на управляющие входы триггеров 6, кодирующего элемента 12 с приорите- с выхода кодирующего элемента 12с приоритетом на входы сумматора 41 и

том и yпpaвляюшJ й вход Сдвиг влево коммутатора 11, Адрес 1 максимального старшего разряда невязок поступает

на управляющие входы триггеров 6, кодирующего элемента 12 с приорите- с выхода кодирующего элемента 12с приоритетом на входы сумматора 41 и

узла 38 сравнения, на второй вход которого поступает величина г задания

точности решения. При достижении заданной точности решения интегрального уравнения (выполнении условия . I .г) первьй узел 38 сравнения выдает сигнал на триггер 25, который запирает элемент И 29, прекращая выполнение последуюпщх итераций. В сумматоре 41 происходит сложение адреса Г с величиной m задания .численного параметра, поступающей на его второй вход, и значение т+1 подается на информационный вход шифратора 40. Через

элемент 33 задержки задержанный сиг- у(х)+0,, 25 х s y(s), 0625х,

нал с выхода элемента И 29 поступает на первый управляющий вход коммутатора 42, переключая его информационный вход на первый выход, и через элемент ИЛИ 35 - на управляющий вход шифратора 40 (при этом величина m+I в дополнительном коде заносится в счетчик 37) и на триггер 27, устанавливая его в состояние, открывающее элемент И 30. С входа 20 тактовые

5 аналитическое решение которого у(х х, Ядро интегрального уравнения k(x,s) х-S,правая часть f(x) х +0,0625х, численный параметр А 0,25.

20 Интервал интегрирования 0,11 р

бивается на 16 равных отрезков, пр

этом h 1/16 0,0625, а величина

h 0,25-0,0625 О, 015625 2

(т 6). Система счисления выбираетимпульсы через элемент И 30 поступают

по выходу 46 на информационный вход ся двоичная. Искомая функция у(х)

коммутатора 11 до тех пор, покаисчисляется в 16 точках (п 16) в

счетчик 37 не вьщаст сигнал перепол-центрах отрезков -разбиения,

нения (количество импульсов равно Начальное значение функции у (х/)

т+1) на триггер 27, который запирает О (i 1,2., ..,,16) заносится в сумэлемент И 30, прекращая подачу такто- 30наторы 5 искомой функции, а соответвых импульсов. Сигнал переполнения счетчика 37 поступает также через коммутатор 42 на триггер 26, устанавливая его в состояние, открывающее элемент И 28, Тактовые импульсы через элемент И 28 поступают по вы- ходу 43 на входы генератора 1 функции и yпpaвляюш й вход коммутатора 13 до тех пор, пока в узел 39 сравнения, на входы которого поступают величины количества импульсов с выхода счетчика 36 и п с входа 21 задания порядка, не вьщаст сигнал (количество импульсов равно п) на второй триггер 26, устанавливая его в состояние, запирающее элемент И 28„Этот же сигнал по выходу 44 поступает на управляющий вход Сдвиг вправо коммутатора 11 и через элемент 31 задержки задержанный сигнал поступает на второй управляющий вход коммутатора 42, переключая его информационный вход на второй выход, и через элемент ИЛИ 35 повторно запускает часть схемы, содержащей шифратор 40, триггер 27, элемент И 30 и счетчик 37. В результате m+J тактовых импульсов по выходу 46 поступают на ин формационньй вход коммутатора 11, а

т

12954136

сигнал переполнения счетчика 37 чероз . коммутатор 42 поступает по выходу 47 на управляющий вход дешифратора 14 и вторые входы блоков элементов И 7. 5 Через элемент 32 задержки задержанный сигнал через элемент ИЛИ 34 поступает на элемент И 29, начиная следующую итерацию.

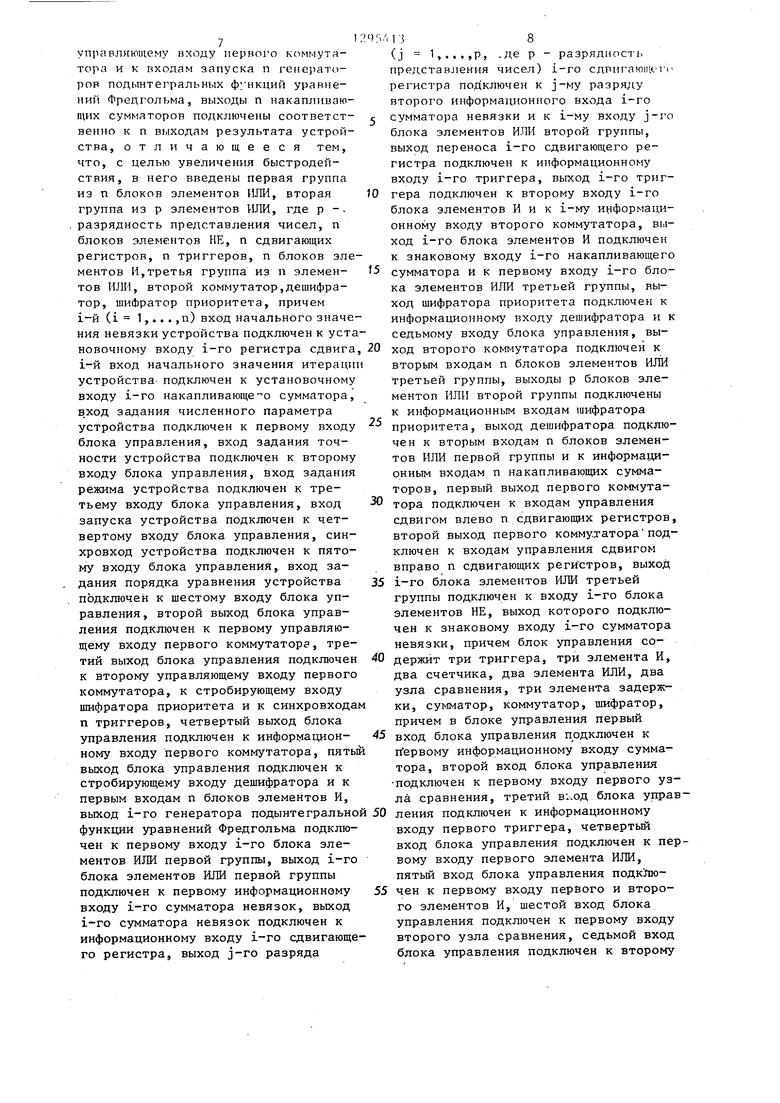

Рассмотрим работу устройства на 10 примере решения интегрального уравнения

5 аналитическое решение которого у(х) х, Ядро интегрального уравнения k(x,s) х-S,правая часть f(x) х +0,0625х, численный параметр А 0,25.

20 Интервал интегрирования 0,11 раз бивается на 16 равных отрезков, при

этом h 1/16 0,0625, а величина

h 0,25-0,0625 О, 015625 2

(т 6). Система счисления выбирает ся двоичная. Искомая функция у(х)

ствующее ему значение невязок f.(x,:) х. + 0,0625 х- - в регистр 4 сдви-. гов. На вход 16 задания численного параметра подавают значение 6 (т 6)

35 точность решения уравнения принимается Е - на вход 17 задания точности решения подают значение 12 (г 12), на вход 21 задания порядка - значение 16 (п 16).

40 В таблице приведены полученные значения искомой функции (сумматоры 5), значения соответствующих невязок (в регистрах 4), которые получены nocfie. выполнения 16 итераций, зна-

45 чения аналитического решения уравнения и погрешность вычислений во всех точках разбиения.

ормула изобретения

Устройство для решения интегральных уравнений Фредгольма второго порядка, включающее п генераторов подынтегральных функций уравнений Фред- 55 гольма, где п - число отрезков интегрирования, п сумматоров невязок, п накапливающих сумматоров, первьш коммутатор, блок управления, первый выход блока управления подключен к

управляющему входу первого коммутатора и к входам запуска п генераторов подынтегральных функций уравнений Фредгол ма, выходы п накапливающих сумматоров подключены соответст- венно к п В1)1ходам результата ycTpovl- ства, отличающееся тем, что, с целью увеличения быстродействия, в него введены первая группа из п блоков элементов ИЛИ, вторая группа из р элементов ИЛИ, где р -- разрядность представления чисел, п блоков элементов НЕ, п сдвигающих регистров, п триггеров, п блоков элементов И,третья группа из п элемен- тон ИЛИ, второй коммутатор,дешифратор, шифратор приоритета, причем i-й (i 1,.. . ,п) вход начального значения невязки устройства подключен к установочному входу i-ro регистра сдвига i-й вход начального значения итераци устройства подключен к установочному входу i-ro накапливающе- о сумматора, вход задания численного параметра устройства подключен к первому входу блока управления, вход задания точности устройства подключен к второму входу блока управления, вход задания режима устройства подключен к третьему входу блока управления, вход запуска устройства подключен к четвертому входу блока управления, син- хровход устройства подключен к пятому входу блока управления, вход задания порядка уравнения устройства подключен к шестому входу блока управления , второй выход блока управления подключен к первому управляющему входу первого коммутатора, третий выход блока управления подключен к второму управляющему входу первого коммутатора, к стробирующему входу шифратора приоритета и к синхровхода п триггеров, четвертый выход блока управления подключен к информацион- ному входу первого коммутатора, пяты выход блока управления подключен к стробирующему входу дешифратора и к первым входам п блоков элементов И, выход i-ro генератора подынтегрально функции уравнений Фредгольма подключен к первому входу i-ro блока элементов ИЛИ первой группы, выход i-ro блока элементов ИЛИ первой группы подключен к первому информационному входу i-ro сумматора невязок, выход i-ro сумматора невязок подключен к информационному входу i-ro сдвигающего регистра, выход j-ro разряда

(J 1,...,р, -Де р - разрядность представления чисел) 1-го сдвигающс-Г регистра подключен к j-му разряду второго информационного входа i-ro сумматора невязки и к i-му входу блока элементов ИЛИ второй группы, выход переноса 1-го сдвигающего регистра подключен к информационному входу i-ro триггера, выход i-ro триггера подключен к второму входу i-ro блока элементов И и к i-му информационному входу второго коммутатора, ВГ)- ход i-ro блока элементов И подключен к знаковому входу i-ro накапливающего сумматора и к первому входу i-ro блока элементов ИЛИ третьей группы, выход шифратора приоритета подключен к информационному входу дешифратора и к седьмому входу блока управления, выход второго коммутатора подключен к вторым входам п блоков элементов ИЛИ третьей группы, выходы р блоков элементов ИЛИ второй группы подключены к информационным входам 1иифратора приоритета, выход дешифратора подключен к вторым входам п блоков элементов ИЛИ первой группы и к информационным входам п накапливающих сумматоров, первый выход первого коммутатора подключен к входам управления сдвигом влево п сдвигающих регистров, второй выход первого коммутатора подключен к входам управления сдвигом вправо п сдвигающих реги стров, выход i-ro блока элементов ИЛИ третьей группы подключен к входу i-ro блока элементов НЕ, выход которого подключен к знаковому входу i-ro сумматора невязки, причем блок управления содержит три триггера, три элемента И, два счетчика, два элемента ИЛИ, два узла сравнения, три элемента задержки, сумматор, коммутатор, шифратор, причем в блоке управления первый вход блока управления подключен к п ервому информационному входу сумматора, второй вход блока управления подключен к первому входу первого узла сравнения, третий в:.од блока управления подключен к информационному входу первого триггера, четвертый вход блока управления подключен к первому входу первого элемента ИЛИ, пятый вход блока управления подк лю- чен к первому входу первого и второго элементов И, шестой вход блока управления подключен к первому входу второго узла сравнения, седьмой вход блока управления подключен к второму

912

информационному входу сумматора и к второму входу первого узла сравнения, выход первого элемента И подключен к первому, выходу блока управления и к информационному входу первого счет- чика, выход которого подключен к второму входу второго узла сравнения, второй вход первого элемента И под ключен к выходу второго триггера, выход второго узла сравнения подключен к второму выходу блока управления, к синхровходу второго триггера и к входу первого элемента задержки, выход которого подключен к первому входу второго элемента ИЛИ и к первому уп- равляющему входу коммутатора, второй вход первого элемента ИЛИ подключен к выходу второго элемента задержки, первый и второй входы второго элемента И подключены соответственно к выходам перво го элемента ИЛИ и первого триггера, выход второго элемента И подключен к третьему выходу блока управления и к входу третьего элемента

задержки, выход которого подключен к

5 0

5

1310

второму входу второго элемента ИЛИ и к второму управляющему входу коммутатора, выход второго элемента ИЛИ подключен к информационному входу третьего триггера и к стробирующему входу шифратора, выход третьего триггера подключен к второму входу третьего элемента И, выход которого подключен к четвертому выходу блока управления и к информационному входу второго счетчика, выход сумматора подключен к информационному входу шифратора, выход которого подключен к установочному входу второго счетчика, В1э1ход которого подключен к синхровходу третьего триггера и к информа:ционному входу коммутатора, первый выход коммутатора подключен к информационному входу второго триггера, второй выход коммутатора подключен к пятому выходу блока управления и к входу второго элемента задержки, выход первого узла сравнения подключен к синхровходу первого триггера.

150,90625 -0,276-10 0,821655 0,821289 -0,000366

160,96875 -О,539-10 0,938843 0,938477 -0,000366

Фиг.2

Редактор С.Патрушева

Составитель В.Смирнов Техред И.Попович

Заказ 619/56Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Устройство для решения интегральных уравнений Фредгольма второго рода | 1988 |

|

SU1617438A1 |

| Устройство для решения интеграль-НыХ уРАВНЕНий | 1979 |

|

SU817726A1 |

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1979 |

|

SU830396A1 |

| Устройство для решения систем линйныхАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU824217A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

Изобретение относится к области вычислительной техники и предназначено для решения интегральных уравне НИИ Фредгольма второго порядка. Цель изобретения - увеличение быстродействия. Поставленная цель достигается тем, что устройство содержит п генераторов 1 подынтегральных функций уравнений Фредгольма, где п - число отрезков интегрирования, п сумматоров 3 невязок, п накапливаюЕцнх сумматоров 3, первьш коммутатор 11, блок 15 управления, п блоков элемен тов ИЛИ 2 первой группы, п блоков элементов НЕ 8, р блоков элементов ИЛИ 10 второй группы, где р - разряд- ность представления чисел в устройстве, п сдвигаюп щс регистров 4, п : триггеров 6, п блоков элементов И 7, п блоков элементов ИЛИ 9 третьей группы, второй коммутатор 13, дешифратор 14, шифратор приоритета 12. Увеличение быстродействия достигается за счет аппаратной реализации итерационного процесса численного решения интегральных уравнений Фредгольма второго рода. 2. ил. с € SNS О© сд оэ Фи$.1

| Верлань А.Ф | |||

| Методы решения интегральных уравнений на аналоговых вычислительных машинах | |||

| Киев, 1972, с | |||

| Вага для выталкивания костылей из шпал | 1920 |

|

SU161A1 |

| Устройство для решения интегральных уравнений | 1978 |

|

SU687452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-15—Подача