00 00 Сл) 00

NO

ся

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отслеживания контуров двумерных объектов | 1986 |

|

SU1314353A1 |

| Микропрограммный процессор | 1978 |

|

SU744587A1 |

| Устройство для отслеживания контуров двумерных объектов | 1991 |

|

SU1827676A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2550555C1 |

| Процессор | 1984 |

|

SU1247884A1 |

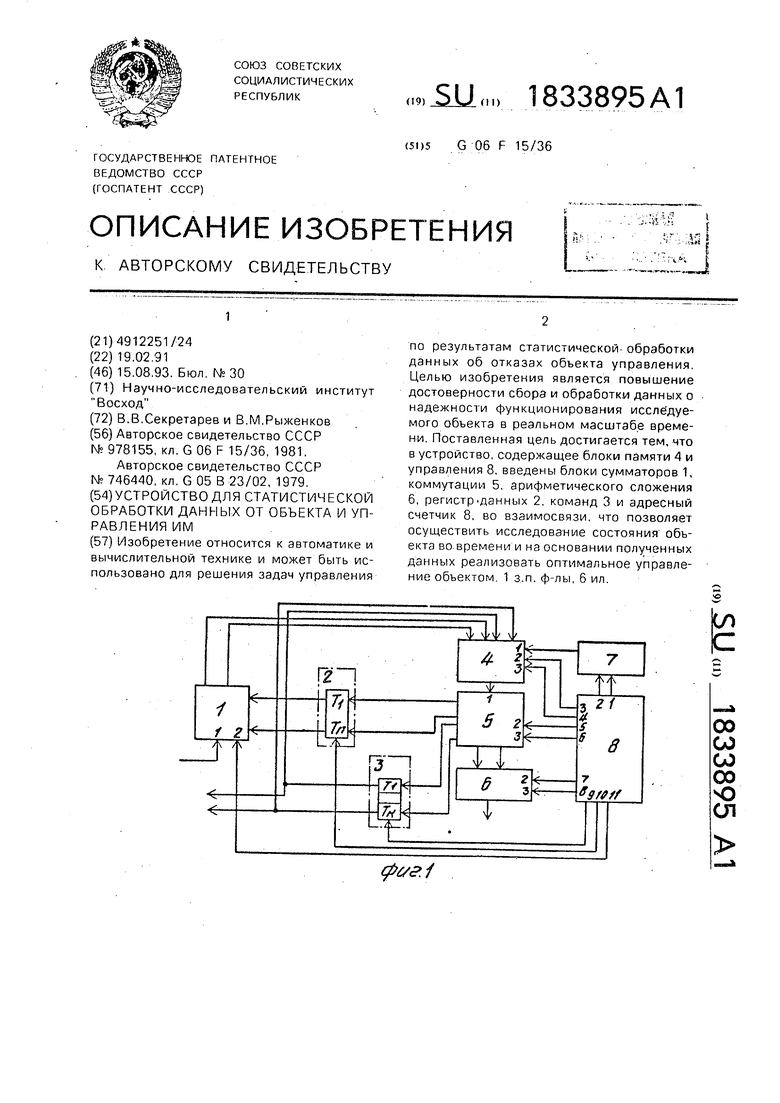

Изобретение относится к автоматике и вычислительной технике и может быть использовано для решения задач управления по результатам статистической- обработки данных об отказах обьекта управления. Целью изобретения является повышение достоверности сбора и обработки данных о надежности функционирования исследуемого объекта в реальном масштабе времени. Поставленная цель достигается тем, что в устройство, содержащее блоки памяти 4 и управления 8, введены блоки сумматоров 1, коммутации 5. арифметического сложения 6, регистр.данных 2, команд 3 и адресный счетчик 8, во взаимосвязи, что позволяет осуществить исследование состояния обьекта во.времени и на основании полученных данных реализовать оптимальное управление объектом. 1 з..п. ф-лы, 6 ил.

(р&г.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для решения задач управлений по результатам статистической обработки данных об отказах объекта управления,

Цель изобретения - повышение достоверности сбора и обработки данных о надежности функционирования исследуемого объекта в реальном масштабе времени.

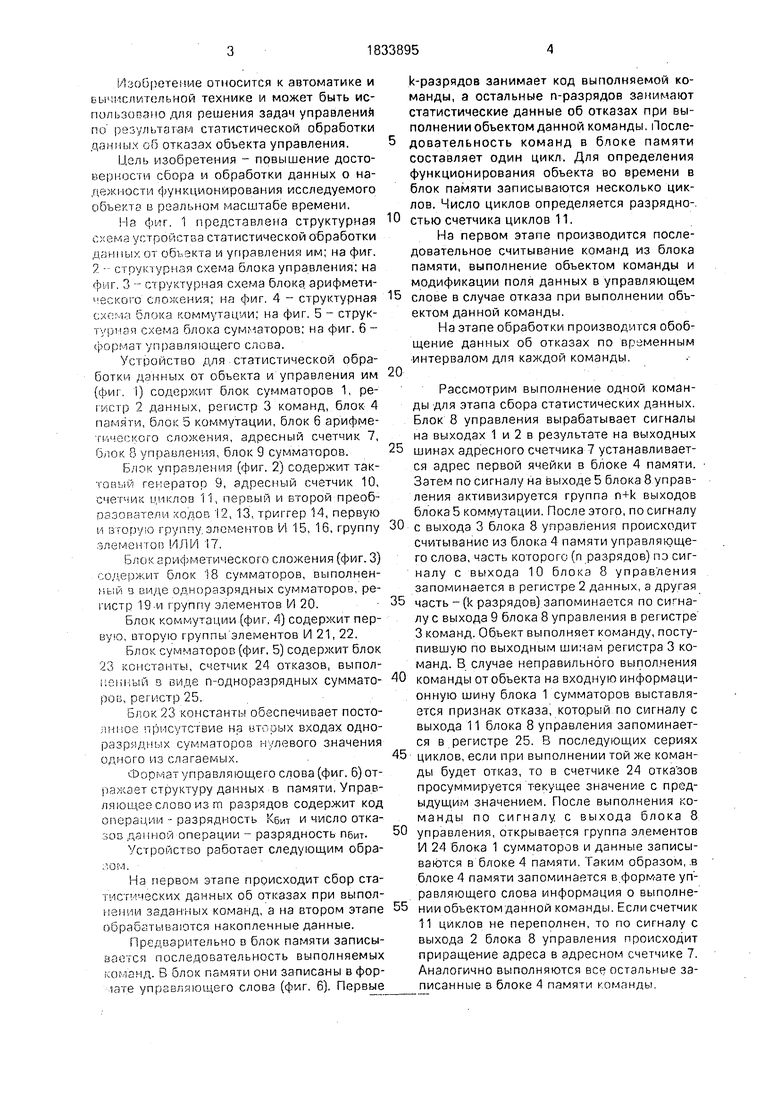

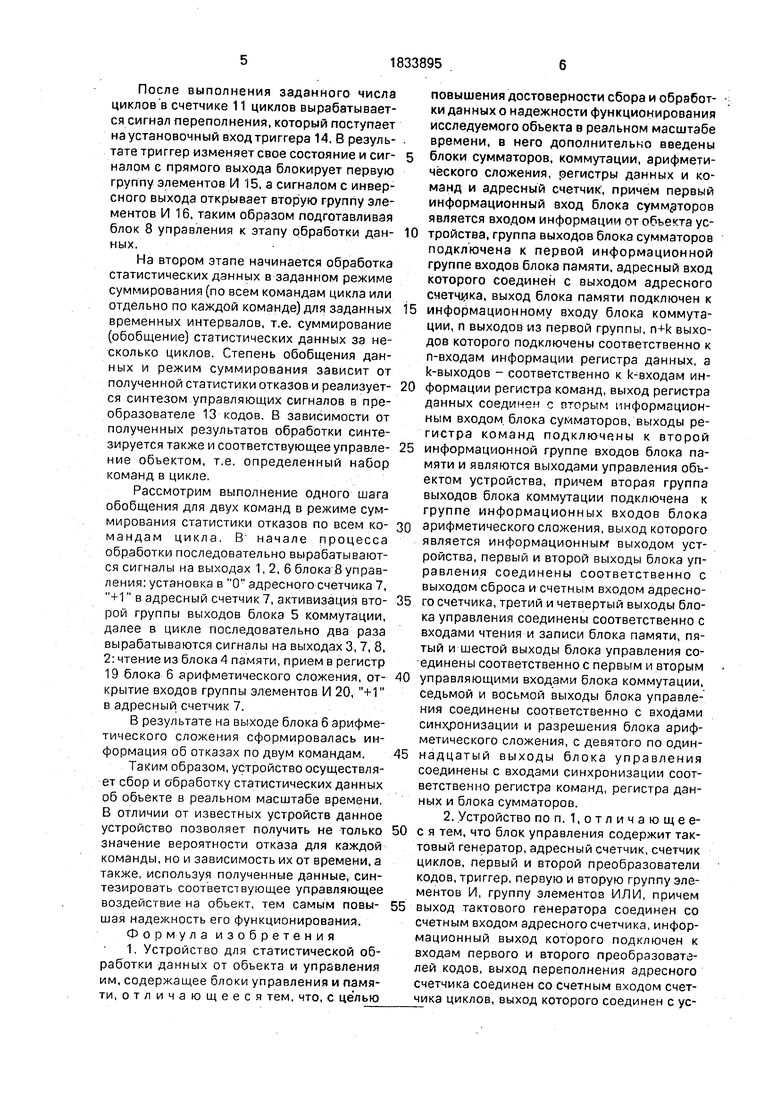

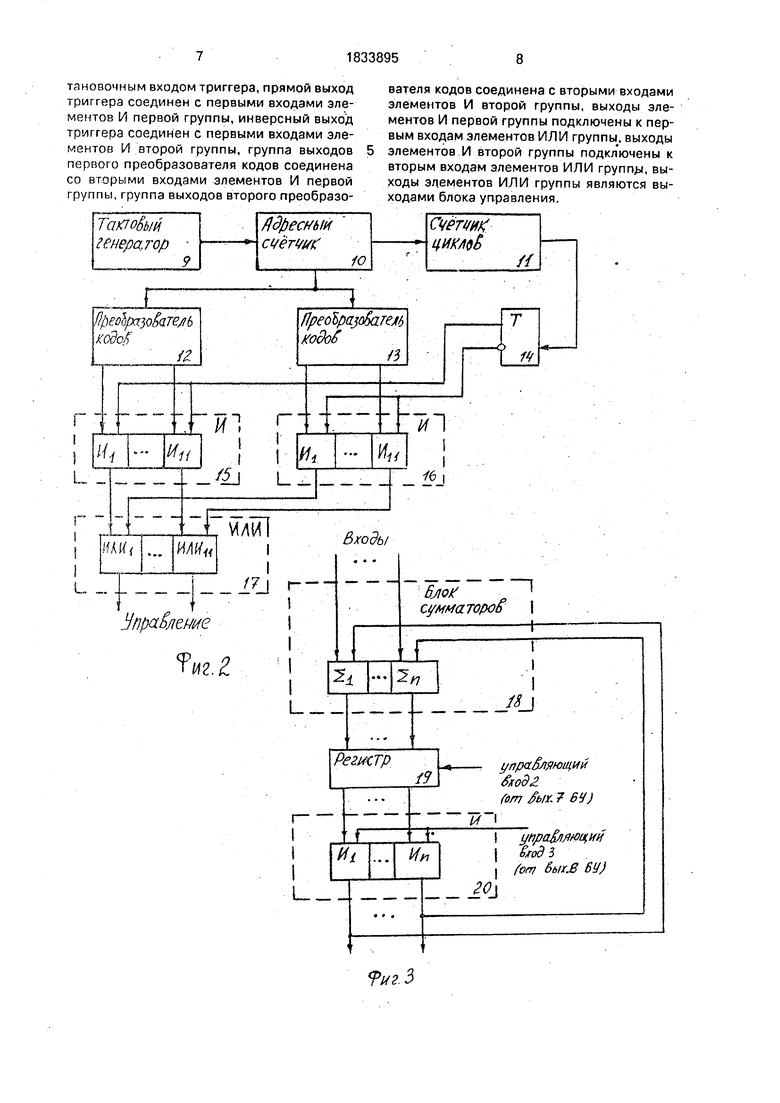

На фиг. 1 представлена структурная схема устройства статистической обработки данных от объекта и управления им; на фиг. 2 -- структурная схема блока управления; на фиг. 3 - структурная схема блока, арифмети- ческого сложения; на фиг. 4 - структурная схпма блока коммутации; на фиг, 5 - структурная схема блока сумматоров; на фиг. 6 - формат управляющего слова.

Устройство для статистической обработки данных от объекта и управления им (фиг. I) содержит блок сумматоров 1, регистр 2 данных, регистр 3 команд, блок 4 памяти, блок 5 коммутации, блок 6 арифметического сложения, адресный счетчик 7, блок 8 управления, блок 9 сумматоров.

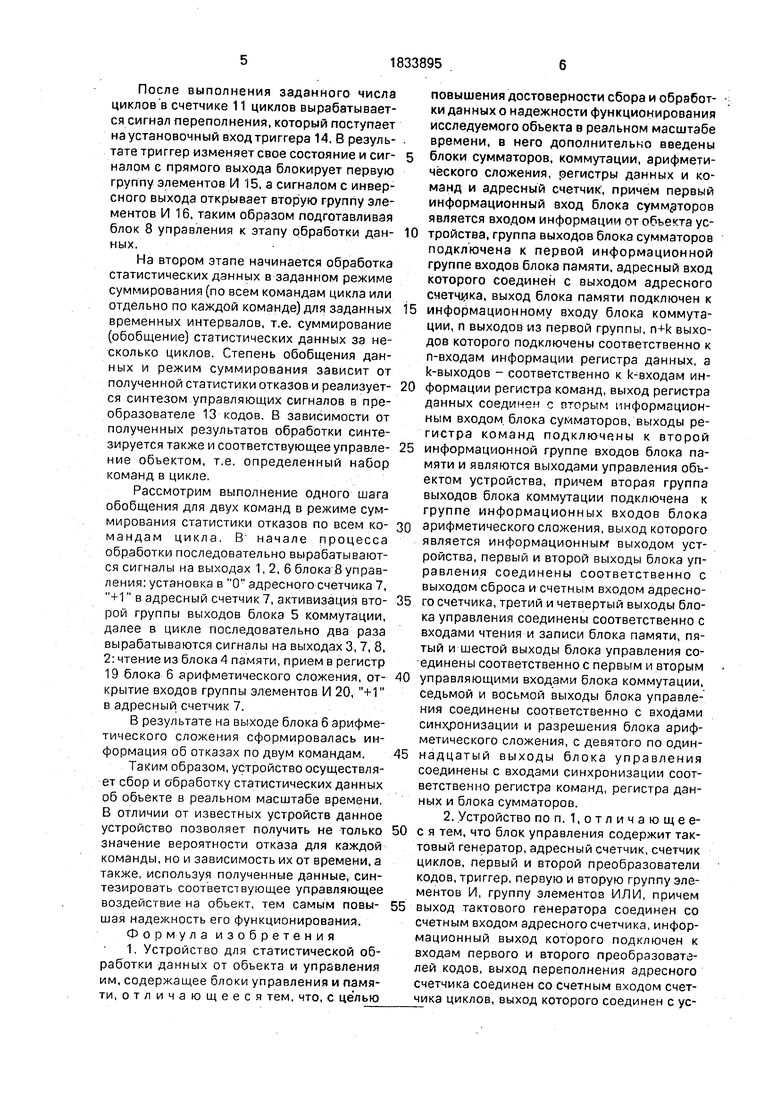

Блок управления (фиг. 2) содержит тактовый генератор 9, адресный счетчик 10, счетчик циклов 11, первый и второй преобразователи кодов 12, 13, триггер 14, первую и вторую группу, элементов И 15, 16, группу .элементов ИЛИ 17.

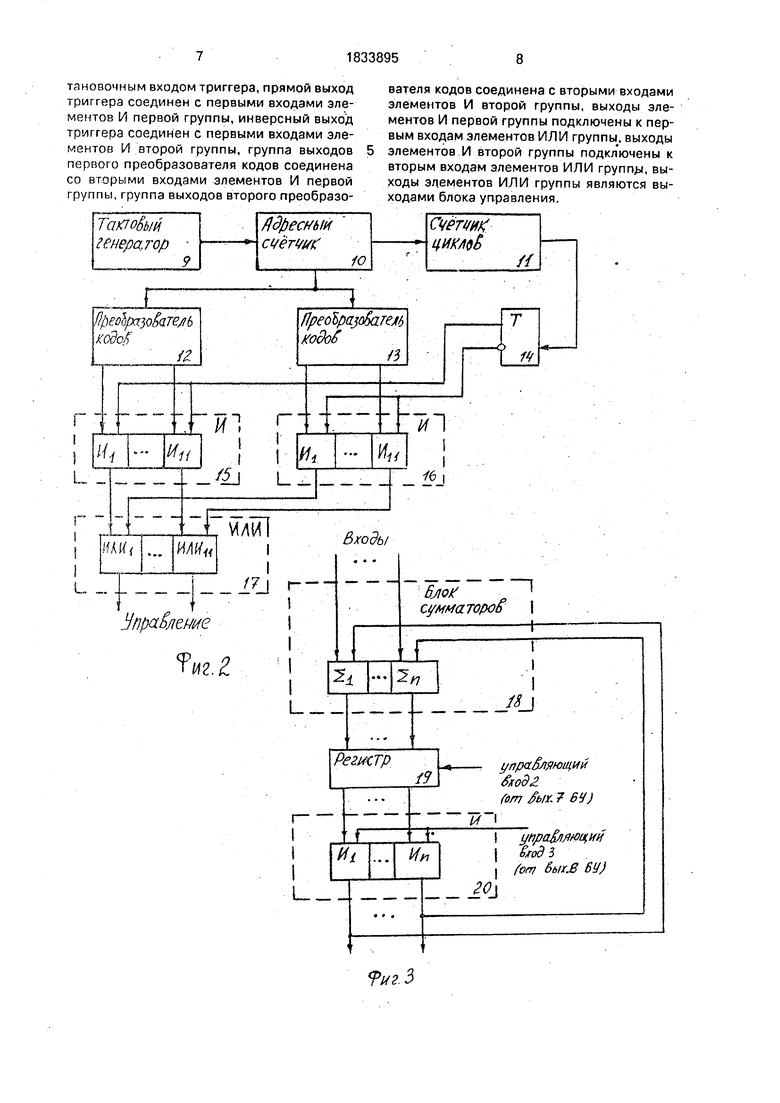

Блок арифметического сложения (фиг. 3) содержит блок 18 сумматоров, выполненный в виде одноразрядных сумматоров, регистр 19-и группу элементов И 20.

Блок коммутации (фиг, 4) содержит первую, вторую группы элементов И 21, 22.

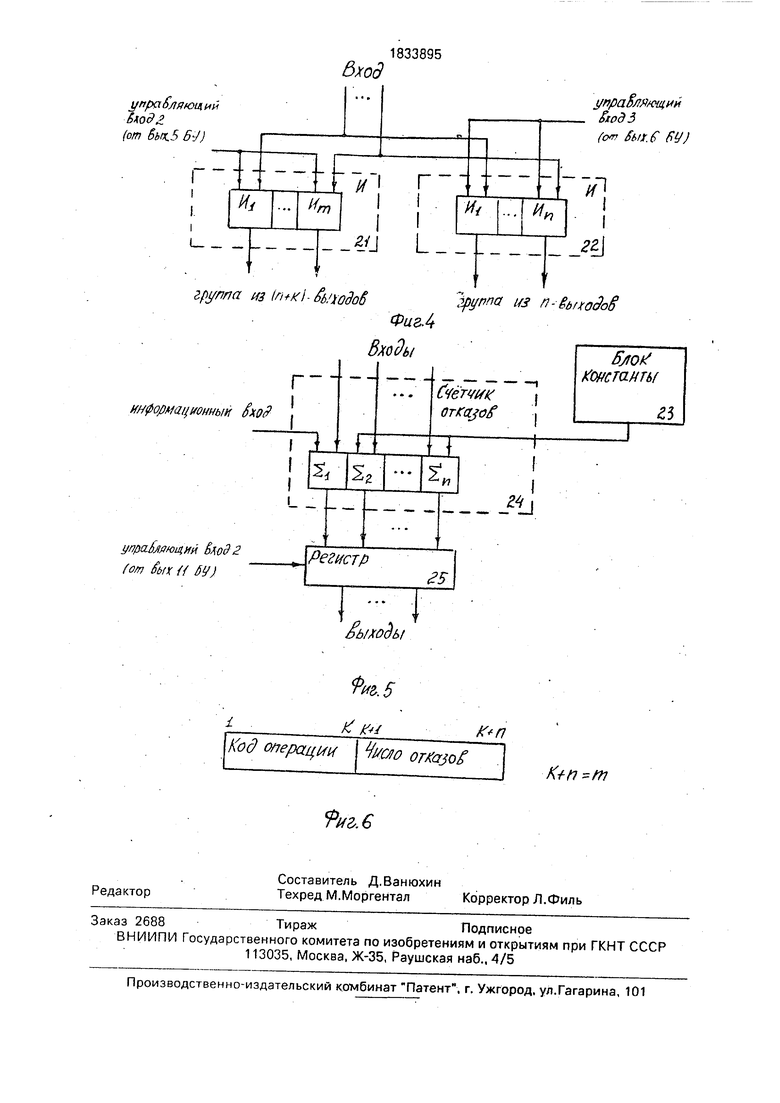

Блок сумматоров (фиг. 5) содержит блок 23 константы, счетчик 24 отказов, выполненный з виде n-одноразрядных сумматоров, регистр 25.

Блок 23 константы обеспечивает постоянное присутствие на вторых входах одноразрядных сумматоров нулевого значения одного из слагаемых.

Формат управляющего слова (фиг. 6) отражает структуру данных в памяти. Управляющее слово из m разрядов содержит код операции - разрядность Кбит и число отказов данной операции - разрядность ПБИТУстройство работает следующим образом.

На первом этапе происходит сбор статистических данных об отказах при выполнении задан-ных команд, а на втором этапе обрабатываются накопленные данные.

Предварительно в блок памяти записывается последовательность выполняемых команд. В блок памяти они записаны в формате управляющего слова (фиг. 6). Первые

k-разрядов занимает код выполняемой команды, а остальные n-разрядов занимают статистические данные об отказах при выполнении объектом данной команды. Последовательность команд в блоке памяти составляет один цикл. Для определения функционирования объекта во времени в блок памяти записываются несколько циклов. Число циклов определяется разрядно-.

стью счетчика циклов 11.

На первом этапе производится последовательное считывание команд из блока памяти, выполнение объектом команды и модификации поля данных в управляющем

5 слове в случае отказа при выполнении объектом данной команды.

На этапе обработки производится обобщение данных об отказах по временным интервалом для каждой команды.

0

Рассмотрим выполнение одной команды для этапа сбора статистических данных. Блок 8 управления вырабатывает сигналы на выходах 1 и 2 в результате на выходных

5 шинах адресного счетчика 7 устанавливается адрес первой ячейки в блоке 4 памяти. Затем по сигналу на выходе 5 блока 8 управления активизируется группа n+k выходов блока 5 коммутации. После этого, по сигналу

0 с выхода 3 блока 8 управления происходит считывание из блока 4 памяти управляющего слова, часть которого (п разрядов) по сигналу с выхода 10 блока 8 управления запоминается в регистре 2 данных, а другая

5 часть -(к разрядов) запоминается по сигналу с выхода 9 блока .8 управления в регистре 3 команд. Объект выполняет команду, поступившую по выходным шинам регистра 3 команд. В случае неправильного выполнения

0 команды от объекта на входную информационную шину блока 1 сумматоров выставляется признак отказа который.по сигналу с выхода 11 блока 8 управления запоминается в регистре 25. В последующих сериях

5 циклов, если при выполнении той же команды будет отказ, то в счетчике 24 отка зов просуммируется текущее значение с предыдущим значением. После выполнения команды по сигналу, с выхода блока 8

0 управления, открывается группа элементов И 24 блока 1 сумматоров и данные записываются в блоке 4 памяти. Таким образом, .в блоке 4 памяти запоминается в.форм-ате управляющего слова информация о выполне5 нии объектом данной команды. Если счетчик 11 циклов не переполнен, то по сигналу с выхода 2 блока 8 управления происходит приращение адреса в адресном счетчике 7. Аналогично выполняются все остальные записанные в блоке 4 памяти команды.

После выполнения заданного числа циклов в счетчике 11 циклов вырабатывается сигнал переполнения, который поступает на установочный вход триггера 14. В результате триггер изменяет свое состояние и сигналом с прямого выхода блокирует первую группу элементов И 15, а сигналом с инверсного выхода открывает вторую группу элементов И 16, таким образом подготавливая блок 8 управления к этапу обработки данных.

На втором этапе начинается обработка статистических данных в заданном режиме суммирования (по всем командам цикла или отдельно по каждой команде) для заданных временных интервалов, т.е. суммирование (обобщение) статистических данных за несколько циклов. Степень обобщения данных и режим суммирования зависит от полученной статистики отказов и реализуется синтезом управляющих сигналов в преобразователе 13 кодов. В зависимости от полученных результатов обработки синтезируется также и соответствующее управление обьектом, т.е. определенный набор команд в цикле.

Рассмотрим выполнение одного шага обобщения для двух команд в режиме суммирования статистики отказов по всем командам цикла, В начале процесса обработки последовательно вырабатываются сигналы на выходах 1, 2, 6 блока 8 управления: установка в О адресного счетчика 7, +1 в адресный счетчик 7, активизация второй группы выходов блока 5 коммутации, далее в цикле последовательно два раза вырабатываются сигналы на выходах 3, 7, 8, 2: чтение из блока 4 памяти, прием в регистр 19 блока 6 арифметического сложения, открытие входов группы элементов И 20, +1 в адресный счетчик 7.

В результате на выходе блока б арифметического сложения сформировалась информация об отказах по двум командам.

Таким образом, устройство осуществляет сбор и обработку статистических данных об объекте в реальном масштабе времени. В отличии от известных устройств данное устройство позволяет получить не только значение вероятности отказа для каждой команды, но и зависимость их от времени, а также, используя полученные данные, синтезировать соответствующее управляющее воздействие на объект, тем самым повышая надежность его функционирования.

Фор м у ла изобретения

повышения достоверности сбора и обработки данных о надежности функционирования исследуемо го обьекта в реальном масштабе времени, в него дополнительно введены

блоки сумматоров, коммутации, арифметического сложения, регистры данных и команд и адресный счетчик, причем первый информационный вход блока сумматоров является входом информации от обьекта ус0 тройства, группа выходов блока сумматоров подключена к первой информационной группе входов блока памяти, адресный вход которого соединен с выходом адресного сяетч ка, выход блока памяти подключен к

5 информационному входу блока коммутации, п выходов из первой группы, n+k выходов которого подключены соответственно к n-входам информации регистра данных, а k-выходов - соответственно к k-входам ин0 формации регистра команд, выход регистра данных соединен с вторым информационным входом, блока сумматоров, выходы регистра команд подключены к второй

5 информационной группе входов блока памяти и являются выходами управления объектом устройства, причем вторая группа выходов блока коммутации подключена к группе информационных входов блока

0 арифметического сложения, выход которого является информационным выходом устройства, первый и второй выходы блока управления соединены соответственно с выходом сброса и счетным входом адресно5 го счетчика, третий и четвертый выходы блока управления соединены соответственно с входами чтения и записи блока памяти, пятый и шестой выходы блока управления соединены соответственно с первым и вторым

0 управляющими входами блока коммутации, седьмой и восьмой выходы блока управления соединены соответственно с входами синхронизации и разрешения блока арифметического сложения, с девятого по один5 надцатый выходы блока управления соединены с входами синхронизации соответственно регистра команд, регистра данных и блока сумматоров.

5 выход тактового генератора соединен со счетным входом адресного счетчика, информационный выход которого подключен к входам первого и второго преобразователей кодов, выход переполнения адресного счетчика соединен со счетным входом счетчика циклов, выход которого соединен с установочным входом триггера, прямой выход триггера соединен с первыми входами элементов И первой группы, инверсный выход триггера соединен с первыми входами элементов И второй группы, группа выходов первого преобразователя кодов соединена со вторыми входами элементов И первой группы, группа выходов второго преобразоTatfofo/йгенератор

Адресный ct/erw

Преобразователь кодоб

в

На

ш п

I k

1 L

ш.

и

мЩ

Входы

L ..

17J l

Управе we

fn №. 2

2i

L

Рештр.

Hi

вателя кодов соединена с вторыми входами элементов И второй группы, выходы элементов И первой группы подключены к первым входам элементов ИЛИ группы, выходы элементов И второй группы подкл ючены к вторым входам элементов ИЛИ группу, выходы элементов ИЛИ группы являются выходами блока управления.

ю

СчёпиХ

ЦИК/10&

//

Т

7П

И,

Ч

к

Ело if сумматороь

I

2

/7

f9

управляющий

&од2

ftm /ь/г. 7 64)

J

цпра&ля&щм

fads

few 6ыкЈ ВУ)

И2.3

управляющий Входе

(от бык.5 БУ)

и,

и,

т

i

i/J

группа из In-nd- Јь/ходо6 группа us п-ёыходоб

Фиг4

Входы

Г

информационный fixoc

Si

управляющий food 2 fan fax //

Регистр

i

управляющий &одЗ

(о быг.б $У)

Л г

У

и

и,

п

fi/rotf

KWCTCLHTbf

Счётчм j orKajof j

tt

и

«i

25

Г77

выходы

Pn.5

X W

| Устройство для сбора и регистрации данных о работе информационно-вычислительной системы | 1981 |

|

SU978155A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления объектом статистической обработки отказов | 1978 |

|

SU746440A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-08-15—Публикация

1991-02-19—Подача