Известны арифметические устройства для выполнения операций сложения и вычитания в самокоитролирующихся циклических кодах, содержащие триггерные регистры 1-го и 2-го числд с цепями записи и установки, схемы циклического переноса, определения знака результата и обнаружения переполнения разрядной сетки и схемы контроля выполнения операций.

Предложенное устройство отличается тем, что каждый i-й разряд помимо триггеров регистров 1-го и 2-го числа содержит два сумматора по mod 2, схему формирования переноса в следующий /-4-1-й разряд и вентиль, причем на первые прямые (инверсные) входы сумматоров Поданы, соответственно, прямые (инверсные) выходы триггеров 1-га и 2-го числа, Ко вторым прямым (инверсным) входам первого и второго сумматоров подключены прямые (инверсные) выходы, соответственно, первого и второго сумматоров предыдущего -1-го разряда; входы схемы переноса связаны с прямыми выходами сумматоров данного разряда и выходом переноса предыдущего /--1-го разряда, связанного также со счетным входом триггера 1-го числа данного г-го разряда и через первую линию задержки со счетным входом триггера 2-го числа следуюн1его г+1-го разряда; прямые выходы (ум.гптороп crnpiuero разряда поданы на пер

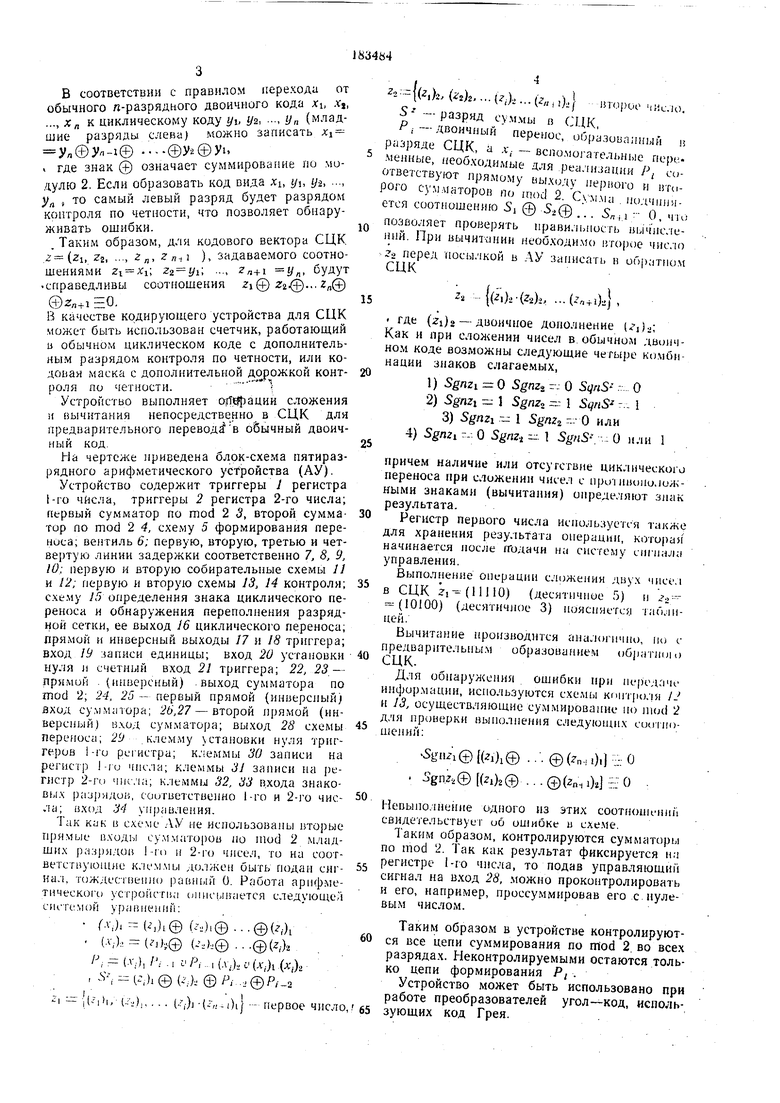

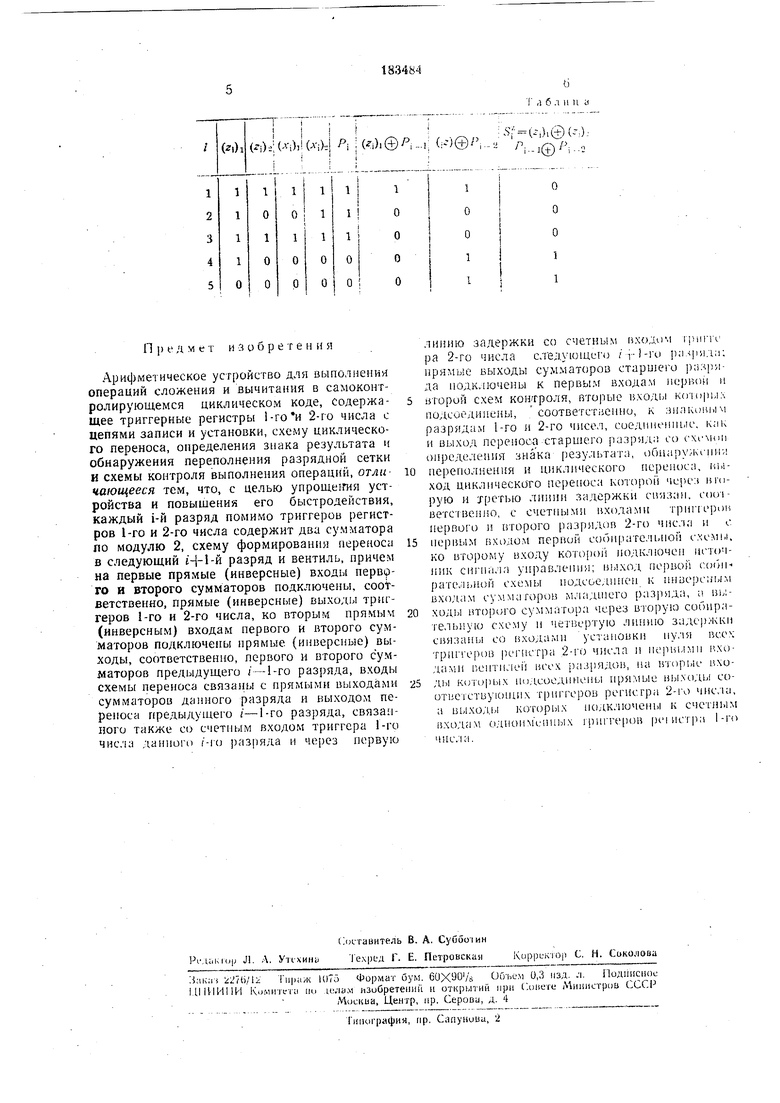

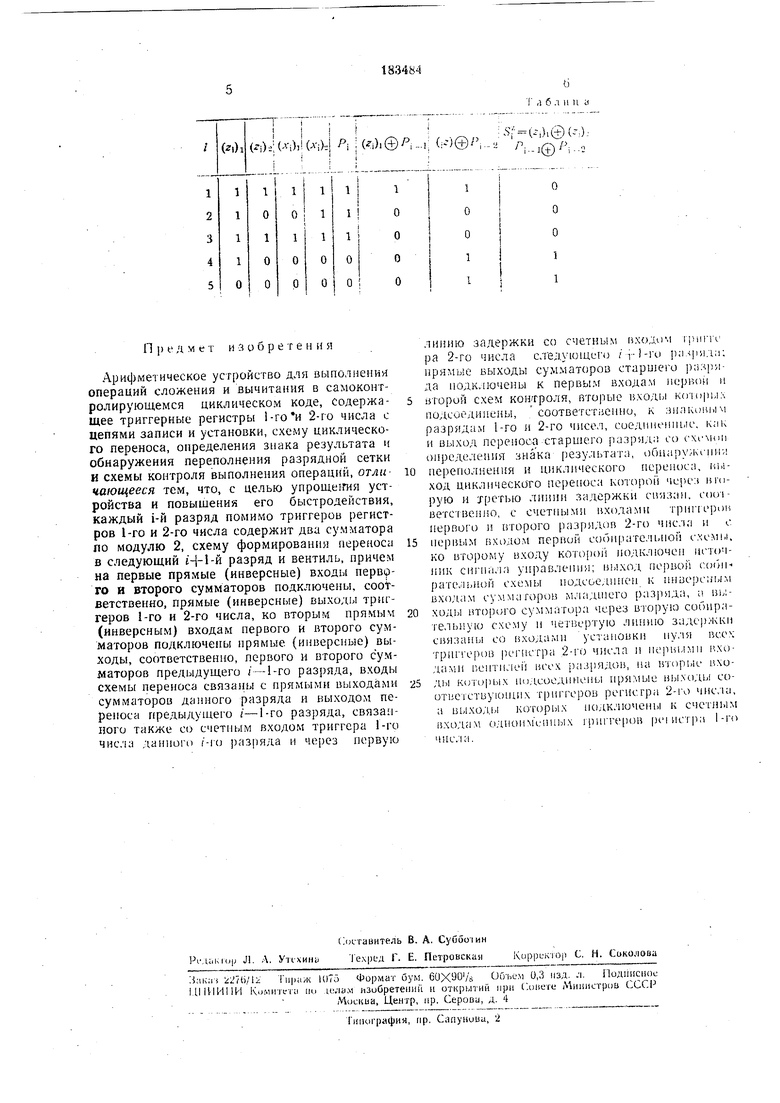

вые входы первой и второй схе.м контроля, на вторые входы которых заведены, соответственно, знаковые разряды 1-го и 2-го чисел, поданные, так же как выход переноса старшего разряда на схему-определения знака результата, обнаружения переполнения и циклического переноса, выход циклического переноса которой через вторую и третью линии задержки связан, соответственно, со счетными входами триггеров первого и второго разрядов 2-го числа и с первым входом первой собирательной схемы, ко второму входу которой подключен источник сигнала управления; выход первой собирательной схемы подсоединен к инверсным входам сумматоров младшего разряда; а выходы второго сумматора через вторую собирательную схему и четвертую линию задержки связаны со входами установки нуля всех триггеров регистра 2-го числа и первыми входами вентилей всех разрядов, на вторые входы которых прямые выходы соответствующих триггеров регистра 2-го числа, а выходы которых подключены, к счетным входам одноименных триггеров регистра 1-го В соответстиин с правилом перехода от обычного п-разрядного двоичного кода Хь .v,, ..., Хп к циклическому коду yi, f/a, .-., Уп (младшие разряды ) можно записать Xi . .-©Уг©Уь . где знак © означает суммирование по мидулю 2, Если образовать код вида Хь уь у-2, , Уд , то самый левый разряд будет разрядом контроля по четности, что позволяет обнаруживать ошибки. Таким образом, для кодового вектора СЦК. .2(Zb za, ..., г„, z „,j }, задаваемого соотношениями Zi Xi; 22 г/ь ..., у„, будут справедливы соотношения г1@г2@...2„@ @Zn+i ЕО. В качестве кодирующего устройства для СЦК может быть использован счетчик, работающий и обычном циклическом коде с дополнительным разрядом контроля по четности, или кодоьая маска с дополнительной дopJЭЖKoй контроля по четности. ; Устройство выполняет оЛ1фации сложения и ычитания непосредственно в СЦК для предварительного перевод в обычный двоичный код. На чертеже приведена блок-схе.ма пятиразрядного арифметического yctpoйcтвa (АУ). Устройство содержит триггеры J регистра 1-го числа, триггеры 2 регистра 2-го числа; первый сумматор по mod 2 3, второй сумматор по mod 2 4, схему 5 формирования переноса; вентиль 6; первую, вторую, третью и четвертую линии задержки соответственно 7, 8, 9, 10; первую и вторую собирательные схемы // и 12; первую и вторую схемы J3, 14 контроля; схему 15 определения знака циклического переноса и обнаружения переполнения разрядной сетки, ее выход 16 циклического переноса; прямой и инверсный выходы 17 и 18 триггера; вход 19 ; аписи единицы; вход 20 установки нуля и счетный вход 21 триггера; 22, 23 - примий .(инверсный) .выход сумматора по mod 2; 2-i, 25 - первый прямой (инверсный) вход сумм;пора; 6,27 - второй прямой (инверсный) вход сумматора; выход 28 схемы переноса; i клемму установки нуля триггеров 1-го регистра; клеммы 30 записи на регистр 1-ги числа; клеммы 31 записи на ptгистр 2-п.) числа; клеммы 32, 33 входа знаковы.х ргиридии, соответстоепно 1-го и 2-го числа; вход 34 управления. 1ак как в схе.ме .ЛУ не использованы вторые прямые входы сум.матороа по niod 2 младших ра; рядаи 1-гп и 2-го чисел, то на соответствующие кл(.м.1ы должен быть подан сигнал, тождиствепло равный 0. Работа арнфметическоси устройств; описьпгпется следующей системой уравнений: ,) - (i.)i@ (г1)1@ . (-s-). (h@ ( -@(,-. А (2,)г (zz)2,... (г.).,... (г„, i).,|- иторие число, S--разряд суммы в СЦК, Я ,--двоичный перенос, образованный и разряде СЦК, а л ,. - всло.мо -ательные переменные, необходимые для .реализации Р соответствуют прямому иыходу периого и итси ого С}мматорон по mod 2. Су.м.ма подчиняется соотношению 5i © S-i@ ... - О, что позволяет проверять правильность вычислений. При вычи7-инии необходимо |$торое число перед посылкой в ЛУ записать н o6|);iTiioM {(г1)2-(г,),, ...(г,о4. где (zija - двоичное дополнение (li:-; Как и при сложении чисел в обычном двоично.м коде возможны следующие четыре комбинации знаков слагаемых, 1)Sgnzi - О Sgm г: О S(/rtS.- О 2)Sgnzi - Sgnzt . 1 SqnS г. I 3) Sgnzi - 1 Sgnzt --О или 4) Sgnzi --- О Sgnz-t - 1 SgnS,-.- О или 1 причем наличие или отсугствие циклическо1о переноса при сложении чисел с про1И1)011оложными знаками (вычитания) определяют знак результата. Регистр первого числа используется для хранения результата операции, которая начинается после ггодачи на систему сигнала управления. Выпол 1ение операции с.южения двух чисел в СЦК г,-(11110) (десятичное 5) ti г.-- (10100) (десятичное 3) поясняется таблицей. Вычитание производится аналогично, но с предварительным образованием обратною СЦК. Для обнаружения ошибки при передаче информации, используются схе.мы контроля IJ и 13, осуществляющие сум.мировапие по mod 2 .1я проверки выполнения следующи.х со(.пч(оепий:-Sgn.i@{(2i)i@ ©(n.i .))-:;: О %n2i© (2i)j@ -©fei) z: о Невыполнение одного из этих cooTHoinenHii свидетельствует иб ошибке и схеме. Таким образом, контролируются сумматоры по mod 2. Так как результат фиксируется H;I регистре 1-го числа, то подав управляющий игнал на вход 28, можно проконтролировать его, например, проссу.ммировав его с пулевым числом. Таким образом в устройстне контролируются все цепи суммирования по mod 2. во всех разрядах. Неконтролируемыми остаются только цепи формирования Я/ .

П р е Л м е т и 3 о б р е т е и и я

Арифметическое устройство для выполнения операций сложения и вычитания в самоконтролирующемся циклическом коде, содержащее триггерные регистры 2-го числа с цепями записи и установки, схему циклического переноса, определения знака результата и обнаружения переполнения разрядной сетки и схемы контроля выполнения операций, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, каждый i-й разряд помимо триггеров регистров 1-го и 2-го числа содержит два сумматора ло модулю 2, схему формирования переноса в следующий разряд и вентиль, причем на первые прямые (инверсные) входы и второго сумматоров подключены, соответственно, прямые (инверсные) выходы триггеров 1-го и 2-го числа, ко вторым прямым (инверсным) входам первого и второго сумматоров подключены прямые (инверсные) выходы, соответственно, первого и второго сумматоров предыдущего /-1-го разряда, входы схемы переноса связаны с прямыми выходами сумматоров данного разряда и выходом переноса предыдущего i-1-го разряда, связанного также со счетным входом триггера 1-го числа данного /-го разряда и через первую

линню задержки со счетным гкходим григгс ра 2-го числа следук) /yl-io рлчряд; ; прямые выходы сумматоров cTapujero разряда нодк.иочены к первым входам lujpi oii и

второй схем контроля, вторые входы KO-lDpUX

подсоединены, cooTBCTCTiiCHHo, к 3iiaKi.4ii.iM разрядам 1-го н 2-го чисел, соединенные, Kaiv и выход переноса старшего разряда ео схемпи онределеиня знака результата, оОнарулченнл неренолнения и циклического нереиоеа, иыход циклического переноса которой через вторую и хретью липни задержки сиязан. eooiветственно, с счетщзши входами триперои нерпого 1 второго разрядов 2-го числа и о iiepiUiiM входом первой еооирательной (..хемы, ко второму входу кото)()й подключен источник сигнала управления; В1лход пе)БОЙ ооГли рательной схемы подсоединен к пнвереьчлм входам сумматоров млади1его разряда, п выходы HTopoio сумматора через Blopyio сооирательную схему н четвертую линию задержки связаны со входами установки иуля псех трщтеров peiiicrpa 2-i-o числа н нерылмн иходами г,ентиле| 1 всех разрядов, на вторые входы К(пч)рых иодеоединены прямые в|)1хс)ды соотиегствуюнщх т)И1терОБ регистра 2-го чис/ш, а выходы KOTopiiix нодк.почены к счетным входа одноимениых 1ригге и)в |)ei истра 1-го mic.ia.

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный операционный блок | 1990 |

|

SU1714585A1 |

| Преобразователь двоичного кода в код с весовыми коэффициентами 1 и -1 и обратно | 1981 |

|

SU1007097A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

Даты

1966-01-01—Публикация