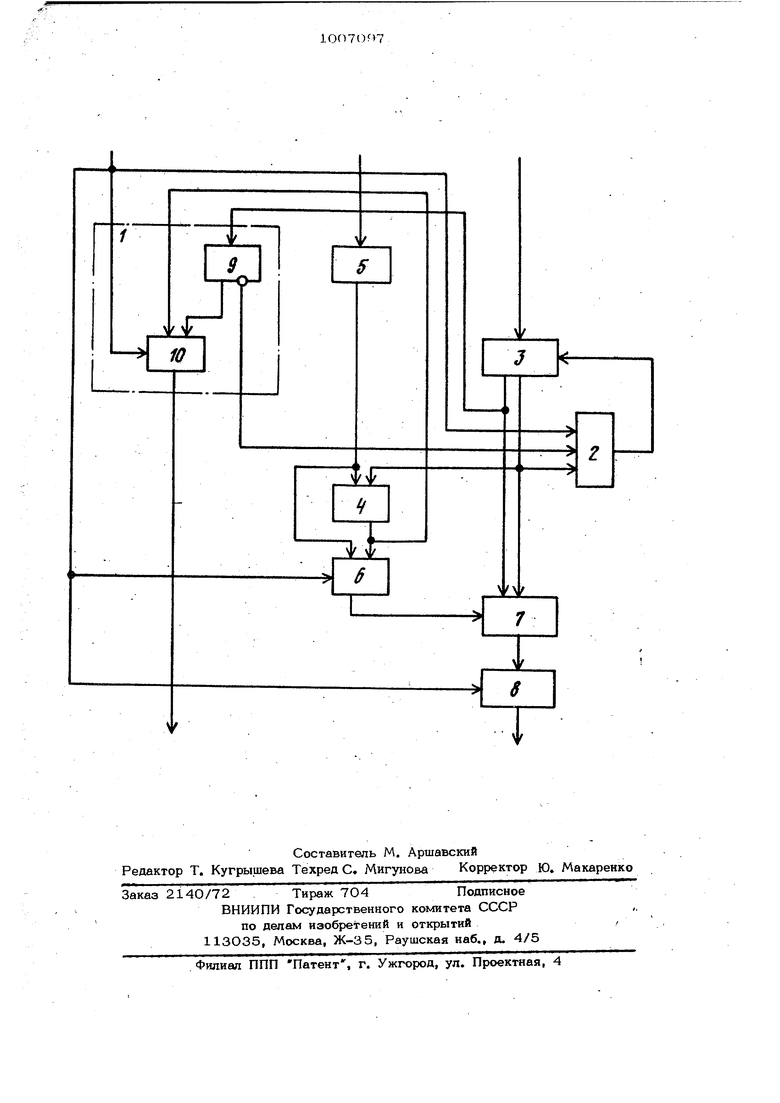

110 Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных вычислительных устройств. Известен преобразователь двоичных чисел в код числа по модулю М, содержа щий регистр, постоянное запоминающее устройство, двоичный сумматор, мультиплексор и два сумматора по модулю М, каждый из которых состоит из трех двоичных сумматоров и мультиплексораС Недостаток известного преобразователя состоит в низком быстродействии и большом объеме аппаратуры. Наиболее близким по технической сущности к предлагаемому является преобра- зователь двоичного кода в код с весовы ми коэффициентами 1 и -1 и обратно, содержащий логический блок, триггер зна ка, группу полусумматоров и выходной мультиплексор ,2., Недостаток данного преобразователя состоит в низком быстродействии, связан ном с необходимостью выполнения четырех операций (сдвиг, сравнение с нулем, передача на сумматор одного из. трех чисел, сложение), а также в относительно большом объеме аппаратуры. Целью изобретения является увеличе ние быстродействия и упрощение преобразователя. Поставленная цель достигается тем, что в преобразователь двоичного кода в код с весовыми коэффициентами 1 и -1 и обратно, содержащий блок определения знака, триггер знака, группу полусумматоров и выходной мультиплексор, выход которого является выходом мантиссы преобразователя, управляющий вход которого соединен с управляющим входом выходного мультиплексора, информационные входы которого соединены с выходами группы полусумматоров, выход блока определения знака является выходом знака преобразователя, вход знака которого соеди иен с входом триггера знака, введены вы вычитайиций , первый и второй элементы ИЛИ-НЕ и управляющий мультиплексор, а блок определения знака содержит элемент ИЛИ-ИЛИ-НЕ и мультиплексор, знака, первый информационный вход которого соединен с выходом первого элемшта ИЛИ-НВ и первым входом управляющего мультиплексора, второй информационный вход которого соединен с выходом триггера знака и первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом старшего разряда вычитающего счетчика и 972 первым входом второго элемента ИЛИНЕ, второй вход которого соединен с инверсным выходом элемента ИЛИ-ИЛИ-НЕ, nfbflMo выход которого соединен с вторым информационным входом мультиплексора знака, входы элемента ИЛИ-ИЛИ-НЕ соединены с выходами вычитаюшего счетчика и с информационными входами полусумматоров; группы, управляющие входы которых соединены с выходом управляюшего мультиплексора, управляющий вход которого соединен с управляющим входом преобразователя, с управляющим вхоДом Мультиплексора знака и с третьим входом второго элемента ИЛИ-НЕ, выход которого соединен со счетным входом вычитающего счетчика, информационные вхоРЫ которого являются входами 1антйссы преобразователя, управляющий вход котоР о соединен с управляющим входом мультиплексора знака. На чертеже представлена блок-схема предлагаемого преобразователя. Преобразователь содержит блок 1 определения знака, элемент ИЛИ-НЕ 2, вычитающий счетчик 3, элемент ИЛИ-НЕ 4, триггер 5 знака, управляющий мультиплексор 6, группу полусумматоров 7, выходной мультиплексор 8. В состав определения знака блока 1 входят элемент ИЛИ-ИЛИ-НЕ 9 и мультиплекстор 1О знака. Предлагаемый преобразователь осуществляет преобразование 1 -разрядного числа со знаком, представленного в си- стеме счисления с цифрами О и 1 в прямом коде Л(о(з„,,„., в его представление по модулю М 2 +1 в системе счисления с цифрами - 1 и 1. ,.rv-.ViZ-V При выполнении прямого преобразования возможны следующие случаи. 1..Если число А является нечетным и положительным, т.е. «0 1,азн О, то A-f( ) 2 2. Если число А является четным и положительным, т.е. C(Q О, , то е,)-м.,Д,,ц-о („ , 3, Если число А является нечетным и отрицательным, т.е.а0 1, cJ 1, то р, SH ° 4. Если 9f О, 1 то -1 .Ъ, 5, Если А О, T,e, O,...i то, не преобразуя мантиссы принимается , Примеры использования выражений ( (2), (3), (4) для выполнения прямого преобразования (при условии, что в си ме счисления с цифрами -1 и 1 цифра кодируется как 1, а цифра (-1) - как приведены ниже.,- 1.А ОД001 (9) 11ОО циклический сдвиг вправо В ОД10О (9) 2.А ОД10О (12) ОНО циклический сдвиг вправо - 1 вычитание единицы В О,0101 (-5 12гт1оа(2%1) 3, А 1ДОО1 (-9) . 11ОО (циклический сдвиг вправо ООН поразрядная инверс В О,ОО11 (-9)4, А 1,11ОО (-12) ОНО циклический сдвиг вправо - 1 вычитание единицы 101О поразрядная инверс О,1010 (5 (-12) mod (2 При выполнении обратного преобраз вания возможны следующие случаи, j 1, Если В О, т,е, , то ), 2, Если В 0, т.е, в,., «ЗН 3, Если В О, т,е, , то, не преобразуя мантиссы, принимаетсяа Примеры использования выражений (5), (6) для выполнения обратного пр образования приведены ниже, 1. В ОДНО (13) 11О1 циклический сдвиг А ОД1О1 (13) 2. В 0,0001 (-13) ОО1О циклический сдвиг Х1О1 поразрядная инверсия Л 1,1101 (-13) Предпагвемый преобразователь -работает следу юшим образом, В исходном состоявнн триггер 5 знака и вычитающий счетчик 3 обнулены. По сигналу пуска в триггер 5. знака и вычитающий счетчик 3 записываются соответственно знак и циклически сдвинутая на один раэряа вправо мантисса преобразуемого числа. Одновременно с сигналом пуска на управляющий вход преобразова- « теля поступает сигнал, определяющий вид преобразования. При выполнении прямого преобразования преобразователь работает следующим образом. После того, как знак и мантисса преобразуемого числа зафиксируются соответственно в триггере 5 знака и вычитающем счетчике 3, на втором выходе элемента ИЛИ-ИЛИ-НЕ 9 в случае, когда преобразуемое число отлично от нуля, образуется признак неравенства преобра- дуемого числа нулю, которое при условии что старший (с номером h ) разряд вычитающего счетчика нулевой, разрешает формирование Э1пем 1том ИЛИ-НЕ 2 сигнала вычитания единицы, под дейстшем которого из содержимого вычитающего счетчика 3 вычитается единица. Во вре- мя вычитания единицы управляющий t nbтиплексор 6 передает знак преобразуемого числа на управляющий вход группы 7 полусумматоров, формируя таким образом при условии, что преобразуемое число отрицательное (в триггере знака за(|«ксиро единица), сигнал выдачи обратного кода. Под действием этого сигнала полусумматоры группы 7 осуществляют поразрядную инверсию кода, поступающего из вычитающего счетчика 3. Если сигнал выдачи обратного кода не образовался то происходит выдача прямого, кода из вычитающего счетчика 3, В результате на выходе группы 7 псЛусумматоров формируется мантисса преобразованного чисда, поступающая на информационный вход выходного мультиплексора 8, который передает ее.без изменений на второй выход преобразователя. На первом выходе преобразователя формируется знак преоб.510 раэованного числа, который равен отрицанию признака норавенства преобразуем го числа нулю. При выполнении обратного преобраз(вания преобразователь работает следующим образом. После того как знак и мантисса преобразуемого числа зафиксируются соотве ственно в триггере 5 знака и вычитающем счетчике 3, при условии, что разряд вычитающего счетчика 3 с номером (О-1) нулевой и преобразуемое число отлично от нуля (в триггере знака 5 зафиксирован нуль), на выходе элемента ИЛИ-НЕ 4 образуется признак обратного кода, поступающий на второй информа ционный вход управляющего мультиплексора 6, который передает его на управля ющий вход полусумматоров группы 7, фор мируя таким образом сигнал выдачи обратного кода. Под действием этого сигнала полусумматоры 7 осуществляют поразрядную инверсию кода, поступающего с выхода вычитаклиего счетчика 3. Если сигнал выдачи обратного кода не образовался, то происходит выдача прямого кода из вычитаюшего счетчика 3. Далее с выходов полусумматоров группы 7 код мантиссы числа поступает на информационный вход выходного мультиплексора 8, где посредством соответствукхией коммутации циклически сдвигается на два разряда влэво. Выходной мультиплексор 8 Передает сдвинутый код мантиссы на вто рой выход преобразователя, формируя таким образом мантиссу преобразованного числа. Знак преобразованного числа, совпадающий с признаком обратного кода, формируется на выходе знака преобра зователя. Время ТУ| за которое осуществляется преобразование преобразователем 2 опредедяется выражением . 97 гдеТпц время приема кода на регистр; -Ьсд- время сдвига J Ьд-И-Ьц- соответственно задержка, вносимая входной комбинационной схемой и комму та торсм со схемой управления; время суммирования; tg - соответственно задержка, вносимая узлом выдачи прямого и обратного кода и выходным мультиплексором. Введение вычитающего счетчика первого и второго элементон ИЛИ-НЕ и управлйклиего мультиплексора позволяет уменьщить время Т до величины . г где igq- время, необходимое для вычитания единицы в вычитающем счетчике (который с целью повьпиения быстродействия следут строить как счетчик с ускоренным переносом). Это обусловлено тем, что вместо четырех операций, выполняемых преобразова- . телем L2 3 в предлагаемом преобразователе ньшолншотся только две операции, совмещенные по времени - вычитание единицы и формирование признака равенства преобразуемого числа нулю. Кроме того, предложенная структура преобразо- вателя позволяет сократить объем оборудования по сравнению с преобразователем С23, так как в кем предусмотрен п -разрядный комбинационный сумматор, коммутатор со схемой управления и t1 -разрядный сдвиговый регистр. Выигрыщ в быстродействии в зависимости от используемой элементной базы лежит в пределах (1,7-3) раза при уменьщении объема аппаратуры в 1,2 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Преобразователь "КОД-ШИМ | 1981 |

|

SU993470A2 |

| Преобразователь @ -разрядного двоичного числа в его представление по модулю @ | 1982 |

|

SU1076899A1 |

| Преобразователь кода в частоту | 2023 |

|

RU2805259C1 |

| Преобразователь последовательного кода в параллельный | 1981 |

|

SU970355A1 |

| Преобразователь напряжения в код | 1976 |

|

SU577670A2 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь параллельного кода в число-импульсный код | 1981 |

|

SU1027714A1 |

| Преобразователь частоты в код | 1980 |

|

SU924859A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В КОД С ВЕССВЫМИ КОЭФФИЦИЕНТАМИ 1 И -1 И ОБРАТНО, содержащий блок определения знака, триггер знака, группу полусумматоров и выходной мультиплексор, выход которого выходом мантиссы преобразователя, управляклдий вход которого соединен с управляющим входом выходного мультиплексора,- информационные входы которого соединены с выходами rfqrnnbi . Полусумматоров, выход определения знака является выходом знака преобразователя, вход знака которого соединен со входом триггера знака, отличающийся тем, что, с целью повышения быстродействия и упрошения преобра- . зователя в него введены вычитаюшвй счетчик, первый и второй элементы ИЛИНЕ и управляющий мультиплексор, а ок определения знака содержит элемент ИЛИИЛИ-НЕ и мультиплексор знака, первый информационный вход которого соединен с выходом первого элемента ИЛИ-НЕ и первым входом управляющего мультиплексора, второй информационный вход которого соединен с выходом триггера знака и первым входом первого элемента ИЛИНЕ, второй вход котсфого соединен с выходом старшего разр1яда вычитающего счетчика и первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом элемента ИЛИ-ИЛИ-НЁ, прямой выход которого соединен с вторым информационным входом мультиплексора знака, входы элемента ИЛИ-ИЛИ-НЕ соединены с выходами вычи тающего счетчика и с информационными В входами, полусумматоров группь, управ- 1якя1ше входь которых соединены с выходом управляющего мультиплексора, управлякший вход соединен с управляющим входом преобразователя, с управляющим входом мультиплексора знака и с третьим входом второго элемента ИЛИ- о НЕ, выход которого соединен со счетным входом тзычитающего счетчика, янформа- , ционные входы которого являются входами мантиссы преобразователя, управляющий вход которого соединен с управляющим входом мультиплексора знака.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для разрыхления дна реки, приводимое в действие силою ее течения | 1929 |

|

SU15131A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

| (прототип), | |||

Авторы

Даты

1983-03-23—Публикация

1981-06-08—Подача