Изобретение относится к вычислительой технике и предназначено для реализации злов и устройств цифровых вычислительных ашин методами интегральной технологии о средним и большим уровнями интеграии.

Целью изобретения является увеличеие быстродействия управляемого арифетического модуля при выполнении перации сложения двух двоичных операнов.

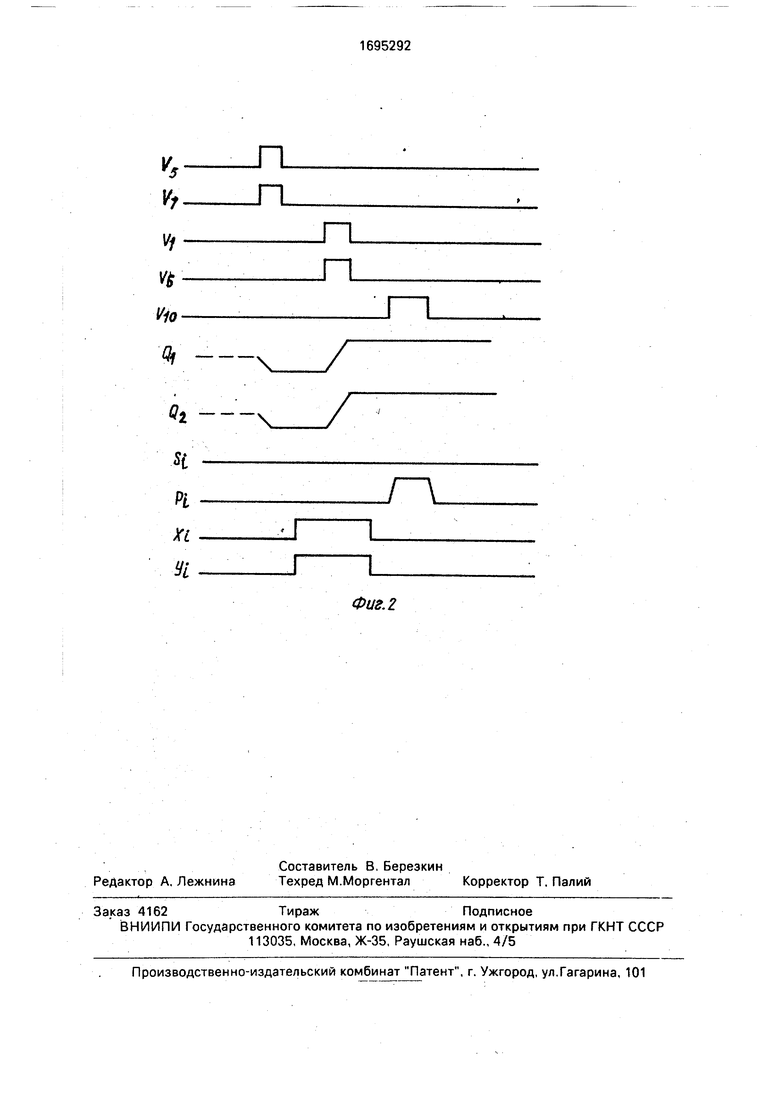

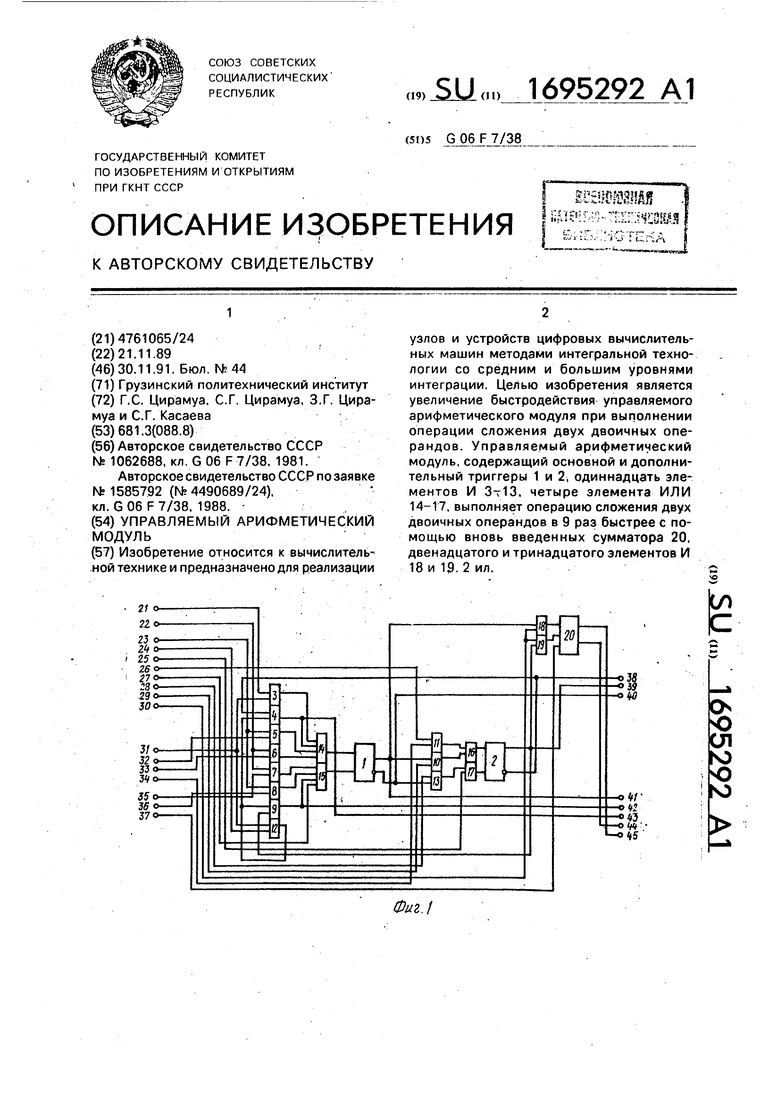

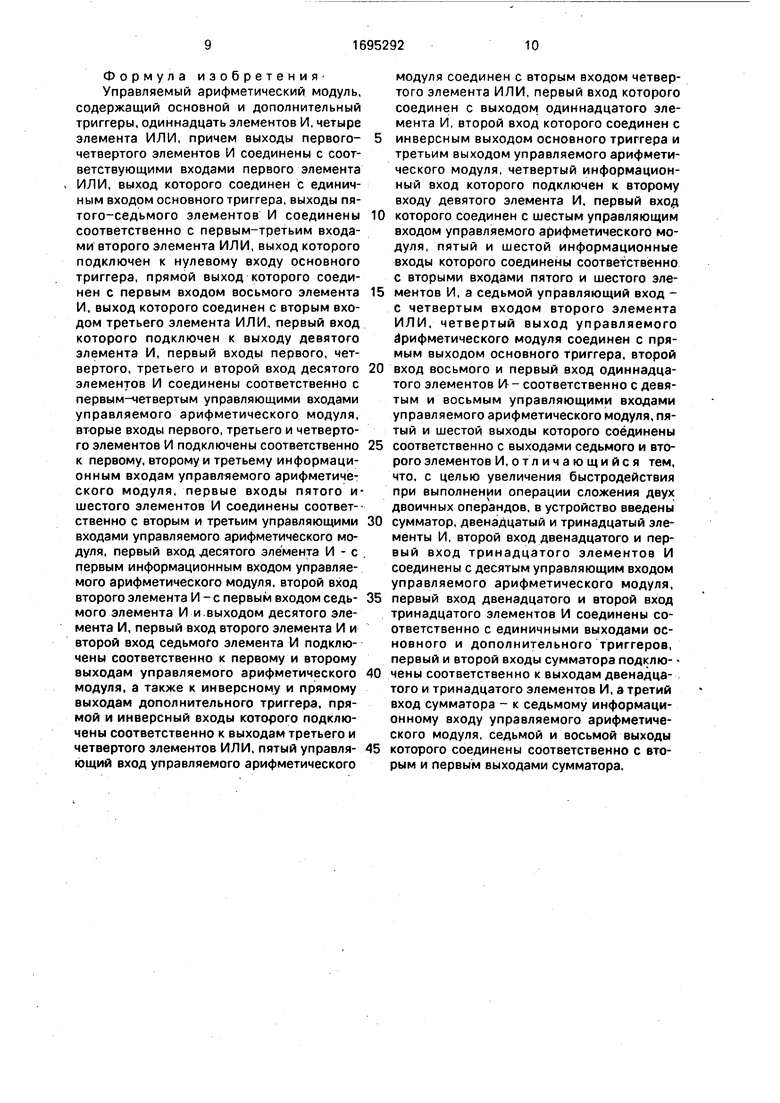

На фиг. 1 представлена схема управлямого арифметического модуля; на фиг, 2 - временная диаграмма его работы в режиме арифметического сложения двух двоичных операндов.

Управляемый арифметический модуль содержит основной и дополнительный триггеры 1 и 2, одиннадцать элементов И 3-13, четыре элемента ИЛИ 14-17, два элемента И 18 и 19, сумматор 20, управляющие входы 21-30, информационные входы 31-37, выходы 38-45. Выходы первого 3, второго 4, третьего 5 и четвертого 6 элементов И соединены с входами первого элемента ИЛИ 14, выход которого соединен с прямым входом основного триггера 1. Выходы пятого 7, шестого 8 и седьмого 9 элементов И соединены с входами второго элемента ИЛИ 15, выход которого подключен к ин- версному входу основного триггера 1, прямой выход которого соединен с первым входом восьмого элемента И 10, выход ко- торого соединен с вторым входом третьего элемента ИЛИ 16, первый вход которого подключен к выходу девятого.элемента И 11. Первые входы первого 3, четвертого 6, третьего 5 и десятого 12 элементов И сое- динены соответственно с первым 21, вторым 22, третьим 23 и четвертым 24 управляющими входами управляемого арифметического модуля. Вторые входы первого 3, третьего 5 и четвертого 6 элементов И подключены соответственно к первому 31, второму 32 и третьему 33 информационным входам управляемого арифметического модуля. Первые входы пятого 7 и шестого 8 элементов И соединены с вторым 22 и третьим 23 управляющими входами управляемого арифметического модуля. Первый вход десятого элемента И 12 соединен с первым информационным входом 31 управляемого арифметического модуля. Второй вход второго элемента И 4 соединен с первым входом седьмого элемента И 9 и выходом десятого элемента И 12. Первый вход второго элемента И 4 и второй вход седьмого элемента И 9 подключены соответственно к первому 38 и второму 39 выходам управляемого арифметического модуля, а

также к инверсному и прямому выходам дополнительного триггера 2, прямой и ин- версный входы которого подключены соответственно к выходам третьего 16 и

четвертого 17 элементов ИЛ И. Пятый управляющий вход 25 управляемого арифметического модуля соединен с вторым входом четвертого элемента ИЛИ 17, первый вход которого соединен с инверсным выходом

0 основного триггера 1 и третьим выходом

40управляемого арифметического модуле, четвертый информационный вход 34 которого подключен к второму входу девятого элемента И 11, первый вход которого сое5 динен с шестым управляющим входом 26 управляемого арифметического модуля, пятый 35 и шестой 36 информационные входы которого соединены соответственно с вторыми входами пятого 7 и шестого

0 8 элементов И. Седьмой управляющий вход 27 управляемого арифметического модуля соединен с четвертым входом второго элемента ИЛИ 15, а четвертый выход

41управляемого арифметического модуля 5 соединен с прямым выходом основного

триггера 1. Второй вход восьмого 10 и первый вход одиннадцатого 13 элементов И соединены соответственно с девятым 29 и восьмым 28 управляющими входами уп- 0 равляемого арифметического модуля, пятый

42и шестой 43 выходы которого соединены соответственно с выходами седьмого 9 и второго 4 элементов И. Второй вход двенадцатого 18 и первый вход тринадца5 того 19 элементов И соединены с десятым управляющим входом 30 управляемого арифметического модуля,-первый вход двенадцатого 19 и второй вход тринадцатого 19 элементов И соединены

0 соответственно с единичными выходами основного 1 и дополнительного 2 триггеров. Первый и второй входы сумматора 20 подключены соответственно к выходам двенадцатого 18 и тринадцатого 19 элементов И, а

5 третий вход подключен к седьмому инфор1 мационному входу 37 управляемого арифметического модуля, седьмой 44 и восьмой 45 выходы которого соединены соответственно с вторым и первым выходами сумма0 тора.

На управляющие и информационные входы управляемого арифметического модуля подаются следующие сигналы;

VI-VIQ - управляющие сигналы (управ5 ляющие входы 21-30 соответственно);

Xi - i-й разряд кода X (первый информационный вход 31);

Qi + 1 - содержимое соседнего старшего разряда (второй информационный вход 32):

Qi - 1 - содержимое соседнего младшего разряда (третий информационный вход 33);

YI - i-й разряд кода Y (четвертый информационный вход 34);

QI - 1 - содержимое соседнего младшего разряда (пятый информационный вход 35);

di + i - содержимое соседнего старшего разряда (шестой информационный вход 36);

PI 1 - перенос единицы из соседнего младшего разряда (седьмой информационный вход 37).

Сигналы Vi-Vio обеспечивают выполнение следующих операций:

Vi (вход 21) - прием операнда Xi в основной триггер 1 и логическое сложение;

V2 (вход 22) - сдвиг в сторону старших разрядов;

Уз (вход 23) - сдвиг в сторону младших разрядов;

V4 (вход 24) - сложение по mod 2;

Vs (вход 25) - установка на нуль дополнительного триггеров 2;

Ve (вход 26) - прием операнда YI в дополнительный триггер 2;

V (вход 27) - установка на нуль основного триггера 1;

Ve (вход 28) - конъюнкция содержимых основного 1 и дополнительного 2 триггера;

Vg (вход 29) - дизъюнкция содержимых основного 1 и дополнительного 2 триггеров;

Ую (вход 30) - арифметическое сложение двух двоичных операндов Xi и YI,

С помощью управляемого арифметического модуля реализуются все 16 функций булевой алгебры двух переменных, некоторые функции трех и четырех переменных, функция двух самостоятельных регистров, функция двухступенчатого регистра, функция преобразования параллельного кода в последовательный и обратно, функция реверсивного регистра сдвига числа, функция двоичного суммирующего или вычитающего счетчика,функция циклического реверсивного регистра сдвига, функция параллельного сумматора с последовательным переносом, функция распространения единицы, нуля и др.

Используя два и более управляемых арифметических модулей, можно реализовать и более сложные функции, в частности функции схем контроля, функции сравнения кодов, функции дешифратора, шифратора, коммутатора каналов, функции преобразования кода Грея в двоичный и наоборот и др.

С помощью предлагаемого управляемого арифметического модуля реализуются

как сингулярные булевые функции и функции двух переменных, так и функции трех, четырех и более переменных.

С целью иллюстрации реализации логи- 5 ческих функций на управляемом арифметическом модуле приведено описание функционирования модуля при реализации отдельных функций.

Функция поразрядной конъюнкции 0 двух двоичных чисел выполняется следующим образом.

Операнд YI подается на четвертый информационный вход 34 и сигналом /е(вход 26) через девятый элемент И 11 и третий

5 элемент ИЛИ 16 заносится в дополнительный триггер 2. Операнд Xi подается на первый информационный вход 31 и сигналом Vi (вход 21) через первый элемент И 3 и первый элемент ИЛИ 14 заносится в основ0 ной триггер 1.. Предварительно-основной 1 и дополнительный 2 триггеры соответственно сигналами V (вход 27) и Vs (вход 25) устанавливаются в нулевое состояние. Для осуществления операции конъюнкции подается

5 сигнал Vs (вход 28), и содержимое основного триггера 1 с инверсного выхода через элементы И 13 и ИЛИ 17 переписывается в дополнительный триггер 2. В результате в дополнительном триггере 2 (выход 39) уста0 навливается логическое произведение

Последовательность выполнения функции поразрядной дизъюнкции аналогична предыдущему, но вместо сигнала Ve (вход 28) следует подать сигнал Vg (вход 29).

5 Функция поразрядной дизъюнкции реализуется также при подаче управляющих сигналов Vi (вход 21) и Ve (вход 26). Прямые коды Xi и YI подаются на первый 31 и четвертый 34 информационные входы и через4

0 элементы ИЗ, ИЛИ 14, И 11 и ИЛИ 16 на прямые входы основного 1 и дополнительного 2 триггеров. В результате в основном триггере 1 получается сумма Xi, а в дополнительном триггере ,

5 где Xi и YJ - содержимое основного 1 и дополнительного 2 триггеров, т.е. третья и четвертая переменные. Далее можно получить или (XivXi1) ()или()3 ( Y,1 ) и т.д.

0Функция сложения по mod 2 двух дво.ичных операндов Xi и YI выполняется следующим образом.

Сигналами V (вход 27) и Vs (вход 25) основной 1 и дополнительный 2 триггеры

5 устанавливаются в нулевое состояние. Сигналом V4 (вход 24) операнд Xi от первого- информационного входа 31 через десятый элемент И 12 подается на первые входы второго 4 и седьмого 9 элементов И, в результате чего в основном триггере 1 устанавливается сумма Xi©0 &- сложение по mod 2). Сигналом Ve (вход 28) & Vg (вход 29) содержимое основного триггера 1 переписывается в дополнительный триггер 2. Повторно подается сигнал V4 (вход 24), и второй операнд YI, подаваемый с первого информационного входа 31, пройдя элементы И 12 и И 4 (или И 9), в основном триггере 1 устанавливает сумму Xi (54 YI. Результат выдается на четвертом выходе 41 управляемого арифметического модуля.

Для реализации функций Пирса, Шеф- фера и эквивалентности производится дизъюнкция, конъюнкция и сложение по mod 2 соответственно и результаты устанавливаются на инверсных выходах основного 1 (третий выход модуля, выход 40) и дополнительного 2 (первый выход модуля, выход 38) триггеров.

Функция сдвига асторону младших разрядов осуществляется за два полутакта. В первом полутакте сигналом /з (вход 23) парафазный код содержимого дополнительного триггера 2(Qi-i, Оы)(1-1)-го разряда через второй (вход 32) и шестой (вход 35) информационные входы и через третий 5 и шестой 8 элементы И переписывается в основной триггер 1 1-го разряда. Перепись из основного триггера 1 в дополнительный триггер 2 осуществляется сигналом Уз(вход 28) &У9(вход29).

Функция сдвига в сторону старших разрядов осуществляется аналогично предыдущему за два полутакта. Сигналом V2 (вход 22) парафазный код содержимого дополнительного триггера 2 (i + 1)-го разряда подается на третий (вход 33) и пятый (вход 35) информационные входы 1-го разряда. Открывается четвертый элемент И 6 или пятый элемент И 7 и возбуждается соответствующий вход основного триггера 1 1-го разряда. Перепись в дополнительный триггер 2 осуществляется сигналом Ув(вход 28) &Уд(вход29).

Счетчик работает как обычный двухтактный суммирующий двоичный счетчик с последовательным переносом.

Для создания структуры многофункционального двоичного счетчика пятый выход 42 1-го управляемого арифметического модуля соединяется с первым информационным входом 31 (i + 1)-го разряда управляемого арифметического модуля.

Двоичный счет осуществляется после установки основного 1 и дополнительного 2 триггеров в нулевое состояние сигналами V (вход 27) и V5 (вход 25). Импульсы счета поступают на первый информационный вход 31 управляемого арифметического модуля первого разряда счетчика

До начала счета на четвертые управляющие входы 24 подается низкий уровень синхроимпульсов, а на восьмые 28 и девятые 29 управляющие входы - высокий уровень. При подаче первого импульса счета ни первый информационный вход 31 младшего разряда счетчика одновременно на четвертые управляющие входы 24 поступает высокий уровень синхроимпульса, кото0 рый через десятый элемент И 12 и второй элемент И 4 переводит основной триггер 1 первого разряда счетчика из состояния О в состояние 1, За второй полупериод синхроимпульса, который подается на

5 восьмые 28 и девятые 29 управляющие входы, дополнительный триггер 2 переходит из состояния О в состояние. После подачи второго импульса счета и первого полупериода синхроимпульса основной триггер 1

0 первого разряда счетчика переходит в состояние О.

Одновременно с пятого выхода 42 управляемого арифметического модуля первого разряда счетчика высокий уровень

5 сигнала подается на первый информационный вход 31 управляемого арифметического модуля второго разряда счетчика и переводит основной триггер 1 второго разряда в состояние 1 и т.д.

0 Функция арифметического сложения двух двоичных операндов Х| и YI осуществляется следующим образом.

Сигналами Vs (вход 25) и V (вход 27) дополнительный 2 и основной 1 триггеры

5 устанавливаются в нулевое состояние. Сигналом Vi (вход 21) операнд Х| от первого информационного входа 31 через пе рвый элемент И 3 и первый элемент ИЛИ 14 запишется в основной триггер 1. Сигналом

0 Ve (вход 26) операнд YI от четвертого информационного входа 34 через девятый элемент И 11 и третий элемент ИЛИ 16 запишется в дополнительный триггер 2, Затем сигналом V10 (вход 30) операнды Х|

5 и YI подаются на вход сумматора 20. Пе: ренос единицы из i - 1-го разряда поступает на третий вход сумматора с седьмого информационного входа 37 i-ro разряда управляемого арифметического модуля.

0 Результат суммирования операндов Xi и YI выдается на восьмом выходе 45 управляемого арифметического модуля, а перенос единицы в i + 1-й разряд - на седьмом выходе 44.

5 Для создания структуры многоразрядного сумматора седьмой выход 44 1-го управляемого арифметического модуля соединяется с седьмым информационным входом 37 i + 1-го управляемого арифметического модуля.

Формула изобретения Управляемый арифметический модуль, содержащий основной и дополнительный триггеры, одиннадцать элементов И, четыре элемента ИЛИ, причем выходы первого- четвертого элементов И соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с единичным входом основного триггера, выходы пя- того-седьмого элементов И соединены соответственно с первым-третьим входами второго элемента ИЛИ, выход которого подключен к нулевому входу основного триггера, прямой выход которого соединен с первым входом восьмого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, первый вход которого подключен к выходу девятого элемента И, первый входы первого, четвертого, третьего и второй вход десятого элементов И соединены соответственно с первым-четвертым управляющими входами управляемого арифметического модуля, вторые входы первого, третьего и четвертого элементов И подключены соответственно к первому, второму и третьему информационным входам управляемого арифметического модуля, первые входы пятого и шестого элементов И соединены соответ- ственно с вторым и третьим управляющими входами управляемого арифметического модуля, первый вход десятого элемента И - с первым информационным входом управляемого арифметического модуля, второй вход второго элемента И - с первым входом седь- мого элемента И и.выходом десятого элемента И, первый вход второго элемента И и второй вход седьмого элемента И подключены соответственно к первому и второму выходам управляемого арифметического модуля, а также к инверсному и прямому выходам дополнительного триггера, прямой и инверсный входы которого подключены соответственно к выходам третьего и четвертого элементов ИЛИ, пятый управля- ющий вход управляемого арифметического

модуля соединен с вторым входом четвертого элемента ИЛИ, первый вход которого соединен с выходом одиннадцатого элемента И, второй вход которого соединен с инверсным выходом основного триггера и третьим выходом управляемого арифметического модуля, четвертый информационный вход которого подключен к второму входу девятого элемента И. первый вход которого соединен с шестым управляющим входом управляемого арифметического модуля, пятый и шестой информационные входы которого соединены соответственно с вторыми входами пятого и шестого элементов И, а седьмой управляющий вход - с четвертым входом второго элемента ИЛИ, четвертый выход управляемого арифметического модуля соединен с прямым выходом основного триггера, второй вход восьмого и первый вход одиннадцатого элементов И-- соответственно с девятым и восьмым управляющими входами управляемого арифметического модуля, пятый и шестой выходы которого соединены соответственно с выходами седьмого и второго элементов И, отличающийся тем, что, с целью увеличения быстродействия при выполнении операции сложения двух двоичных операндов, в устройство введены сумматор, двенадцатый и тринадцатый элементы И, второй вход двенадцатого и первый вход тринадцатого элементов И соединены с десятым управляющим входом управляемого арифметического модуля, первый вход двенадцатого и второй вход тринадцатого элементов И соединены соответственно с единичными выходами основного и дополнительного триггеров, первый и второй входы сумматора под к л ю- - чены соответственно к выходам двенадцатого и тринадцатого элементов И, а третий вход сумматора - к седьмому информационному входу управляемого арифметического модуля, седьмой и восьмой выходы которого соединены соответственно с вторым и первым выходами сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1988 |

|

SU1585792A2 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Управляемый логический модуль | 1980 |

|

SU962923A1 |

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| Многофункциональный регистр | 1988 |

|

SU1624529A1 |

| Управляемый логический модуль | 1984 |

|

SU1196851A1 |

| Управляемый логический модуль | 1985 |

|

SU1273916A1 |

| Арифметическое устройство по модулю три | 1991 |

|

SU1797116A1 |

Изобретение относится к вычислительной технике и предназначено для реализации узлов и устройств цифровых вычислительных машин методами интегральной технологии со средним и большим уровнями интеграции. Целью изобретения является увеличение быстродействия управляемого арифметического модуля при выполнении операции сложения двух двоичных операндов. Управляемый арифметический модуль, содержащий основной и дополнительный триггеры 1 и 2, одиннадцать элементов И Зт13, четыре элемента ИЛИ 14-17, выполняет операцию сложения двух двоичных операндов в 9 раз быстрее с помощью вновь введенных сумматора 20, двенадцатого и тринадцатого элементов И 18 и 19. 2 ил.

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Управляемый арифметический модуль | 1988 |

|

SU1585792A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-11-21—Подача