w

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов двух величин | 1983 |

|

SU1140133A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1986 |

|

SU1327097A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1987 |

|

SU1425663A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТОВ ТРЕХ ВЕЛИЧИН | 1992 |

|

RU2024938C1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух величин | 1989 |

|

SU1661799A2 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| Линейно-круговой интерполятор | 1985 |

|

SU1302241A2 |

| Устройство для управления многокоординатным оборудованием | 1987 |

|

SU1427334A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ РАЗНОСТИ КВАДРАТОВ ДВУХ ВЕЛИЧИН | 1992 |

|

RU2022359C1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в аналоговых вычислительных машинах, а также в системах автоматики, например, для вычислений длины двумерного вектора по его составляющим. Устройство для извлечения квадратного корня из суммы квадратов двух величин содержит пять блоков выделения модуля 1-5, блок выделения минимального сигнала 6, блок выделения максимального сигнала 7, инвертор 8, делитель 9, четыре сумматора 10-13. 1 ил,

00

со

V4

ГО

3

Изобретение относится к вычислительной технике и автоматике, оно может быть использовано в аналоговых вычислительных машинах, а также в системах автоматики, например, для вычисления длины двумерного вектора по его составляющим.

Цель изобретения - повышение точности,

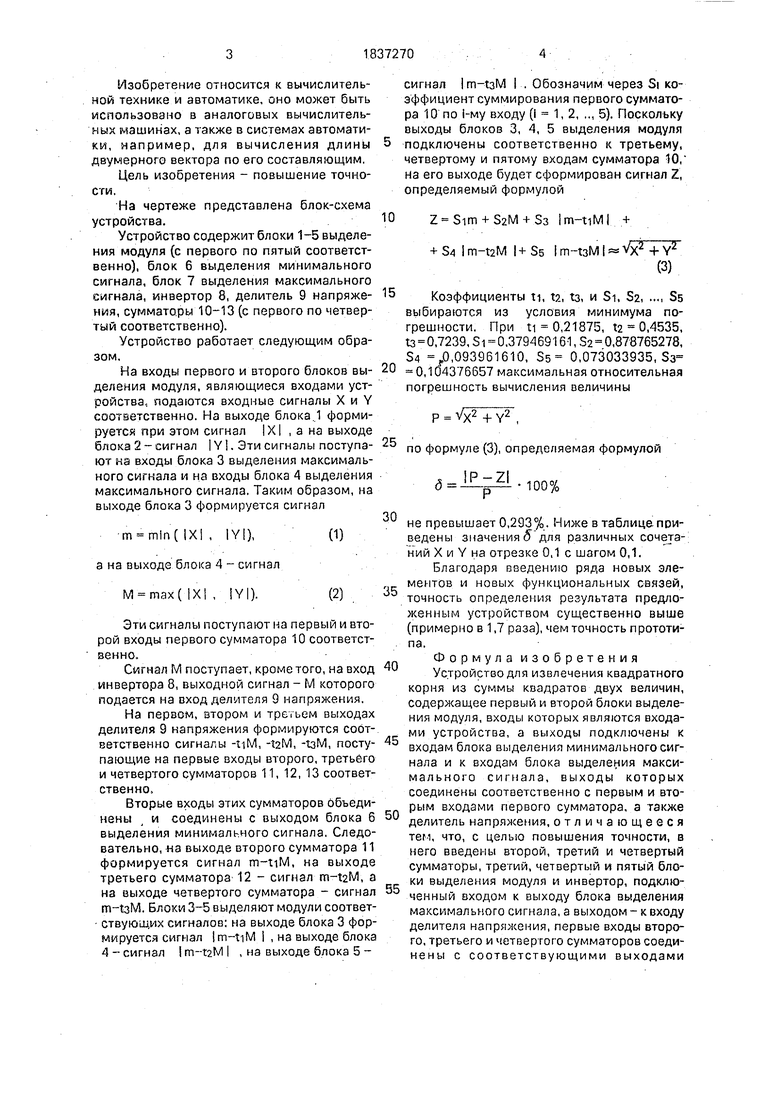

На чертеже представлена блок-схема устройства.

Устройство содержит блоки 1-5 выделения модуля (с первого по пятый соответственно), блок 6 выделения минимального сигнала, блок 7 выделения максимального сигнала, инвертор 8, делитель 9 напряжения, сумматоры 10-13 (с первого по четвертый соответственно).

Устройство работает следующим образом.

На входы первого и второго блоков выделения модуля, являющиеся входами устройства, подаются входные сигналы X и Y соответственно. На выходе блока. 1 формируется при этом сигнал IXI , а на выходе блока 2 - сигнал IYI. Эти сигналы поступают на входы блока 3 выделения максимального сигнала и на входы блока 4 выделения максимального сигнала. Таким образом, на выходе блока 3 формируется сигнал

m min(|Xl, IYI),

(D

а на выходе блока 4 - сигнал

M max( |Xi , IYI).(2)

Эти сигналы поступают на первый и второй входы первого сумматора 10 соответственно.

Сигнал М поступает, кроме того, на вход инвертора 8, выходной сигнал - М которого подается на вход делителя 9 напряжения.

На первом, втором и третьем выходах делителя 9 напряжения формируются соответственно сигналы -tiM, -taM, -1зМ, поступающие на первые входы второго, третьего и четвертого сумматоров 11, 12, 13 соответственно,

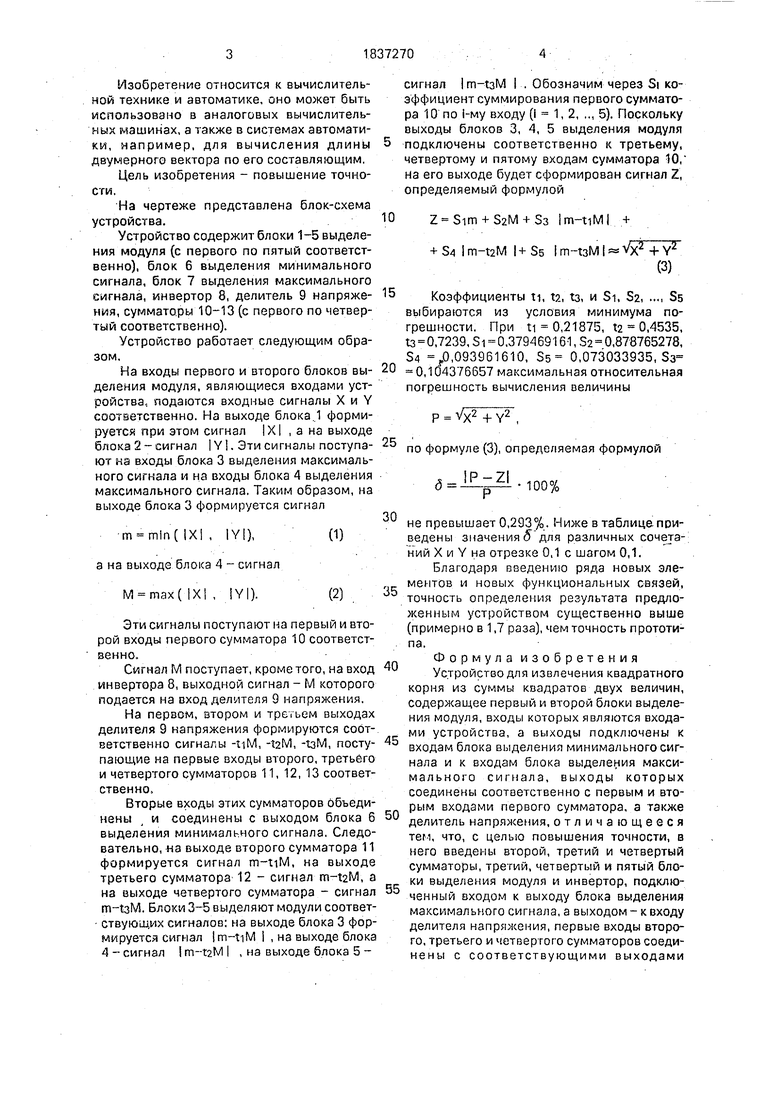

Вторые входы этих сумматоров объединены и соединены с выходом блока 6 выделения минимального сигнала. Следовательно, иа выходе второго сумматора 11 формируется сигнал m-tiM, на выходе третьего сумматора 12 - сигнал m-taM, a на выходе четвертого сумматора - сигнал m-tsM. Блоки 3-5 выделяют модули соответствующих сигналов: на выходе блока 3 формируется сигнал Im-tiM i , на выходе блока 4 - сигнал m-t2M I , на выходе блока 5 сигнал Im-taM I . Обозначим через Si коэффициент суммирования первого сумматора 10 по -му входу (1 1,2, .,, 5). Поскольку выходы блоков 3, 4, 5 выделения модуля подключены соответственно к третьему, четвертому и пятому входам сумматора 10, на его выходе будет сформирован сигнал Z, определяемый формулой

10

Z Sim + S2M + S3 lm-tiM| +

+ SA I m-taM I + 85 I m-taM I

Vx2 + Y2 (3)

Коэффициенты ti, ta, t3, и Si, Sa, ..., Ss выбираются из условия минимума погрешности. При ti 0,21875, t2 0,4535, 13 0,7239, Si 0,379469161, Sa 0,878765278, 84 ,0,093961610, Ss 0,073033935,53

0,104376657 максимальная относительная погрешность вычисления величины

по формуле (3), определяемая формулой

. юо%

не превышает 0,293%. Ниже в таблице приведены значения 5 для различных сочетаний X и Y на отрезке 0,1 с шагом 0,1.

Благодаря введению ряда новых элементов и новых функциональных связей, точность определения результата предложенным устройством существенно выше (примерно в 1,7 раза), чем точность прототипа.

Формула изобретения Устройство для извлечения квадратного корня из суммы квадратов двух величин, содержащее первый и второй блоки выделения модуля, входы которых являются входами устройства, а выходы подключены к входам блока выделения минимального сигнала и к входам блока выделения максимального сигнала, выходы которых соединены соответственно с первым и вто0

рым входами первого сумматора, а также

делитель напряжения, отличающееся тем, что, с целью повышения точности, в него введены второй, третий и четвертый сумматоры, третий, четвертый и пятый бло- ки выделения модуля и инвертор, подключенный входом к выходу блока выделения максимального сигнала, а выходом - к входу делителя напряжения, первые входы второго, третьего и четвертого сумматоров соеди- нены с соответствующими выходами

518372706

делителя напряжения, вторые входы объе-его, четвертого и пятого блоков выделения

динены и соединены с выходом блока выде-модуля, выходы которых подключены соотления минимального сигнала, а выходыветственно к третьему, четвертому и пятому

соединены с входами соответственно треть-входам первого сумматора.

Авторы

Даты

1993-08-30—Публикация

1990-10-08—Подача