-J

-1

8

СП

О) О) со

Изобретение относится к вычисли- ;тельной технике и может быть исполь- |зовано в различных преобразователях, la. также в устройствах обработки дне- кретной информации.

Цель изобретения - повышение точ-j ности вычисления.

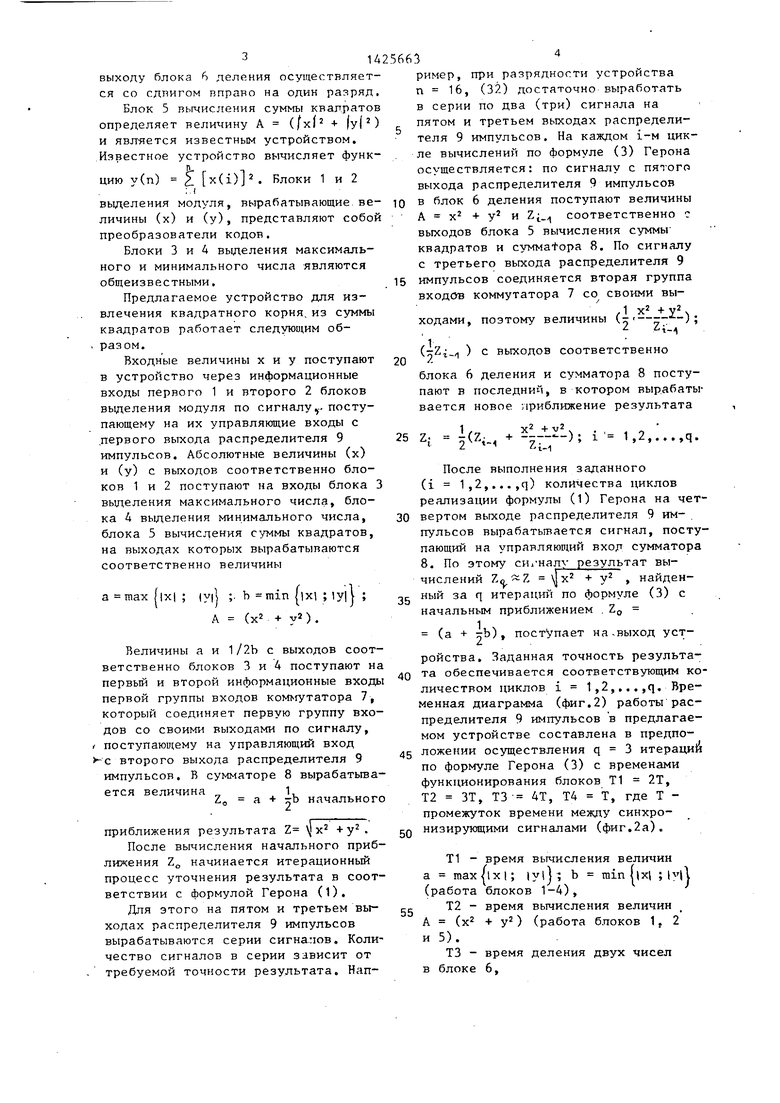

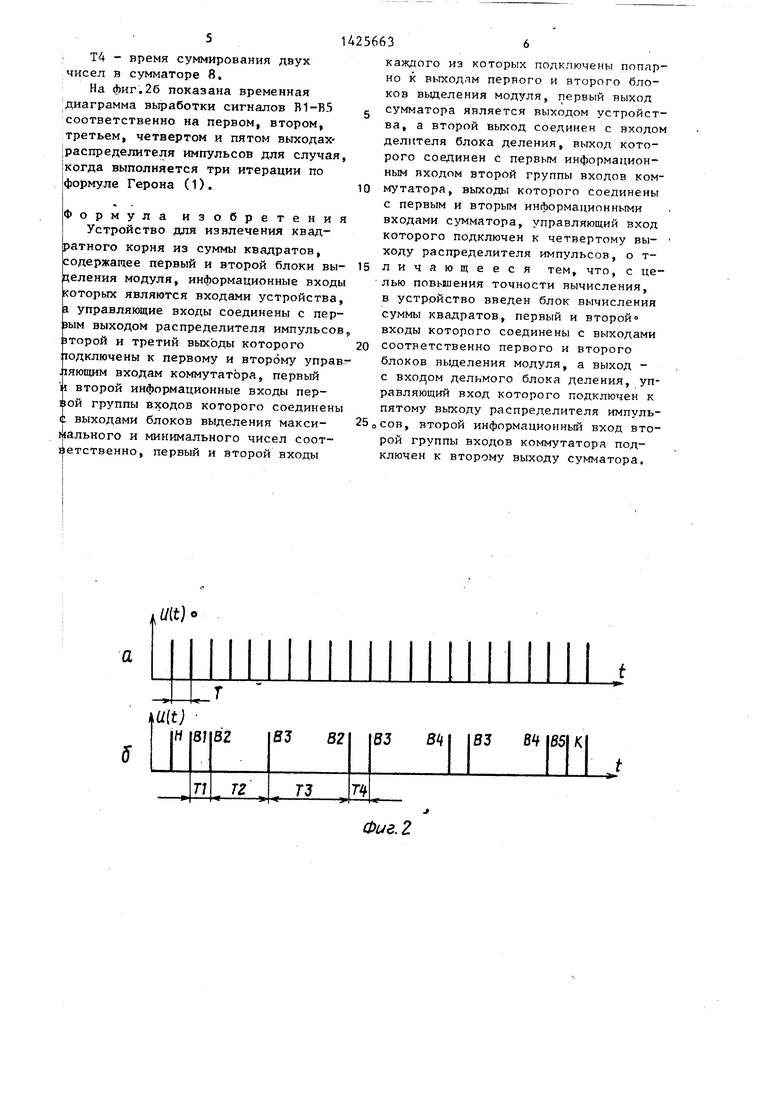

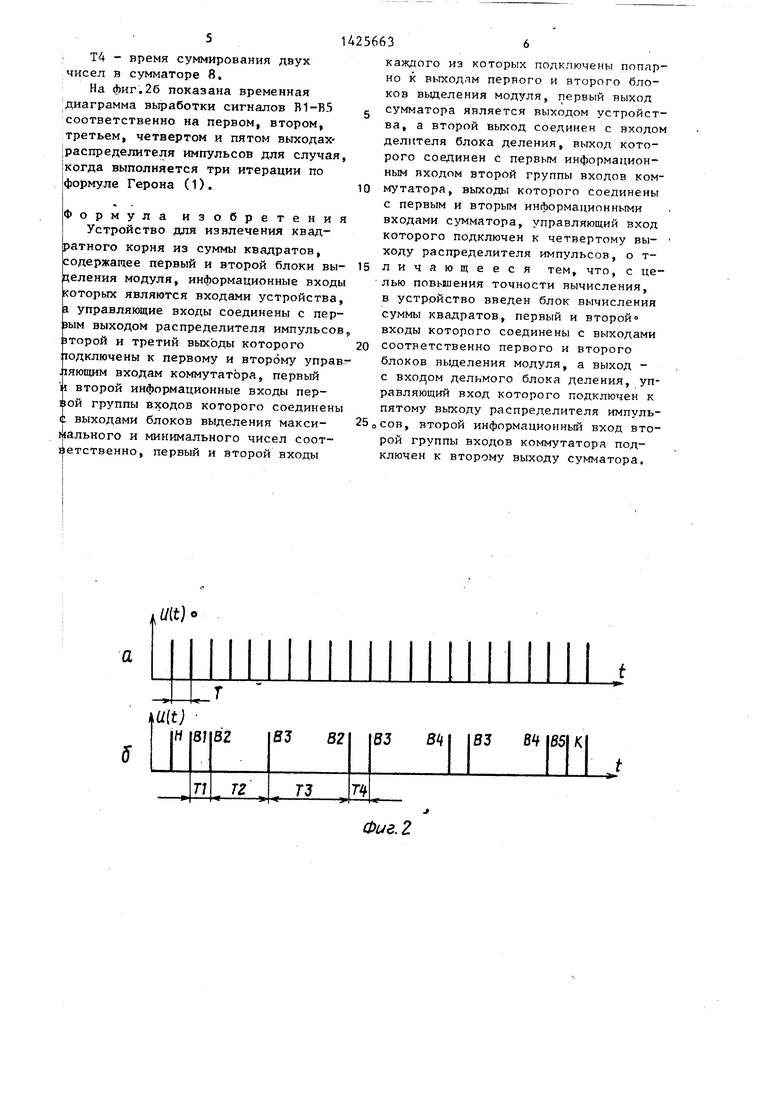

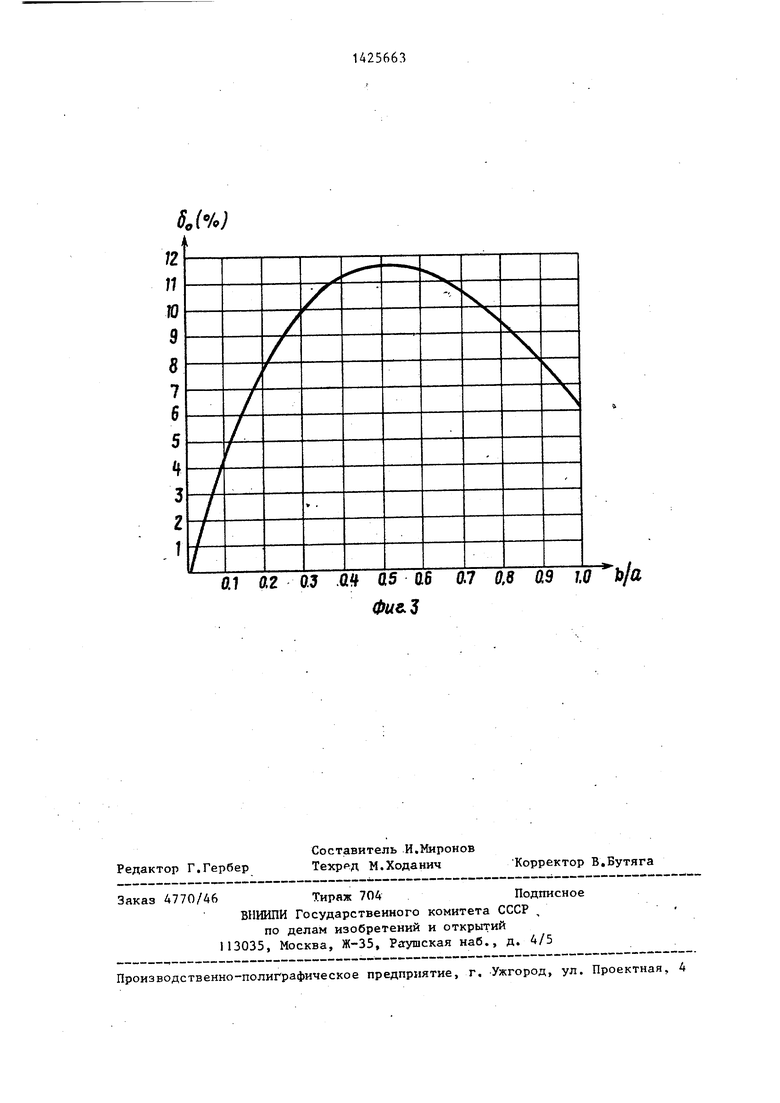

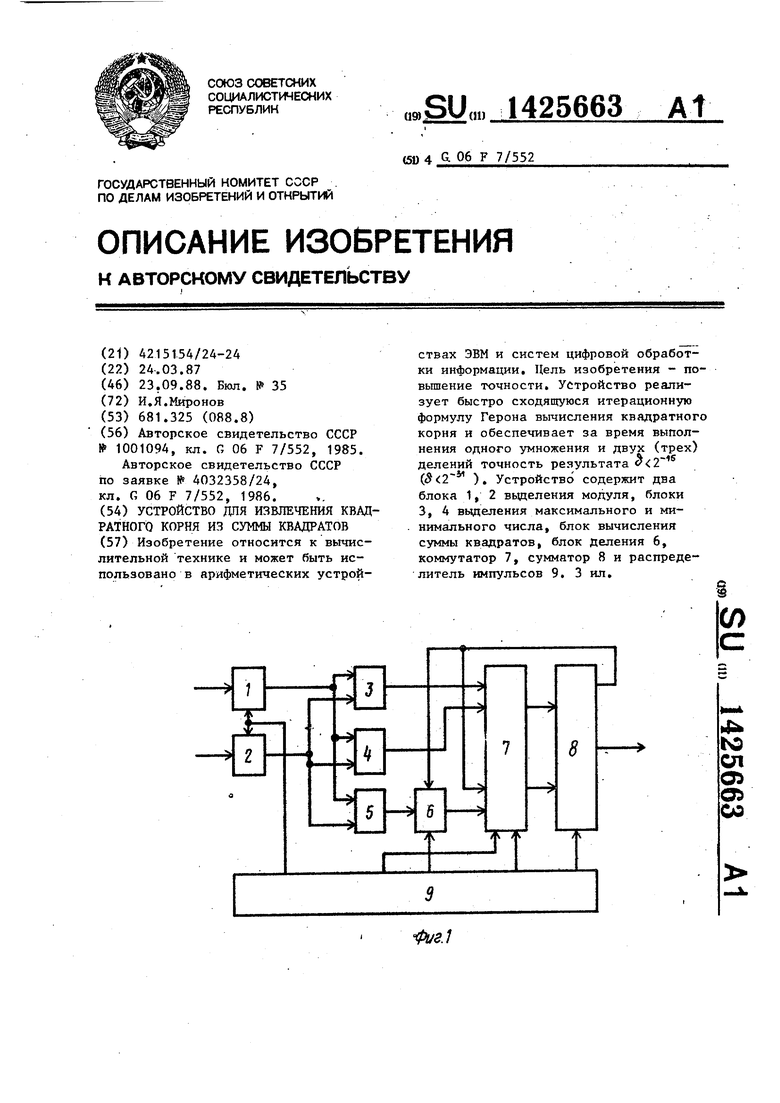

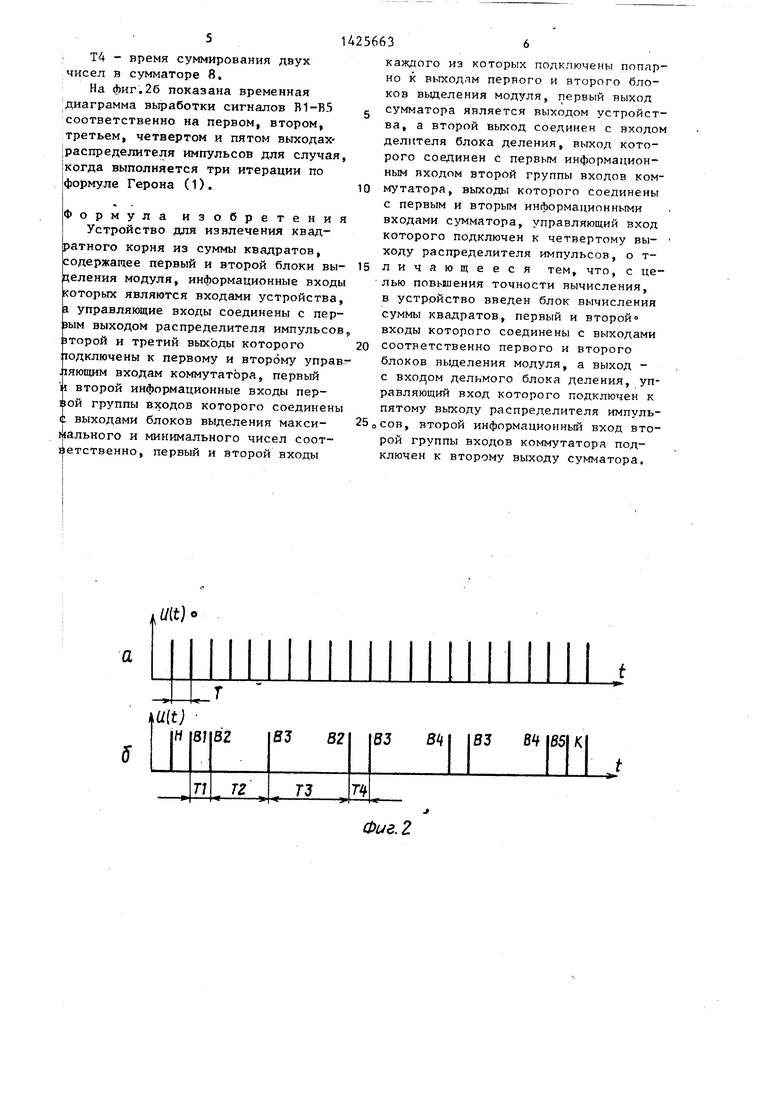

На фиг.1 представлена функцио- Мальная схема устройства} на фиг.2 Ьременная диаграмма работы устройства; на фиг.З - график точности начального приближения результата.

Устройство для извлечения квадрат- яого корня из суммы квадратов со- держит первый 1 и второй 2 блоки выделения модуля, блок 3 вьаделения мак :имального числа, блок 4 выделения инимального числа,, блок 5 вычисления уммы квадратов, блок 6 деления, комта тор 7, сумматор 8,. распределитель импульсов. I Предлагаемое устройство производит вычисление квадратного корня из (;уммы квадратов двух чисел по итера- ционной формуле Герона

2 +v2

z (Zi.,

+ iJLZl -

Z.;

(1)

I a inax||x|)|y|j -b min {lx ; lyij ,

1| де X, у - входные величиныJ Z - точное значение резулы : . тата;

4 и Z; - приближенные значения результата перед и после

выполнения i-й итерации} а, b - максимальные и минималь- : ные значения из чисел

1x1 , 1у .

Относительная ошибка результата вычисляется по формуле

..

Zi - Z

(2)

За начальное приближение результата Принимаем величину

2о (); 4- ,8% 2. (3)

График точности начального приближения Zto в зависимости от соотношения - приведен на фиг.З. а

Известно, что итерационный процесс вычислений по формуле Герона (1) быстро сходится к точному значению функции Z х + у , при этом после У каждого цикла вычислений количество верных знаков увеличивается более, чем в два раза, а относительная ошибка изменяется по закону

;.,.2- 2(4)

Начальное приближение в соответствии с (3) имеет точность 2 , поэтому имеем

,2- ,2-, ,2- §,2; , . .

Б настоящее время широко используется 16-разрядные и 32-разрядные серийные ЭВМ типа АСВТ-М. Для получения точности, при которой ошибка меньше цены младшего разряда при вычислении 16-разрядногС (32- разрядного) результата Z | х + у достаточно выполнить две (три) итерации по формуле Герона (1), принимая за начальное приближение вели- чину Zo по соотношению (3) с точностью ,8%.

Из формуль (3) видно, что для вычисления начального приближения Z необходимо выделить величины

||Х1 ; iyi ; (х( ; у , сдвинуть величину b min (lx| ; I вправо на один разряд, вычислить

Z (а + |ь).

При вычислениях по итерационной формуле Герона величины слагаемых

„ Х2 4-V2

Zj, ; тагсже перед поступле i-t

нием в сумматор 8 должны быть сдвинуты вправо на один разряд. Это выполнено в устройстве путем жесткой коммутации следукяцим образом.

Выход блока 4 выделения минимального числа подключен к второьгу информационному входу первой группы входов коммутатора 7 со сдвигом впра во на один разряд.

Подключение первого и второго информационных входов второй группы входов коммутатора 7 соответственно к второму выходу сумматора 8 и к

выходу блока - деления осуществляется со сдпигом вправо на один разряд. Блок 5 вьмисления суммы квадратов определяет величину А (fxl -t- |уП ) и является известным устройством. Известное устройство вычисляет функцию

у(п) x(i)2. Блоки 1 и 2

выделения модуля, вырабатывающие величины (х) и (у), представляют собой преобразователи кодов.

Блоки 3 и 4 выделения максимального и минимального числа являются общеизвестными.

Предлагаемое устройство для извлечения квадратного корня, из суммы квадратов работает следующим об- разом.

Входные величины хну поступают в устройство через информационные входы первого 1 и второго 2 блоков выделения модуля по сигналу., поступающему на их управляющие входы с .первого выхода распределителя 9 импульсов. Абсолютные величины (х) и (у) с выходов соответственно блоков 1 и 2 поступают на входы блока 3 выделения максимального числа, блока Д выделения минимального числа, блока 5 вычисления суммы квадратов, на выходах которых вырабатываются соответственно величины

a max|lx|; (уА ;. h min |lxi ; 1у| V ; А (х + у2) .

Величины а и 1/2Ь с выходов соответственно блоков 3 и 4 поступают на первый и второй информационные входы первой группы входов коммутатора 7, который соединяет первую группу входов со своими выходами по сигналу, поступающему на управляющий вход с второго выхода распределителя 9 импульсов. В сумматоре 8 вырабатывается величина 1,

Za а b начального

приближения результата Z х

После вычисления начального приближения ZQ начинается итерационный процесс уточнения результата в соответствии с формулой Герона (1).

Для этого на пятом и третьем выходах распределителя 9 импульсов вырабатываются серии сигна.тюв. Количество сигналов в серии зависит от требуемой точности результата. Например, при разрядности устройства п 16, (32) достаточно выработать в серии по два (три) сигнала на пятом и третьем выходах распределителя 9 импульсов. На каждом L-M цикле вычислений по формуле (3) Герона осуществляется: по сигналу с пятого выхода распределителя 9 импульсов

в блок 6 деления поступают величины А х + у и Zi соответственно с выходов блока 5 вычисления суммы квадратов и сумматора 8. По сигналу с третьего выхода распределителя 9

импульсов соединяется вторая группа входов коммутатора 7 со своими вы..1 х2 +у2.

ходами, поэтому величины ();

t-

/ I г,

(-Z ) с выходов соответственно

1. 2

блока 6 деления и сумматора 8 поступают в последний, в котором вырабатывается новое приближение результата

Z. i(Z. + - -----); i 1,2,..,,q, f- I 1-1

После выполнения заданного (i 1,2,,..,q) количества циклов реализации формулы (1) Герона на четвертом выходе распределителя 9 импульсов вырабатьгоается сигнал, поступающий на управляющий вход сумматора 8. По этому CHi Hany результат вычислений Zn Z j х У найденный за q итераций по формуле (3) с начальным приближением . ZQ

(а + Ь), поступает на-выход устройства, Заданная точность результата обеспечивается соответствующим количеством циклов i 1,2q. Вреенная диаграмма (фиг.2) работы распределителя 9 импульсов в предлагаемом устройстве составлена в предположении осуществления q 3 итераций по формуле Герона (3) с временами функционирования блоков Т1 2Т, Т2 ЗТ, ТЗ- 4Т, Т4 Т, где Т - промежуток времени между синхронизирующими сигналами (фиг,2а).

11 - время вычисления величин max|lx|; lyl); b rain Ьх| ; ivA забота блоков 1-4),

Т1 - время вычисления величин а

(раб

g Т2 - время вычисления величин А (х « у ) (работа блоков 1, 2 и 5).

ТЗ - время деления двух чисел в блоке 6,

5

Т4 - время суммирования двух чисел в сумматоре 8.

На фиг.2б показана временная ;диаграмма вьфаботки сигналов В1-В5 соответственно на первом, втором, третьем, четвертом и пятом выходах распределителя импульсов для случа |когда выполняется три итерации по формуле Герона (1).

Формула изобретения I Устройство для извлечения квадратного корня из суммы квадратов, содержащее первый и второй блоки вы- целения модуля, информационные входы которых являются входами устройства, а управляющие входы соединены с пер- зым выходом распределителя импульсов,, :зторой и третий выходы которого подключены к первому и второму управ- ляющим входам коммутатора, первый и второй информационные входы пер- |ой группы входов которого соединены (; выходами блоков выделения макси- 1||ального и минимального чисел соот- 1 етственно, первый и второй входы

каждого из которых подключены попарно к выходам первого и второго блоков выделения модуля, первый выход сумматора является выходом устройства, а второй выход соединен с входом делителя блока деления, выход которого соединен с первым информационным входом второй группы входов коммутатора, выходы которого соединены с первым и вторым информационными входами сумматора, управляющий вход которого подключен к четвертому вы- ходу распределителя импульсов, о тличающееся тем, что, с целью повышения точности вычисления, в устройство введен блок вычисления суммы квадратов, первый и второй входы которого соединены с выходами

соответственно первого и второго блоков выделения модуля, а выход - с делимого блока деления, управляющий вход которого подключен к пятому выходу распределителя импульо сов, второй информационный вход второй группы входов коммутатора подключен к второму выходу сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов | 1986 |

|

SU1327097A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1267409A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1522198A1 |

| Устройство для извлечения корня четвертой степени | 1985 |

|

SU1262487A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| Устройство для извлечения квадратного корня и его обратной величины | 1988 |

|

SU1545218A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1983 |

|

SU1116428A2 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Функциональный преобразователь | 1986 |

|

SU1456951A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и систем цифровой обработки информации. Цель изобретения - повышение точности. Устройство реализует быстро сходящуюся итерационную формулу Герона вычисления квадратного корня и обеспечивает за время выполнения одного умножения и двух (трех) делений точность результата 2

Фиг.г

ол 0.2 0.5 -Qtt as аб а о.в аэ ю ь/а

Фие.

| Устройство для извлечения квадратного корня из суммы квадратов | 1981 |

|

SU1001094A1 |

| С, 06 F 7/552, 1985 | |||

| Авторское свидетельство СССР по заявке № 4032358/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-24—Подача