11

Изобретение относится к вычислительной технике и может быть использовано в различных функциональнь.х преобразователях, а также -в устрой- ствах обработки дискретной информации.

Цель изобретения - повьппение быстродействия и точности вычисления.

На фиг. 1 изображена функциональная схема устройства; на фиг, 2 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит первый 1 и второй 2 блоки выделения модуля, блок 3 выделения максимального числа, блок А выделения минимального числа, квадратор 5, блок 6 деления коммутатор 7, сумматор 8 и распределитель 9 импульсов.

Устройство производит вычисление квадратного корня из суммы квадратов двух чисел по приближенной формуле

Z.. V х2 +y2 Va +b ;

пр Znp +

35. 64

а+

81

256

b

np

a-M«Kc|lxl;ly(; ,Д1х|;|у1Ь (1) где к,у - входные величины;

Z - точное значение- результата; приближенное значение результата;а,Ь - максимальное и минимальное значение из чисел хр, ly. Относительная ошибка результата вычисляется по формуле

(J .nf Z

(2)

Для вывода (1) используем итерационный процесс Герона для извлечения квадратного корня из числа А:

А I .„ . А , 1

,.,-fi-). (Z..,

+Ъ

),

(3)

где i - очередной номер итерации;

7 1-1

Z. - приближенные значения результата до и после вьшолнения i-й итерации.

Принимая за начальное приближение результата величину

7 Са+ 51- . К) о 256

а также используя формулу Герона (3)j получим

а+

81

256

(4)

K,t

Формула (4) обеспечивает точность вьгаисления результата, при которой абсолютное значение относительной ошибки не превосходит величины

,27%. .1 Экспериментально, методом подбора,

установлено, что формула (1) обеспечивает более высокую точность вычисления квадратного корня из суммы квадратов двух чисел, при этом абсолютное значение относительной ошибки

не превосходит величины Znp -Z 1.

(г

пр1

,ii%.

ошибка о

зависит только

т.е.. формула (1) позволяет повысить точность результата в 2,5 раза по 25 сравнению с формулой (4).

Легко показать, что относительна

-Z пр Z

от величины Ъ/а. 30

dV,,

rip

40 Как видно из формулы (1), вычисление квадратного корня из суммы квад- ратов двух чисел в предлагаемом устройстве можно производить за один цикл работы квадратора 5 и блока 6

45 деления, а также операций выделения модуля, определения максимального и минимального значений а,Ь из чисел i X 1; J. у 1-5 сдвигов и суммирования

50 В устройстве производится вычисление следзлощих величин:

fi i;iyilitivii i;iyi ;

- -- -

)-b;

)-f.

Сдвиг двоичных чисел в предлагаемом устройстве производится путем жесткой коммутации входов и выходов следующим образом.

Выход блока 4 вьщеления минималького числа подключен к второму, третьему и чeтвepтo fy информационным входам первой группы входов коммутатора 7 со сдвигом вправо соответственно на 2,4,8 разрядов. Выход блока 6 деления подключен, к второму, третьему и четвертому информационным входам второй группы входов коммутатора 7 со сдвигом вправо соответственно на 1,5,6 разрядов.

Блоки 1 и 2 выделения модуля, вы

рабатывающие величины {х|; |у|, представляют собой преобразователи кодов

Сумматор 8 (с коммутатором на выходе), производит суммирование поступающих на его информационные входы четьфех чисел по сигналам с распределителя импульсов на управляющие входы коммутатора 7. Выдача результа тов суммирования производится по сигналам, поступающим на управляющие входы коммутатора на выходе сумматора 8 с третьего и пятого выходов распределителя 9 импульсов. Блоки 3 и 4 вьщеления максимального и минимального числа являются общеизвестными.

Устройство для извлечения квадратного корня из суммы квадратов работает следующим образом.

Входные величины х,у поступают в устройство через информационные входы первого 1 и второго 2 блоков выделения модуля по сигналу, поступающем на их управляющие входы с первого выхода блока 9 управления. Абсолютные величины 1x1; 1 у | с выходов блоков 1 и 2 выделения модуля поступают на входы блока 3 вьщеления максималь- .кого числа и блок 4 вьщеления минимального числа, на выходах которых вырабатываются соответственно величины

а wawflxl; |у| ; Ь мин{|х| ; |у| .

Величина Ь м„н 1х|;1у1Т) с выхода

блока.4 выделения минимального числа поступает в квадратор 5, который производит вычисление величины Ь. Одновременно величина а с выхода блока 3 вьщеления максимального числа и величины 1/4Ь; 1/16Ь; 1/25бЬ с выхода блока 4 вьщеления минимального числа поступают на все четыре информационных входа первой группы

входов коммутатора 7, который соеди- няет первую группу входов со своими выходами по сигналу поступающему на свой первый управляющий вход с второго выхода распределителя 9 импульсов, В сумматоре 8 производится вычисление величины

10

d(a+ I b 1 Ы236 Ь) (а |зб Ь).

По сигналу, поступающему с третьего выхода распределителя импульсов на первый управляющий вход сумматора 8, в последнем открьшается допол- нительный выход, по которому величина

81

Ъ()

поступает на вход делителя блока 6 деления, на вход делимого которого поступает величина Ь с выхода квадратора 5. Блок 6 деления вырабатывй- ет величину

Ь. Ь

d

а+

81 256

25

По сигналу с четвертого выхода блока 9, поступалощего на второй уп- равляющий вход коммутатора 7, в по- 30 следнем соединяется вторая группа входов с выходами, поэтому величина млкс ( 1УП выхода блока 3 вьщеления максимального числа, а также

величины

1

f;

1

f. jf

64

с выхЬда

1

2 32

блока 6 деления поступают на информационные входы сумматора 8, который в соответствии с формулой (1) вычисляет результат

f) ,

или

45

256

По сигналу с пятого выхода распределителя 9 импульсов, поступающего на второй управляющий вход сумматора 8, в последнем открьтается основной gQ выход, по которому результат вычисления квадратного корня из суммы квадратов двух чисел, вычисленный по приближенной формуле (1), поступает на выход устройства.

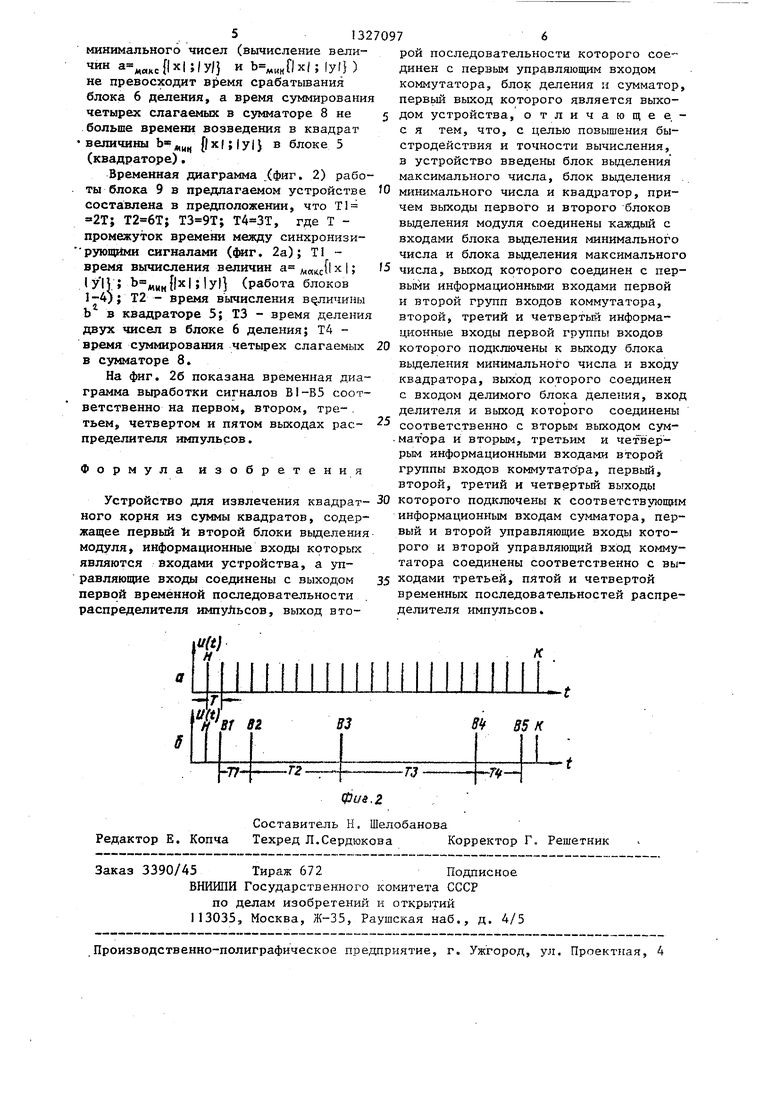

На фиг. 2 изображена временная диаграмма работы устройства в предположении, что суммарное время функционирования блока 5 (квадратор) и блоков 3 и 4 вьщеления максимального и

55

.513270976

минимального чисел (вычисление вели- рой последовательности которого сое«ми fixl;lylj в блоке 5

;|у|} и Ь „„Д|х| ; |у(} ) не превосходит время срабатывания блока 6 деления, а время суммирования четырех слагаемых в сумматоре 8 не больше времени возведения в квадрат

величины Ь (квадраторе).

Временная диаграмма (фиг. 2) работы блока 9 в предлагаемом устройстве составлена в предположении, что Т1 2Т; , где Т - промежуток времени между синхронизи рующйми сигналами (jeir. 2а); Т1 - время вычисления величин а I

Ш

динен с первым управляющим входом коммутатора, блок деления и сумматор, первьш выход которого является выхо5 дом устройства, отличающее, - с я тем, что, с целью повышения быстродействия и точности вычисления, в устройство введены блок вьщеления максимального числа, блок вьщеления . минимального числа и квадратор, причем выходы первого и второго блоков выделения модуля соединены тсаждый с входами блока выделения минимального числа и блока вьщеления максимального

5 числа, выход которого соединен с пер- вьми информа1дионными входами первой и второй групп входов коммутатора, второй, третий и четвертый информационные входы первой группы входов

ly lV; ;|у) (работа блоков

1-4;; Т2 - время вычисления в ичины

Ь в квадраторе 5; ТЗ - время деления

двух чисел в блоке 6 деления; Т4 время суммирования четьфех слагаемых 20 которого подключены к вьпсоду блока

в сумматоре 8.вьщеления минимального числа и входу

На фиг. 26 показана временная дна- квадратора, грамма выработки сигналов BI-B5 соответственно на первом, втором, тре25

тьем, четвертом и пятом выходах распределителя импульсов.

Формула изобретения

выход которого соединен с входом делимого блока деления, вход делителя и выход которого соединены соответственно с вторым выходом сум- матЪра и вторым, третьим и четв ер- рьм информационными входами второй группы входов коммутатора, первьй, второй, третий и четвертый выходы

Устройство для извлечения квадрат- ЗО которого подключены к соответствующим ного корня из суммы квадратов, содер- информационным входам сумматора, первый и второй управляющие входы которого и второй управляющий вход коммутатора соединены соответственно с вы 35 ходами третьей, питой и четвертой временных последовательностей распределителя импульсов.

жащее первый ti второй блоки вьщеления модуля, информационные входы которых являются входами устройства, а управляющие входы соединены с выходом первой временной последовательности распределителя импуЛьсов, выход втоU(t) ft

Фиа.2

Составитель Н, Шелобанова Редактор Е. Копча Техред Л.Сердюкова Корректор Г. Решетник

Заказ 3390/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

динен с первым управляющим входом коммутатора, блок деления и сумматор, первьш выход которого является выходом устройства, отличающее, - с я тем, что, с целью повышения быстродействия и точности вычисления, в устройство введены блок вьщеления максимального числа, блок вьщеления . минимального числа и квадратор, причем выходы первого и второго блоков выделения модуля соединены тсаждый с входами блока выделения минимального числа и блока вьщеления максимального

числа, выход которого соединен с пер- вьми информа1дионными входами первой и второй групп входов коммутатора, второй, третий и четвертый информационные входы первой группы входов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов | 1987 |

|

SU1425663A1 |

| Устройство для адаптивного скользящего сглаживания | 1986 |

|

SU1387017A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1983 |

|

SU1116428A2 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1981 |

|

SU1001094A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1101818A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ И СРАВНЕНИЯ ЭФФЕКТИВНОСТИ ФУНКЦИОНИРОВАНИЯ ОДНОТИПНЫХ ОРГАНИЗАЦИЙ, УЧИТЫВАЮЩЕЕ ВЗАИМОДЕЙСТВИЕ С ДРУГИМИ УРОВНЯМИ СТРУКТУРЫ | 2012 |

|

RU2504831C1 |

| Устройство для определения закона распределения | 1986 |

|

SU1388900A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

Изобретение относится к вычислительной технике и может быть использовано в различных функциональных преобразователях, а также в устройствах обработки дискретной инфорт мации. Цель изобретения - повьшение быстродействия и точности вычисления, что достигается благодаря введению в устройство, содержащее блоки I и 2 выделения модуля, блок 6 деления, коммутатор 7, сумматор 8 и распределитель 9 импульсов, блока 3 выделе- :ния максимального числа, блока 4 выделения минимального числа, квадрато- ра 5 с соответствующим их подключением. 2 ил. (Л Фиг.Г

| Устройство для вычисления функции | 1976 |

|

SU634271A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1981 |

|

SU1001094A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1986-03-03—Подача