Изобретение относится к вычислительной технике, а более конкретно - к устройствам ввода-вывода информации, ис- псльзующим интерфейсы ЕС ЭВМ,

Целью изобретения является устранени

е указанных выше недостатков.

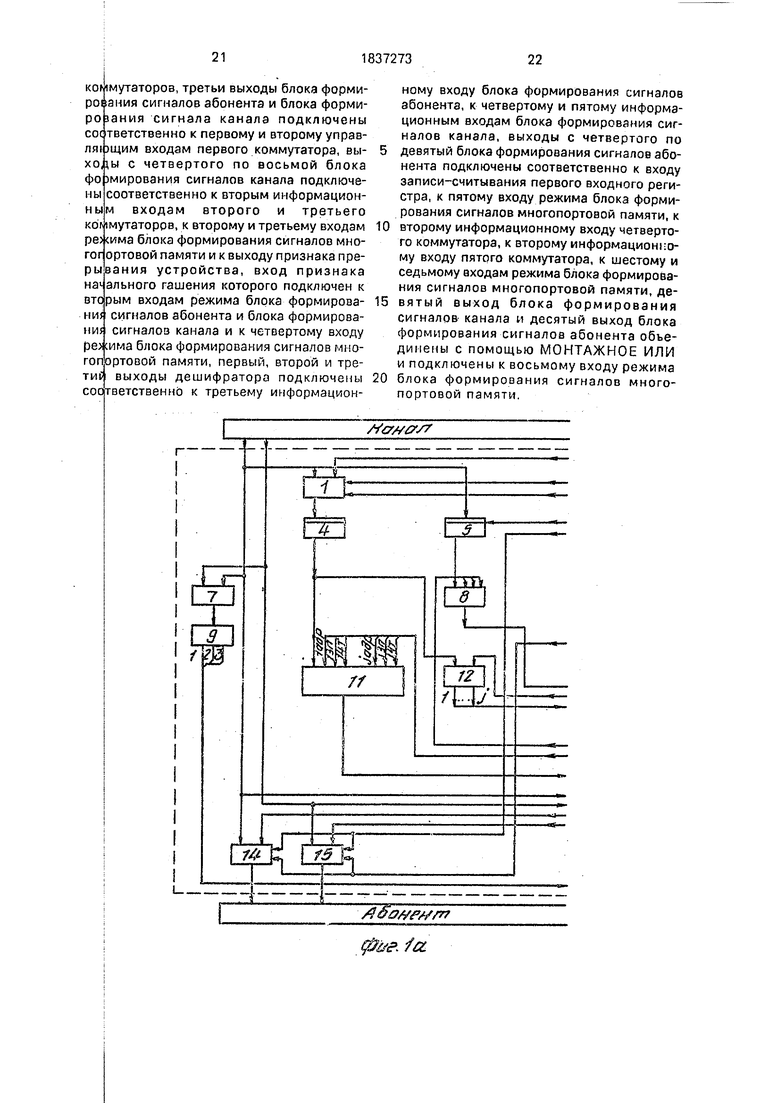

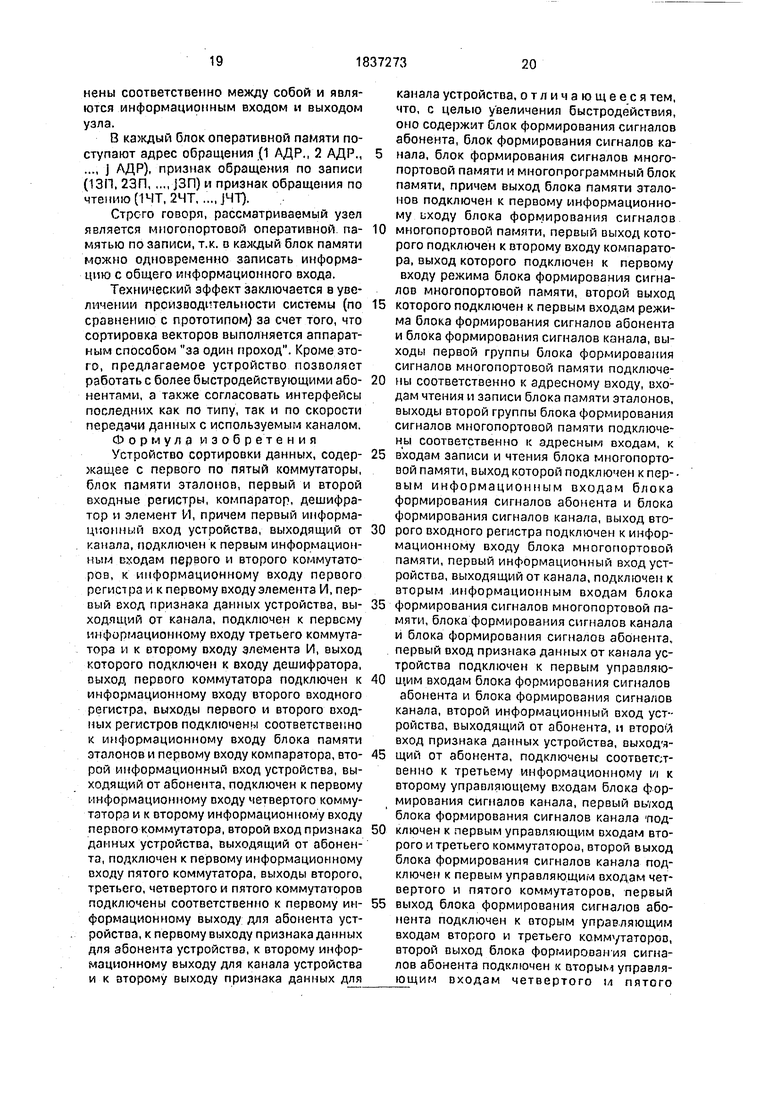

Сущность изобретения заключается в том, что устройство для сортировки данных, содержащее с первого по пятый коммутаторы, блок памяти эталонов, первый и второй входные регистры, компаратор, дешифратор и элемент И, первый информационный вход устройства, выходящий от канала, под- ключен к первым информационным входам пе рвого и второго коммутаторов, к информационному входу первого регистра и к пер- вс му входу элемента И. Первый вход признака данных устройства, выходящий от канала, подключен к первому информационному входу третьего коммутатора и ко второму входу элемента И, выход которого подключен ко входу дешифратора. Выход первого коммутатора подключен к информационному входу второго входного регистра. Выходы первого и второго входных регистров подключены соответственно к информационному входу блока памяти эталонов и к первому входу компаратора. Второй информационный вход устройства, входящий от абонента, подключен к первому информационному входу четвертого коммутатора и ко второму информационному входу первого коммутатора. Второй вход признака данных устройства, выходящий от абонента, подключен к первому информационному входу пятого коммутатора. Выходы второго, третьего, четвертого и пятого коммутаторов подключены соответственно к первому информационному выходу для абонента устройства, к первому выходу признака данных для абонента устройства, ко второму информационному выходу для канала устройства и ко второму выходу признака данных для канала устройства, введены: блок формирования сигналов абонента, блок формирования сигналов канала.

(Л

С

00

ы

|

ю s

W

блок формирования сигналов многопортовой памяти и многопортовый блок памяти. Выход блока памяти эталонов подключен к первому информационному входу блока формирования сигналов многопортовой памяти, первый выход которого подключен ко второму входу компаратора, выход которого подключен к первому входу режима блока формирования сигналов многопортовой памяти, второй выход которого подключен к пэрвым входам режима блока формирования сигналов абонента и блока формирования сигналов канала. Выходы первой группы блока формирования сигналов многопортовой памяти подключены соответственно к адресному входу, входам чтения и записи блока памяти эталонов. Выходы второй группы блока формирования сигналов многопортовой памяти подключены соответственно к адресным входам, ко входам записи и чтения блока многопортовой памяти, выход которой подключен к первым информационным входам блока формиро оания сигналов абонеита и блока формирования сигналов канала. Выход второго входного регистра подключен к информационному входу многопортовой памяти. Первый информационный вход устройства, выходящий от канала.подключен ко вторым информационным входам блока формирования сигналов многопортовой памяти, блока формирования сигналов канала и блока формирования сигналов абонента. Первый вход признака данных от канала устройства подключен к первым управляющим входам блока формирования сигналов абонента и блока формирования сигналов канала. Второй информационный вход устройства, выходящий от абонента, и второй вход признака данных устройства, входящий от абонента, подключены соответственно к третьему информационному и ко второму управляющему входам блока формирования сигналов канала. Первый выход блока формирования сигналов канала подключен к первым управляющим входам второго и третьего коммутаторов. Второй выход блока формирования сигналов канала подключен к первым управляющим входам четвертого и .питого коммутаторов. Первый выход блока формирования сигналов абонента подключен к вторым управляющим входам второго и третьего коммутаторов. Второй выход блока формирования сигналов абонента подключен ко вторым управляющим входам четвертого и пятого коммутаторов. Третьи выходы блока формирования сигналов абонента и блока формирования сигнала канала подключены соответственно, к первому и ко второму управляющим входам первого

коммутатора. Выходы с четвертого по восьмой блока формирования сигналов канала подключены соответственно ко вторым информационным входам второго и третьего

коммутаторов, ко второму и к третьему входам режима блока формирования сигналов многопортовой памяти и к выходу признака прерывания устройства, вход признака начального гашения которого подключен ко

вторым входам режима блока формирования сигналов абонента и блока формирования сигналов канала и к четвертому входу режима блока формирования сигналов многопортовой памяти. Первый, второй и третий выходы дешифратора подключены соответственно к третьему информационному входу блока формирования сигналов абонента, к четвертому и пятому информационным входам блока

формирования сигналов канала. Выходы с четвертого по девятый блоки формирования сигналов абонента подключены соответственно ко входу записи-считывания первого входного регистра, к пятому входу режима

блока формирования сигналов многопортовой памяти, ко второму информационному входу четвертого коммутатора, ко второму информационному входу пятого коммутатора, к шестому и к седьмому входам режима

блока формирования сигналов многопортовой памяти. Девятый выход блока формирования сигналов канала и десятый выход блока формирования сигналов абонента объединены с помощью монтажное ИЛИ

и подключены к восьмому входу режима блока формирования сигналов многопортовой памяти.

В заявляемое устройство введены узлы: многопортовый блок памяти и блоки форми рования сигналов абонента, канала и много- портовой памяти, которые вместе с остальными узлами позволяют расширить область возможного применения устройства за счет работы с более быстродействующими абонентами, а также увеличить производительность устройства по сравнению с прототипом.

Существенные отличия заключаются в том, что введенные узлы: многопортовый блок памяти и блоки формирования сигналов абонента, канала и многопортовой памяти дают новые возможности - позволяют: - согласовать интерфейсы ЕС ЭВМ раз- личных типов (например, между абонентом и предлагаемым устройством может использоваться потоковая передача данных, а между ЭВМ и предлагаемым устройством - со взаимосвязанными сигналами запроса и ответа);

- согласовать скоростные данные абонента и канала (например, передачу информации между абонентом и предлагаемым устройством можно выполнять в более высоком темпе, чем между устройством и калом).

Таким образом, использование указзн- х выше блоков расширяет класс збонен- тоЬ, работающих с данным каналом.

Кроме этого, в ряде случаев появляется возможность увеличить расстояние между Э1 М и абонентом за счет разбиения общей дл лны между указанными устройствами на две части: канал - предлагаемое устройство и предлагаемое устройство - абонент.

При этом длина каждой из частей опре- де 1яется типом используемого интерфейса и максимальными задержками абонента, пр здлагаемого устройства и канала.

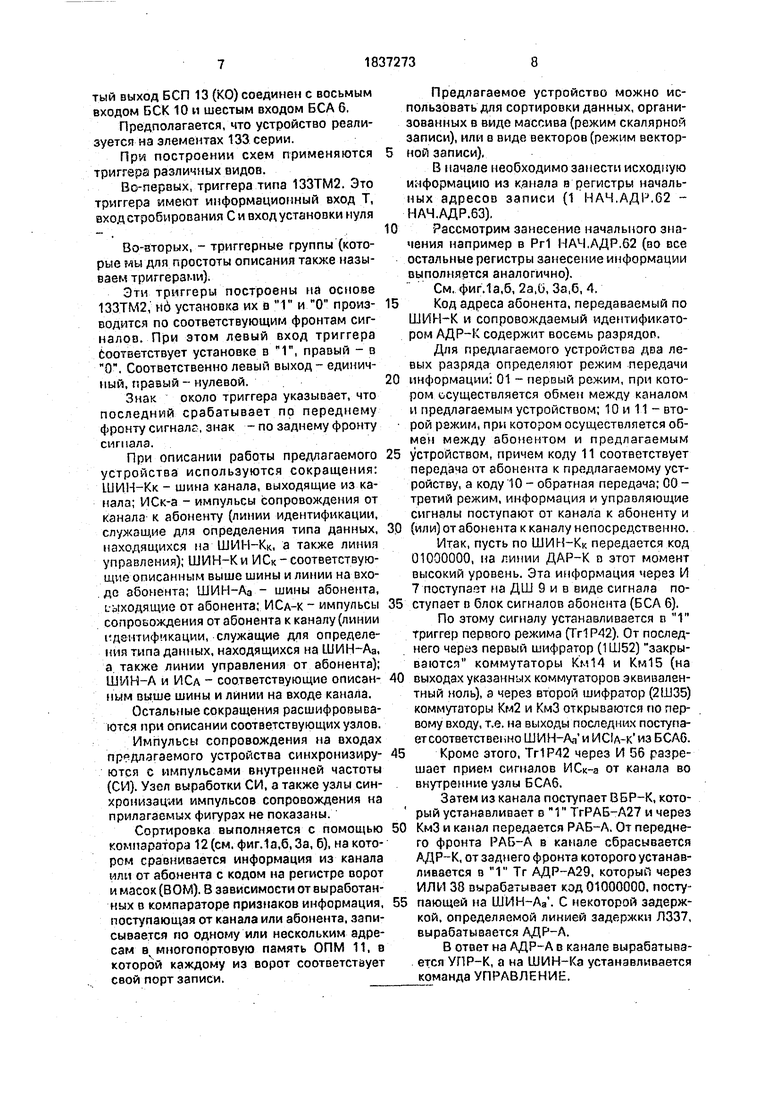

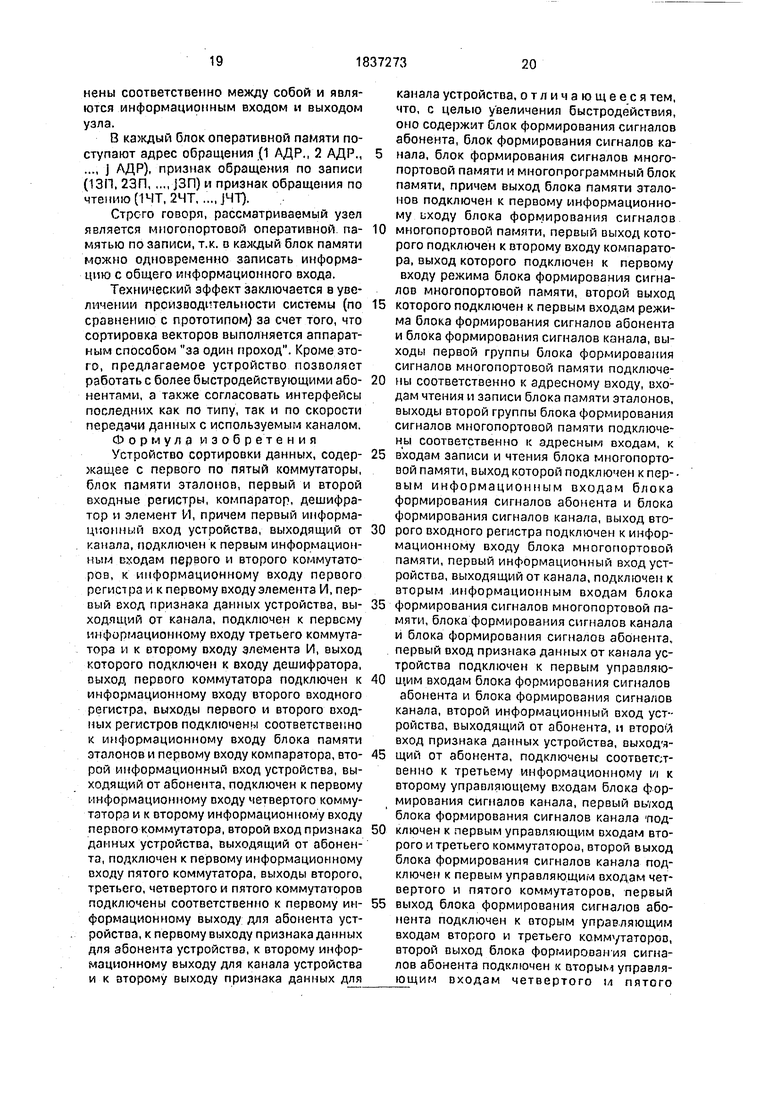

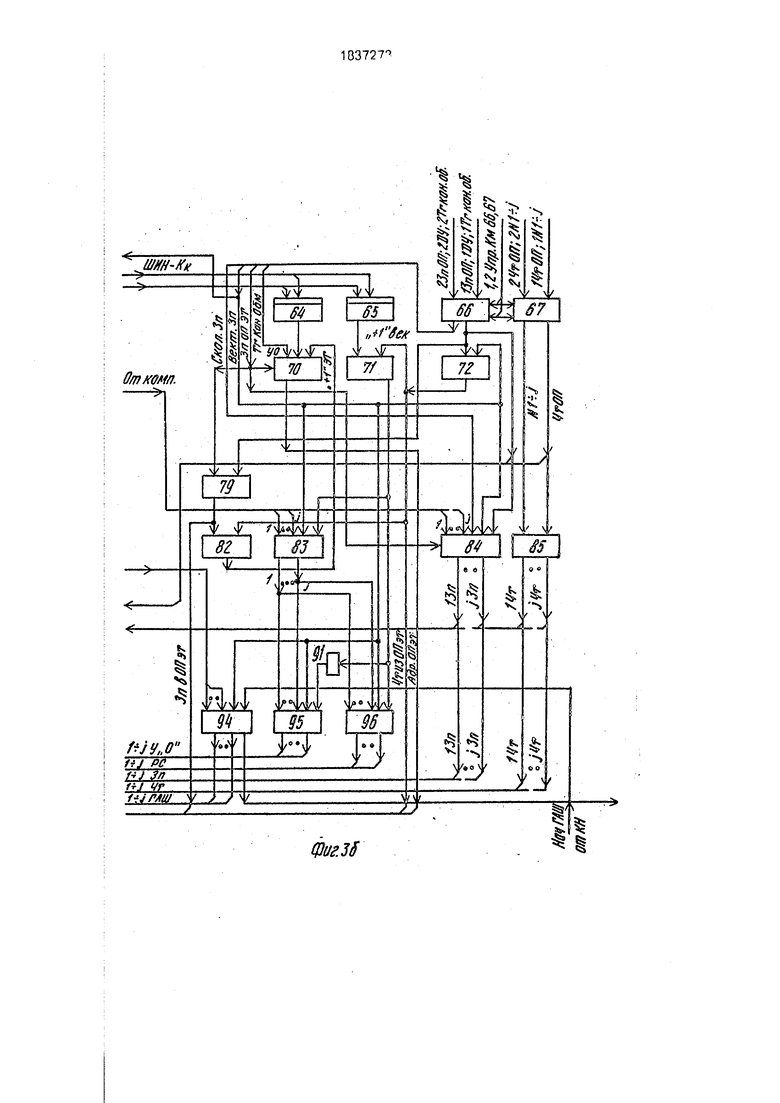

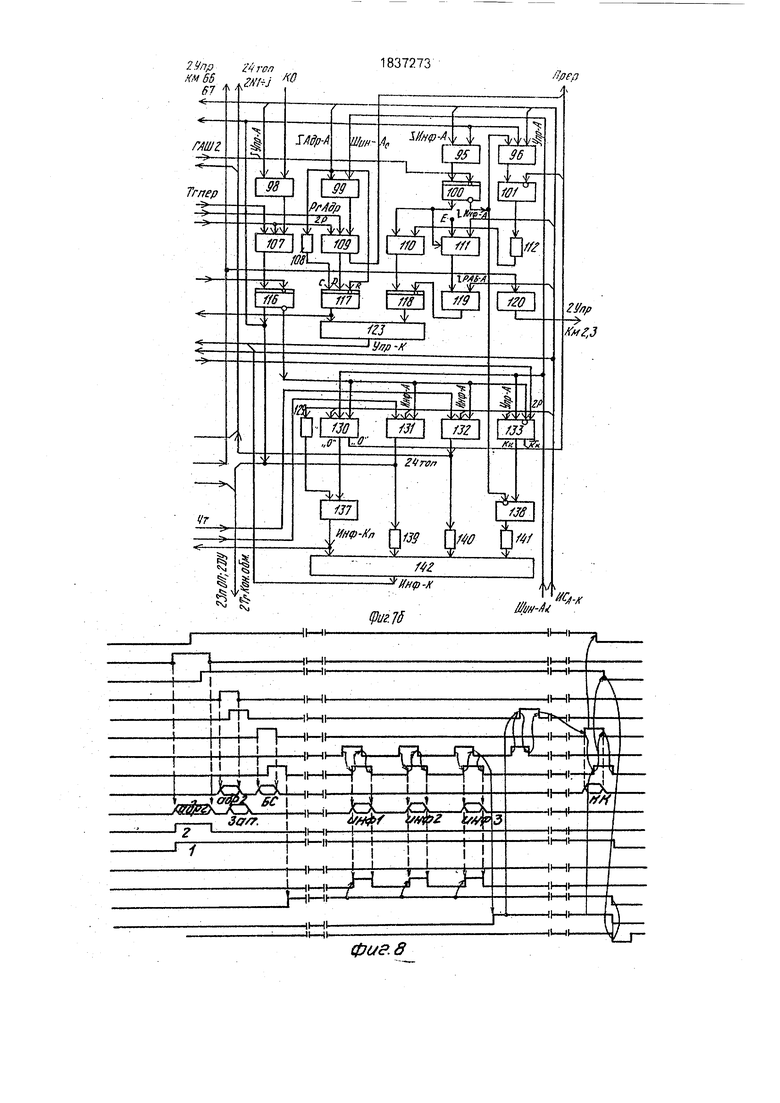

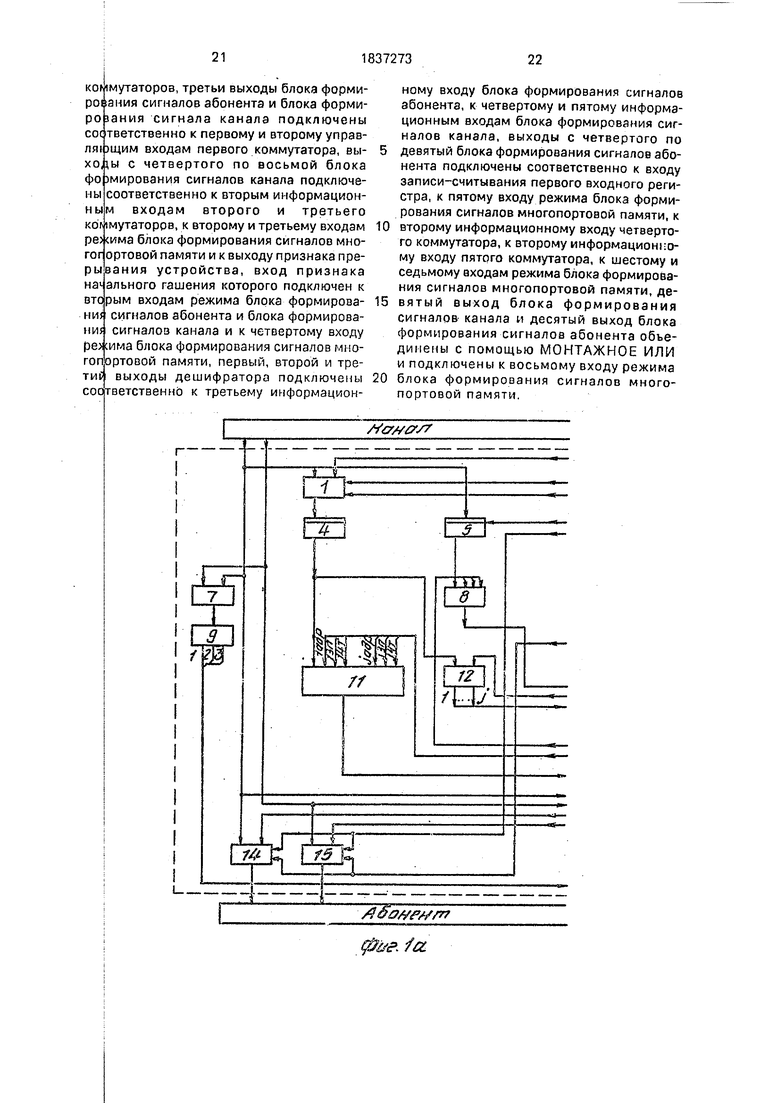

Описание изобретения поясняется рисунками: фиг.1а, 16 - блок-схема устройства фиг,2а, 26 - пример конкретного вы юлнения блока формирования сигналов абонента (БСА6); фиг.За, 36 - пример конк- ре ного выполнения блока формирования CHI налов многопортовой памяти (БСП 13); фи А - временная диаграмма работы БСА 6 при команде УПРАВЛЕНИЕ; фиг.5 - временная диаграмма работы БСА б при. переда1- е информации из канала в предлагаемое устройство; фиг.6 - временная диаграмма работы БСА 6 при передаче информации из предлагаемого устройства в канал; фиг.7а, 76 - пример конкретного выполнения блока формирования сигналов канала (БСК 10); фиг.8 - временная диаграмма работы БСК 10 при передаче информации от абонента в предлагаемое устройство; фиг.9 - временная диаграмма работы БСК 10 при передаче ин({ ормации от предлагаемого устройства к абоченту; фиг.10- пример конкретного выполнения многопортового блока памяти

(фИ

.11).

Устройство сортировки данных, именуемое в дальнейшем устройство, представлен ) на фиг. 1 а, 16 и содержит коммутаторы (Км) 1, 2, 3, первый регистр входа (РгВх) 4, второй регистр входа (РгВх) 5, блок форми- Ров.жия сигналов абонента (БСА) 6, схему И 7, б; ок памяти эталонов (ОПЭТ) 8, дешифратор (ДШ) 9, блок формирования сигналов канала (БСК) 10, многопортовой памяти (OHii/in) 11, компаратор (КОМП) 12, блок формирования сигналов памяти (БСП) 13, коммутаторы 14 и 15.

1ервый вход Км соединен с первыми вхо,Ј ами устройства, схемы И 7, Км 14, БСА 6, Б Ж 10, БСП 14 и РгВХ 5. Второй вход Км 1 coi динен со вторыми входами устройства, БСК 10 и первым входом Км 2. Третий и

четвертый входы Км 1 соединены соответственно с первыми выходами БСА 6 и БСК 10. Выход Км 1 соединен со входом РгВх 4, а выход последнего соединен с первыми вхо- 5 дамиОПМП 11 иКОМП 12.

Второй вход схемы И 7 соединен с третьими входами устройства, БСК 10, первым Км 15 и вторым входом БСА 6. Выход схемы И 7 соединен с входами ДШ 9, а 10 выходы последнего - с третьим входом БСА б и четвертым входом БСК 10,

Второй вход Км 14 соединен со вторым выходом БСК 10, а выход ДКДм 14 - с первым выходом устройства. 15 Второй вход Км 15 соединен с третьим выходом БСК 10, а выход Км 15 - со вторым выходом устройства. Третьи входы Км 14, Км 15 соединены со вторым выходом БСА б (1УПР.Км 14, 15), а четвертые входы Км 14, 0 Км 15 - с четвертым выходом БСК 10 (2УПР Км 14, 15).

Входы со 2-го по (3+1) ОПМ 11 соединены с первым выходом БСП 13, а выход ОПМП 11 соединен с четвертым входом БСА 5 б и пятым входом БСК 10.

Второй вход РгВх 5 соединен с третьим выходом БСА 6, а выход РгВх 5 - с первым входом ОПЭТ 8. Второй, третий и четвертый входы ОПЭТ 8 соединены со вторым выхо- 0 дом БСП 13, а выход ОПЭТ 8 - со вторым выходом БСП 13.

Второй вход КОМП 12 соединен с третьим выходом БСП 13, а выход (1-) КОМП 12 - с третьим входом БСП 13. 5 Второй вход Км 2 соединен с четвертым выходом БСА 6, а выход первого - с третьим выходом устройства.

Первый вход Км 3 соединен с четвертым входом устройства и шестым входом БСК 10, 0 второй вход Км 3 - с пятым выходом БСА 6, а выход КМ 3-е четвертым выходом устройства. Третьи входы Км 2, Км 3 соединены с шестым выходом БСА б (1УПР, Км 2, 3), четвертые входы Км 2, Км 3 - с пятым выходом 5 БСК 10(2УПР, Км 2, 3).

Пятый вход устройства (НАЧ.ГАШ. от КН) соединен с пятым входом БСА 6, седьмым входом БСК 10, четвертым входом БСП 13.

Пятый выход устройства (ПРЕР) соеди- 0 нен с шестым выходом БКС 10.

Седьмые выходы БСА 6 и БСК 10 соединены с пятым входом БСП 13.

Восьмой выход БСА 6 соединен с шестым входом БСП 13.

5 Девятый выход БСА 6 соединен с седьмым входом БСП 13. Десятый выход БСА 6 соединен с восьмым входом БСП 13.

Восьмой выход БСК 10 соединен с девятым входом БСП 13. Девятый выход БСК 10 соединен с десятым входом БСП 13. Четвертый выход БСП 13 (КО) соединен с восьмым входом БСК 10 и шестым входом БСА 6.

Предполагается, что устройство реализуется на элементах 133 серии.

При построении схем применяются триггера различных видов.

Во-первых, триггера типа 133ТМ2. Это триггера имеют информационный вход Т, входетробирования С и вход установки нуля

Во-вторых, - триггерные группы (которые мы для. простоты описания также называем триггерами).

Эти триггеры построены на основе 133ТМ2, нб установка их в 1 и О производится по соответствующим фронтам сигналов. При этом левый вход триггера боответствует установке в Г, правый - в О. Соответственно левый выход - единичный, правый - нулевой.

Знак около триггера указывает, что последний срабатывает по переднему фронту сигнал, знак - по заднему фронту сигнала.

При описании работы предлагаемого устройства используются сокращения: ШИ.Н-Кк - шина канала, выходящие из канала; ИСк-а - импульсы сопровождения от канала к абоненту (линии идентификации, служащие для определения типа данных, находящихся на ШИН-Кк, а также линия управления); ШИН-Ки ИСк - соответствующие описанным выше шины и линии на вхо- . до абонента; ШИН-Аа - шины абонента, уходящие от абонента; ИСд-к - импульсы сопровождения от абонента к каналу (линии идентификации, служащие для определения типа данных, находящихся на ШИН-Аа, а также линии управления от абонента); ШМН-А и ИСд - соответствующие описанным выше шины и линии на входе канала.

Остальные сокращения расшифровываются при описании соответствующих узлов. Импульсы сопровождения на входах предлагаемого устройства синхронизируются с импульсами внутренней частоты (СИ). Узел выработки СИ, а также узлы синхронизации импульсов сопровождения на прилагаемых фигурах не показаны.

Сортировка выполняется с помощью компаратора 12 (см. фиг.1а,б, За, б), на котором сравнивается информация из канала млн от абонента с кодом на регистре ворот и масок (ВОМ), В зависимости от выработанных в компараторе признаков информация, поступающая от канала или абонента, записывается по одному или нескольким адресам вч многопортовую память ОПМ 11, в которой каждому из ворот соответствует свой порт записи.

Предлагаемое устройство можно использовать для сортировки данных, организованных в виде массива (режим скалярной записи), или в виде векторов (режим вектор- ной записи),

В начале необходимо занести исходную информацию из к,аиала в регистры начальных адресов записи (1 НАЧ.АДР.62 - НАЧ.АДР.63).

0 Рассмотрим занесение начального значения например в Рг1 НАЧ.АДР.62 (во все остальные регистры занесение информации выполняется аналогично).

См,фиг.1а,б, 23,0,33,6, 4. 5 Код адреса абонента, передаваемый по ШИИ-К и сопровождаемый идентификатором АДР-К содержит восемь разрядоо.

Для предлагаемого устройства два левых разряда определяют режим передачи 0 информации: 01 - первый режим, при котором осуществляется обмен между каналом и предлагаемым устройством; 10 и 11 - вто- рой режим, при котором осуществляется обмен между абонентом и предлагаемым 5 устройством, причем коду 11 соответствует передача от абонента к предлагаемому устройству, а коду 10 - обратная передача; 00 - третий режим, информация и управляющие сигналы поступают от канала к абоненту и 0 (или) от абонента к каналу непосредственно. Итак, пусть по ШИН-КК передается код 01000000, на линии ДАР-К в этот момент высокий уровень. Эта информация через И 7 поступает на ДШ 9 и в виде сигнала по- 5 ступает в блок сигналов абонента (БСА 6).

По этому сигналу устанавливается н 1 триггер первого режима (Тг1Р42). От последнего через первый шифратор (1Ш52) закрываются коммутаторы Км14 и Км15 (на 0 выходах указанных коммутаторов эквивалентный ноль), а через второй шифратор (2Ш35) коммутаторы Км2 и КмЗ открываются по первому входу, т.е. на выходы последних поступает соответственно ШИН-Ад и из БСАО. 5 Кроме этого, Тг1Р42 через И 56 разрешает прием сигналов ИСк-а от канала во внутренние узлы БСАб,

Затем из канала поступает ВБР-К, кото- рый устанавливает в 1 ТгРАБ-А27 и через 0 КмЗ и канал передается РАБ-А. От переднего фронта РАБ-А в канале сбрасывается АДР-К, от заднего фронта которого устанавливается в 1 Тг АДР-А29, который через ИЛИ 38 вырабатывает код 01000000. посту- 5 лающей на ШИН-Аа . С некоторой задержкой, определяемой линией задержки Л337, вырабатывается АДР-А.

В ответ на АДР-А в канале вырабатывается УИР-К, а на ШИН-Ка устанавливается команда УПРАВЛЕНИЕ.

По-переднему фронту УПР-К данная команда принимается в регистр команд (эгКОМ31) и через ДШ39 вырабатывает сиг- ь ал УПР, поступающей на И 44, И 45.

По заднему фронту УПР-К через И 23 устанавливается в ГТгУПР-Ап 32, сигнал с т которого через ИЛИ 40 и Л341 поступает Е канала в виде УПР-А. На ШИН-Аа в этот момент низкий уровень, что соответствует нулевому байту состояния, В ответ на УПР- УА канал вырабатывает ИНФ-К, по переднему фронту которого Тг УПР-Ап 32 устанавливается в О.

По заднему фронту ИНФ-К через И 34 и Л349 устанавливается в 1 ТгИНФ-Ау 53. Оброс последнего производится передним оронтом ИНФ-К через ИЛИ 51.

По заднему фронту ИНФ-К устанавлива- {тся в Г триггер передачи (Тг передачи 43).

При нулевом состоянии триггера конца обмена (1Тг, кон.обм. 43) по каждому ИНФ- К через схему разрешения приема (И 44) Е ырабатывается сигнал разрешения приема (ЭАЗР.ПР). Указанный сигнал с частью разрядов РгКОМ.31 (NPEf). определяющих, в t акой именно регистр будет заноситься ин- оормация, поступают на вход БСП13.

В БСП13 сигналы РАЗр.ПР. и № РЕГ поступают на ДШ88, в котором вырабатывается разрешающий сигнал приема в соответствующий регистр. (В нашем случае - в 1 НАЧ.АДР.62). Информация в регистр поступает с ШИН-Кн. .

Сигнал разрешения приема в регистр (IP. в РЕГ) выполняет также сдвиг в регистре.

Так продолжается до тех пор, пока в соответствующий регистр не будет полностью занесена необходимая информация и (знал определяет окончание обмена,

В этом случае в ответ на ИНФ-А в канале вырабатывается УПР-К, по переднему оронту которого через ИЛИ 18, И 26 устанавливается в 1 триггер конца обмана (1Тг.КОН.ОБМ. 34).

В этом случае сброс Тг ИНФ-Ау 53 производится по переднему фронту УПР-К через И 48, ИЛИ 51. По заднему фронту УПР-К через ИЛИ-НЕ 17. Л320, И 24 устанавливается в 1, Тг УПР-Ао 33 и через ИЛИ 38 на ИН-Аа передается код КАНАЛ КОНЧИЛ (КК), а через ИЛИ 40, ЛЗ 41 - сигнал УПР-А. 1о УПР-А в канале происходит сброс ВБР-К п вырабатывается ИНФ-К, по переднему оронту которого через ИЛИ 17, И 19 сбрасывается Тг РАБ-А27, а через ИЛИ 25 - Тг ПР-АоЗЗ, От заднего фронта сигнала с Тг АБ-А27 через Л321, Л322 вырабатывается импульсный сигнал начального гашения (Тг НАЧ.ГАШ 1 28), который через И 36 в виде

сигнала ГАШ1 поступает на установку нуля ТМР42, Тг.ПЕРЕДАЧИ 43, Рг.КОМ.31, 1Tr.KOH.05M.34.

Таим образом, в регистр 1 НАЧ.АДР.62 5 занесена необходимая информация из канала.

Аналогично заносится информация и в остальные регистры.

Рассмотрим теперь передачу массива

Ю данных из канала в предлагаемое устройство с использованием сортировки (режим скалярной записи),

Весь процесс обмена взаимозависимыми сигналами выполняется аналогично опи15 санному выше. Временная диаграмма для этого режима приведена на фиг.5.

На ДШ39 вместо команды УПРАВЛЕНИЕ (УПР) расшифровывается команда ЗАПИСЬ (ЗП).

0 в случае по каждому ИНФ-К в режиме передачи через И 58 вырабатывается сигнал 13ПОП, который через коммутатор (КМ66), открытый по первому входу (1УПР.Км6б, 67 - высокий, 2УПР Кмбб, 67 - низкий) поступает

5 на ДШ ЗПОП84. Вместе с сигналом 13ПОП с Рг.КОМ 31 поступают: 1ДУ (дополнительные указания, определяющие в данном случае скалярный режим записи), а также состояние 1 Тг.кон.обм.34.

0 Одновременно информация по ШИН- Кк принимается в первый входной регистр (Pr ВХ4) через КМ1, открытый по первому входу (1 УПР КмГ - высокий, 2 УПР Км1 - низкий), Информация на выходе РгВХ4 по5 вторяет информацию на выходе Км1.

Информация на выходе РгВх4 повто- . ряет информацию на выходе Км1.

Запись информации выполняется в многопортовую память (ОПМП11) по

0 соответствующему адресу (или нескольким адресам). Информационный вход данной памяти является общим для всех портов и соединен с выходом РгВХ 4.

Данная память имеет j портов (1-J), в

5 нее поступает j адресов (1 АДР. - j АДР.); признаков записи (13П - j ЗП) и столько же признаков чтения (1 ЧТ - J ЧТ).

Информация с РгВХ4, поступающая на первый вход компаратора, сравнивается на

0 последней с той, которая поступает на ее второй вход. В данном случае это будет информация с первого регистра ворот и масок (1ВОМ73), поступающая через Км76 (Сигнал . ВЕКТ.ЗП. поступает низким уровнем).

5 В результате сравнения на выходе КОМП.12 вырабатывается один (или несколько) признаков 1 - J, поступающих на ДШ ЗПОП 84. Кроме этих сигналов на указанный дешифратор поступают также сиг- налы режима записи (скалярная запись высоким уровнем, векторная запись - низким).

На выходе ДШ ЗПОП 84 возникает высокий уровень разрешения записи на тех проводах 13П- j ЗП, которые соответствуют разрешенным портам записи.

Адреса записи формируются на сумматорах записи (1 2) ЗП77 - jЈ ЗП48), на каждом из которых суммируются три значения - начальный адрес (1НАЧ.АДР.62 - J НАЧ.АДР.63), счетчик пектора (1 СчВЕКТ68 - j Сч.ВЕКТбЭ) и счетчик записи (1 Сч.ЗП74 - j Сч.ЗП75).

Отметим здесь, что счетчики записи находятся в нулевом состоянии и в формировании адреса записи в данном режиме участия не принимают.

Выходы сумматоров записи поступают на первые входы коммутаторов адреса (1КМ.АДРЕС86 - j Км.АДР87), управляемые выходами КмЗПбб и КмЧт67.

В нашем случае коммутаторы адреса открываются по первому входу. Таким образом в ОПМП11 поступают адреса записи.

Сигналы 13П - j ЗП поступают также на счетчики векторов (1 Сч.ВЕК.68 - j Сч.ВЕК.69) и по заднему фронту сигнала увеличивают содержимое соответствующих счетчиков на 1, подготавливая тем самым адреса записи для следующего обращения. Последовательность окончания аналогична описанной выше.

После окончания режима скалярной записи весь массив данных, переданный из канала, сказался рассортированным по соответствующим адресам в ОПМП11, причем адреса начала каждого такого подмассива содержится в регистре начального адреса (1 НАЧ.АДP.62-J НАЧ.АДР.63), а количество записанных элементов массива - в счетчиках векторов (1 Сч.ВЕК.68-J Сч.ВЕК.69).

Пусть теперь стоит задача - рассортированный массив данных передать из ОПМП11 в канал. По команде ЧТЕНИЕ в канал передается один подмассив.

Временная диаграмма работы для данного случая приведена на фиг.6.

Начальная выборка выполняется аналогично описанному выше.

На ДШ39 расшифровывается команда ЧТЕНИЕ (ЧТ). Через И 47 по заднему фронту ИНФ-К устанавливается в Н1 триггер ИНФ-А чтения (ТгИНФ-А чт55), по которому через И 57 вырабатывается 1 ЧтОП, поступающий через Км ЧТ 67 на ДШ ЧтОП 85 (см. фиг.3,6).

Вместе с сигналом 1 ЧТ.ОП с Рг.КОМ31 передается № 1 - j - номер порта, откуда следует передать информацию в канал.

На выходе ДШЧТОП85 возникает высокий уровень разрешения ЧТЕНИЯ на одном из проводов 1ЧТ - j ЧТ, номер которого указан в № 1 - j.

Адреса чтения портов (подмассивов) формируются на сумматорах ЧТЕНИЯ (1 Чт89 j 2Чт90), на каждом из которых складываются два значения - начальный адрес (1 НАЧ.АДР.62 - j НАЧ.АДР.63) и счетчик чте- имя (1сЧ.ЧТ92 - j Сч.ЧТ.93).

Выходы сумматоров чтения поступают на вторые входы коммутаторов адреса (1 Км.АДР.вб-j КМ АДР.87), управляемые выходами Км ЗП66 и КМ ЧТ 67. В рассматри- ваемом примере коммутаторы адреса открываются по второму входу. Таким образом, в ОПМП11 поступают адреса чтения.

Сигналы 1ЧТ - J Чт поступают также на счетчики чтения (1 C4. Сч.ЧТ.93) и по заднему фронту сигнала увеличивают содержимое соответствующих счетчиков на 1, подготавливая тем самым адреса чтения для следующего.

Информация, прочитанная из ОПМП11

поступает через И 30, ИЛИ 38 на ШИН-Аа.

От переднего фронта Тг ИНФ-А ЧТ 55

через ЛЗ 59, ИЛИ 60 вырабатывается ИНФА, поступающий в канал. Задержка ЛЗ 59

выбрана из расчета, чтобы ИНФ-А появился бы позже информации на ШИН-Аа.

По переднему фронту ИНФ-К сбрасывается ТГ И НФ.-А чт.55.

Такая последовательность сигналов продолжается до тех пор, пока весь задан- ный подмассив не будет передан в канал.

.На схемах сравнения (1 СРАВ7 80 - j СРАВ.81) сравнивается конечный адрес записи с текущим адресом чтения для каждого подмассива. При возникновении равенства возникает сигнал PABHO(1P-j Р), поступающий на ДШ ГАШ.94. на выходе этого дешифратора возникает сигнал КОНЕЦ ОБМЕНА (КО), поступающий на ИЛИ 18. По КО начинается последовательность оконча- ния,

Кроме этого, на ДШ ГАШ 94 вырабатывается сигнал гашения (1 ГАШ - J ГАШ), устанавливающий в О соответствующие счетчики ( СЧ век.68 - J Сч.век.69; 1 сч ЗП 74 - j Сч ЗП 75) 1 Сч ЧТ 92 - j Сч ЧТ 93).

По переднему фронту КО через ИЛИ 18, И 26 устанавливается в 1 Тг КОН.ОБМ.34.

В этом случае по заднему фронту ИНФ- К через ИЛИ-НЕ 17, ЛЗ 20, И 24 устанавли- вается в единицу триггер УПР-А окончания (Тг УПР-АоЗЗ), который через ИЛИ 40, ЛЗ 41 вырабатывает сигнал УПР-а, а через ИЛИ 38 передает на ШИН-А а Код КАНАЛ КОНЧИЛ СЯ(КК).

По сигналу УПР-К, выработанному в ка- н|ле в ответ на УПР-А, срабатывает ВБР-К, ч( рез ИЛИ 16, И 19 устанавливается в ноль Ti РАБ-А27. .Через ИЛИ 25 по переднему ф юнту УПР-К устанавливается в О Т г УЩР-АоЗб.

Рассмотрим организацию режима век- тфжой записи.

В этом случае код в регистр ворот и масок поступает из памяти эталонов (ОП ЭТ 8)| в которую он был предварительно занесен по команде ЗП ОП ЭТ.

Затем, одновременно с приемом эле- м« нтов вектора в РгВХ4, в регистр 2ВОМ61 читается код из ОП ЭТ 8. Коммутатор Км76 срыт по второму входу (т.е. задан режим (торной записи) и на КОМП12 происходит шнение указанных кодов.

В связи с тем, что в общем случае адрес чиси вектора выясняется лишь в конце

от ве ср|

за пе пр ве ва за ди гд со по

редачи (по последнему ему компоненту), инят следующий алгоритм сортировки торов - каждый элемент вектора записы- тся по всем адресам записи портов 1-j, a ем, после окончания вектора, произво- ся корректировка адресов портов: там, накопленные признаки с КОМП12 не тветствуют условию сравнения, адреса тов корректируются, Отметим, что вначале занесение инфор- из канала в память эталонов 8.

Выработка сигналов в БСАб выполняете аналогично описанному выше режиму скглярной записи, нов 1ДУ указан признак записи в ОП ЭТ.

Этот признак через КмЗПбб поступает на Сч.АДР.ЭТ 70, И79 и ДШЗПОП 84.

По каждому 13П ОП через И79, ИЛИ82 к сметчику адреса добавляется единица для модификации адреса записи,

ДШ ЗПОП 84 в данном режиме блокирован и 13П - j ЗП тождественно равны нулю. С И79 в ОПЭТ8 поступает сигнал ЗП ЭТ, со Сч.АДР.ЭТ 70 - адрес ОПЭТ, с Х5 - информация из канала. Информа- на выходе РгВхБ повторяет инфррма- на входе этого регистра при высоком

ОП

РгЕ

ЦИ5 ЦИН

уро

ОП ока

рне сигнала Р.2РгВх.

Таким образом, запись производится в

)Т 8, а многопортовая память ОПМП 11

зывается заблокирована.

После передачи всего массива, по высокому уровню с 1 Тг. КОН.ОБМ.34 Сч./ 1ДР.ЭТ70 устанавливается в нулевое соCTOf

ние (УО).

На этом режим записи в ОПЭТ8 заканчивается.

(Рассмотрим теперь более подробно ре- векторной записи для информации, пожш

туг|ающей из канала.

Выработка сигналов в БСА6 выполняется аналогично описанному выше режиму скалярной записи, но в ДУ1 указан признак векторной записи. Этот признак (ВЕКТ.ЗП) 5 поступает на И72, накопитель признаков (НАКОП, ПР83), Км76, ДШ ГАШ 94, ДШ У О 95, ДШ PC 96, ДШ ЗП ОП 84.

По сигналу 13ПОП из БСАб на ДШ ЗПОП84 вырабатываются одновременно 0 все признаки 13П - ЗП и запись информации в ОПИ11 производится из РгВХ4 одновременно по всем адресам 1 АДР. - j АДР. После этого во все счетчики векторов (1 C4.BEK.68-j Сч.ВЕК.69) по сигналам 13П - 5 j ЗП добавляются единицы, тем самым модифицируя адреса записи,

Через И 2 к счетчику длины вектора (Сч.ДЛ.ВЕК 71) по каждому сигналу записи добавляется единица (+1 ВЕК). Этот же 0 сигнал используется как сигнал чтения из ОПЭТ8 (ЧТ и ОПЭТ), а через ИЛИ 82 он поступает на модификацию Сч.АДР.ЭТ70,

Информация из ОПЭТ 8 принимается в регистр 2ВОМ61 и через Км76 поступает как 5 второй операнд на КОМП12.

Так продолжается до тех пор, пока содержимое Сч.ДЛ.ВЕК 71 не сравняется с содержимым Рг.ДЛ.ВЕК 65. В этом случае вырабатывается сигнал КОНЕЦ ВЕКТОРА 0 (KB), поступающий на .ОП.ПРЗЗ, ДШ PC 96 и через ЛЗ 91 на ДШ У О 95.

На ДШ PC 96 анализируются накопленные признаки для передаваемого вектора, и там, где эти признаки равны единице (т.е. 5 вектор удовлетворяет условиям сравнения) содержимое счетчиков векторов (1 Сч.ВЕК 68 - J Сч.ВЕК 69) прибавляется к содержимому счетчиков записи (1 Сч.ЗП74 - J Сч.ЗП 75). Это сложение выполняется по разреша- 0 ющему 1 -J РСсДШ PC 96.

После такого добавления с некоторой задержкой, определяемой ЛЗ 91, все счетчики векторов обнуляются по сигналам 1 - У О с ДШ У О 95.

5 Таким образом, по окончании записи каждого вектора в ОПМ11 производится корректировка адресов записи (1АДР - j АДР) для следующего вектора.

Рассмотрим теперь обмен информа- 0 цией предлагаемого устройства с абонентом.

В начале абонент настраивается на работу с устройством. Так для дисков такая настройка может заключаться в подводе го- 5 ловок, поиску зоны по идентификатору и т.д. В этом случае канал передает абоненту команду управления, причем обмен взаимозависимыми сигналами выполняется строго в режиме ЗАПРОС-ОТВЕТ (см. фиг. 1а, б, 7а, б).

В этом случае одновременно с сигналом АДР-К на ШЙН-Кк канал выставляет код, содержащий в левых разрядах 00.

На ДШ9 вырабатывается сигнал 0, поступающий в БСК10. Здесь он устанавливает в 1 триггер третьего режима (ТгЗР127), который через 1Ш134 открывает Км14 и Км 15 по первому входу, а через 2Ш120- Км2 и КмЗ по второму входу.

Таким образом ШИН-Ка и СКк-а непосредственно поступают к абоненту (от кана- ла), а ШИН-Аа и ИСд-к к каналу (от абонента). В этом случае обмен выполняется строго по 3 .

Рассмотрим теперь передачу информации от абонента и запись в ОПМП11 предлагаемого устройства (см. фиг. 7а, б, 8).

Из канала по одной из линий СКк-А передается сигнал АДР-К, по ШИН-Кк - вд, содержащий в левых (старших) разрядах 11.

На ДШ9 вырабатывается сигнал 2, поступающий в БКС10, где устанавливается в 1 триггер второго режима (Тг2Р 126).

Одновременно код команды (11) запоминается в регистре команд (РгКОМ. 135), а номер абонента - в регистре адреса (Рг.АДР.104).

На выходе 1Ш134 появляется сигнал 2УПР Км 14, 15, переключающий Км14 и Км 15 на второй вход.

На выходе 2Ш 120 появляется сигнал 2УПР Км 2, 3, переключающий Км2 и КмЗ таким образом, что на выходах последних устанавливается низкий уровень.

После этого функции канала выполняет БСК 10; информация по ШИН-КК и ИСк-а поступает к абоненту; на ШИН-А в ИСд в канале - нули.

От Тг 2Р126 срабатывает ТгАДР-К 103. Через И114, ИЛИ115 адрес (номер) абонента поступает на ШИН-КК, а индентификатор АДР-К поступает через ЛЗ 113 на ИСК-А1.

От Tr 2P 126 с некоторой задержкой, определяемой Л397, срабатывает Тг ВБР-К 102, выход которого в виде сигнала ВБР-К поступает на ИСк-д1

В ответ на ВБР-К от абонента поступает сигнал РАБ-А, от переднего фронта которого срабатывается ТгАДР-К 103. В ответ на задний фронт АДР-К абонент отвечает АДР- А и на ШИН-Аа выставляется адрес (номер) абонента, к которому производится обращение. Через И99 этот адрес поступает на первый вход сумматора ( Ј Ю9), второй вход которого соединен с РгАДР 104. а тре- тий (разрешающий) с Тг2Р 126.

Если адрес обращения к абоненту совпадает с ответным адресом (от абонента), на выходе - X 109 возникает высокий уровень. По переднему фронту АДР-А через ЛЗ 108 устанавливается в 1 Тг УПР-Кп 117. Величина задержки ЛЗ 108 определяется временем, необходимым для успокоения переходных процессов .

Если же указанные выше адреса не совпадают на выходе Ј 109 - высокий уровень и данный сигнал поступает на прерывание.

0 G выхода Тг УПР-Кп 117 через H1Q6, ИЛИ115 передается на ШИН-Кк команда ЗАПИСЬ. Второй вход И106 соединен с ДШ136, который превращает условную форму задания команды в ту форму, которую 5 воспринимает абонент.

Сигнал с выхода Тг УПР-Кп 117 через ИЛ И123 в виде УПР-К поступает на ИСк-д . По переднему фронту УПР-К у абонента сбрасывается АДР-А, по переднему фронту 0 которого Тг УПР-Кп117 устанавливается в О, От заднего фронта УПР-К у абонента устанавливается в 1 УПР-А и на ШИН-Аа выставляется байт состояния. На дешифратор байта состояния (ДШ БС 130) поступают 5 УПР-Аа и сигнал с нулевого выхода 2Тг КОН.ОБМ.116 (Если нет конца обмена, последний выход имеет высокий уровень).

Если байт состояния, поступающий от абонента, нулевой, на выходе О - высокий 0 уровень.

По переднему фронту УПР-А через ЛЗ

129, задержка которой выбрана из условия

успокоения переходного процесса в

ДШБС130, через И137, ИЛИ142, сигнал

5 ИНФ-К поступает на ИСк-д.

От переднего фронта ИНФ-К сбрасывает УПР-А у абонента, от заднего фронта ИНФ-К подготовки (ИНФ-Кп) устанавливается в 1 триггер передачи (Тг ПЕРЕД 128), 0 На этом заканчивается начальная выборка и начинается передача данных.

Абонент вырабатывает сигнал ИНФ-А на ИС-А-К, а на ШИН-Аа при этом выставлена информация от абонента. На входы И131 5 поступают сигналы: ЗП с ДШ136, ИНФ-А с нулевого выхода ТгКОН.ОБМ. 116. С выхода И131 сигнал 23ПОП поступает на вход БСП 13. В данном случае сигнал 2 УПР Кмбб является сигналом высокого уровня (расшиф- 0 рован режим два) и по сигналу 23ПОП выполняется запись в ОПМП11. Вместе с сигналом 23ПОП в БСП13 передаются дополнительные указания (2ДУ), определяющие режим векторной или скалярной записи, а также состояние 5 2 ТгКОН.ОБМ. 116.

С некоторой задержкой, определяемой уставкой ЛЗ 139 через ИЛИ142 вырабатывается ИНФ-К, поступающий на ИСк-а1. Величина задержки ЛЗ 139 определяется окончанием процесса записи в память.

На линии 2 УПР Км1 - высокий уровень, н 1 УПР Км - низкий.

Высокий уровень 2 УПР Км1 определяется единичным состоянием триггера второго режима (Тг2Р 126).

При этом информация с ШИН-Аэ через I м1 поступает на входной регистр РгАх4, а атем на КОМП12 и в ОПМ11 (на информа- и ионный вход последней).

Далее выполняются действия, анало- г 1чные описанным выше (при записи от ка- ьала).

Через некоторое время, определяемое бонентом, вновь появляется ИНФ-А, а на L JHH-Aa - информация от абонента.

Процесс записи и в ОПМП11 продолжается до тех пор, пока не закончится массив г ередачи.

В этом случае на последний ИНФ-К по аднему его фронту абонент вырабатывает ПР-А на ИСд-к, а на ШИН-А при этом выставляется информация КАНАЛ КОНЧИЛ ((К) - при нормальном окончании обмена.

По переднему фронту УПР-А через ЛИ98, И107 уста на вливается в 1 триггер онца обмена (2 Тг.КОН.ОБМ.116), Отметим, то остальные входы на И107 - второго ре- има и Тг ПЕР являются высокими и посту- г ают соответственно с Тг2Р12б и гПЕРЕД128. Через И-НЕ 94 при высоких ровнях УПР-А и 2Тг КОН.ОБМ.116 сбрасы- аетсяТГВБР-К102.

На дешифраторе конца канала (ДШ КК 33) на выходе КК устанавливается высокий ровень, если по ШИН-П поступил код КА- АЛ КОНЧИЛ, в противном случае высокий эовень устанавливается на выходе КК. По- ледний поступает на выход устройства на ферывание.

Через И96, И101, ЛЗ 112, ИЛИ 10 по среднему фронту УПР-А устанавливается в Г триггер УПР-К окончания (Тг УПР-К0 118), который через ИЛИ 123 в качестве :игнала УПР-К поступает на ИСк-д. (Деист- стельно, нулевой выход Тг КОН.КАН.100 - )ысокий, единичный выход 2 Тг (ОН.ОБМ.116- высокий, КК- низкий).

От переднего фронта УПР-К в режиме жончания сбрасывается УПР-А и РАБ-А, а ю заднему фронту последнего через И119 :брасывается Тг УПР-Ко 118, что соответст- }ует сбросу ИНФ-К (Триггер КОНЕЦ по КА- ЧАЛУ-Тг КОН.КАН.100 находится в О, на управляющем входе коммутатора Км111 - -(изкий уровень, а на выходе последнего - эысокий (Е).).

Рассмотрим теперь режим чтения на ЭПМП 11 и записи к абоненту (см. фиг. 7а, 6.9).

Начальная выборка (подготовка) отличается от описанной выше лишь тем. что на ДШ 136 вырабатываются сигналы ЧТЕНИЕ, Чт.

Режим передачи состоит в том, что от 5 абонента поступает сигнал ИНФ-А, являющийся запросом информации.

На вход И132 поступают высокие уровни с ДШ 136 (чт), с инверсного плеча 2 Тг КОН.ОБМ.116 и сигнал ИНФ-А от абонента.

0 На выходе И132 формируется сигнал 24т ОП, поступающий в БС113. Одновременно с этим сигналом с Рг КОМ. 135 поступает номер порта (2 № 1 - J) из которого выполняется чтение.

5 В данном случае (как и в предыдущем) 2 УПР Км 66, 67 находится в высоком уровне (расшифрован режим два) и по сигналу 2 ЧТОП производится чтение информации из ОПМП11.

0 С некоторой задержкой, определяемой ЛЗ 140, через ИЛИ 142 вырабатывается ИНФ-К, поступающий на ИСк-д. Величина задержки определяется окончанием процесса чтения из памяти. Через И 105, ИЛИ

5 115 прочитанная из памяти информация поступает на ШИН-Кк и далее к абоненту.

Через некоторое время, определяемое абонентом, вновь появляется ИНФ-А от абонента. Так продолжается, пока не закон0 чится массив передачи.

В этом случае в БСП 13 вырабатывается сигнал КОНЕЦ ОБМЕНА (КО). Через ИЛИ 98, И 107 устанавливается в 1 2 Тг.КОН,ОБМ.116. По следующему сигналу

5 ИНФ-А вместо ИНФ-К будет выработан УПР-К. Действительно, схема И 132 блокируется низким уровнем с нулевого плеча 2 Тг КОН.ОБМ.116. Через И95 устанавливается в 1 Тг КОН.КАН.100, который через ИЛИ

0 100установитв ГТгУПР-Ко112. Км 111 по управлению переключается на второй вход и по заднему фронту ИНФ-А Тг УПР-Ко 118 устанавливается в 0й. что равносильно сбросу сигнала УПР-К.

5 От заднего фронта УПР-К в последовательности окончания устанавливается в 1 УПР-А и на ШИН-Ао выставляется информация КАНАЛ КОНЧИЛ (КК).

Через ДШ КК 133. W 138, ЛЗ 141. ИЛИ

0 142 вырабатывается ИНФ-К. Гашение Тг ВБР-К выполняется аналогично предыдущему.

На фиг. 10 представлен пример конк- . ретного выполнения узла многопортовой

5 памяти (ОПМП 11).

Здесь ОП1, ОП2, .... ОП представляют собой блоки оперативной памяти с независимым обращением.

Информационные входы, а также выходы всех блоков оперативной памяти объедиены соответственно между собой и являтся информационным входом и выходом зла.

В каждый блок оперативной памяти потупают адрес обращения (1 АД Р., 2 АДР., .., j АДР), признак обращения по записи

13П, ) и признак обращения по

тению (1ЧТ, 2ЧТ, ...,J4T).

Строго говоря, рассматриваемый узел является многопортовой оперативной, памятью по записи, т.к. в каждый блок памяти можно одновременно записать информацию с общего информационного входа.

Технический эффект заключается в увеличении производительности системы (по сравнению с прототипом) за счет того, что сортировка векторов выполняется аппаратным способом за один проход. Кроме этого, предлагаемое устройство позволяет работать с более быстродействующими абонентами, а также согласовать интерфейсы последних как по типу, так и по скорости передачи данных с используемым каналом. Формула изобретения Устройство сортировки данных, содержащее с первого по пятый коммутаторы, блок памяти эталонов, первый и второй входные регистры, компаратор, дешифратор и элемент И, причем первый информационный вход устройства, выходящий от канала, подключен к первым информационным входам первого и второго коммутаторов, к информационному входу первого регист ра и к первому входу элемента И, первый вход признака данных устройства, вы- ходлщий от канала, подключен к первому информационному входу третьего коммутатора и к второму входу элемента И, выход которого подключен к входу дешифратора, выход первого коммутатора подключен к информационному входу второго входного регистра, выходы первого и второго входных регистров подключены соответственно к информационному входу блока памяти эталонов и первому входу компаратора, второй информационный вход устройства, выходящий от абонента, подключен к первому информационному входу четвертого коммутатора и к второму информационному входу первого коммутатора, второй вход признака данных устройства, выходящий от абонента, подключен к первому информационному входу пятого коммутатора, выходы второго, третьего, четвертого и пятого коммутаторов подключены соответственно к первому информационному выходу для абонента устройства, к первому выходу признака данных для абонента устройства, к второму информационному выходу для канала устройства и к второму выходу признака данных для

канала устройства, отличающееся тем, что, с целью увеличения быстродействия, оно содержит блок формирования сигналов абонента, блок формирования сигналов канала, блок формирования сигналов многопортовой памяти и многопрограммный блок памяти, причем выход блока памяти эталонов подключен к первому информационному ьходу блока формирования сигналов

0 многопортовой памяти, первый выход которого подключен к второму входу компаратора, выход которого подключен к первому входу режима блока формирования сигналов многопортовой памяти, второй выход

5 которого подключен к первым входам режима блока формирования сигналов абонента и блока формирования сигналов кгэнала, выходы первой группы блока формирования сигналов многопортовой памяти подключе0 мы соответственно к адресному входу, входам чтения и записи блока памяти эталонов, выходы второй группы блока формирования сигналов многопортовой памяти подключены соответственно к адресным входам, к

5 входам записи и чтения блока многопортовой памяти, выход которой подключен к пер-- вым информационным входам блока формирования сигналов абонента и блока формирования сигналов канала, выход вто0 рого входного регистра подключен к информационному входу блока многопортовой памяти, первый информационный вход устройства, выходящий от канала, подключен к вторым .информационным входам блока

5 формирования сигналов многопортовой памяти, блока формирования сигналов канала и блока формирования сигналов абонента, первый вход признака данных от канала устройства подключен к первым управляю0 щим входам блока формирования сигналов абонента и блока формирования сигналов канала, второй информационный вход устройства, выходящий от абонента, и второй вход признака данных устройства, выходч5 щий от абонента, подключены соответственно к третьему информационному и к второму управляющему входам блока формирования сигналов канала, первый выход блока формирования сигналов канала тюд0 ключей к первым управляющим входам второго и третьего коммутаторов, второй выход блока формирования сигналов канала подключен к первым управляющим входам четвертого и пятого коммутаторов, первый

5 выход блока формирования сигналов абонента подключен к вторым управляющим входам второго и третьего коммутаторов, второй выход блока формирования сигналов абонента подключен к вторым управляющим входам четвертого м пятого

коммутаторов, третьи выходы блока форми- ропания сигналов абонента и блока форми- розания сигнала канала подключены состветственно к первому и второму управляющим входам первого коммутатора, выходы с четвертого по восьмой блока формирования сигналов канала подключе- иы|соответственно к вторым информационным входам второго и третьего

KOh

ре

мутаторов, к второму и третьему входам

има блока формирования сигналов мно- гог|ортовой памяти и к выходу признака пре- рывания устройства, вход признака начального гашения которого подключен к втррым входам режима блока формирова- ни; сигналов абонента и блока формировали сигналов канала и к четвертому входу режима блока формирования сигналов многопортовой памяти, первый, второй и третий выходы дешифратора подключены соответственно к третьему информационному входу блока формирования сигналов абонента, к четвертому и пятому информационным входам блока формирования сигналов канала, выходы с четвертого по девятый блока формирования сигналов абонента подключены соответственно к входу записи-считывания первого входного регистра, к пятому входу режима блока формирования сигналов многопортовой памяти, к второму информационному входу четвертого коммутатора, к второму информационному входу пятого коммутатора, к шестому и седьмому входам режима блока формирования сигналов многопортовой памяти, девятый выход блока формирования сигналов канала и десятый выход блока формирования сигналов абонента объединены с помощью МОНТАЖНОЕ ИЛИ и подключены к восьмому входу режима блока формирования сигналов многопортовой памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство для сопряжения | 1983 |

|

SU1176338A2 |

| Устройство для обмена информацией | 1985 |

|

SU1339572A1 |

| Устройство для сопряжения вычислительной машины с внешними абонентами | 1984 |

|

SU1265784A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1615728A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

Изобретение относится к вычислительной технике, а именно к устройствам ввода- вывода информации, использующим интерфейсы ЕС ЭВМ. Целью изобретения является увеличение быстродействия. Устройство содержит коммутаторы 1-3, регистры 4, 5 входа, блок 6 формирования сигналов абонента, схему И 7, блок 8 памяти эталонов, дешифратор 9, блок 10 формирования сигналов канала, блок 11 многопортовой памяти, компаратор 12, блок 13 формирования сигналов памяти, коммутаторы 14, 15. 10 ил.

/З&а&ем/г

fre. fa

-S5

I

со rCN

Гсо ее

vRs

т

I

Ј

§ § J

t

I

fc

:

V/s/

ft%. Kjff/7; /rf+jO/j

3i7 7/%r; /rOfl3Ti Одр Offэт

лр-отхомлор,

I

§§

fltWt

fT L

я

кодер-, м чека, г-ой ажроно.хам/г.

ь

v

I

С

Ж

1Г4Ш

±Л

е

а

-4

1

-

§

«Ч

-/

oa со -J ю

-4

CO

р

i i

&

т

m

/

fe

/

I

N

I

Л/

п г- см гOD

СО

Ш

i

:

t; «

фи.8

Ч/ : .-, W . VI/ W

i I i i i i

ГФ Ф

NT

.

эдактор Н.Коляда

Составитель А.Шафран Техред М.Моргентдл

(рма.З

ф#с./0

Корректор М.Андрушенко

Авторы

Даты

1993-08-30—Публикация

1990-03-16—Подача