Изобретение относится к области вычислительной технике, в частности к организации микропрограммных мультиплексных каналов микропрограммных вычислительных машин, и может быть использовано для ор- ганизации обмена информацией между периферийными устройствами и процессором.

Цель изобретения - повышение надежности за счет сокращения канального оборудования и обеспечение возможности диагностирования оборудования канала.

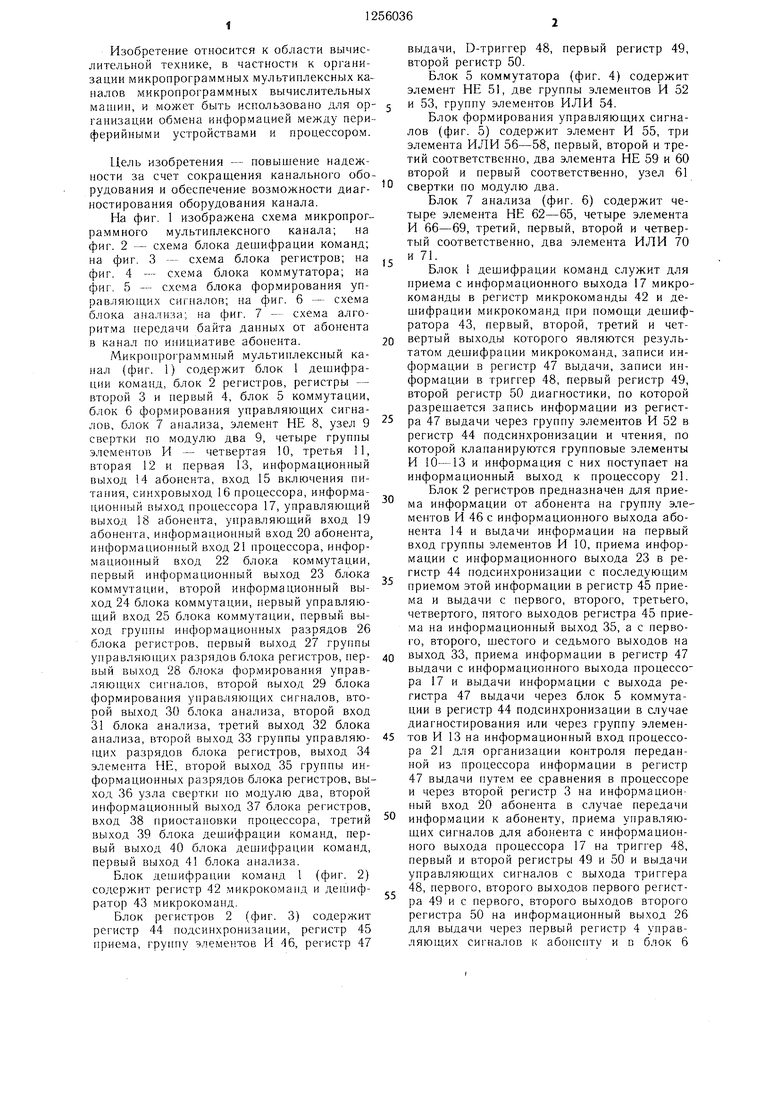

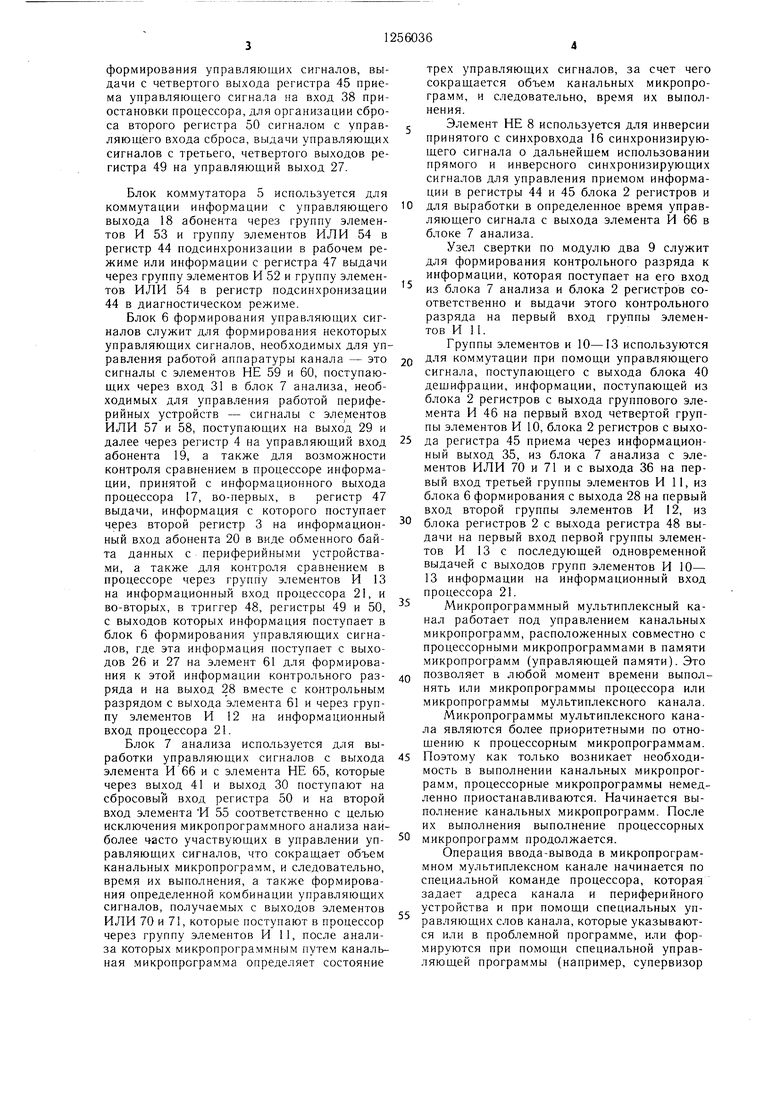

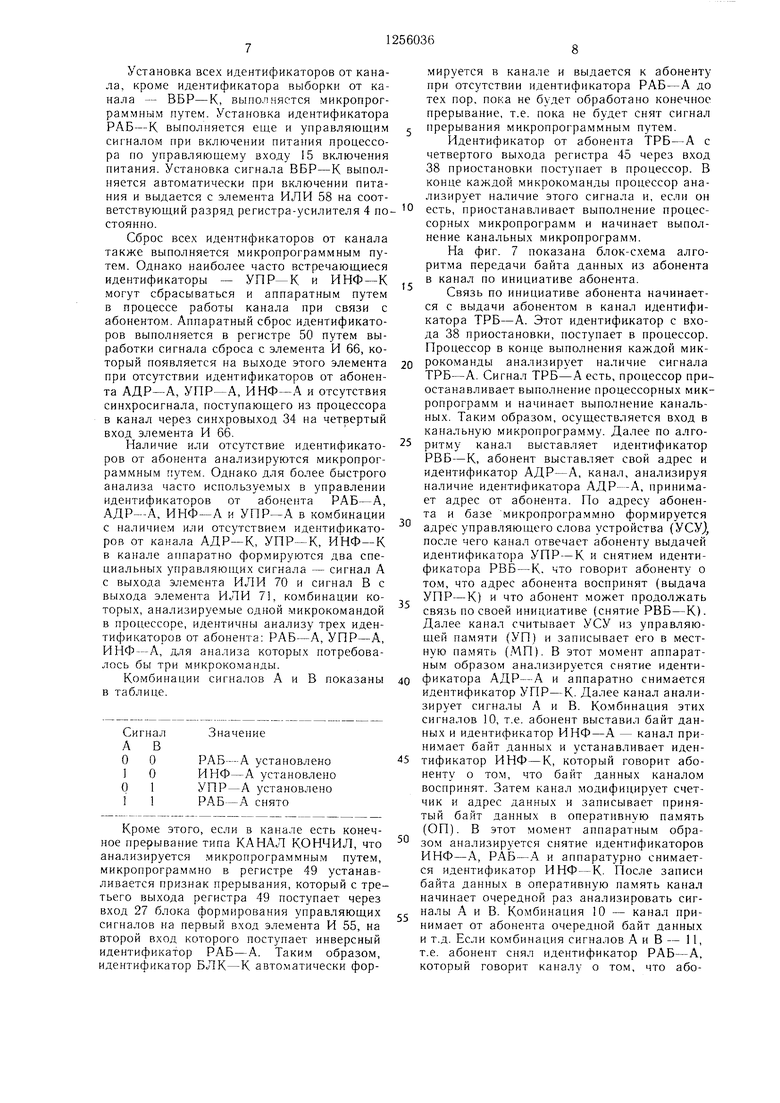

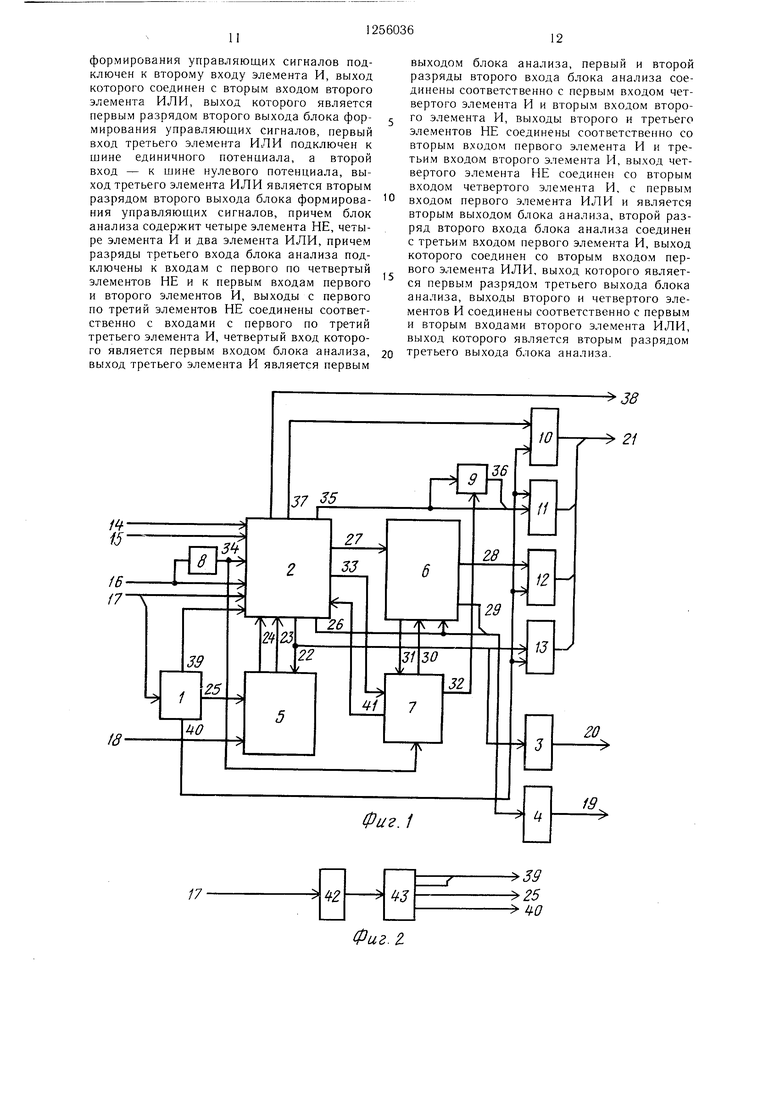

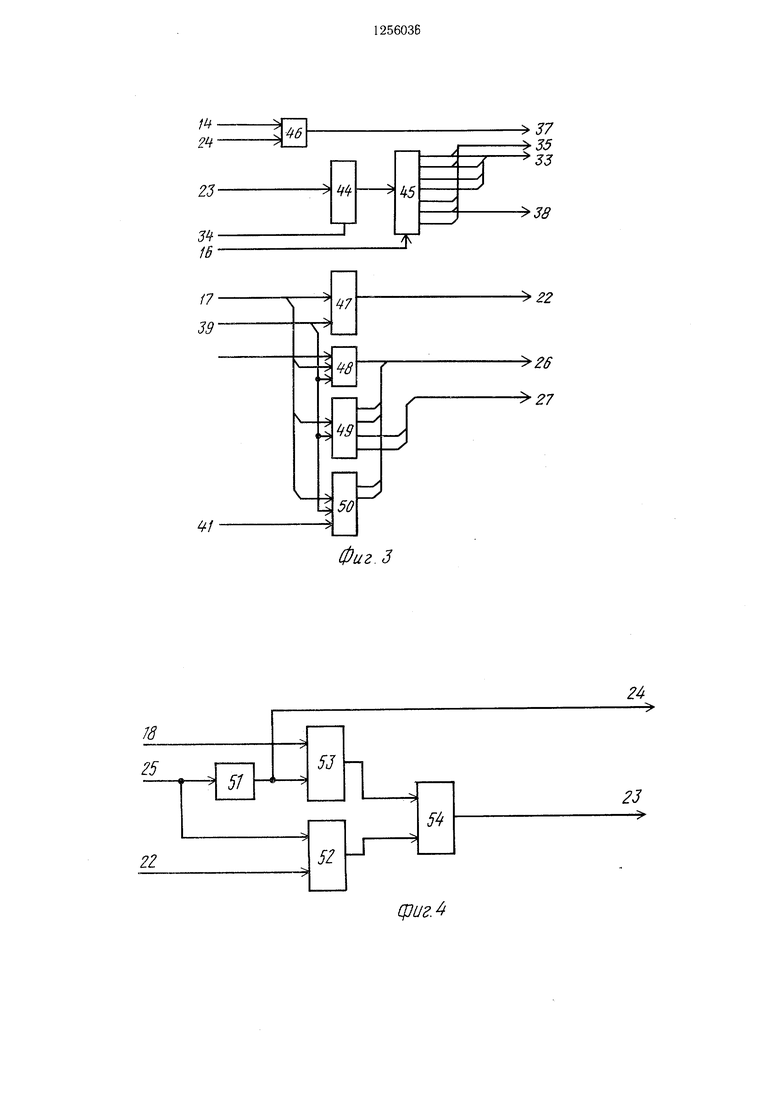

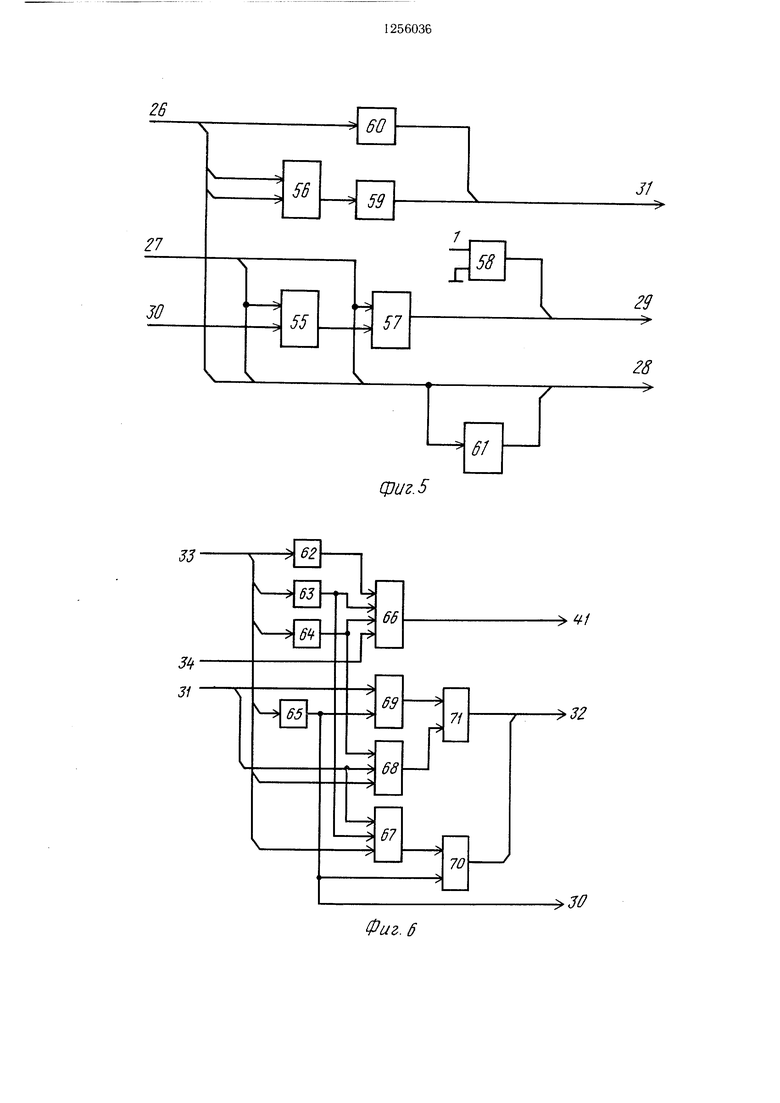

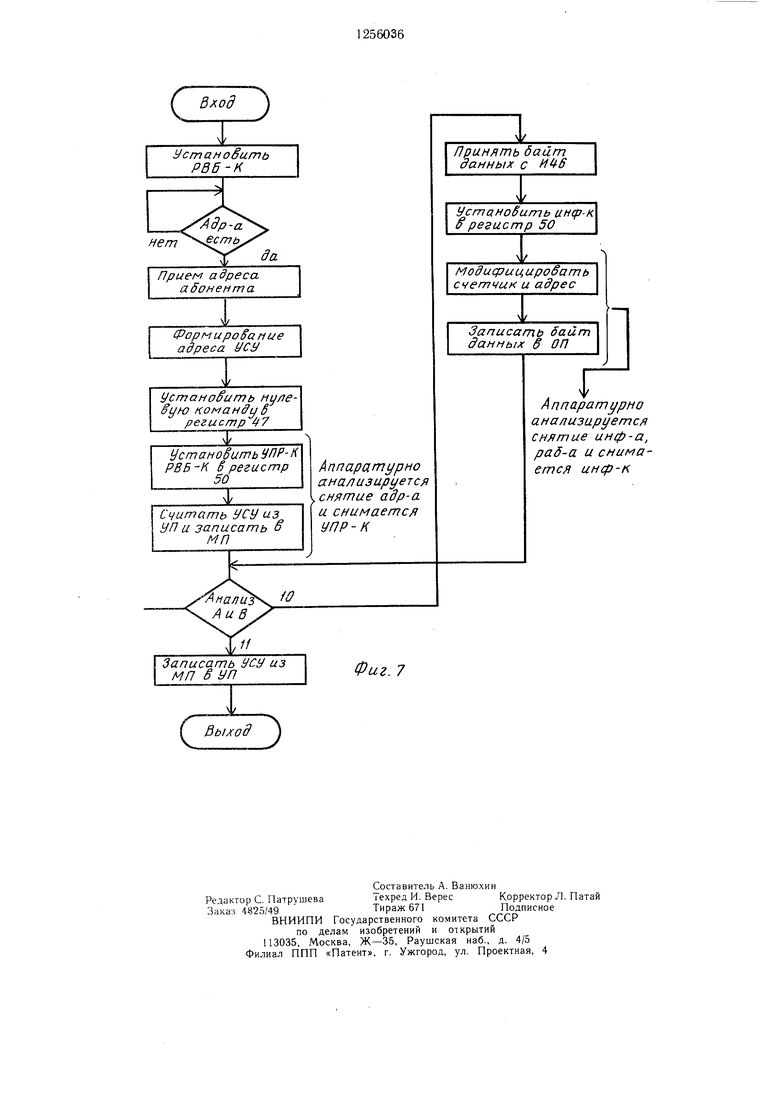

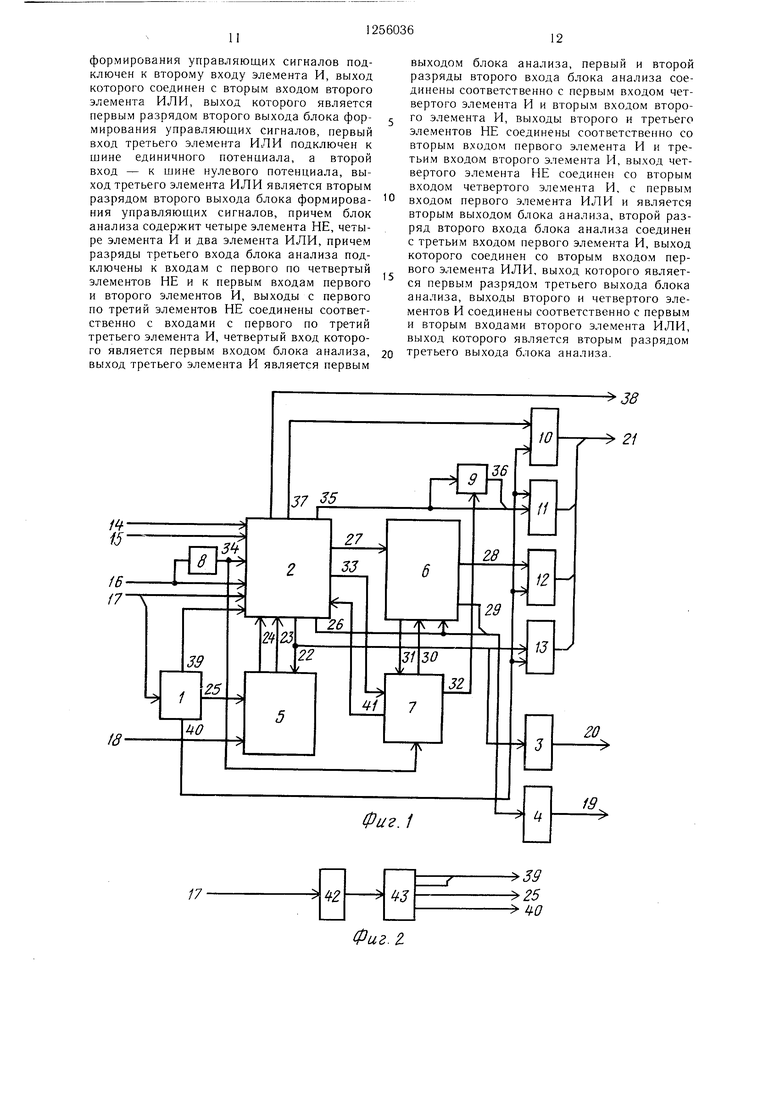

На фиг. 1 изображена схема микропрограммного мультиплексного канала; на фиг. 2 - схема блока дешифрации команд; на фиг. 3 - схема блока регистров; на фиг. 4 - схема блока коммутатора; на фиг. 5 -- схема блока формирования управляющих сигналов; на фиг. 6 - схема блока анализа; на фиг. 7 - схема алгоритма передачи байта данных от абонента в канал по инициативе абонента.

МикропрО1 раммный мультиплексный канал (фиг. 1) содержит блок 1 дешифрации команд, блок 2 регистров, регистры - второй 3 и первый 4, блок 5 коммутации, блок 6 формирования управляющих сигналов, блок 7 анализа, элемент НЕ 8, узел 9 свертки по модулю два 9, четыре группы элементов И - четвертая 0, третья П, вторая 12 и первая 13, информационный выход 14 абонента, вход 15 включения питания, синхровыход 16 процессора, информационный выход процессора 17, управляющий выход 18 абонента, управляющий вход 19 абонента, информационный вход 20 абонента, информационный вход 21 процессора, информационный вход 22 блока коммутации, первый информационный выход 23 блока коммутации, второй информационный выход 24 блока коммутации, нервый управляющий вход 25 блока коммутации, первый выход груцпы информационных разрядов 26 блока регистров, нервый выход 27 группы управляющих разрядов блока регистров, пер- вый выход 28 блока формирования управляющих сигналов, второй выход 29 блока формирования управляющих сигналов, второй выход 30 блока анализа, второй вход 31 блока анализа, третий выход 32 блока анализа, второй выход 33 грунны управляю- тих разрядов блока регистров, выход 34 элемента НЕ, второй выход 35 группы информационных разрядов блока регистров, выход 36 узла свертки но модулю два, второй информационный выход 37 блока регистров, вход 38 приостановки процессора, третий выход 39 блока дешифрации команд, первый выход 40 блока ден1ифрации команд, первый выход 41 блока анализа.

Блок дeнJифpaции команд 1 (фиг. 2) содержит регистр 42 микрокоманд и дешифратор 43 микрокоманд.

Блок регистров 2 (фиг. 3) содержит регистр 44 подсинхроннзации, регистр 45 приема, группу элементов И 46, регистр 47

0

0

0 5

выдачи, D-триггер 48, первый регистр 49, второй регистр 50.

Блок 5 коммутатора (фиг. 4) содержит элемент НЕ 51, две группы элементов И 52 и 53, группу элементов ИЛИ 54.

Блок формирования управляющих сигналов (фиг. 5) содержит элемент И 55, три элемента ИЛИ 56-58, первый, второй и третий соответственно, два элемента НЕ 59 и 60 второй и первый соответственно, узел 61 свертки по модулю два.

Блок 7 анализа (фиг. 6) содержит четыре элемента НЕ 62-65, четыре элемента И 66-69, третий, нервый, второй и четвертый соответственно, два элемента ИЛИ 70 и 71.

Блок 1 дешифрации команд служит для нриема с информационного выхода 17 микрокоманды в регистр микрокоманды 42 и де- щифрации микрокоманд при помощи дешифратора 43, нервый, второй, третий и четвертый выходы которого являются результатом дешифрации микрокоманд, записи информации в регистр 47 выдачи, записи информации в триггер 48, первый регистр 49, второй регистр 50 диагностики, по которой разрешается запись информации из регистра 47 выдачи через группу элементов И 52 в регистр 44 подсинхронизации и чтения, по которой клананируются групповые элементы И 10-13 и информация с них поступает на информационный выход к процессору 21.

Блок 2 регистров предназначен для приема информации от абонента на группу элементов И 46 с информационного выхода абонента 14 и выдачи информации на первый вход группы элементов И 10, приема информации с инфор.мационного выхода 23 в регистр 44 подсинхронизации с последующим приемом этой информации в регистр 45 приема и выдачи с первого, второго, третьего, четвертого, пятого выходов регистра 45 приема на информационный выход 35, а с первого, второго, шестого и седьмого выходов на выход 33, приема информации в регистр 47 выдачи с информационного выхода процессора 17 и выдачи информации с выхода регистра 47 выдачи через блок 5 коммутации в регистр 44 подсинхронизации в случае диагностирования или через группу элементов И 13 на информационный вход процессора 21 для организации контроля переданной из процессора информации в регистр 47 выдачи путем ее сравнения в процессоре и через второй регистр 3 на информационный вход 20 абонента в случае передачи информации к абоненту, приема унравляю- щих сигналов для абонента с информационного выхода процессора 17 на триггер 48, первый и второй регистры 49 и 50 и выдачи управляющих сигналов с выхода триггера 48, первого, второго выходов первого регистра 49 и с первого, второго выходов второго регистра 50 на информационный выход 26 для выдачи через первый регистр 4 управляющих си|-налов к абопспту и D блок 6

формирования управляющих сигналов, выдачи с четвертого выхода регистра 45 приема управляющего сигнала на вход 38 приостановки процессора, для организации сброса второго регистра 50 сигналом с управ- ляющего входа сброса, выдачи управляющих сигналов с третьего, четвертого выходов регистра 49 на управляющий выход 27.

Блок коммутатора 5 используется для коммутации информации с управляющего выхода 18 абонента через группу элементов И 53 и группу элементов ИЛИ 54 в регистр 44 подсинхронизации в рабочем режиме или информации с регистра 47 выдачи через группу элементов И 52 и группу элементов ИЛИ 54 в регистр подсинхронизации 44 в диагностическом режиме.

Блок 6 формирования управляющих сигналов служит для формирования некоторых управляющих сигналов, необходимых для управления работой аппаратуры канала - это сигналы с элементов НЕ 59 и 60, поступающих через вход 31 в блок 7 анализа, необходимых для управления работой периферийных устройств - сигналы с элементов ИЛИ 57 и 58, поступающих на выход 29 и далее через регистр 4 на управляющий вход абонента 19, а также для возможности контроля сравнением в процессоре информации, принятой с информационного выхода процессора 17, во-первых, в регистр 47 выдачи, информация с которого поступает через второй регистр 3 на информацион- ный вход абонента 20 в виде обменного байта данных с периферийными устройствами, а также для контроля сравнением в процессоре через rpynriy элементов И 13 на информационный вход процессора 21, и во-вторых, в триггер 48, регистры 49 и 50, с выходов которых информация поступает в блок 6 формирования управляющих сигналов, где эта информация поступает с выходов 26 и 27 на элемент 61 для формирования к этой информации контрольного раз- ряда и на выход 28 вместе с контрольным разрядом с выхода элемента 61 и через группу элементов И 12 на информационный вход процессора 21.

Блок 7 анализа используется для выработки управляющих сигналов с выхода элемента И 66 и с элемента НЕ 65, которые через выход 41 и выход 30 поступают на сбросовый вход регистра 50 и на второй вход элемента И 55 соответственно с целью исключения микропрограммного анализа наиболее часто участвующих в управлении уп- равляющих сигналов, что сокращает объем канальных микропрограмм, и следовательно, время их выполнения, а также формирования определенной комбинации управляющих сигналов, получаемых с выходов элементов ИЛИ 70 и 71, которые поступают в процессор через группу элементов И 11, после анализа которых микропрограммным путем канальная .микропрограмма определяет состояние

5

0 5 0

5 -

5

трех управляющих сигналов, за счет чего сокращается объем канальных микропрограмм, и следовательно, время их выполнения.

Элемент НЕ 8 используется для инверсии принятого с синхровхода 16 синхронизирующего сигнала о дальнейщем использовании прямого и инверсного синхронизирующих сигналов для управления приемом информации в регистры 44 и 45 блока 2 регистров и для выработки в определенное вртмя управляющего сигнала с выхода элемента И 66 в блоке 7 анализа.

Узел свертки по модулю два 9 служит для формирования контрольного разряда к информации, которая поступает на его вход из блока 7 анализа и блока 2 регистров соответственно и выдачи этого контрольного разряда на первый вход группы элементов И 11.

Группы элементов и 10-13 используются для коммутации при помощи управляющего сигнала, поступающего с выхода блока 40 дешифрации, информации, поступающей из блока 2 регистров с выхода группового эле- .мента И 46 на первый вход четвертой группы элементов И 10, блока 2 регистров с выхода регистра 45 приема через информационный выход 35, из блока 7 анализа с элементов ИЛИ 70 и 71 и с выхода 36 на первый вход третьей группы элементов И II, из блока 6 формирования с выхода 28 на первый вход второй группы элементов И 12, из блока регистров 2 с выхода регистра 48 выдачи на первый вход первой группы элементов И 13 с последующей одновременной выдачей с выходов групп элементов И 10- 13 информации на информационный вход процессора 21.

Микропрограммный мультиплексный канал работает под управлением канальных микропрограмм, расположенных совместно с процессорными микропрограммами в памяти .микропрограмм (управляющей памяти). Это позволяет в любой момент времени выполнять или микропрограммы процессора или микропрограммы мультиплексного канала.

Микропрограммы мультиплексного канала являются более приоритетными по отно- щению к процессорным микропрограммам. Поэтому как только возникает необходимость в выполнении канальных микропрограмм, процессорные микропрограммы немедленно приостанавливаются. Начинается выполнение канальных микропрограмм. После их выполнения выполнение процессорных микропрограмм продолжается.

Операция ввода-вывода в микропрограммном мультиплексном канале начинается по специальной команде процессора, которая задает адреса канала и периферийного устройства и при помощи специальных управляющих слов канала, которые указываются или в проблемной программе, или формируются при помощи специальной управляющей программы (например, супервизор

ввода-вывода) указывает код команды, начальный адрес оперативной памяти для организации обмена данными, количество передаваемых байт данных и другие управляю - щие признаки, по которым под управлением специальпой канальной микропрограммы формируется управляюн ее слово устройства.

Формирование управляющего слова устройства выполняется с использованием нескольких ячеек в местной памяти процессора, построенной на полупроводниковых запо минаюна,их элементах, быстродействие которых соизмеримо с быстродействием регистровой памяти, что позволяет значительно сократить время работы канальных микропрограмм. С этой же целью управляющее слово устройства, если его необходимо сохранить, переписывается из местной памяти процессора не в оперативную память, а в управ- память, быстродействие которой гораздо вьппе оперативной памяти.

Так как канал может работать с несколь- кими периферийными устройствами (абонентами) одновременно, то для каждого абонента необходимо сохранять его управляющее слово. Для этой цели в управляющей памяти отводится специальная область для хранения управляющего слова для каждого абонента. Причем общая область в управляющей памяти для хранения всех управляющих слов отводится таким образом, чтобы выборку управляющих слов из управляющей памяти можно бы организовать по адресу периферийного устройства, совмещенного с он- ределенной базой, определяющей начало массива. Это позволяет простым способом быстро извлекать из управляющей памяти управляющее слово для конкретного периферийного устройства. Извлеченное из управляющей памяти управляющее слово помещается в местную память процессора, и при необходимости обратно переписывается в управляющую память. Таким образом, возможность одновременной работы канала с несколькими периферийными устройствами определяется количеством управляющих слов, которые могл т храниться в управ- ;1яющсй памяти, т.е. объемом управляющей памяти или количеством подканалов, отведенной для хранения управляюп 1их слов. В местной памяти используется столько ячеек, сколько необходимо для хранения одного управляющего слова.

После формирования управляющего слова устройства канальная микропрограмма начинает организовывать связь с периферий- ным устройством (абонентом) но специальному интерфейсу ввода-вывода. При этом информационный байт данных вместе с контрольным разрядом из процессора передается к абоненту через информационный вход от процессора 17, регистр 47 выдачи во второй информационный вход 22 блока 2 регистров и регистр 3. Управляющие идентификаторы канала из процессора передаются

О

0 5 о 5

0 5

к абоненту через информационный вход от процессора 17, триггер 48, регистры 49 и 50, информационные выходы 22 и 26 блока 2 регистров и с выходов элемента ИЛИ 58 и 57 через выход 29 блока 6 формирования управляющих сигналов и далее через регистр 4 на управляющий выход к абоненту 20. Причем с выхода триггера 48 выдается идентификатор работы от канала - РАБ-К, с первого по четвертый выходы регистра 49 выдаются идентификаторы распространения выборки от канала - РВБ-К, адрес от капала - АДР-К, прерывания - ПРЕР, блокировка от канала - БЛК-К соответственно, с первого и второго выходов регистра 50 выдаются идентификаторы управления от канала - УПР-К и информация от канала - ИНФ-К.

Информационный байт данных вместе с контрольным разрядом от абонента к процессору поступает с информационного входа от абонента 14 через группу элементов И 46, группу элементов И 10 и информационный выход к процессору 21. Управляющие сигналы от абонента к процессору поступают с группового управляющего входа от абонента 18 через группу элементов И 53, группу элементов ИЛИ 54 в блок 2 регистров по информационному входу 23 и далее через регистр 44, подсинхронизации, регистр 45 приема, через информационный выход 35 блока 2 регистров и с выходов элементов ИЛИ 70 и 71 через информационный выход 32 блока 7 анализа вместе с сформированным на узле 9 контрольным разрядом через группу элементов И 11 и информационный выход к процессору 21. Причем с первого, второго,третьего, четвертого, пятого шестого и седьмого выходов регистра 45 приема выдаются идентификаторы работы от абонента - РАБ-А, адрес от абонента - АДР-А, выборка от абонента - ВБР-А, требования от абонента - ТРБ-А, отключение от абонента - ОТК-А управление от абонента - УПР-А и информация от абонента - ИНФ-А соответственно. Контроль переданной информации из процессора в канал по информационному входу от процессора 17 и правильность работы,связанной с этой передачей оборудования канала, выполняется путем возврата этой информации в процессор через группы элементов И 12 и 13 и ее сравнения в процессоре с переданной. Этот контроль выполняется в процессе работы канала при передаче данных из процессора к абоненту.

Контроль работы оборудования канала, связанного с передачей данных из абонента в. процессор, осуществляется в диагностическом режиме путем занесения в регистр 45 приема фиктивных идентификаторов от абонента через регистр 47 выдачи и блок 5 коммутации с дальнейщим анализом снятых с группы элементов И 12 и информационного выхода к процессору 21 заранее известных идентификаторов.

Установка всех идентификаторов от канала, кроме идентификатора выборки от канала - ВБР-К, выполняется микропрограммным путем. Установка идентификатора РАБ-К выполняется еыде и управляющим сигналом при включении питания процессора по управляющему входу 15 включения питания. Установка сигнала ВБР-К выполняется автоматически при включении питания и выдается с элемента ИЛИ 58 на соответствующий разряд регистра-усилителя 4 постоянно.

Сброс всех идентификаторов от канала также выполняется микропрограммным путем. Однако наиболее часто встречающиеся идентификаторы - УПР-К и ИНФ-К могут сбрасываться и аппаратным путем в процессе работы канала при связи с абонентом. Аппаратнь й сброс идентификаторов выполняется в регистре 50 путем выработки сигнала сброса с элемента И 66, который появляется на выходе этого элемента при отсутствии идентификаторов от абонента АДР-А, УПР-А, ИНФ--А и отсутствия синхросигнала, поступающего из процессора в канал через синхровыход 34 на четвертый вход элемента И 66.

Наличие или отсутствие идентификаторов от абонента анализируются микропрограммным путем. Однако для более быстрого анализа часто используемых в управлении идентификаторов от або.чента РАБ-А, АДР-А, ИНФ-А и УПР-А в комбинации с наличием или отсутствием идентификаторов от канала АДР--К, УПР-К, ИНФ-К в канале аппаратно формируются два специальных управляю цих сигнала - сигнал А с выхода элемента ИЛИ 70 и сигнал В с выхода элемента ИЛИ 71, комбинации которых, анализируемые одной микрокомандой в npotieccope, идентичны анализу трех идентификаторов от абонента: РАБ-А, УПР-А, ИНФ-А, для анализа которых потребовалось бы три микрокоманды.

Комбинации сигналов А и В показаны в таблице.

Значение

РАБ---А установлено ИНФ-А установлено УПР-А установлено РАБ-А снято

Кроме этого, если в канале есть конечное прерывание типа КАНАЛ КОНЧИЛ, что анализируется микропрограммным путем, микропрограммно в регистре 49 устанавливается признак прерывания, который с третьего выхода регистра 49 поступает через вход 27 блока формирования управляющих сигналов на нервЕзГЙ вход элемента И 55, на второй вход которого поступает инверсный идентификатор РАБ-А. Таким образом, идентификатор БЛК-К автоматически фор0

5

0

5

0

5

0

5

0

мируется в канале и выдается к абоненту при отсутствии идентификатора РАБ-А до тех пор. пока не будет обработано конечное прерывание, т.е. пока не будет снят сигнал прерывания микропрограммным путем.

Идентификатор от абонента ТРБ-А с четвертого выхода регистра 45 через вход 38 приостановки поступает в процессор. В конце каждой микрокоманды процессор анализирует наличие этого сигнала и, если он есть, приостанавливает выполнение процессорных микропрограмм и начинает выполнение канальных микропрограмм.

На фиг. 7 показана блок-схема алгоритма передачи байта данных из абонента в канал по инициативе абонента.

Связь по инициативе абонента начинается с выдачи абонентом в канал идентификатора ТРБ-А. Этот идентификатор с входа 38 приостановки, поступает в процессор. Процессор в конце выполнения каждой микрокоманды анализирует наличие сигнала ТРБ-А. Сигнал ТРБ-А есть, процессор приостанавливает выполнение процессорных микропрограмм и начинает выполнение канальных. Таким образом, осуществляется вход в канальную микропрограмму. Далее по алгоритму канал выставляет идентификатор РВБ-К, абонент выставляет свой адрес и идентификатор АДР-А, канал, анализируя наличие идентификатора АДР--А, принимает адрес от абонента. По адресу абонента и базе микропрограммно формируется адрес управляющего слова устройства (УСУ), после чего канал отвечает абоненту выдачей идентификатора УПР-К и снятием идентификатора РВБ - К. что говорит абоненту о том, что адрес абонента воспринят (выдача УПР-К) и что абонент может продолжать связь по своей инициативе (снятие РВБ-К). Далее канал считывает УСУ из управляющей памяти (УП) и записывает его в местную память (.1П). В этот момент аппаратным образом анализируется снятие идентификатора АДР-А и аппаратно снимается идентификатор УПР-К. Далее канал анализирует сигналы А и В. Комбинация этих сигналов 10, т.е. абонент выставил байт данных и идентификатор ИНФ-А - канал принимает байт данных и устанавливает идентификатор ИНФ-К, который говорит абоненту о том, что байт данных каналом воспринят. Затем канал модифицирует счетчик и адрес данных и записывает принятый байт данных в оперативную память (ОП). В этот момент аппаратным образом анализируется снятие идентификаторов ИНФ-А, РАБ-.А и аппаратурно снимается идентификатор ИНФ - К. После записи байта данных в оперативную память канал начинает очередной раз анализировать сигналы А и В. Комбинация 10 - канал принимает от абонента очередной байт данных и т.д. Если комбинация сигналов А и В - 11, т.е. абонент снял идентификатор РАБ-А, который говорит каналу о том, что абоцент прекращает связь с каналом, канал записывает управляющее слово устройства из местпой памяти в упраЕ ляющую память. На этом выполнение канальной микропрограммы заканчивается и процессор переходит к продолжению выполнения ранее прерванной процессорной микропрограммы.

Формула изобретения

Микропрограммный мультиплексный капал, содержащий блок дешифрации команд, блок регистров, два регистра, причем информационный выход процессора подключен к информационному входу блока дешифрации команд и к первому информационному входу блока регистров, выходы первого и второго регистров подключены к управляюш.ему входу абонента и к информационному входу абонента соответственно, отличающийся тем, что, с целью повышения надежности за счет сокращения канального оборудования и обеспечения возможности диагностирования оборудования канала, он содержит блок коммутации, блок формирования управляющих сигналов, блок анализа, элемент НЕ, узел свертки по модулю два, четыре группы элементов И, причем информационный выход абонента подключен к второму информационному входу блока регистров, выход первого информационного разряда блока регистров соединен с информационным входом второго регистра, выход первой группы информационных разрядов блока регистров соединен с входом первой группы информационных разрядов первого регистра, информационный вход блока коммутации соединен с выходом первого информационного разряда, блока регистров, первые входы элемептов И первой и второй групп соединены с выходом первого информационного разряда блока регистров и первым выходом блока формирования управляющих сигналов соответственно, вторые входы элементов И первой и второй групп соединены с первым выходо.м блока дешифрации команд, первый и второй информационные выходы блока коммутации соединены с третьим информационным и разрешающим входами блока регистров соответственно, первый управляющий вход блока коммутации соединен с вторым выходом блока дешифрации команд, а второй управляющий вход блока коммутации подключен к управляюн;ему выходу абонента, выход синхронизации процессора подключен к входу синхронизации блока регистров и к входу элемента НЕ, выход которого соединен с инверсным входом синхронизации блока регистров и первым входом блока анализа, третий выход блока дешифрации команд соединен с входом записи блока регистров, вход сброса блока регистров соединен с первым выходом блока анализа, выход первой группы информационных разрядов блока регистров соединен с первым

5

0

5

0

0

5

0

5

входом блока формирования управляющих сигналов, выход управляющего разряда блока регистров соединен с входом приостанова процессора, выход первой группы управляющих разрядов блока регистров соединен с вторым входом блока формирования управляющих сигналов, второй выход блока формирования управляющих сигналов соединен с входом второй группы информационных разрядов первого регистра, третий выход блока формирования управляющих сигналов соединен с вторым входом блока анализа, выход второй группы управляющих разрядов блока регистров соединен с третьим входом блока анализа, второй выход блока анализа соединен с третьим входом блока формирования управляющих сигналов, выход второй группы информационных разрядов блока регистров соединен с первым входом узла свертки по модулю два и с первыми входами соответствующих элементов И третьей группы, выход второго информационного разряда блока регистров соединен с первыми входами элементов И четвертой группы, выходы элементов И с первой по четвертую групп подключены к информационному входу процессора, третий выход блока анализа соединен с первыми входами соответствующих элементов И третьей группы и со вторым входом узла свертки по модулю два, выход которого соединен с первым входом соответствующего элемента И третьей группы, вторые входы элементов И третьей и четвертой групп соединены с первым выходом блока дещифрации команд, причем блок формирования управляющих сигналов содержит два элемента НЕ, три элемента ИЛИ, элемент И и узел свертки по модулю два, причем первый, второй и третий разряды первого входа блока формирования управляющих сигналов подключены к входу первого элемента НЕ, к первому и второму входам первого элемента ИЛИ соответственно, выход первого элемента ИЛИ соединен с входом второго элемента НЕ, выходы первого и второго элементов НЕ являются первым и вторым разрядами третьего выхода блока формирования управляющих сигналов, группа разрядов первого входа блока .формирования управляющих сигналов соединена с группой разрядов входа узла свертки по модулю два и является группой разрядов первого выхода блока формирования управляющих сигналов, первый и второй разряды второго входа блока формирования управляющих сигналов подключены к первым входам элемента И и второго элемента ИЛИ соответственно, соединены с первым и вторым разрядами входа узла свертки по модулю два и являются первым и вторым разрядами первого выхода блока формирования управляющих сигналов, выход узла свертки по модулю два является контрольным разрядом первого выхода блока формирования управляющих сигналов, третий вход блока

формирования управляющих сигналов подключен к второму входу элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого является первым разрядом второго выхода блока формирования управляющих сигналов, первый вход третьего элемента ИЛИ подключен к щине единичного потенциала, а второй вход - к шине нулевого потенциала, выход третьего элемента ИЛИ является вторым разрядом второго выхода блока формирования управляющих сигналов, причем блок анализа содержит четыре элемента НЕ, четыре элемента И и два элемента ИЛИ, причем разряды третьего входа блока анализа подключены к входам с первого по четвертый элементов НЕ и к первым входам первого и второго элементов И, выходы с первого по третий элементов НЕ соединены соответственно с входами с первого по третий третьего элемента И, четвертый вход которого является первым входом блока анализа, выход третьего элемента И является первым

выходом блока анализа, первый и второй разряды второго входа блока анализа соединены соответственно с первым входом четвертого элемента И и вторым входом второго элемента И, выходы второго и третьего элементов НЕ соединены соответственно со вторым входом первого элемента И и третьим входом второго элемента И, выход четвертого элемента НЕ соединен со вторым входом четвертого элемента И, с первым входом первого элемента ИЛИ и является вторым выходом блока анализа, второй разряд второго входа блока анализа соединен с третьим входом первого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, выход которого является первым разрядом третьего выхода блока анализа, выходы второго и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого является вторым разрядом третьего выхода блока анализа.

Фиг. г

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для формирования сигнала подключения периферийного устройства к каналу ввода-вывода | 1985 |

|

SU1247881A1 |

Изобретение относится к области вычислительной техники, в частности к организации микропрограммных мультиплексных каналов микропрограммных вычислительных машин и может быть использовано для организации обмена информацией между периферийными устройствами и процессором. Целью изобретения является повышение надежности за счет сокращения начального оборудования и обеспечения возможности диагностирования оборудования канала. Канал содержит блок дешифрации команд, блок регистров, два регистра, блок коммутации, блок формирования управляющих сигналов, блок анализа, элемент НП, узел свертки по модулю два, четыре группы элементов И. 7 и.:1., 1 табл. У Ч4 / СТЯЩ 4t; „,.

25

53

23

22

52

сриг.

3

31

фиг. 5

V/

69

- г

71

32

Фиг. 6

Г влодJ

Принять байт данных с

нет

Прием адреса абонента

Устанобить ин(р-к о рези с тр 50

/

Модисрицироёать c /emчuк и адрес

Форм upoSa ние адреса УСУ

Установить ну/ie- ёую команду ё регистр 7

.

Аппаратурно анализируется .снятие адр-а и снимается УПР- К

Записать байт данных § ОП

1

Аппаратурно а нализируется снятие инф-а, рад-а и снимается инф-ц

11

Г

Фиг. 7

| Мультиплексный канал | 1979 |

|

SU824183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-04-09—Подача