Изобретение относится к преобразова- ельной технике и может использоваться для питания электропривода.

Цель изобретения - повышение надеж10СТИ.

Цель достигается тем, что в непосредст- зенный преобразователь частоты, содержаний трансформатор, вторичная сторона соторого снабжена дополнительными отпайками, блок полностью управляемых клю- ей переменного тока с усилителями - ормирователями сигналов, распределитель управляющих сигналов, задатчик час- готы, причем - начала, концы и дополнительные отпайки вторичных фазных обмотоктрансформатора, а также выходные выводы подключены к блоку ключей, управляющие входы которого связаны с распределителем управляющих сигналов, подсоединенным к задатчику частоты, дополнительно введены задатчик амплитуды и управляемый делитель частоты. При этом через последний подключены к распределителю управляющих сигналов оба задатчика, а задатчик амплитуды связан со входом распределителя также и непосредственно. Вывод первичной стороны трансформатора образуют входные выводы преобразователя.

Вторичная сторона соединена в звезду, а число витков между общей точкой вторичных Фазных обмоток и 1-й дополнительной отпайкой выбрано равным

Wi WH Wi cos (тг/m ),

со со 1 GJ vl

где I 2, 3, 4 ... - номер дополнительной отпайки;АЛ/1, Wi-i -число витков между концом фазной обмотки (общей точкой вторичных обмоток) и соответственно первой дополнительной отпайкой и предыдущей дополнительной отпайкой; m - число фаз согласующего трансформатора (т 2, если число фаз таково, что вектор одного фазного напряжения совпадает с вектором другого противофазного напряжения, то в формулу подставляют т/2).

При этом из ключей, связанных одним полюсом с выводами фазных обмоток трансформатора, образованы m фазных групп путем объединения их вторых полюсов пофазно, а каждый выходной вывод с помощью ключей, образующих две нагрузочные группы, подключен к общей точке каждой фазной группы. Задатчик частоты включает в себя задающий генератор, два делителя частоты и запоминающую ячейку.

Три первых устройства соединены последовательно. Запоминающая ячейка подключена к управляющему входу первого делителя, и вместе со вторым делителем- к распределителю управляющих сигналов. Выход первого делителя связан также с дополнительно введенным управляемым делителем частоты, управляющий вход которого подсоединен к задатчику амплитуды. В распределитель управляющих сигналов в качестве входных устройств включены три реверсивных сдвиговых регистра, при этом первый и третий включены по кольцевой схеме, тактирующий вход первого связан с задатчиком частоты, а в двух других - с дополнительным управляемым делителем частоты. Регистры имеют соответственно 2т выходов XL ха,..., Х2т первый, (2n-i) выходов У1, У2У2п-1 ВТОРОЙ И (2п-2) ВЫХОДОВ Х1,

za22п-2 третий, где п - число доступных

точек на каждой вторичной фазной обмотке. Входы предварительной установки первого регистра соединены с запоминающей ячейкой задатчика частоты, второго - с задатчиком амплитуды, а их управляющие входы соответственно первого - с запоминающей ячейкой, второго и третьего - с нечетными выходами первого регистра через элемент ИЛИ. Выходное устройство распределителя управляющих сигналов представляет собой логический блок, входы которого подключены ко всем выходам названных выше регистров, а выходы связаны с блоком ключей, а именно, с ключами фазных групп выходы Fi.i, F1.2,..., Fi.n; F2,1, F2,2,

.... F2,nl ... Fm,1, Fm.2, ... fm,n И С КЛЮЧЭМИ

нагрузочных групп выходы Li,i, 1.2.1..... Lm.1,

Ll,2, L.2,2,.., Lm,2 И ВЫХОДНЫМИ СИГНЭЛЭМИ

описывается следующими выражениями; .

0

5

0

L1,1 XI + X2m, L2,1 X2m-1 + X2m-2Lm,1

X2 + хз;

Ll,2 Xm + Xm-И, L-2,2 Xm-1 + Xm-2Lm,2

Xm+2 + Xm-KJ,

Fl,1-Ll,l(yi+y2n-l)+ U.2.X1, Fl,2 L1,l(y2

+ У2п-2) + 11.2(Z2 + Z2n-2). .... Fi.n Ll.1,yn +

+Li,2.xn;

F2.1 L2.l(yi + У2П-1) + L2.2.X1,F2,2

L2.1(y2 + У2п-2) + L-2,2(Z2 + Z2n-2)F2,n

,1.Уп +L2.2-Xn;

Fm.1 Lm,l(yi + Y2n-l) + lm.2.zi,Fm,2

.i(y2 + У2П-2) + Lm.2(x2 +X2n-2)Fm,n

Lm.1.yn + Lm,2.Zn.

В настоящее время не известен непосредственный преобразователь частоты,расположение дополнительных отпаек на вторичной стороне согласующего трансформатора в котором выбрано в соответствии с приведенным выше правилом, в систему управления в вёден задатчик амплитуды, который подключается также к распределителю управляющих сигналов непосредственно, а также через дополнительный управляемый делитель частоты, введенный между задатчиком частоты и упомянутым распределителем сигналов.

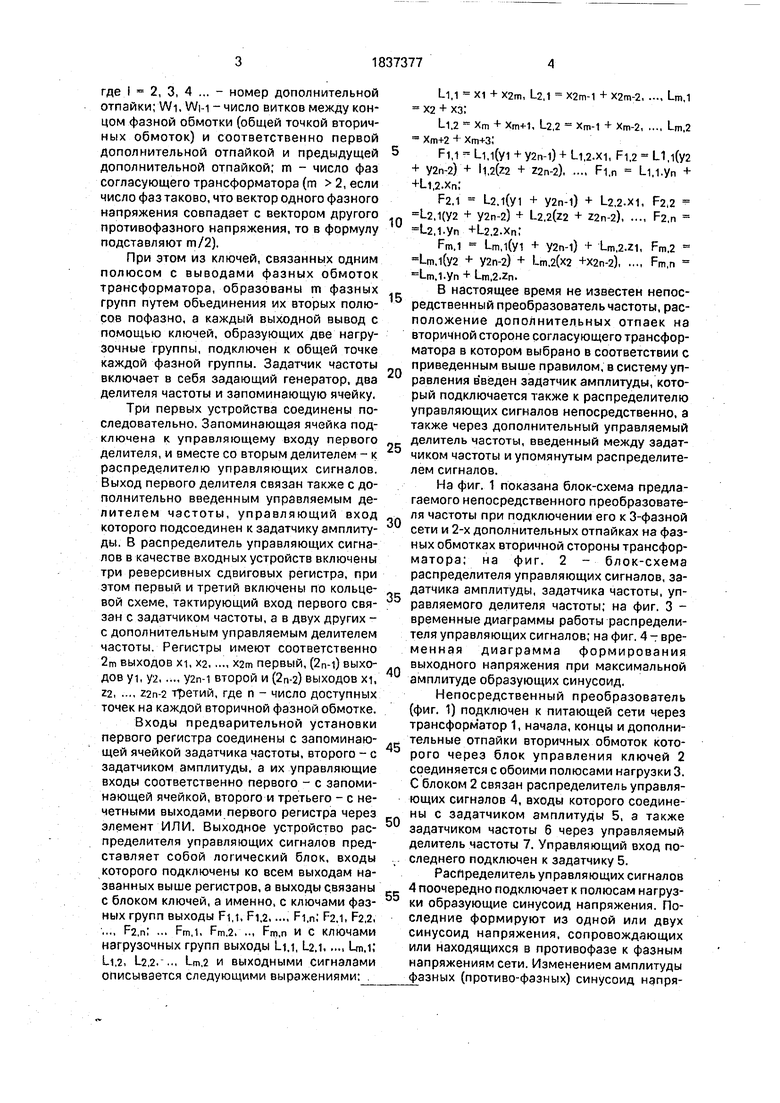

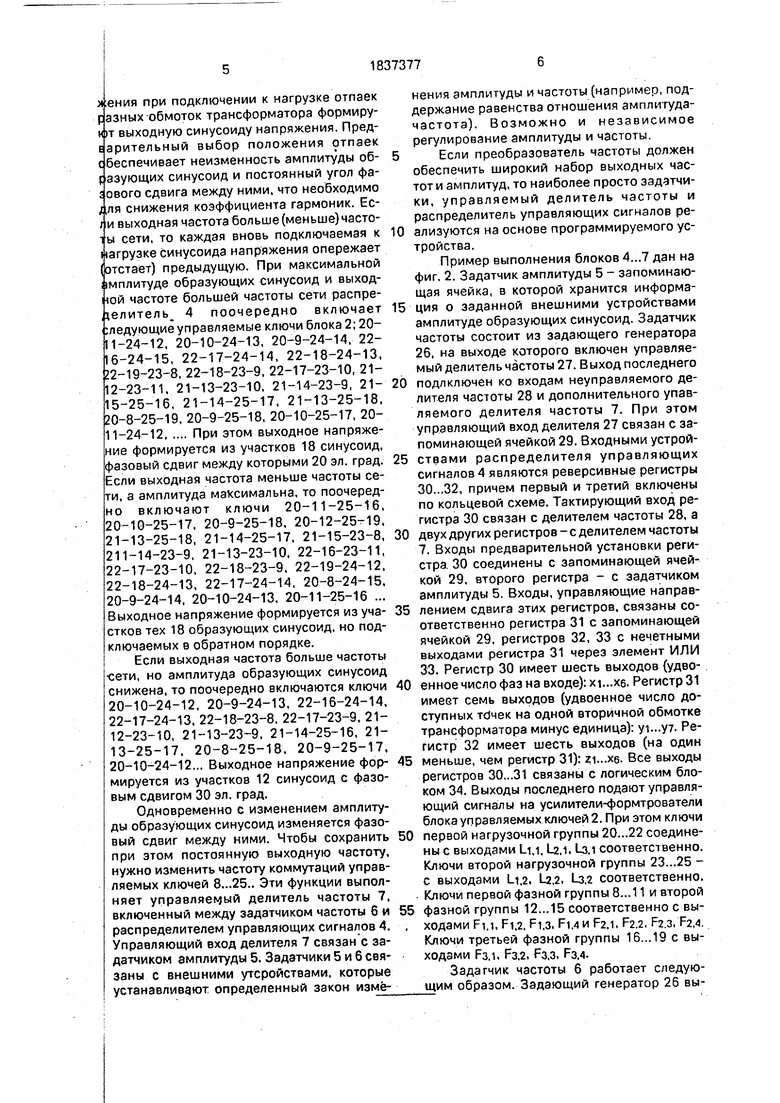

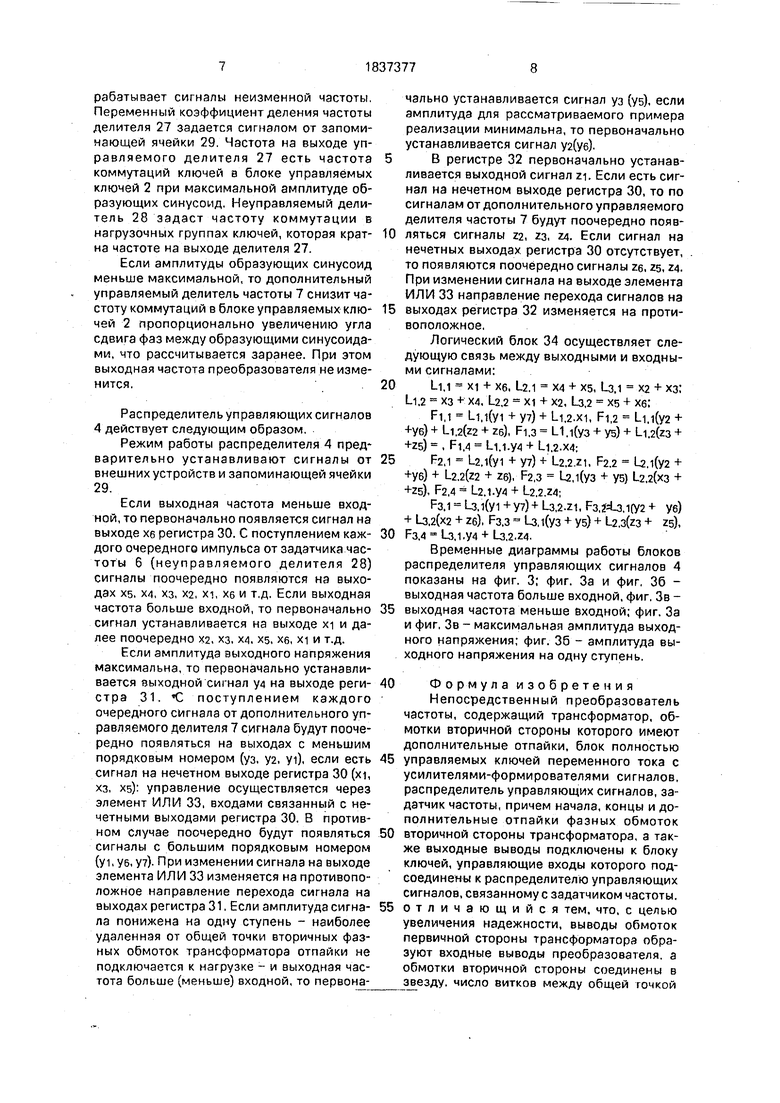

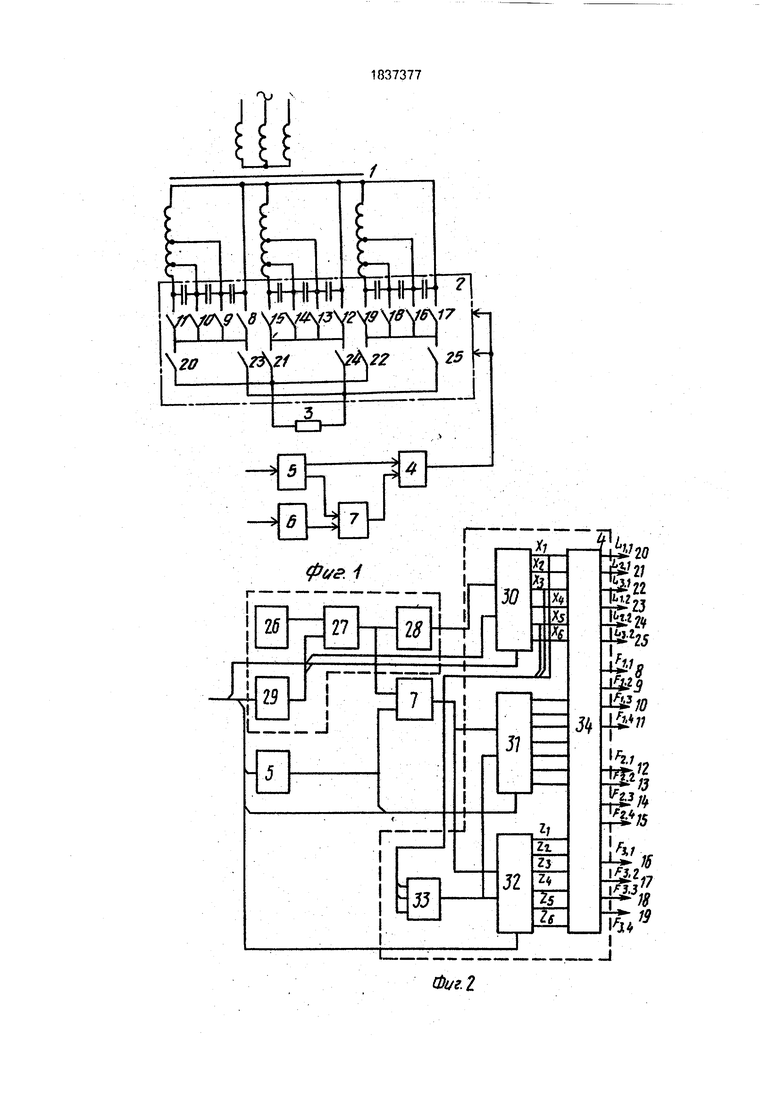

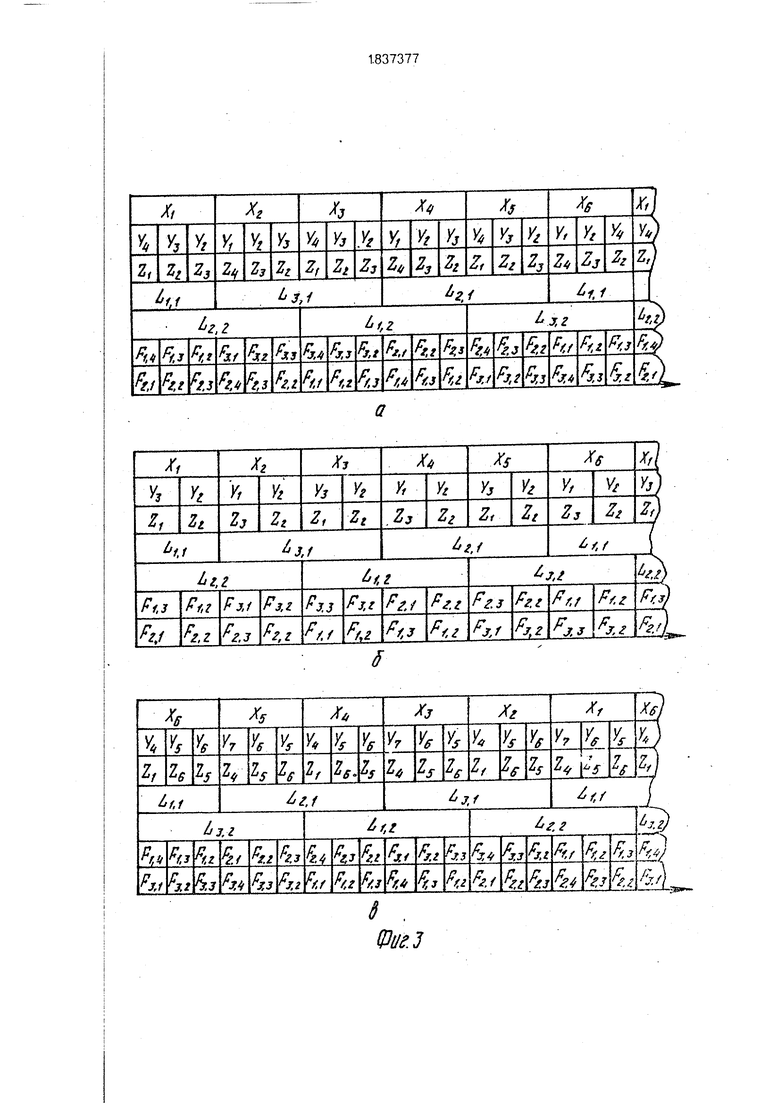

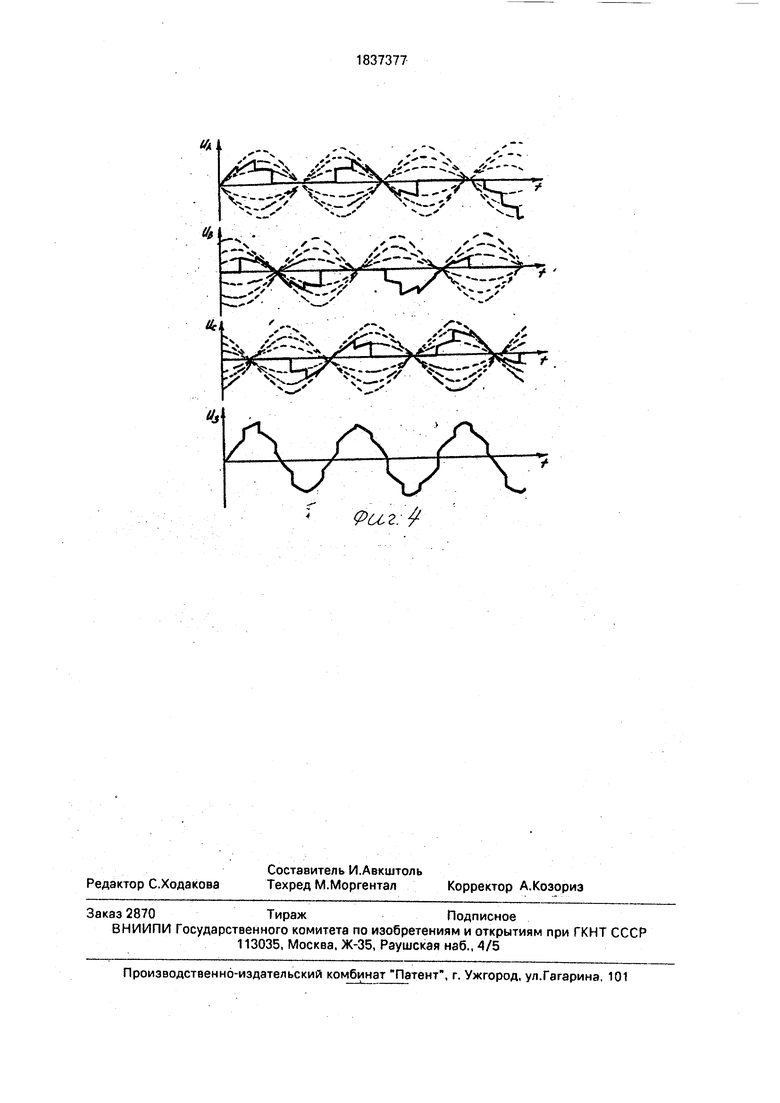

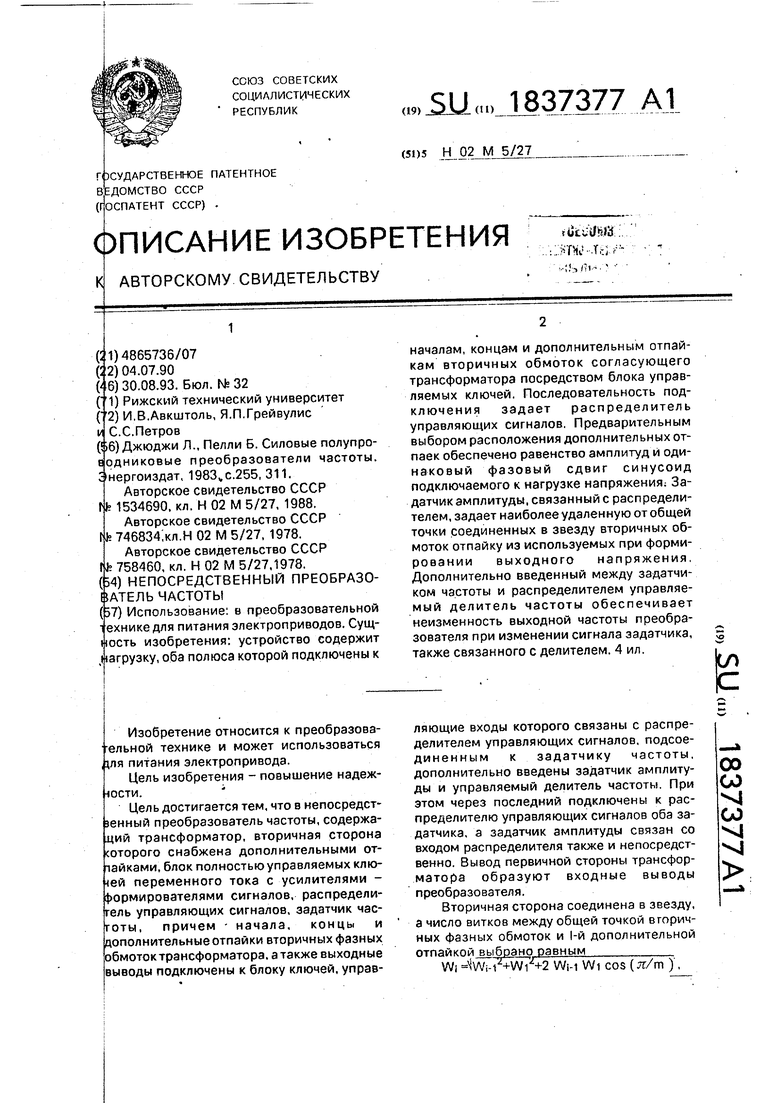

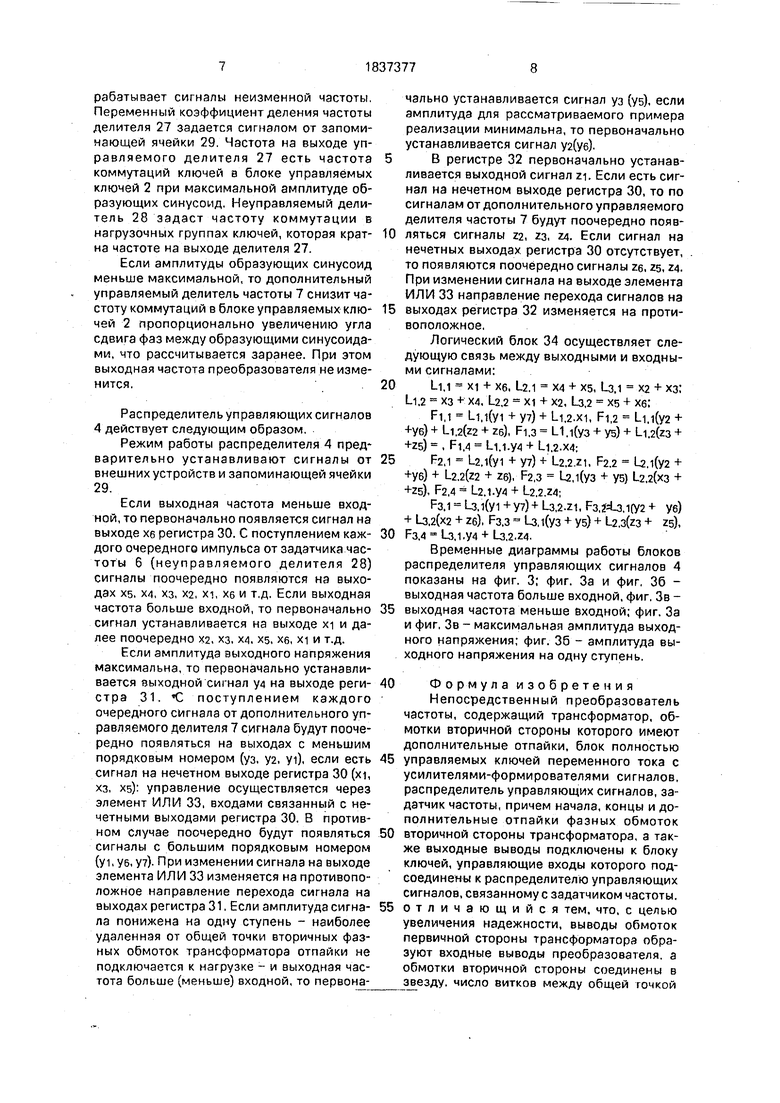

На фиг. 1 показана блок-схема предлагаемого непосредственного преобразователя частоты при подключении его к 3-фазной сети и 2-х дополнительных отпайках на фазных обмотках вторичной стороны трансформатора; на фиг. 2 - блок-схема распределителя управляющих сигналов, задатчика амплитуды, задатчика частоты, управляемого делителя частоты; на фиг. 3 - временные диаграммы работы распределителя управляющих сигналов; на фиг. 4 - вре- менная диаграмма формирования выходного напряжения при максимальной амплитуде образующих синусоид.

Непосредственный преобразователь (фиг. 1) подключен к питающей сети через трансформатор 1, начала, концы и дополнительные отпайки вторичных обмоток которого через блок управления ключей 2 соединяется с обоими полюсами нагрузки 3. С блоком 2 связан распределитель управляющих сигналов 4, входы которого соединены с задатчиком амплитуды 5, а также задатчиком частоты 6 через управляемый делитель частоты 7. Управляющий вход по- ... следнего подключен к задатчику 5.

Распределитель управляющих сигналов 4 поочередно подключает к полюсам нагрузки образующие синусоид напряжения. Последние формируют из одной или двух синусоид напряжения, сопровождающих или находящихся в противофазе к фазным напряжениям сети. Изменением амплитуды фазных (противо-фазных) синусоид напря0

5

0

5

0

ения при подключении к нагрузке отпаек азных обмоток трансформатора формиру- т выходную синусоиду напряжения. Пред- арительный выбор положения отпаек беспечивает неизменность амплитуды об- азующих синусоид и постоянный угол фа- ового сдвига между ними, что необходимо ля снижения коэффициента гармоник. Ес- и выходная частота больше (меньше) часто- ы сети, то каждая вновь подключаемая к агрузке синусоида напряжения опережает отстает) предыдущую. При максимальной мплитуде образующих синусоид и выход- ой частоте большей частоты сети распре- елитель 4 поочередно включает ледующие управляемые ключи блока 2; 20- 1-24-12, 20-10-24-13, 20-9-24-14, 22- 6-24-15, 22-17-24-14, 22-18-24-13, 2-19-23-8, 22-18-23-9, 22-17-23-10, 21- 2-23-11. 21-13-23-10, 21-14-23-9, 21- 5-25-16, 21-14-25-17, 21-13-25-18, 0-8-25-19, 20-9-25-18, 20-10-25-17, 20- 1-24-12, .... При этом выходное напряже- ие формируется из участков 18 синусоид, азовый сдвиг между которыми 20 эл. град, ели выходная частота меньше частоты се- и, а амплитуда максимальна, то поочеред- о включают ключи 20-11-25-16, 0-10-25-17, 20-9-25-18, 20-12-25-19, 1-13-25-18, 21-14-25-17. 21-15-23-8, 11-14-23-9, 21-13-23-10. 22-16-23-11, 2-17-23-10, 22-18-23-9, 22-19-24-12, 2-18-24-13, 22-17-24-14, 20-8-24-15, 0-9-24-14, 20-10-24-13, 20-11-25-16 ... ыходное напряжение формируется из уча- тков тех 18 образующих синусоид, но под- лючаемых в обратном порядке.

Если выходная частота больше частоты сети, но амплитуда образующих синусоид снижена, то поочередно включаются ключи 20-10-24-12, 20-9-24-13, 22-16-24-14, 22-17-24-13. 22-18-23-8. 22-17-23-9, 21- 12-23-10, 21-13-23-9, 21-14-25-16, 21- 13-25-17. 20-8-25-18. 20-9-25-17, 20-10-24-12... Выходное напряжение формируется из участков 12 синусоид с фазовым сдвигом 30 эл. град.

Одновременно с изменением амплитуды образующих синусоид изменяется фазовый сдвиг между ними. Чтобы сохранить при этом постоянную выходную частоту, нужно изменить частоту коммутаций управляемых ключей 8...25.. Эти функции выполняет управляемый делитель частоты 7. включенный между задатчиком частоты 6 и распределителем управляющих сигналов 4. Управляющий вход делителя 7 связан с задатчиком амплитуды 5. Задатчики 5 и 6 связаны с внешними утсройствами. которые устанавливают определенный закон изменения амплитуды и частоты (например, поддержание равенства отношения амплитуда- частота). Возможно и независимое регулирование амплитуды и частоты. 5Если преобразователь частоты должен

обеспечить широкий набор выходных частот и амплитуд, то наиболее просто задатчи- ки, управляемый делитель частоты и распределитель управляющих сигналов ре- 10 ализуются на основе программируемого устройства.

Пример выполнения блоков 4...7 дан на фиг, 2. Задатчик амплитуды 5 - запоминающая ячейка, в которой хранится информа15 ция о заданной внешними устройствами амплитуде образующих синусоид. Задатчик частоты состоит из задающего генератора 26, на выходе которого включен управляемый делитель частоты 27. Выход последнего

0 подлключен ко входам неуправляемого делителя частоты 28 и дополнительного упав- ляемого делителя частоты 7. При этом управляющий вход делителя 27 связан с запоминающей ячейкой 29. Входными устрой5 ствами распределителя управляющих сигналов 4 являются реверсивные регистры 30...32, причем первый и третий включены по кольцевой схеме. Тактирующий вход регистра 30 связан с делителем частоты 28, а

0 двух других регистров -с делителем частоты 7. Входы предварительной установки регистра. 30 соединены с запоминающей ячейкой 29, второго регистра - с задатчиком амплитуды 5. Входы, управляющие направ5 лением сдвига этих регистров, связаны соответственно регистра 31с запоминающей ячейкой 29, регистров 32, 33 с нечетными выходами регистра 31 через элемент ИЛИ 33. Регистр 30 имеет шесть выходов (удво0 енное число фаз на входе): xi...xe. Регистр 31 имеет семь выходов (удвоенное число доступных тбчек на одной вторичной обмотке трансформатора минус единица): у1...уу. Регистр 32 имеет шесть выходов (на один

5 меньше, чем регистр 31): zi...xe. Все выходы регистров 30...31 связаны с логическим блоком 34. Выходы последнего подают управляющий сигналы на усилители-формтрователи блока управляемых ключей 2. При этом ключи

0 первой нагрузочной группы 20...22 соединены с выходами Li,i. La.1.1-3,1 соответственно. Ключи второй нагрузочной группы 23...25 - с выходами ,2. 1-г,2, I-3.2 соответственно. Ключи первой фазной группы 8...11 и второй

5 фазной группы 12,„15 соответственно с вы, ХОДаМИ Fi.l, Fl.2. Fl.3, Fl.4H F2,1, F2.2, F2.3, F2A

Ключи третьей фазной группы 16...19 с выходами Рз.1, F3.2, Рз.З. F3.4.

Задагчик частоты 6 работает следую- щим образом. Задающий генератор 26 вырабатывает сигналы неизменной частоты. Переменный коэффициент деления частоты делителя 27 задается сигналом от запоминающей ячейки 29. Частота на выходе управляемого делителя 27 есть частота коммутаций ключей в блоке управляемых ключей 2 при максимальной амплитуде образующих синусоид. Неуправляемый делитель 28 задаст частоту коммутации в нагрузочных группах ключей, которая кратна частоте на выходе делителя 27.

Если амплитуды образующих синусоид меньше максимальной, то дополнительный управляемый делитель частоты 7 снизит частоту коммутаций в блоке управляемых ключей 2 пропорционально увеличению угла сдвига фаз между образующими синусоидами, что рассчитывается заранее. При этом выходная частота преобразователя не изменится,

Распределитель управляющих сигналов 4 действует следующим образом.

Режим работы распределителя 4 предварительно устанавливают сигналы от внешних устройств и запоминающей ячейки 29.

Если выходная частота меньше входной, то первоначально появляется сигнал на выходе хб регистра 30. С поступлением каждого очередного импульса от зэдэтчика частоты 6 (неуправляемого делителя 28) сигналы поочередно появляются на выходах Х5, Х4, хз, Х2, XL хб и т.д. Если выходная частота больше входной, то первоначально сигнал устанавливается на выходе xi и далее поочередно хз, хз, Х4. xs, xe, xi и т.д.

Если амплитуда выходного напряжения максимальна, то первоначально устанавливается выходной сигнал у4 на выходе регистра 31. С поступлением каждого очередного сигнала от дополнительного управляемого делителя 7 сигнала будут поочередно появляться на выходах с меньшим порядковым номером (уз, У2, yi), если есть сигнал на нечетном выходе регистра 30 (xi, хз, ХБ): управление осуществляется через элемент ИЛИ 33, входами связанный с нечетными выходами регистра 30. В противном случае поочередно будут появляться сигналы с большим порядковым номером (yi. Уб, уу). При изменении сигнала на выходе элемента ИЛИ 33 изменяется на противоположное направление перехода сигнала на выходах регистра 31. Если амплитуда сигнала понижена на одну ступень - наиболее удаленная от общей точки вторичных фазных обмоток трансформатора отпайки не подключается к нагрузке - и выходная частота больше (меньше) входной, то первоначально устанавливается сигнал уз (УБ), если амплитуда для рассматриваемого примера реализации минимальна, то первоначально устанавливается сигнал У2(уе).

В регистре 32 первоначально устанавливается выходной сигнал ZL Если есть сигнал на нечетном выходе регистра 30, то по сигналам от дополнительного управляемого делителя частоты 7 будут поочередно появляться сигналы Z2, 23, 24. Если сигнал на нечетных выходах регистра 30 отсутствует, то появляются поочередно сигналы ze, 25,24. При изменении сигнала на выходе элемента ИЛИ 33 направление перехода сигналов на

выходах регистра 32 изменяется на противоположное.

Логический блок 34 осуществляет следующую связь между выходными и входными сигналами:

Li,i xi + Хб, L-2.1 Х4 + xs, L3.1 Х2 + хз;

L1.2 ХЗ + Х4, L.2,2 Х1 + Х2, ,2 Х5 + Хб.Р

Fl.l Li,i(yi + уу) + Li,2.xi, Fi,2 Li,i(y2 + +уе) + Li,2(z2 + zg), Fi,3 L1,i(ys + ys) + (-1.2(23 + +Z5J , Fl,4 Ll.1.y4 + L1.2.X4;

F2,1 L-2,l(yi + yy) + L-2.2.Z1, F2.2 12.1(У2 +

+Уб) + t-2.2(Z2 + 26), F2,3 L2,l(y3 + У5) L.2,2(X3 + +Z5J, F2.4 L2.1.V4 + .2.Z4;

F3.1 L3.l(yi +УУ)+ L3.2.Z1, Рз,2:4-3,1(У2 + Уб) + L3,2(X2 + 26), Рз.З ет U, 1(УЗ + Уб) + L2,3(23 + Z5), Рз,4 1з,1.У4 + L3,2.24.

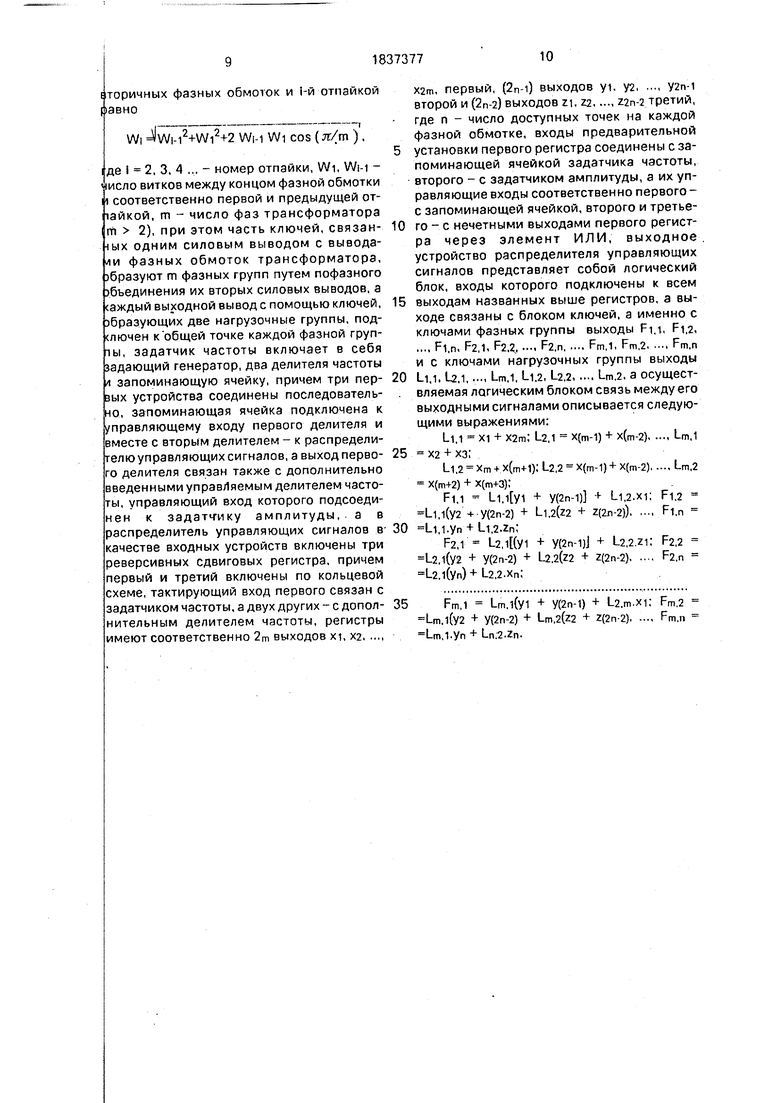

Временные диаграммы работы блоков распределителя управляющих сигналов 4 показаны на фиг. 3; фиг. За и фиг, 36 - выходная частота больше входной, фиг, Зв - выходная частота меньше входной; фиг. За и фиг, Зв - максимальная амплитуда выходного напряжения; фиг. 35 - амплитуда выходного напряжения на одну ступень.

Формула изобретения

Непосредственный преобразователь частоты, содержащий трансформатор, обмотки вторичной стороны которого имеют дополнительные отпайки, блок полностью

управляемых ключей переменного тока с усилителями-формирователями сигналов, распределитель управляющих сигналов, за- датчик частоты, причем начала, концы и дополнительные отпайки фазных обмоток

вторичной стороны трансформатора, а также выходные выводы подключены к блоку ключей, управляющие входы которого подсоединены к распределителю управляющих сигналов, связанному с задатчиком частоты.

отличающийся тем, что, с целью увеличения надежности, выводы обмоток первичной стороны трансформатора образуют входные выводы преобразователя, а обмотки вторичной стороны соединены в звезду, число витков между общей точкой

торичных фазных обмоток и i-й отпайкой эвно

Wi Wi-i +Wi2+2 Wi-1 Wi cos (л/т ),

де i 2, 3, 4 ... - номер отпайки, Wi, Wi-1 - исло витков между концом фазной обмотки i соответственно первой и предыдущей от- 1айкой, m - число фаз трансформатора m 2), при этом часть ключей, связанных одним силовым выводом с выводами фазных обмоток трансформатора, бразуют m фазных групп путем пофазного объединения их вторых силовых выводов, а аждый выходной вывод с помощью ключей, бразующих две нагрузочные группы, под- лючен к общей точке каждой фазной груп- ы, задатчик частоты включает в себя адающий генератор, два делителя частоты i запоминающую ячейку, причем три пер- ых устройства соединены последователь- ю, запоминающая ячейка подключена к правляющему входу первого делителя и месте с вторым делителем - к распредели- елю управляющих сигналов, а выходперво- о делителя связан также с дополнительно веденными управляемым делителем часто- ы, управляющий вход которого подсоеди- ен к задатч%1ку амплитуды, а в аспределитель управляющих сигналов в- ачестве входных устройств включены три еверсивных сдвиговых регистра, причем ервый и третий включены по кольцевой хеме, тактирующий вход первого связан с адатчиком частоты, а двух других - с допол- ительным делителем частоты, регистры меют соответственно 2т выходов xt, X2

Х2т, первый, (2n-i) выходов yi, у2 У2п-1

второй и (2п-2) выходов zi, Z2z2n-2 третий,

где п - число доступных точек на каждой фазной обмотке, входы предварительной

5 установки первого регистра соединены с запоминающей ячейкой задатчика частоты, второго - с задатчиком амплитуды, а их управляющие входы соответственно первого - с запоминающей ячейкой, второго и третье0 го - с нечетными выходами первого регистра через элемент ИЛИ, выходное устройство распределителя управляющих сигналов представляет собой логический блок, входы которого подключены к всем

5 выходам названных выше регистров, а выходе связаны с блоком ключей, а именно с ключами фазных группы выходы Fi.t, Fi,2, .... Fi,n, F2,1, F2.2,.... F2,n, .... Fm,i, Fm,2, .... Fm,n и с ключами нагрузочных группы выходы

0 Li.i. ,1,.... Lm,1, М,2, L.2,2Lm.2. а осущест. вляемая логическим блоком связь между его выходными сигналами описывается следующими выражениями:

L.1.1 XI + X2m; L2.1 Х(т-1) + х(т-2)Ui,1

5 х2 + хз;

L1.2 Хт + х(т-Н); 1-2,2 Х(т-1) + Х(т-2)Lm,2

Х(т+2) + Х(т+3):

Fi.i U, + у(2п-1) + Li,2.xi; Fi,2

U,l(y2 + y(2n-2) + Ll,2(Z2 + 2(2л-2)) Fl.n

0 U,i.yn + Li,2.zn;

F2.1 L2,l(yi + Y(2n-1)j + L2.2.Z1; F2,2

L2,l(y2 + У(2п-2) + L2,2(Z2 + Z(2n-2) F2,n

L2.l(yn) + L2,2.Xn.

5Fm.1 Lm,l(yi + У(2п-1) + L2.m.xi; Fm.2

Lm.l(y2 + У(2п-2) + Lm,2(Z2 + Z(2n-2) Fm,n

m,1.yn + U..Zn.

J

v/wy у

v/7 W-

)

-

)

5

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления электродвигателем переменного тока | 1983 |

|

SU1336188A1 |

| Автономная система электроснабжения стабильной частоты | 1978 |

|

SU758460A1 |

| Автономная система электроснабжения | 1978 |

|

SU771844A1 |

| Преобразователь частоты с квазиоднополюсной модуляцией | 1978 |

|

SU771821A1 |

| СПОСОБ МУЛЯРА УПРАВЛЕНИЯ ЧАСТОТОЙ ВРАЩЕНИЯ M-ФАЗНОГО ЭЛЕКТРОДВИГАТЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ЕГО ВАРИАНТЫ) | 1993 |

|

RU2106054C1 |

| Способ управления вентильным электродвигателем и устройство для его осуществления | 1990 |

|

SU1823082A1 |

| Цифровой измеритель электрической энергии многофазной сети | 1988 |

|

SU1647443A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

| Устройство для управления трехфазным преобразователем постоянного напряжения | 1988 |

|

SU1598084A1 |

m urn

ty

-&21

%з2

Bi

4

l-glO

l&v

u

Ф0 /«

IjSto /

G3Ji

ГГ7

jT

J

СЙуг2

fej

ЯI

,. .- -;Г :--; Лг:

x.-- x ct

/ -V

.

-.4

:j4. x Ј---- s

ff .

-.4

---- -

/,

Риг:#

Авторы

Даты

1993-08-30—Публикация

1990-07-04—Подача