Изобретение относится к электротехнике и может быть использовано для управления электродвигателем, преимущественно с частотным управлением.

Целью изобретения является упрощение конструкции за счет исключения аналоговых преобразователей и обеспечения возможности параллельного преобразования информации и повыщение точности.

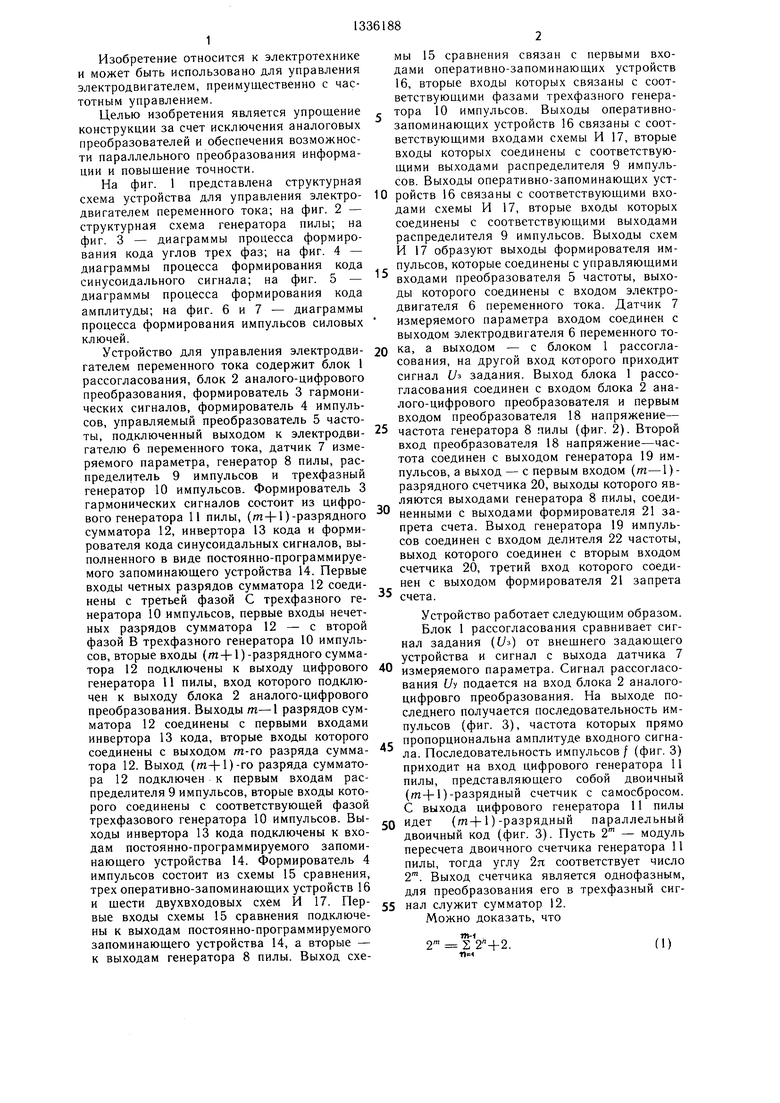

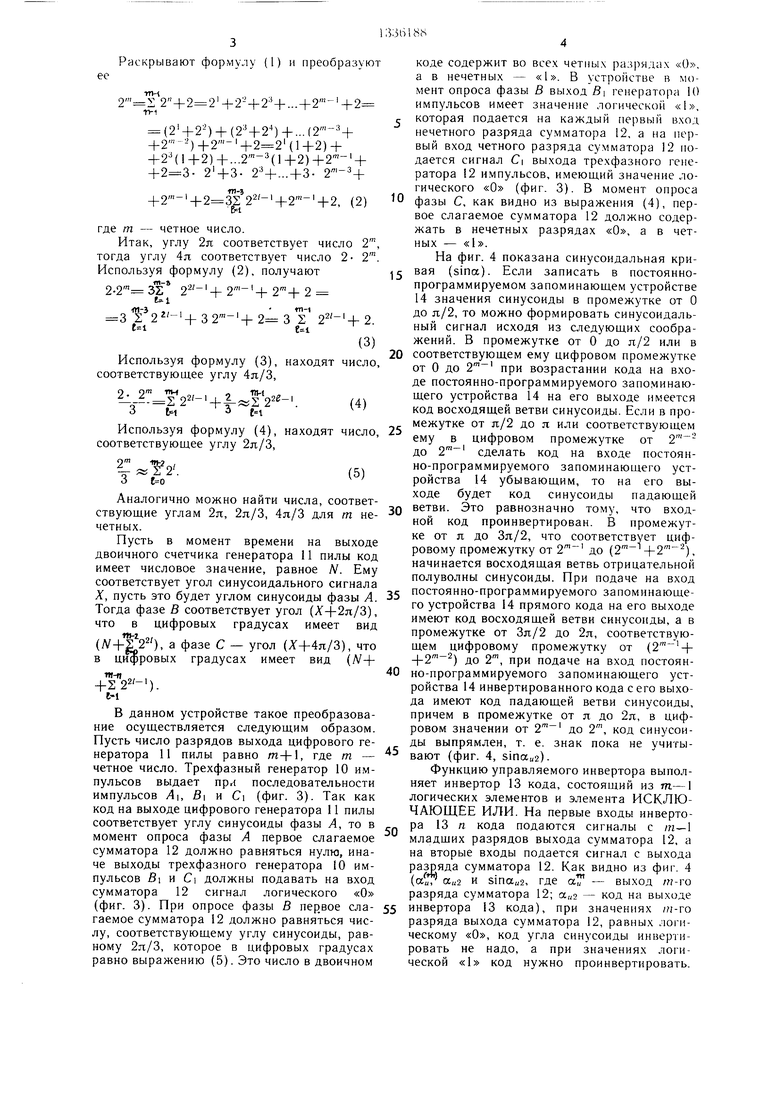

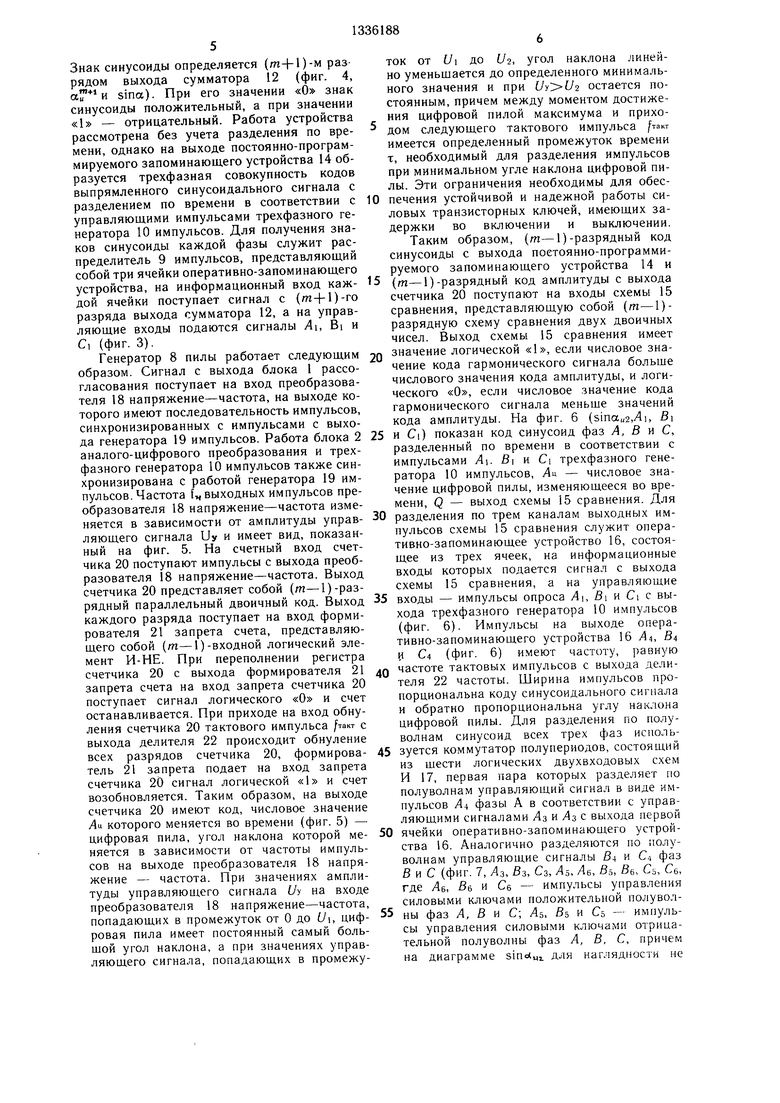

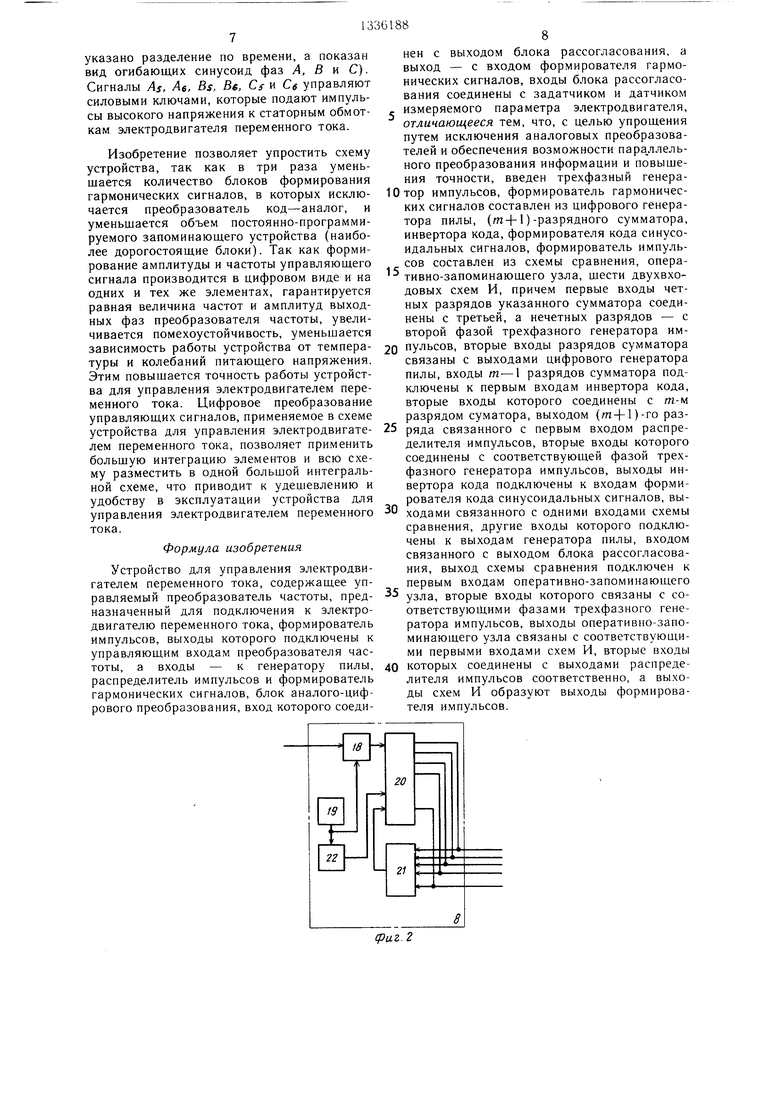

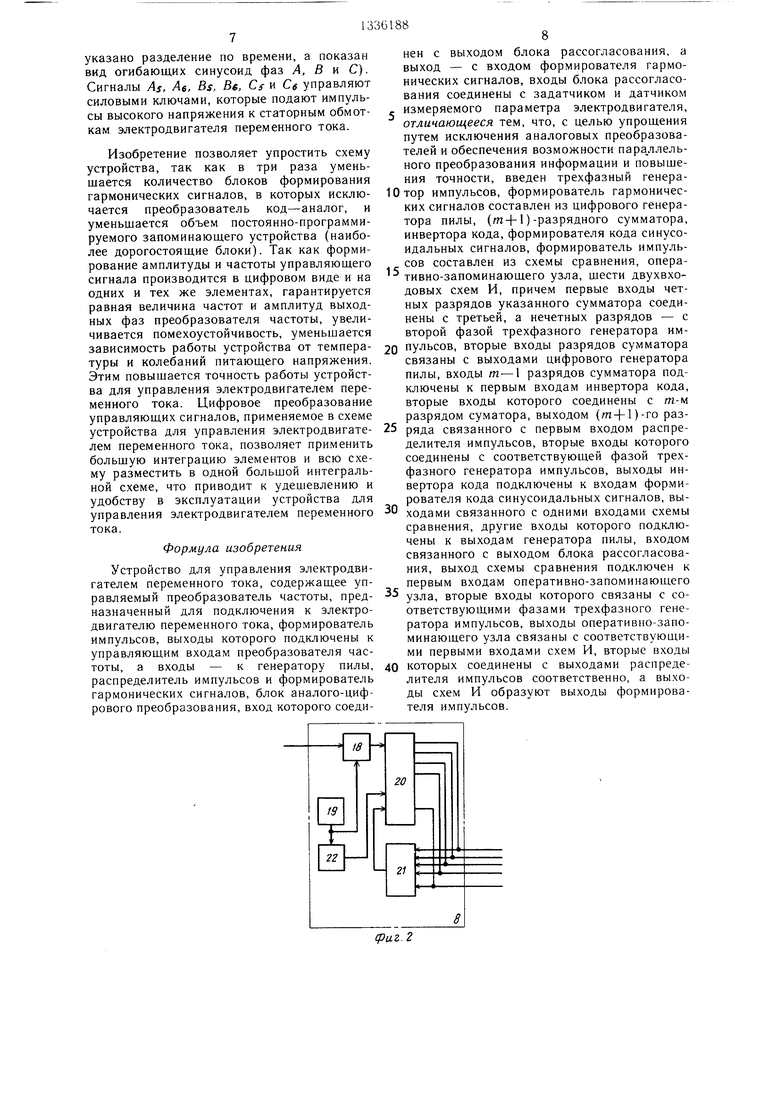

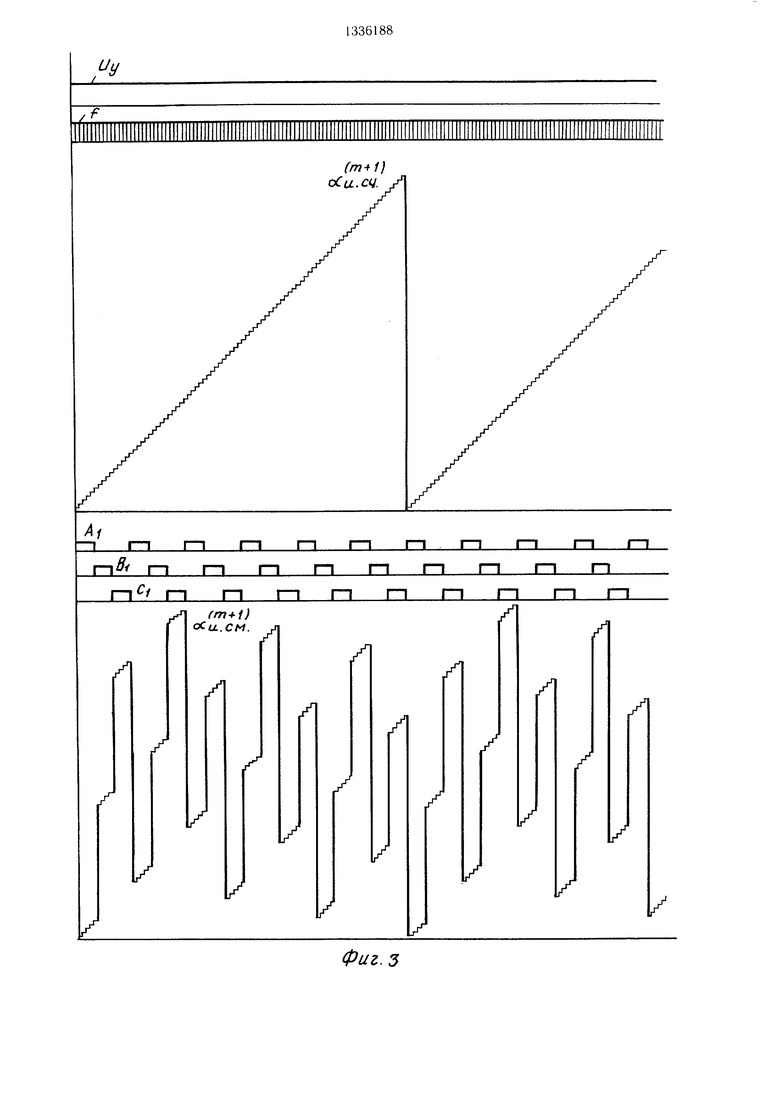

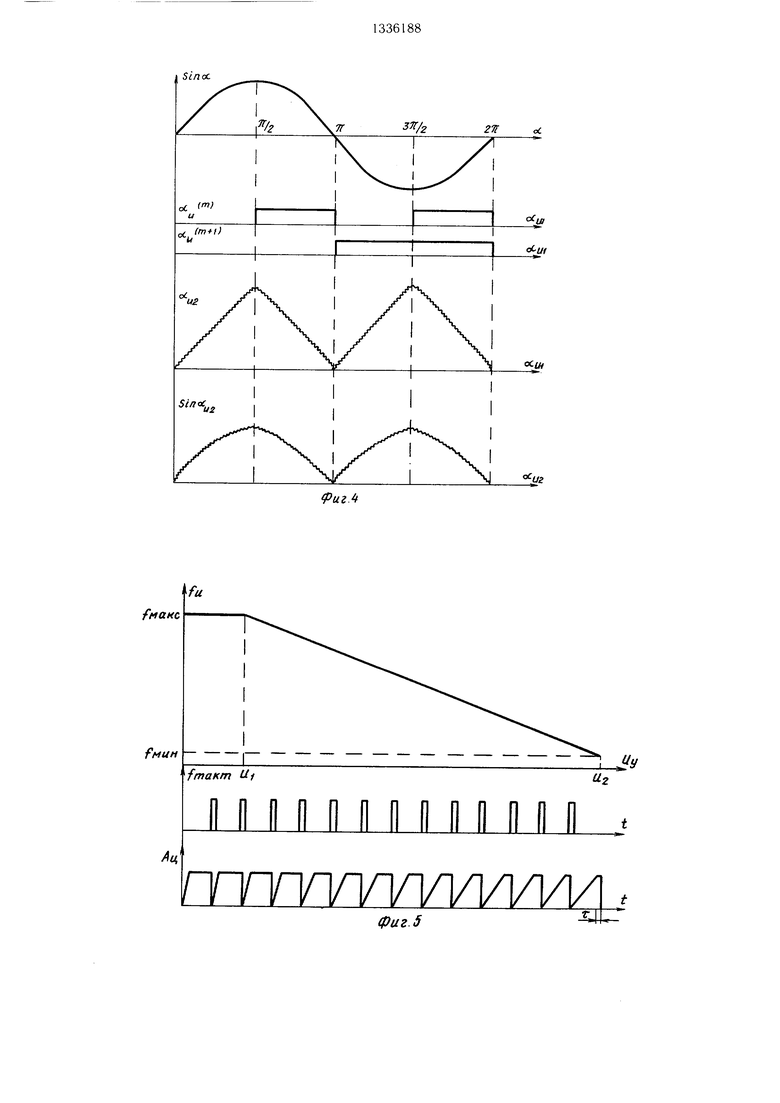

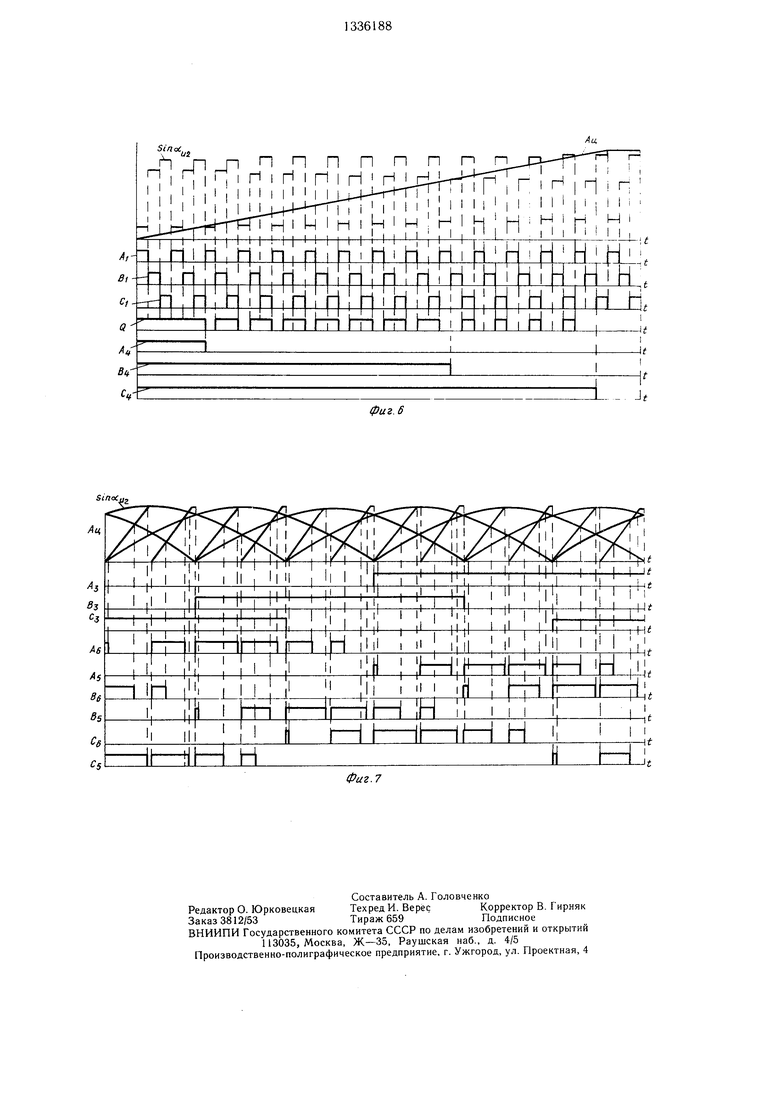

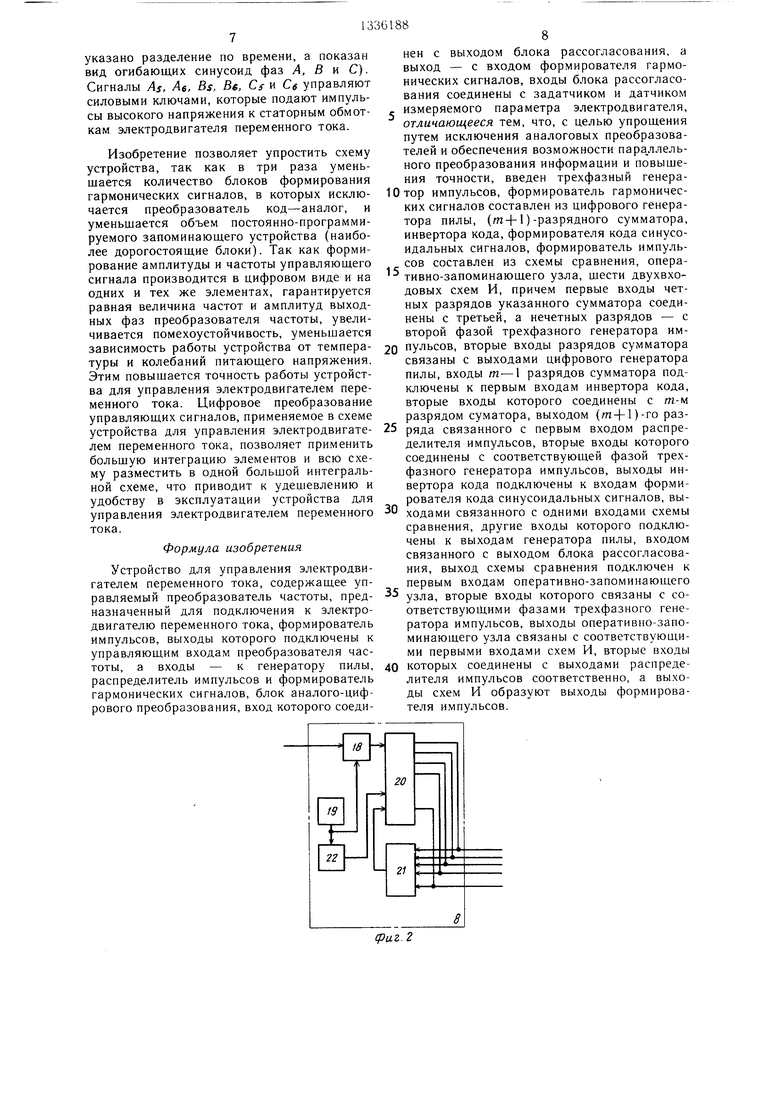

На фиг. 1 представлена структурная схема устройства для управления электродвигателем переменного тока; на фиг. 2 - структурная схема генератора пилы; на фиг. 3 - диаграммы процесса формирования кода углов трех фаз; на фиг. 4 - диаграммы процесса формирования кода синусоидального сигнала; на фиг. 5 - диаграммы процесса формирования кода амплитуды; на фиг. 6 и 7 - диаграммы процесса формирования импульсов силовых ключей.

Устройство для управления электродвигателем переменного тока содержит блок 1 рассогласования, блок 2 аналого-цифрового преобразования, формирователь 3 гармонических сигналов, формирователь 4 импульсов, управляемый преобразователь 5 частоты, подключенный выходом к электродвигателю 6 переменного тока, датчик 7 измеряемого параметра, генератор 8 пилы, распределитель 9 импульсов и трехфазный генератор 10 импульсов. Формирователь 3 гармонических сигналов состоит из цифрового генератора 11 пилы, (т+1)-разрядного сумматора 12, инвертора 13 кода и формирователя кода синусоидальных сигналов, выполненного в виде постоянно-программируемого запоминающего устройства 14. Первые входы четных разрядов сумматора 12 соединены с третьей фазой С трехфазного генератора 10 импульсов, первые входы нечетных разрядов сумматора 12 - с второй фазой В трехфазного генератора 10 импульсов, вторые входы (т-{-1) -разрядного сумматора 12 подключены к выходу цифрового генератора 11 пилы, вход которого подключен к выходу блока 2 аналого-цифрового преобразования. Выходы m-1 разрядов сумматора 12 соединены с первыми входами инвертора 13 кода, вторые входы которого соединены с выходом т-го разряда сумматора 12. Выход (т+1)-го разряда сумматора 12 подключен к первым входам распределителя 9 импульсов, вторые входы которого соединены с соответствующей фазой трехфазового генератора 10 импульсов. Выходы инвертора 13 кода подключены к входам постоянно-программируемого запоминающего устройства 14. Формирователь 4 импульсов состоит из схемы 15 сравнения, трех оперативно-запоминающих устройств 16 и шести двухвходовых схем И 17. Первые входы схемы 15 сравнения подключены к выходам постоянно-программируемого запоминающего устройства 14, а вторые - к выходам генератора 8 пилы. Выход схемы 15 сравнения связан с первыми входами оперативно-запоминающих устройств 16, вторые входы которых связаны с соответствующими фазами трехфазного генера- тора 10 импульсов. Выходы оперативно- запоминающих устройств 16 связаны с соответствующими входами схемы И 17, вторые входы которых соединены с соответствующими выходами распределителя 9 импульсов. Выходы оперативно-запоминающих уст0 ройств 16 связаны с соответствующими входами схемы И 17, вторые входы которых соединены с соответствующими выходами распределителя 9 импульсов. Выходы схем И 17 образуют выходы формирователя импульсов, которые соединены с управляющими входами преобразователя 5 частоты, выходы которого соединены с входом электродвигателя 6 переменного тока. Датчик 7 измеряемого параметра входом соединен с выходом электродвигателя 6 переменного то0 ка, а выходом - с блоком 1 рассогласования, на другой вход которого приходит сигнал б з задания. Выход блока 1 рассогласования соединен с входом блока 2 аналого-цифрового преобразователя и первым входом преобразователя 18 напряжение-

5 частота генератора 8 пилы (фиг. 2). Второй вход преобразователя 18 напряжение-частота соединен с выходом генератора 19 импульсов, а выход - с первым входом (т-1)- разрядного счетчика 20, выходы которого являются выходами генератора 8 пилы, соединенными с выходами формирователя 21 запрета счета. Выход генератора 19 импульсов соединен с входом делителя 22 частоты, выход которого соединен с вторым входом счетчика 20, третий вход которого соединен с выходом формирователя 21 запрета счета.

Устройство работает следующим образом. Блок 1 рассогласования сравнивает сигнал задания (Уз) от внешнего задающего устройства и сигнал с выхода датчика 7 измеряемого параметра. Сигнал рассогласования t/y подается на вход блока 2 аналого- цифровго преобразования. На выходе последнего получается последовательность импульсов (фиг. 3), частота которых прямо пропорциональна амплитуде входного сигнала. Последовательность импульсов / (фиг. 3) приходит на вход цифрового генератора 11 пилы, представляющего собой двоичный ()-разрядный счетчик с самосбросом. С выхода цифрового генератора 11 пилы

0 идет (m-j-l)-разрядный параллельный двоичный код (фиг. 3). Пусть 2 - модуль пересчета двоичного счетчика генератора 11 пилы, тогда углу 2я соответствует число 2. Выход счетчика является однофазным, для преобразования его в трехфазный сиг5 нал служит сумматор 12. Можно доказать, что

0

5

0

5

т-1

2- S .

Т)ч

;i)

Раскрывают формулу (1) и преобразуют

ее

т-(

2 +2 2 +2-+2- +-+2 +2

П (2 +2- ) + (2 + 2-) +... ( +2 - -) +2 (1 +2) + +2 (1 +2) +...( 1 +2) + 2 + 3. ..+3-

+2 - +2 з| 2 - +2 - +2, (2)

где т - четное число.

Итак, углу 2л соответствует число 2, тогда углу 4л соответствует число 2- 2™. Используя формулу (2), получают

2-2 32Г

3 +32 - + 2 3 Y 22 - +2.

(3)

Используя формулу (3), находят число, соответствующее углу 4я/3,

i-j 2 - +2 +2

tn-t

22 - + vye

/ 1 2 ,о2е-1

N

М

Используя формулу (4), находят число, соответствующее углу 2я/3,

.Т2 .

Аналогично можно найти числа, соответствующие углам 2л, 2я/3, 4л/3 для т нечетных.

Пусть в момент времени на выходе двоичного счетчика генератора 11 пилы код имеет числовое значение, равное N. Ему соответствует угол синусоидального сигнала Л, пусть это будет углом синусоиды фазы А. Тогда фазе В соответствует угол (А +2л/3), что в цифровых градусах имеет вид

(), а фазе С - угол (А +4л/3), что в цифровых градусах имеет вид (

). t-i

В данном устройстве такое преобразование осуществляется следующим образом. Пусть число разрядов выхода цифрового генератора 11 пилы равно т+1, где т - четное число. Трехфазный генератор 10 импульсов выдает при последовательности импульсов А, В и Ci (фиг. 3). Так как код на выходе цифрового генератора 11 пилы соответствует углу синусоиды фазы Л, то в момент опроса фазы А первое слагаемое сумматора 12 должно равняться нулкз, иначе выходы трехфазного генератора 10 импульсов Bi и Ci должны подавать на вход сумматора 12 сигнал логического «О (фиг. 3). При опросе фазы В пер.вое слагаемое сумматора 12 должно равняться числу, соответствующему углу синусоиды, равному 2л/3, которое в цифровых градусах равно выражению (5). Это число в двоичном

коде содержит во всех четных разрядах «О, а в нечетных - «1. В устройстве в момент опроса фазы В выход В генератора 10 импульсов имеет значение логической «1, с которая подается на каждый первый вход нечетного разряда сумматора 12, а на первый вход четного разряда сумматора 12 подается сигнал Ci выхода трехфазного генератора 12 импульсов, имеющий значение логического «О (фиг. 3). В момент опроса

0 фазы С, как видно из выражения (4), первое слагаемое сумматора 12 должно содержать в нечетных разрядах «О, а в четных - «1.

На фиг. 4 показана синусоидальная вая (sina). Если записать в постоянно- программируемом запоминающем устройстве 14 значения синусоиды в промежутке от О до л/2, то можно формировать синусоидальный сигнал исходя из следующих соображений. В промежутке от О до л/2 или в

20 соответствующем ему цифровом промежутке от О до при возрастании кода на входе постоянно-программируемого запоминающего устройства 14 на его выходе имеется код восходящей ветви синусоиды. Если в промежутке от л/2 до л или соответствующем ему в цифровом промежутке от до сделать код на входе постоянно-программируемого запоминающего устройства 14 убывающим, то на его выходе будет код синусоиды падающей

30 ветви. Это равнозначно тому, что входной код проинвертирован. В промежутке от л до Зл/2, что соответствует цифровому промежутку от до (), начинается восходящая ветвь отрицательной полуволны синусоиды. При подаче на вход

25 постоянно-программируемого запоминающего устройства 14 прямого кода на его выходе имеют код восходящей ветви синусоиды, а в промежутке от Зл/2 до 2л, соответствующем цифровому промежутку от ( + +2) до 2, при подаче на вход постоян40 но-программируемого запоминающего устройства 14 инвертированного кода с его выхода имеют код падающей ветвн синусоиды, причем в промежутке от л до 2л, в цифровом значении от до , код синусоиды выпрямлен, т. е. знак пока не учиты вают (фиг. 4, sinaug).

Функцию управляемого инвертора выполняет инвертор 13 кода, состоящий из т.- 1 логических элементов и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. На первые входы инверто ра 13 п кода подаются сигналы с т-1 младщих разрядов выхода сумматора 12, а на вторые входы подается сигнал с выхода разряда сумматора 12. Как видно из фиг. 4 ( а«2 и 51па„2, где аГ - выход т-го разряда сумматора 12; а„2 - код на выходе

55 инвертора 13 кода), при значениях разряда выхода сумматора 12, равных логическому «О, код угла синусоиды инвертировать не надо, а при значениях логической «1 код нужно проинвертировать.

Знак синусоиды определяется (т-|-1)-м разрядом выхода сумматора 12 (фиг. 4, аГ и sina). При его значении «О знак синусоиды положительный, а при значении «1 - отрицательный. Работа устройства рассмотрена без учета разделения по времени, однако на выходе постоянно-программируемого запоминающего устройства 14 образуется трехфазная совокупность кодов выпрямленного синусоидального сигнала с разделением по времени в соответствии с управляющими импульсами трехфазного генератора 10 импульсов. Для получения знаков синусоиды каждой фазы служит распределитель 9 импульсов, представляющий собой три ячейки оперативно-запоминающего

ток от и до t/2, угол наклона линейно уменьщается до определенного минимального значения и при остается постоянным, причем между моментом достижения цифровой пилой максимума и прихо дом следующего тактового импульса fTaKT имеется определенный промежуток времени т, необходимый для разделения импульсов при минимальном угле наклона цифровой пилы. Эти ограничения необходимы для обес10 печения устойчивой и надежной работы силовых транзисторных ключей, имеющих задержки во включении и выключении. Таким образом, (т-1)-разрядный код синусоиды с выхода постоянно-программируемого запоминающего устройства 14 и

устройства, на информационный вход каж- 15 (т-1)-разрядный код амплитуды с выхода

дои ячейки поступает сигнал с (т+1)-го разряда выхода сумматора 12, а на управляющие входы подаются сигналы А, Bi и Ct (фиг. 3).

счетчика 20 поступают на входы схемы 15 сравнения, представляющую собой (т-1)- разрядную схему сравнения двух двоичных чисел. Выход схемы 15 сравнения имеет

Генератор 8 пилы работает следующим 20 значение логической «1, если числовое знаобразом. Сигнал с выхода блока 1 рассогласования поступает на вход преобразователя 18 напряжение-частота, на выходе которого имеют последовательность импульсов, синхронизированных с импульсами с выхочение кода гармонического сигнала больше числового значения кода амплитуды, и логического «О, если числовое значение кода гармонического сигнала меньше значений кода амплитуды. На фиг. 6 (sinaua i, В

да генератора 19 импульсов. Работа блока 225 и Ci) показ ан код синусоид фаз А, В С,

аналого-цифрового преобразования и трех-разделенный по времени в соответствии с

фазного генератора 10 импульсов также син-импульсами А. В и Ci трехфазного генехронизирована с работой генератора 19 им-ратора 10 импульсов. Ли - числовое знапульсов. Частота выходных импульсов пре-чение цифровой пилы, изменяющееся во вреобразователя 18 напряжение-частота изме-мени, Q - выход схемы 15 сравнения. Для

няется в зависимости от амплитуды управ-30 разделения по трем каналам выходных имляющего сигнала Uy и имеет вид, показанный на фиг. 5. На счетный вход счетчика 20 поступают импульсы с выхода преобразователя 18 напряжение-частота. Выход счетчика 20 представляет собой (т-1)-разпульсов схемы 15 сравнения служит оперативно-запоминающее устройство 16, состоящее из трех ячеек, на информационные входы которых подается сигнал с выхода схемы 15 сравнения, а на управляющие

рядный параллельный двоичный код. Выход 35 входы - импульсы опроса Л|, Bi и Ci с вы- каждого разряда поступает на вход форми- хода трехфазного генератора 10 импульсов рователя 21 запрета счета, представляю- (фиг. щего собой (т-1)-входной логический элемент И-НЕ. При переполнении регистра счетчика 20 с выхода формирователя 21 дО запрета счета на вход запрета счетчика 20 поступает сигнал логического «О и счет останавливается. При приходе на вход обнуления счетчика 20 тактового импульса /такт с выхода делителя 22 происходит обнуление

6). Импульсы на выходе оперативно-запоминающего устройства 16 4, 64 и С4 (фиг. 6) имеют частоту, равную частоте тактовых импульсов с выхода делителя 22 частоты. Ширина импульсов пропорциональна коду синусоидального сигнала и обратно пропорциональна углу наклона цифровой пилы. Для разделения по полуволнам синусоид всех трех фаз испольвсех разрядов счетчика 20, формирова- 45 зуется коммутатор полупериодов, состоящий

тель 21 запрета подает на вход запрета счетчика 20 сигнал логической «1 и счет возобновляется. Таким образом, на выходе счетчика 20 имеют код, числовое значение Ли которого меняется во времени (фиг. 5) -

из шести логических двухвходовых схем И 17, первая пара которых разделяет по полуволнам управляющий сигнал в виде импульсов АИ фазы А в соответствии с управляющими сигналами Лз и Лз с выхода первой

цифровая пила, угол наклона которой ме- 50 ячейки оперативно-запоминающего устрой- няется в зависимости от частоты импульсов на выходе преобразователя 18 напряжение - частота. При значениях амплитуды управляющего сигнала Uy на входе преобразователя 18 напряжение-частота, попадающих в промежуток от О до U, цифровая пила имеет постоянный самый большой угол наклона, а при значениях управляющего сигнала, попадающих в промежуства 16. Аналогично разделяются по полуволнам управляющие сигналы 64 и С фаз в и С (фиг. 7, Лз, Вз, Сз, Ло, Лб, В-„, Se, Cs, Се, где Лб, Вб и Сб - импульсы управления силовыми ключами положительной полувол- 55 ны фаз Л, В и С; Лб, BS и Со - импульсы управления силовыми ключами отрицательной полуволны фаз Л, В, С, причем на диаграмме з1по1„ для наглядности не

ток от и до t/2, угол наклона линейно уменьщается до определенного минимального значения и при остается постоянным, причем между моментом достижения цифровой пилой максимума и приходом следующего тактового импульса fTaKT имеется определенный промежуток времени т, необходимый для разделения импульсов при минимальном угле наклона цифровой пилы. Эти ограничения необходимы для обеспечения устойчивой и надежной работы силовых транзисторных ключей, имеющих задержки во включении и выключении. Таким образом, (т-1)-разрядный код синусоиды с выхода постоянно-программируемого запоминающего устройства 14 и

(т-1)-разрядный код амплитуды с выхода

(т-1)-разрядный код амплитуды с выхода

счетчика 20 поступают на входы схемы 15 сравнения, представляющую собой (т-1)- разрядную схему сравнения двух двоичных чисел. Выход схемы 15 сравнения имеет

значение логической «1, если числовое зназначение логической «1, если числовое значение кода гармонического сигнала больше числового значения кода амплитуды, и логического «О, если числовое значение кода гармонического сигнала меньше значений кода амплитуды. На фиг. 6 (sinaua i, В

разделения по трем каналам выходных импульсов схемы 15 сравнения служит оперативно-запоминающее устройство 16, состоящее из трех ячеек, на информационные входы которых подается сигнал с выхода схемы 15 сравнения, а на управляющие

входы - импульсы опроса Л|, Bi и Ci с вы- хода трехфазного генератора 10 импульсов (фиг.

входы - импульсы опроса Л|, Bi и Ci с вы- хода трехфазного генератора 10 импульсов (фиг.

6). Импульсы на выходе оперативно-запоминающего устройства 16 4, 64 и С4 (фиг. 6) имеют частоту, равную частоте тактовых импульсов с выхода делителя 22 частоты. Ширина импульсов пропорциональна коду синусоидального сигнала и обратно пропорциональна углу наклона цифровой пилы. Для разделения по полуволнам синусоид всех трех фаз используется коммутатор полупериодов, состоящий

из шести логических двухвходовых схем И 17, первая пара которых разделяет по полуволнам управляющий сигнал в виде импульсов АИ фазы А в соответствии с управляющими сигналами Лз и Лз с выхода первой

50 ячейки оперативно-запоминающего устрой-

ства 16. Аналогично разделяются по полуволнам управляющие сигналы 64 и С фаз в и С (фиг. 7, Лз, Вз, Сз, Ло, Лб, В-„, Se, Cs, Се, где Лб, Вб и Сб - импульсы управления силовыми ключами положительной полувол- 55 ны фаз Л, В и С; Лб, BS и Со - импульсы управления силовыми ключами отрицательной полуволны фаз Л, В, С, причем на диаграмме з1по1„ для наглядности не

указано разделение по времени, а показан вид огибающих синусоид фаз Л, В и С). Сигналы AS, Аб, Bs, Be, Cf и Се управляют силовыми ключами, которые подают импульсы высокого напряжения к статорным обмот- кам электродвигателя переменного тока.

Изобретение позволяет упростить схему устройства, так как в три раза уменьшается количество блоков формирования гармонических сигналов, в которых исклю- чается преобразователь код-аналог, и уменьшается объем постоянно-программируемого запоминающего устройства (наиболее дорогостоящие блоки). Так как формирование амплитуды и частоты управляющего сигнала производится в цифровом виде и на одних и тех же элементах, гарантируется равная величина частот и амплитуд выходных фаз преобразователя частоты, увеличивается помехоустойчивость, уменьшается зависимость работы устройства от темпера- туры и колебаний питающего напряжения. Этим повышается точность работы устройства для управления электродвигателем переменного тока. Цифровое преобразование управляющих сигналов, применяемое в схеме устройства для управления электродвигате- лем переменного тока, позволяет применить большую интеграцию элементов и всю схему разместить в одной большой интегральной схеме, что приводит к удешевлению и удобству в эксплуатации устройства для управления электродвигателем переменного тока.

Формула изобретения

Устройство для управления электродвигателем переменного тока, содержащее управляемый преобразователь частоты, предназначенный для подключения к электродвигателю переменного тока, формирователь импульсов, выходы которого подключены к управляющим входам преобразователя частоты, а входы - к генератору пилы, распределитель импульсов и формирователь гармонических сигналов, блок аналого-цифрового преобразования, вход которого соеди

5

0 0 5

О

0

5

нен с выходом блока рассогласования, а выход - с входом формирователя гармонических сигналов, входы блока рассогласования соединены с задатчиком и датчиком измеряемого параметра электродвигателя, отличающееся тем, что, с целью упрощения путем исключения аналоговых преобразователей и обеспечения возможности пара ллель- ного преобразования информации и повышения точности, введен трехфазный генератор импульсов, формирователь гармонических сигналов составлен из цифрового генератора пилы, (т+1)-разрядного сумматора, инвертора кода, формирователя кода синусоидальных сигналов, формирователь импульсов составлен из схемы сравнения, оперативно-запоминающего узла, шести двухвхо- довых схем И, причем первые входы четных разрядов указанного сумматора соединены с третьей, а нечетных разрядов - с второй фазой трехфазного генератора импульсов, вторые входы разрядов сумматора связаны с выходами цифрового генератора пилы, входы m-1 разрядов сумматора подключены к первым входам инвертора кода, вторые входы которого соединены с т-м разрядом суматора, выходом (т+1)-го разряда связанного с первым входом распределителя импульсов, вторые входы которого соединены с соответствующей фазой трехфазного генератора импульсов, выходы инвертора кода подключены к входам формирователя кода синусоидальных сигналов, выходами связанного с одними входами схемы сравнения, другие входы которого подключены к выходам генератора пилы, входом связанного с выходом блока рассогласования, выход схемы сравнения подключен к первым входам оперативно-запоминающего узла, вторые входы которого связаны с соответствующими фазами трехфазного генератора импульсов, выходы оперативно-запоминающего узла связаны с соответствующими первыми входами схем И, вторые входы которых соединены с выходами распределителя импульсов соответственно, а выходы схем И образуют выходы формирователя импульсов.

(rrj-H) oCa.cQ.

Ci

n ГП n

X

fm+1)

..CM.

/1

A

/1

XI

X

/

/

V

V

V

V

/

V

фаг. 5

/1

/

/1

/1

A

/

/

/

V

V

V

I/

/

1У

since

27fci

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления электродвигателем переменного тока | 1984 |

|

SU1457141A1 |

| Программируемый многоканальный цифровой синтезатор частот | 1988 |

|

SU1608777A1 |

| Прибор для измерения частотных характеристик | 1986 |

|

SU1335935A1 |

| Формирователь сигналов | 1988 |

|

SU1598198A2 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2020724C1 |

| Способ измерения скорости вращения вала и устройство для его осуществления | 1978 |

|

SU864131A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Одноканальное цифровое устройство для управления @ -фазным @ -пульсным вентильным преобразователем | 1990 |

|

SU1757057A1 |

| Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой | 1987 |

|

SU1497722A1 |

Изобретение относится к электротехнике. Целью изобретения является упрощение за счет исключения аналоговых преобразователей и обеспечения возможности параллельного преобразования информа ъ ции и повышение точности. Указанная цель достигается введением в устройство управления электродвигателем переменного тока трехфазного генератора 10 импульсов и выполнением формирователя 3 гармонического сигнала в виде соединенных между собой цифрового генератора 11 пилы, (т+1)-разрядного сумматора 12, инвертора кода 13, формирователя 14 кода синусоидальных сигналов. Формирователь импульсов составлен из соединенных между собой схемы сравнения 15, оперативно-запоминающих устройств 16 и двухвходовых схем И 17. В результате уменьщается количество блоков, объем постоянно-программируемого запоминающего устройства, гарантируется равная величина частот и амплитуд выходных фазных напряжений преобразователя частоты 5, увеличивается помехоустойчивость. Уменьшается зависимость работы устройства от температуры и колебаний питающего напряжения. 7 ил. S (Л 00 оо 05 00 оо

fMOHC

fMUH

fmoKm

N И fl И П n П n П e

Yтr гY f fvvwvw.

Uz

фиг. 5

П П iriiriipiiP i i

П П П П

, J

SinaC

Аи,

Вз С}

ii|) I HH i i il li

г-iiP I I

fi

-4

m

I I

M-iT

4

LL

i III

rl

±

hi

iM H

Фаг.7

t

I I

I I

-iT

4

LL

±

hi

I I

| Обухов С | |||

| Г., Рагулин А | |||

| М | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления электро-дВигАТЕлЕМ пЕРЕМЕННОгО TOKA | 1978 |

|

SU813653A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-09-07—Публикация

1983-09-01—Подача