Изобретение относится к импульсной технике и может быть использовано в системах программного управления, устройствах функционального контроля интегральных схем, устройствах функционального контроля запоминающих устройств.

Целью изобретения является повышение надежности устройства за счет его упрощения.

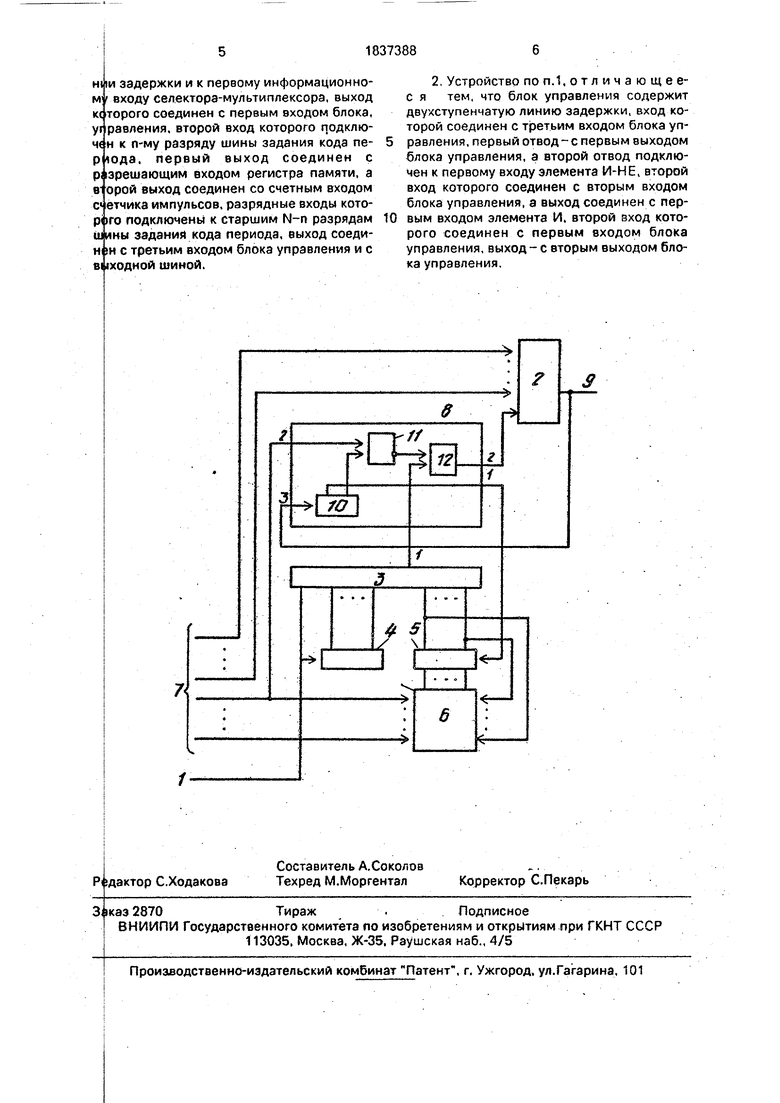

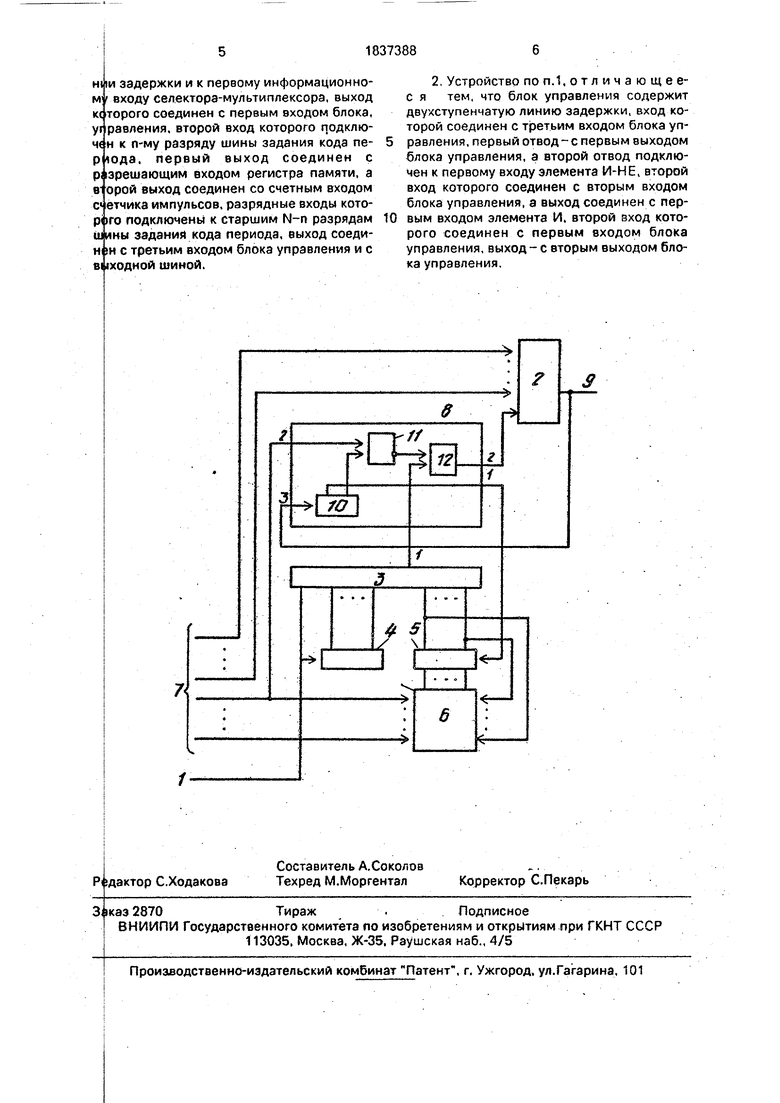

На чертеже представлена электрическая функциональная схема устройства.

Устройство содержит шину 1 импульсов образцовой частоты, счетчик 2 импульсов, селектор-мультиплексор 3, к-1 информационных входов которого подключены к отводам ступенчатой линии 4 задержки, адресные входы соединены с выходами разрядов регистра 5 памяти и с первыми входами сумматора 6, вторые входы которого подключены к n-младшим разрядам шины 7 задания кода периода, а выходы соединен с входами разрядов регистра 5 памяти, шина 1 импульсов образцовой частоты подключена к входу ступенчатой линии 4 задержки и к первому информационному входу селектора-мультиплексора 3,выход которого соединен с первым входом блока 8 управления, второй вход которого подключен к n-му разряду шины 7 задания кода периода, первый выход соединен с разрешающим входом счетчика 2 импульсов, работающего в режиме делителя с переменным коэффициентом деления частоты, разрядные входы которого подключены к старшим N-n разрядам шины 7 задания кода периода, выход соединен с третьим входом блока 8 управления и с выходной шиной 9. Блок 8 управления содержит двухступенчатую линию 10 задержки, вход которой соединен с третьим входом блока 8 управления, первый отвод соединен с первым выходом блока 8 управления, а второй отвод подключен к первому входу элемента И-НЕ 11, второй вход которого соединен с вторым входом блока 8 управления, а выход соединен с первым входом элемента И 12, второй вход которого соединен с первым входом блока 8 управления, выход - с вторым выходом блока 8 управления.

00 GJ J СО 00 00

Устройство работает следующим образом.

На вход линии 4 и на первый информационный вход селектора-мультиплексора 3 с шины 1 поступает последовательность импульсов образцовой частоты F0. На линии 4 осуществляется последовательный сдвиг на величину То/К. На выход селектора-мультиплексора 3 в каждом периоде подключается серия, сдвинутая на величину т0 Т0/К относительно серии, действовашей на его выходе в предыдущем периоде. Порядок переключения серий определяется частью устройства в составе регистра 5 и сумматора 6, данная часть устройства формирует код номера по закону

гон-1 mt + m0,

где mi-н - номер серии, подключаемой на выход селектора-мультиплексора 3 в периоде:

mf - номер серии, подключаемой на выход селектора-мультиплексора 3 в периоде;

то - значение младших разрядов кода периода.

С выхода селектора-мультиплексора 3 выбранная серия поступает на счетный вход счетчика 2, при этом коэффициент деления определяется старшими М-n разрядами ко- да периода из шины 7 и соответствует коэффициенту М0. Импульс с выхода счетчика 2 через блок 8 управления поступает на разрешающий вход регистра 5, осуществляя перезапись кода, что в конечном итоге приводит к формированию на выходе счетчика 2 следующего импульса, сдвинутого относительно предыдущего на величину Т, при этом дополнительный сдвиг обусловлен действием на входе счетчика 2 в смежных периодах разных серий.

Блок 8 управления выполняет в устройстве функции вспомогательного характера. Ниже представлен вариант, предназначенный для подавления на выходе селектора- мультиплексора 3 импульсов, длительность которых менее Гимн. Область применения данного варианта определяется условиями:

То -То .

-- г Ј., Тимп -rr tn адмпN

где То - период следования импульсов образцовой частоты;

tnnn -длительность импульса в последовательности Fol

К - коэффициент из формулы:

tn - длительность импульса переполнения счетчика 11 импульсов.

Устройство работает следующим образом.

Импульс переполнения счетчика 2, поданный на третий вход блока 8 и задержанный на линии 10, с первого ее отвода поступает на разрешающий вход регистра

0

5

0

5

0

5

0

5

0

5

5. Задержка от начала до первого отвода линии 10 подбирается таким образом, чтобы выполнялось условие

ti То,

где tt - задержка на выходе селектора-мультиплексора 3 момента переключения относительнофронтаимпульса, предшествующего моменту переключения.

Приведенные выше математические выражения (в совокупности) позволяют однозначно установить связь появления усеченного по длительности импульсе на выходе селектора-мультиплексора 3 со чением n-го разряда кода задания период, и использовать этот разряд для управления блокировкой путем подключения его к второму входу блока 8 или к второму вхоДу элемента 11. на первый вход которого с втб рого отвода линии 10 поступает блокирую щий импульс. При значении п-го разряда равном 1, разрешается прохождение бло- кирущего импульса на второй вход элементе 12, где и осуществляется блокировка усеченного импульса. Задержка от начала до второго отвода линии 10 подбирается с учетом совмещения во времени (на входах элемента 12} фронта блокирующего импульса и момента переключений серий.

В случае использования устройства в области, определяемой условием

,

tnsin

достаточно проинвертировать входную последовательность FO, что приводит данный случай к рассмотренному ранее. Вариант блока 8 в этом случае будет иметь в составе {дополнительно к описанному выше варианту) элемент НЕ.

Таким образом, период следования выходных импульсов устройства будет

Т М0 То + то То/К.

Формула изобретения

1. Устройство для управления периодом следования импульсов, содержащее шину импульсов образцовой частоты, счетчик импульсов, селектор-мультиплексор, к--1 информационных входов которого подключены к отводам ступенчатой линии задержки, адресные входы соединены с выходами разрядов регистра памяти и с пер выми входами сумматора, вторые входы которого подключены к n-младшим разрядам шины задания кода периода, а выходы соединены с входами разрядов регистра памяти, отличающееся тем, что, с целью повышения надежности устройства путем его упрощения, в него введен блок управления, причем шина импульсов образцовой частоты подключена к входу ступенчатой лим w

У ч«н

нфи задержки и к первому информационно- входу селектора-мультиплексора, выход которого соединен с первым входом блока, равления, второй вход которого подклю- к n-му разряду шины задания кода периода, первый выход соединен с разрешающим входом регистра памяти, а 81 орой выход соединен со счетным входом с етчика импульсов, разрядные входы кото- pi iro подключены к старшим N-n разрядам шины задания кода периода, выход соединен с третьим входом блока управления и с выходной шиной.

2, Устройство поп.1,отличающее- с я тем, что блок управления содержит двухступенчатую линию задержки, вход которой соединен с третьим входом блока управления, первый отвод - с первым выходом блока управления, а второй отвод подключен к первому входу элемента И-НЕ, второй вход которого соединен с вторым входом блока управления, а выход соединен с первым входом элемента И. второй вход которого соединен с первым входом блока управления, выход-с вторым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления периодом следования импульсов | 1981 |

|

SU1003315A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| Рециркуляционный преобразователь кода во временной интервал | 1987 |

|

SU1474847A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Каскадный рециркуляционный преобразователь код - время | 1989 |

|

SU1709529A1 |

| ПЛКЙТНО-ИХШЕСЙА*ЬИБ;1ИО'^ЕКАГ. Л. Биланов | 1972 |

|

SU342297A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1431038A1 |

Использование: устройство для управления периодом следования импульсов может использоваться в системах программного управления, в устройствах функционального контроля интегральных схем и запоминающих устройств. Сущность изобретения: устройство содержит счетчик импульсов, селектор-мультиплексор, ступенчатую линию задержки, регистр памяти, сумматор, блок управления, шины образцовой частоты, кода период и выходную. 1 з.п. ф-лы, 1 ил/

Авторы

Даты

1993-08-30—Публикация

1989-07-13—Подача