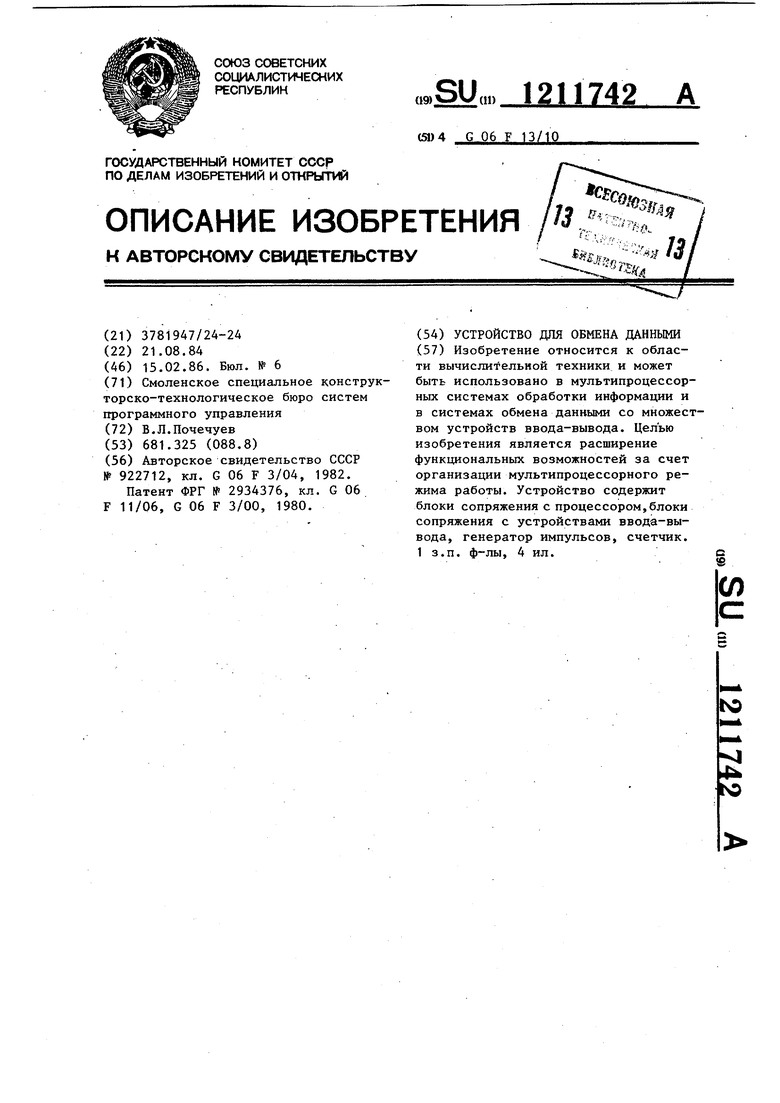

Изобретение относится к вычислительной технике и может быть использовано в мультипроцессорных системах обработки информации и в системах обмена данными со множеством устройств ввода-вывода.

Целью изобретения является расширение функциональных возможностей за счет организации мультипроцессорного режима работы.

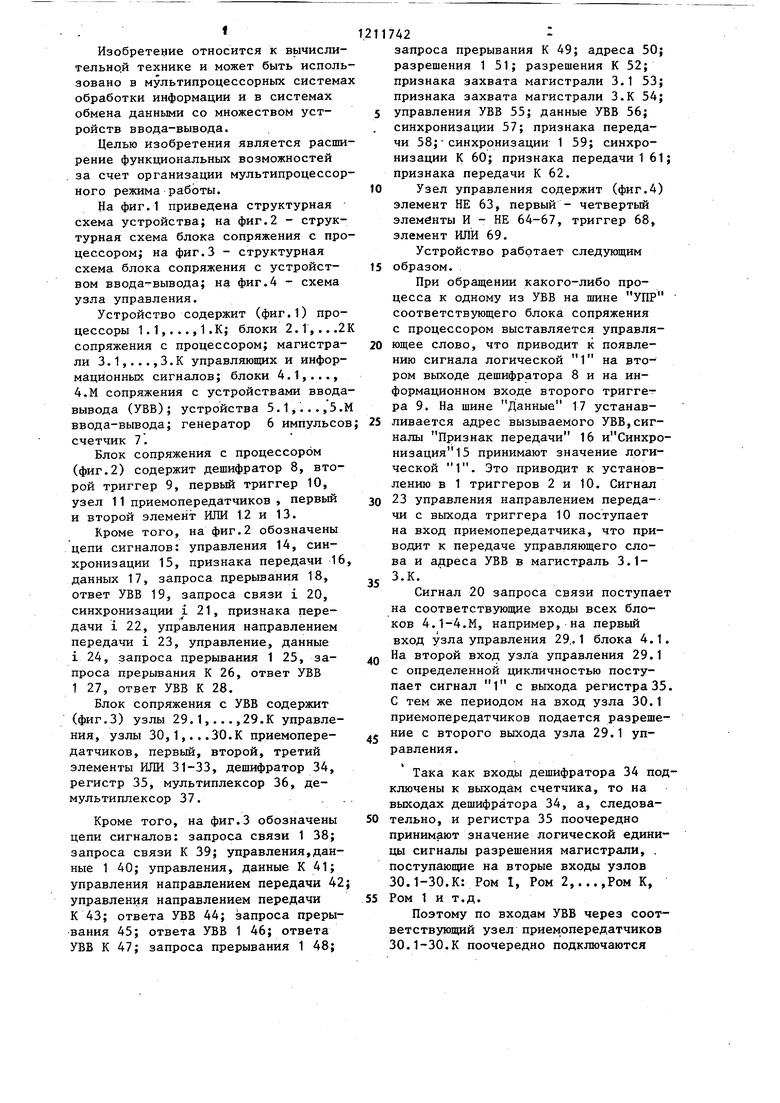

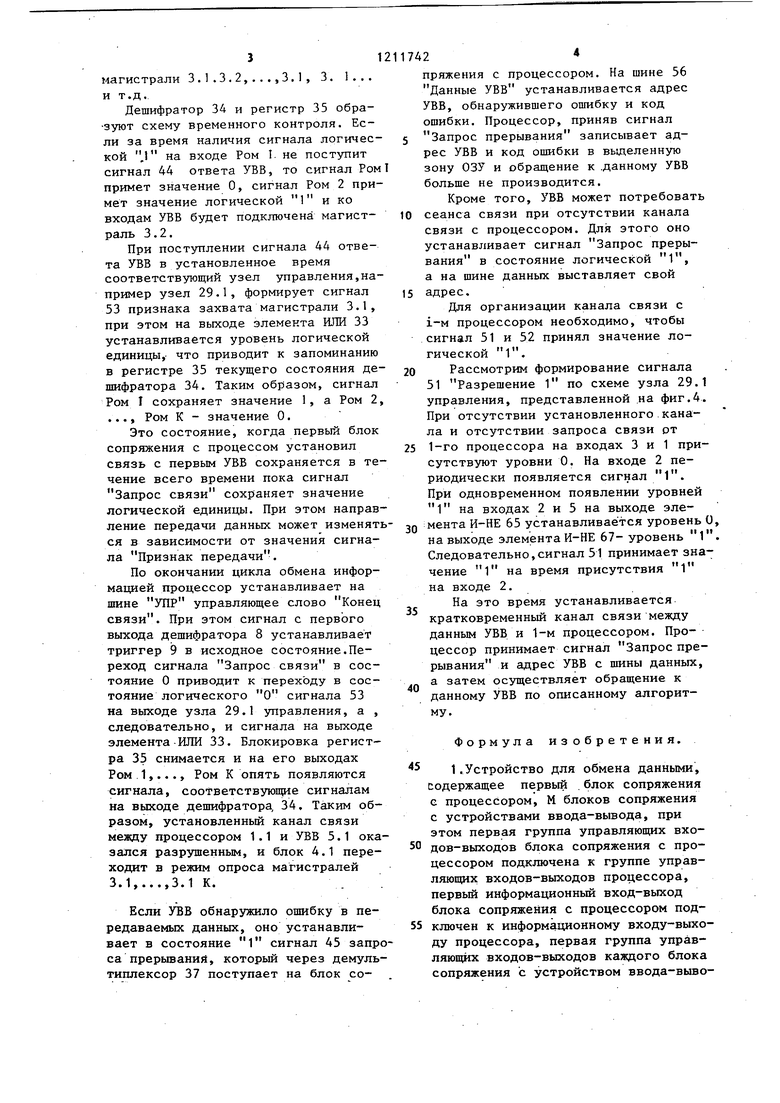

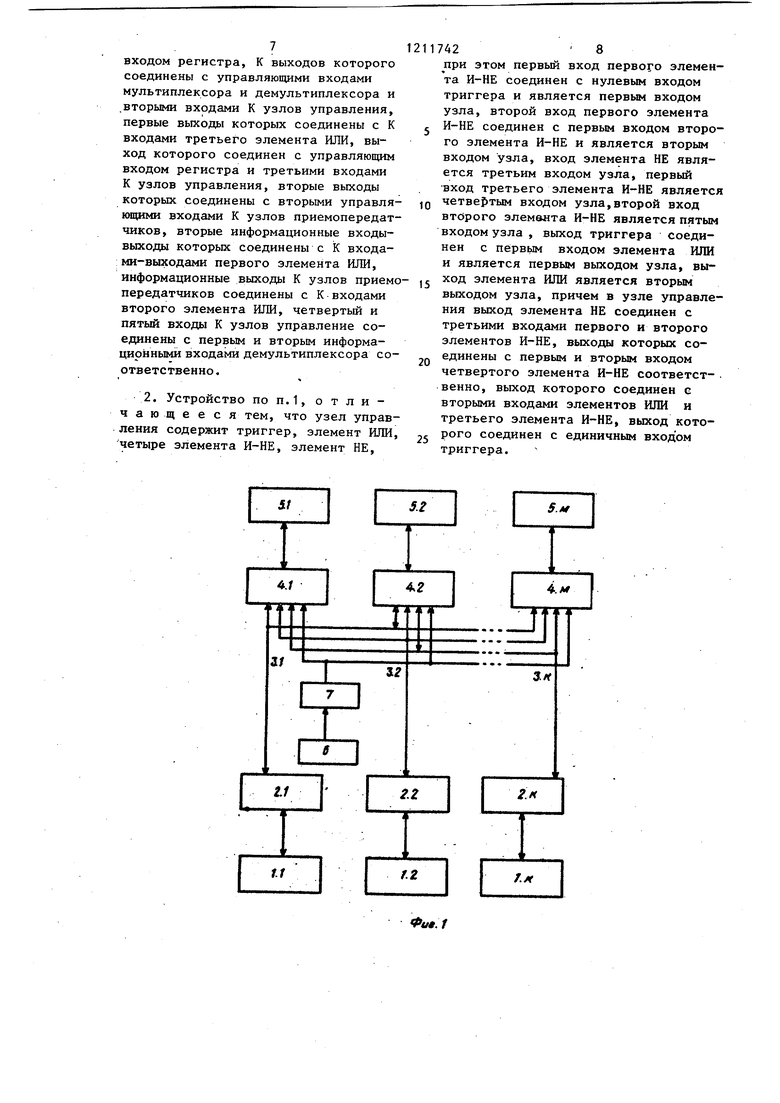

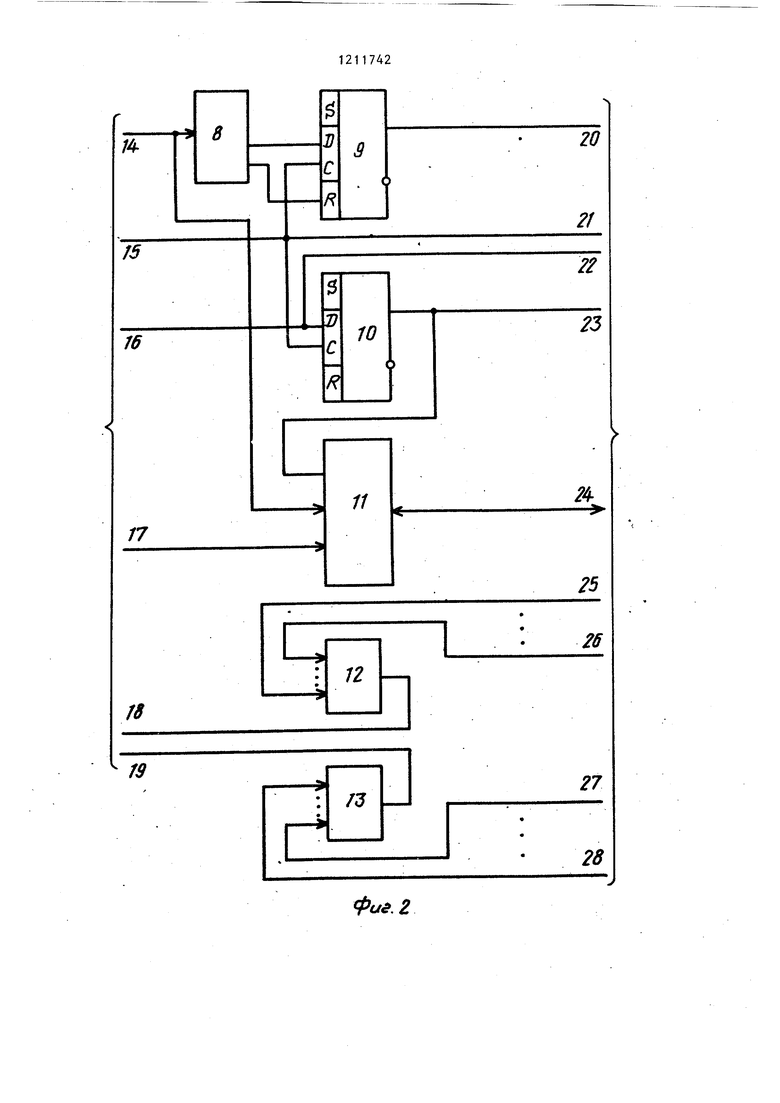

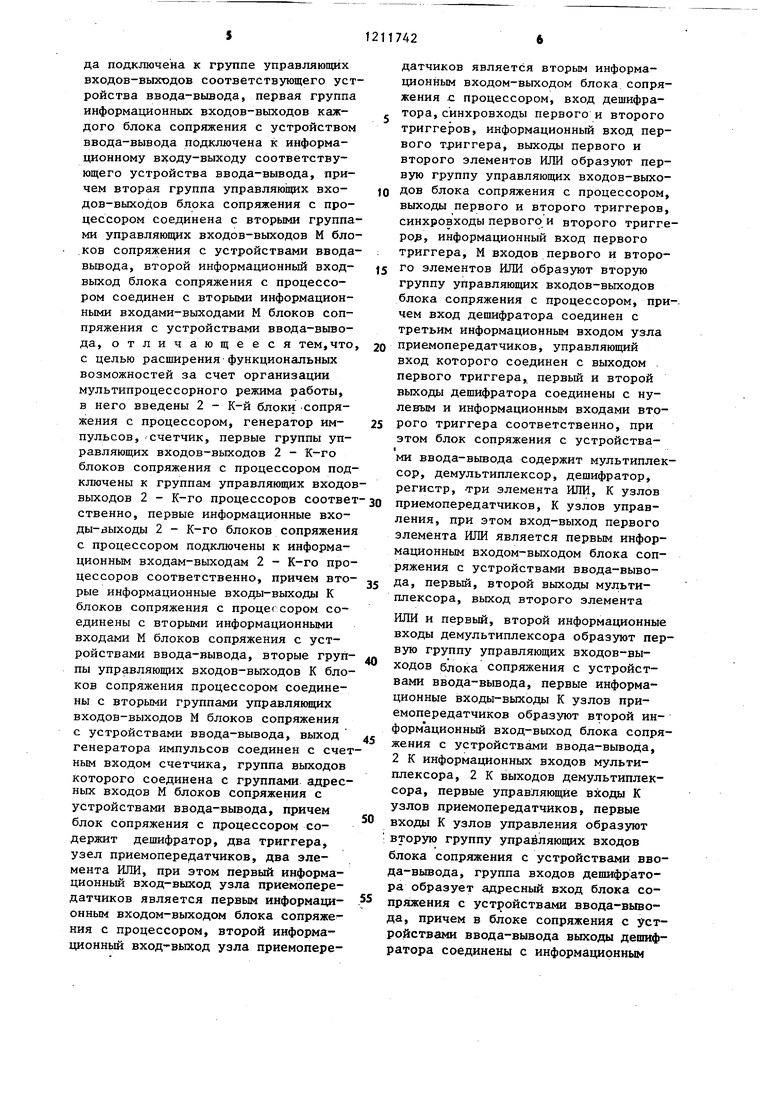

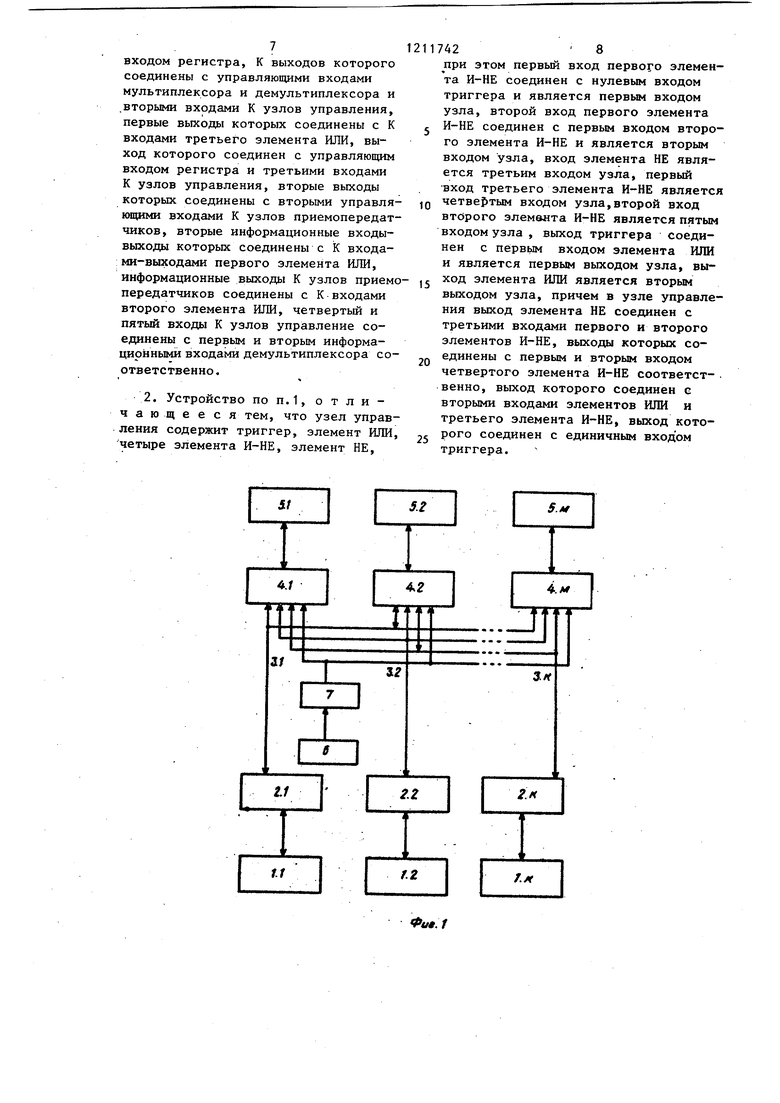

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока сопряжения с процессором; на фиг.З - структурная схема блока сопряжения с устройством ввода- вывода; на фиг.4 - схема узла управления.

Устройство содержит (фиг.1) процессоры 1.11.К; блоки 2.1,...2К

сопряжения с процессором; магистрали 3.1,...,3.К управляющих и информационных сигналов; блоки 4.1,..., 4.М сопряжения с устройствами ввода- вывода (УВВ); устройства 5.1,.. .,5 .М ввода-вывода; генератор 6 импульсов счетчик 7.

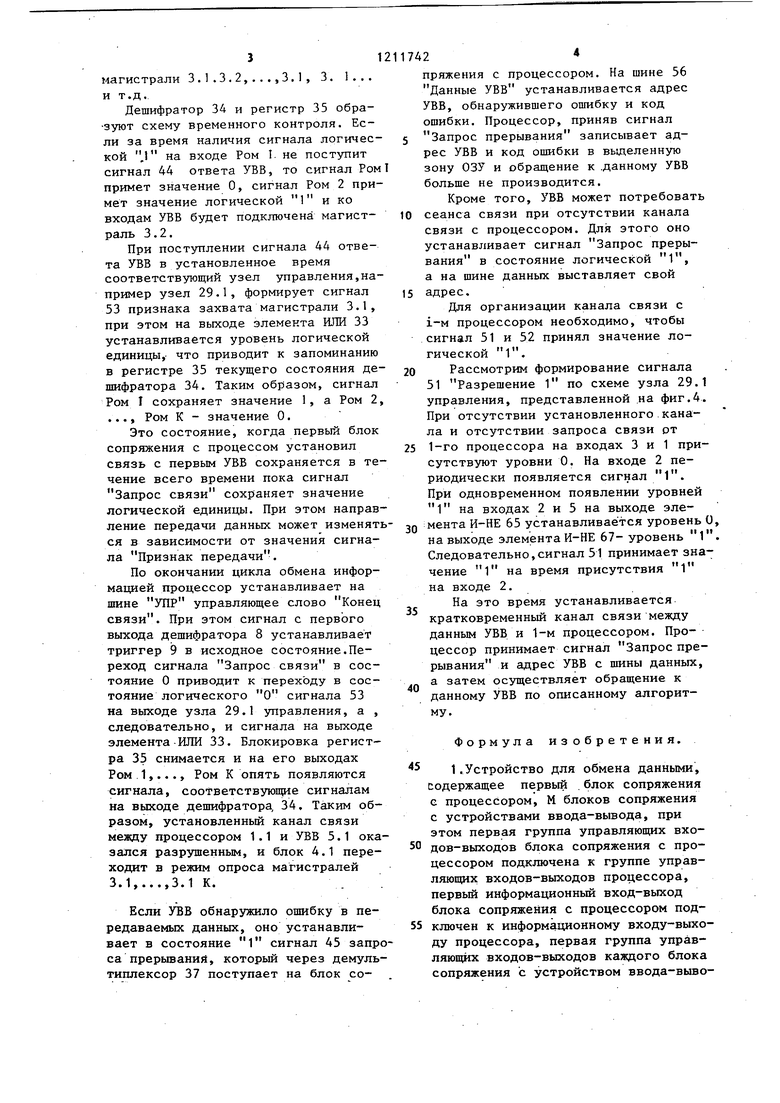

Блок сопряжения с процессором (фиг.2) содержит дешифратор 8, второй триггер 9, первый триггер 10, узел 11 приемопередатчиков , первый и второй элемент ИЛИ 12 и 13.

Кроме того, на фиг.2 обозначены цепи сигналов: управления 14, синхронизации 15, признака передачи 16, данных 17, запроса прерывания 18, ответ УВВ 19, запроса связи i 20, синхронизации i 21, признака передачи i 22, управления направлением передачи i 23, управление, данные i 24, запроса прерывания 1 25, запроса прерывания К 26, ответ УВВ 1 27, ответ УВВ К 28.

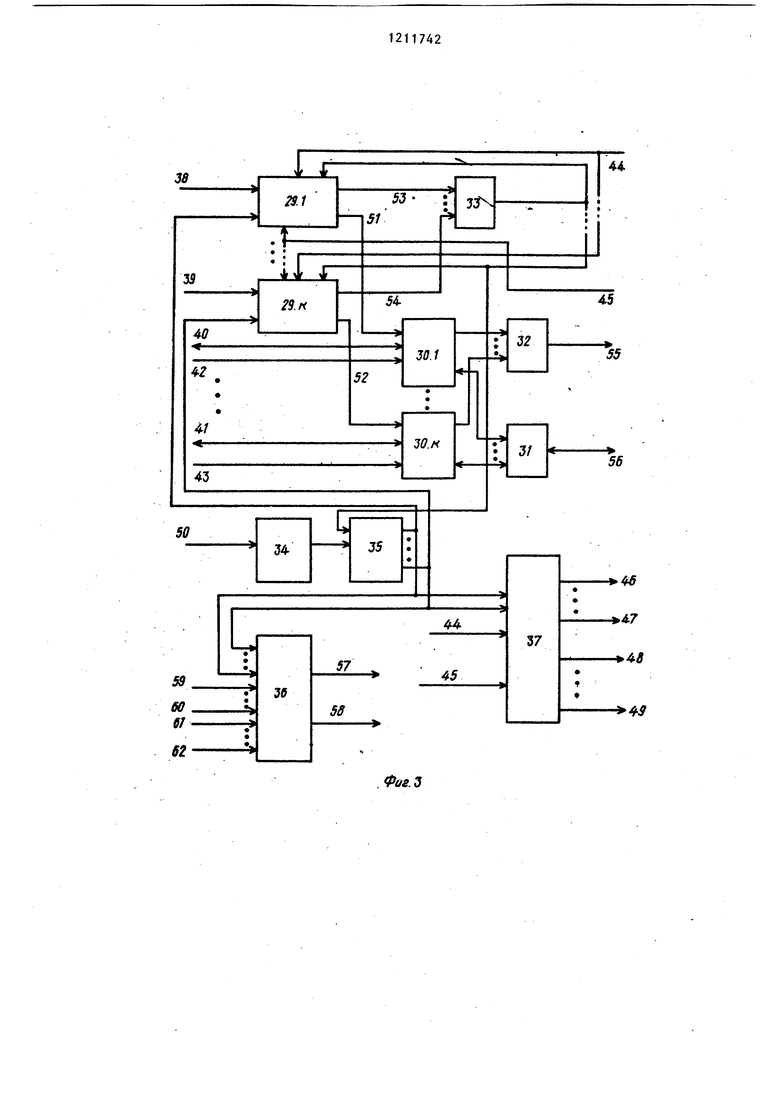

Блок сопряжения с УВВ содержит (фиг.З) узлы 29.1,... ,29.К управления, узлы 30,1,...ЗО.К приемопередатчиков, первый, второй, третий элементы ИЛИ 31-33, дешифратор 34, регистр 35, мультиплексор 36, де- мультиплексор 37...

Кроме того, на фиг.З обозначены цепи сигналов: запроса связи 1 38; запроса связи К 39; управления,данные 1 40; управления, данные К 41; управления направлением передачи 42; управления направлением передачи К 43; ответа УВВ 44; запроса прерывания 45; ответа УВВ 1 46; ответа УВВ К 47; запроса прерывания 1 48;

1211742

запроса прерывания К 49; адреса 50; разрешения 1 51; разрешения К 52; признака захвата магистрали 3.1 53; признака захвата магистрали З.К 54;

управления УБВ 55; данные УВВ 56; синхронизации 57; признака передачи 58;-синхронизации 1 59; синхронизации К 60; признака передачи 1 61; признака передачи К 62.

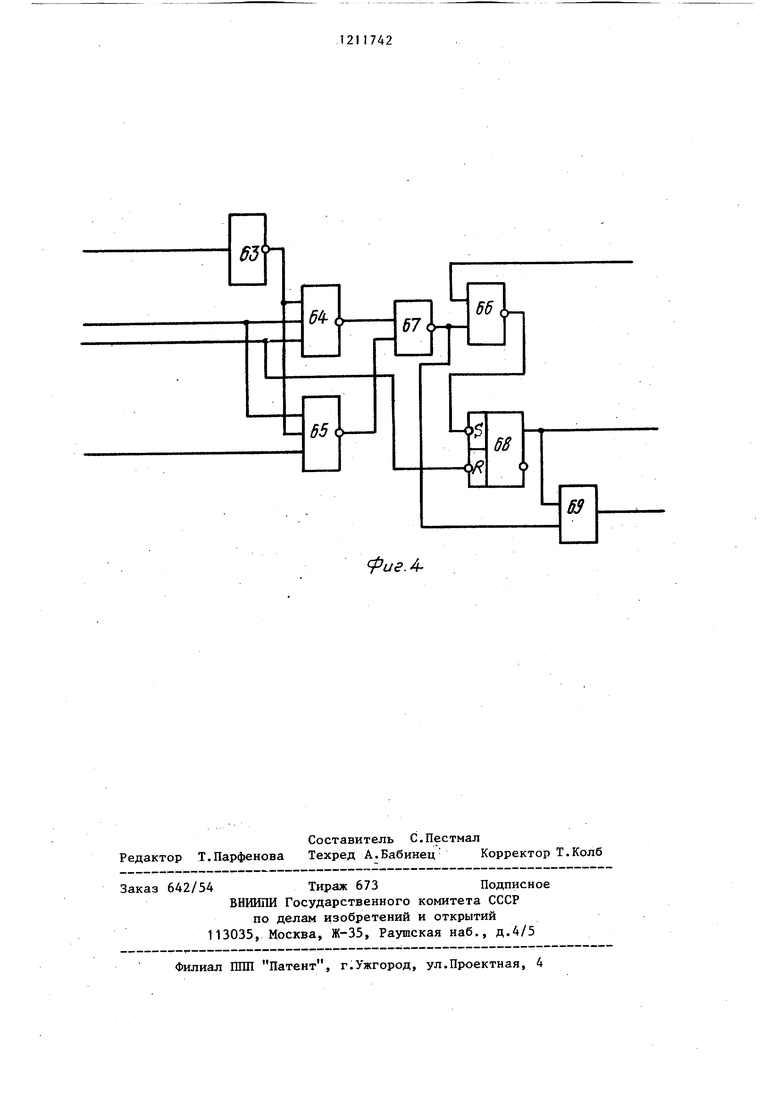

Узел управления содержит (фиг.4) элемент НЕ 63, первый - четвертый элементы И - НЕ 64-67, триггер 68, элемент ИЛИ 69.

Устройство работает следующим

образом.

При обращении какого-либо процесса к одному из УВВ на шине УПР соответствующего блока сопряжения с процессором выставляется управляющее слово, что приводит к появлению сигнала логической 1 на втором выходе дешифратора 8 и на информационном входе второго триггера 9. На шине Данные 17 устанавливается адрес вызываемого УВВ,сигналы Признак передачи 16 и Синхро- низация 15 принимают значение логической 1. Это приводит к установлению в 1 триггеров 2 и 10. Сигнал

23 управления направлением переда-- чи с выхода триггера 10 поступает на вход приемопередатчика, что приводит к передаче управляющего слова и aftpeca УВВ в магистраль 3.1- З.К.

Сигнал 20 запроса связи поступает на соответствующие входы всех блоков 4.1-4.М, например, на первый вход узла управления 29.. 1 блока 4.1. На второй вход узла управления 29.1 с определенной цикличностью поступает сигнал 1 с выхода регистра 35. С тем же периодом на вход узла 30.1 приемопередатчиков подается разрешение с второго выхода узла 29.1 управления.

Така как входы дешифратора 34 подключены к выходам счетчика, то на выходах дешифратора 34, а, следовательно, и регистра 35 поочередно

принимают значение логической единицы сигналы разрешения магистрали, . поступающие на вторые входы узлов 30.1-30.К: Ром 1, Ром 2,...,Ром К,

Ром 1 и т.д.

Поэтому по входам УВВ через соответствующий узел приемопередатчиков 30.1-30.К поочередно подключаются

3

магистрали З..3.2,...,3.1, 3. 1,.. и т.д.

Дешифратор 34 и регистр 35 обра- зуют схему временного контроля. Если за время наличия сигнала логической ,1 на входе Ром I. не поступит сигнал 44 ответа УВВ, то сигнал Ром примет значение О, сигнал Ром 2 примет значение логической 1 и ко входам УВВ будет подключена магистраль 3.2.

При поступлении сигнала 44 ответа УВВ в установленное время соответствующий узел управления,например узел 29.1, формирует сигнал 53 признака захвата магистрали 3.1, при этом на выходе элемента ИЛИ 33 устанавливается уровень логической единицы,- что приводит к запоминанию в регистре 35 текущего состояния де- пшфратора 34. Таким образом, сигнал Ром I сохраняет значение 1, а Ром 2 .... Ром К - значение О.

Это состояние, когда первый блок сопряжения с процессом установил связь с первым УВВ сохраняется в течение всего времени пока сигнал Запрос связи сохраняет значение логической единицы. При этом направление передачи данных может изменяться в зависимости от значения сигнала Признак передачи.

По окончании цикла обмена информацией процессор устанавливает на шине УПР управляющее слово Конец связи. При этом сигнал с первого выхода дешифратора 8 устанавливает триггер 9 в исходное состояние.Переход сигнала Запрос связи в состояние О приводит к переходу в состояние логического О сигнала 53 на выходе узла 29.1 управления, а , следовательно, и сигнала на выходе элемента-ИЛИ 33. Блокировка регистра 35 снимается и на его выходах Ром . 1,..., Ром К опять появляются сигнала, соответствующие сигналам на выходе дешифратора, 34, Таким образом, установленный канал связи между процессором 1.1 и УВВ 5.1 оказался разрушенным, и блок 4.1 переходит в режим опроса магистралей

Jx

Если УВВ обнаружило ошибку в передаваемых данных, оно устанавливает в состояние 1 сигнал 45 запроса прерывания, который через демуль- типлексор 37 поступает на блок со2

пряжения с процессором. На шине 56 Данные УВВ устанавливается адрес УВВ, обнаружившего ошибку и код ошибки. Процессор, приняв сигнал

Запрос прерывания записывает адрес УВВ и код ошибки в выделенную зону ОЗУ и обращение к .данному УВВ больше не производится.

Кроме того, УВВ может потребовать

сеанса связи при отсутствии канала связи с процессором. Для этого оно устанавливает сигнал Запрос прерывания в состояние логической 1, а на шине данных выставляет свой

адрес.

Для организации канала связи с i-M процессором необходимо, чтобы сигнал 51 и 52 принял значение логической 1.

Рассмотрим формирование сигнала 51 Разрешение 1 по схеме узла 29.1 управления, представленной на фиг.4. При отсутствии установленного.канала и отсутствии запроса связи от

1-го процессора на входах 3 и 1 присутствуют уровни 0. На входе 2 периодически появляется сигнал 1. При одновременном появлении уровней 1 на входах 2 и 5 на выходе элемента И-НЕ 65 устанавливается уровень О, на выходе элемента И-НЕ 67- уровень 1. Следовательно,сигнал 51 принимает значение 1 на время присутствия 1 на входе 2.

На это время устанавливается кратковременный канал связи между данным УВВ и 1-м процессором. Процессор принимает сигнал Запрос прерывания и адрес УВВ с шины данных, а затем осуществляет обращение к данному УВВ по описанному алгоритму.

Формула изобретения.

1.Устройство для обмена данными, содержащее первый блок сопряжения с процессором, М блоков сопряжения с устройствами ввода-вывода, при этом первая группа управляющих входов-выходов блока сопряжения с процессором подключена к группе управляющих входов-выходов процессора, первый информационный вход-выход блока сопряжения с процессором подключен к информационному входу-выходу процессора, первая группа управляющих входов-выходов каждого блока сопряжения с устройством ввода-выво

да подключена к группе управляющих входов-выходов соответствующего устройства ввода-вывода, первая группа информационных входов-выходов каждого блока сопряжения с устройством ввода-вывода подключена к информационному входу-выходу соответствующего устройства ввода-вывода, причем вторая группа управляющих входов-выходов блока сопряжения с процессором соединена с вторыми группами управляющих входов-выходов М бло .ков сопряжения с устройствами ввода вьшода, второй информационный вход- выход блока сопряжения с процессором соединен с вторыми информационными входами-выходами М блоков соп- пряжения с устройствами ввода-вывода, отличающееся тем,что с целью расширения функциональных возможностей за счет организации мультипроцессорного режима работы, в него введены 2 - К-й блоки-сопряжения с процессором, генератор импульсов, счетчик, первые группы управляющих входов-выходов 2 - К-го блоков сопряжения с процессором подключены к группам управляющих входо выходов 2 - К-го процессоров соотвественно, первые информационные входы-выходы 2 - К-го блоков сопряжени с процессором подключены к информационным входам-выходам 2 - К-го процессоров соответственно, причем вторые информационные входы-выходы К блоков сопряжения с процессором соединены с вторыми информационными входами М блоков сопряжения с устройствами ввода-вывода, вторые группы управляющих входов-выходов К блоков сопряжения процессором соединены с вторыми группами управляющих входов-выходов М блоков сопряжения с устройствами ввода-вывода, выход генератора импульсов соединен с счетным входом счетчика, группа выходов которого соединена с группами адресных входов М блоков сопряжения с

устройствами ввода-вывода, причем блок сопряжения с процессором содержит дешифратор, два триггера, узел приемопередатчиков, два элемента ИЛИ, при этом первый информационный вход-выход узла приемопередатчиков является первым информационным входом-выходом блока сопряже ния с процессором, второй информационный вход-выход узла приемопередатчиков является вторым информационным входом-выходом блока сопряжения с процессором, вход дешифра- - тора, синхровходы первого и второго триггеров, информационный вход первого триггера, выходы первого и второго элементов ИЛИ образуют первую группу управляющих входов-выхоJO Дов блока сопряжения с процессором, выходы первого и второго триггеров, синхровходы первого и второго тригге- роэ, информационный вход первого

: триггера, М входов первого и второJ5 го элементов ИЛИ образуют вторую группу управляющих входов-выходов блока сопряжения с процессором, при-, чем вход дешифратора соединен с третьим информационным входом узла

20 приемопередатчиков, управляющий вход которого соединен с выходом . первого триггера, первый и второй выходы дешифратора соединены с нулевым и информационным входами вто- 25 рого триггера соответственно, при

этом блок сопряжения с устройства- (

ми ввода-вывода содержит мультиплексор, демультиплексор, дешифратор, регистр, -три элемента ШШ, К узлов 30 приемопередатчиков, К узлов управления, при этом вход-выход первого элемента ИЛИ является первым информационным входом-выходом блока сопряжения с устройствами ввода-выво- 35 да, первый, второй выходы мультиплексора, выход второго элемента

ШШ и первый, второй информационные входы демультиплексора образуют первую группу управляющих входов-вы- ходов блока сопряжения с устройствами ввода-вывода, первые информационные входы-выходы к узлов приемопередатчиков образуют второй информационный вход-выход блока сопря- 5 жения с устройствами ввода-вывода, 2 К информационных входов мультиплексора, 2 К выходов демультиплексора, первые управляющие входы К узлов приемопередатчиков, первые 0 входы К узлов управления образуют вторую группу управляющих входов блока сопряжения с устройствами ввода-вывода, группа входов дешифратора образует адресный вход блока со- 5 пряжения с устройствами ввода-вывода, причем в блоке сопряжения с устройствами ввода-вывода выходы дешифратора соединены с информационным

входом регистра, К выходов которого соединены с управляющими входами мультиплексора и демультиплексора и .вторыми входами К узлов управления, первые выходы которых соединены с К входами третьего элемента ИЛИ, выход которого соединен с управляющим входом регистра и третьими входами К узлов управления, вторые выходы которых соединены с вторыми управляющими входами К узлов приемопередатчиков, вторые информационные входы- выходы которых соединены с К входами-выходами первого элемента ИЛИ, информационные выходы К узлов приемопередатчиков соединены с К входами второго элемента ИЛИ, четвертый и пятый входы К узлов управление соединены с первым и вторым информационными входами демультиплексора соответственно,

t«

2. Устройство по П.1, отличающееся тем, что узел управления содержит триггер, элемент ИЛИ четыре элемента И-НЕ, элемент НЕ,

10

15

20

25

742 8

при этом первый вход первого элемен та И-НЕ соединен с нулевым входом триггера и является первым входом узла, второй вход первого элемента И-НЕ соединен с первым входом второго элемента И-НЕ и является вторым входом узла, вход элемента НЕ является третьим входом узла, первый вход третьего элемента И-НЕ является четвертым входом узла,второй вход второго элемента И-НЕ является пятым входом узла , выход триггера соединен с первым входом элемента ИЛИ и является первым выходом узла, выход элемента ИЛИ является вторым выходом узла, причем в узле управления выход элемента НЕ соединен с третьими входами первого и второго элементов И-НЕ, выходы которых соединены с первым и вторым входом четвертого элемента И-НЕ соответст- венно, выход которого соединен с вторыми входами элементов ИЛИ и третьего элемента И-НЕ, выход которого соединен с единичным входом триггера.

Фи,2

. Фиг. 3

иеЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Система программного управления станками | 1985 |

|

SU1328792A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

Изобретение относится к области вычислительной техники и может быть использовано в мультипроцессорных системах обработки информации и в системах обмена данными со множеством устройств ввода-вывода. Целью изобретения является расширение функциональных возможностей за счет организации мультипроцессорного режима работы. Устройство содержит блоки сопряжения с процессором,блоки сопряжения с устройствами ввода-вывода, генератор импульсов, счетчик. 1 з.п. ф-лы, 4 ил.

| Система обработки информации | 1978 |

|

SU922712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент ФРГ № 2934376, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-08-21—Подача