Изобретение относится к области радиолокации и может быть использовано при построении импульсных радиолокаторов различного назначения.

Известны устройства цифровой когерентной фильтрации, используемые в радиолокационных станциях (см. патент США №3622089 по кл. США 343-5 DP, книгу Слока В.К. "Вопросы обработки радиолокационных сигналов", Советское радио, M., 1970 г., стр.196-203). Наиболее близким по технической сущности к заявляемому является устройство, описанное в книге Слока В.К. "Вопросы обработки радиолокационных сигналов".

Это устройство содержит когерентный гетеродин, амплитудный бинарный квантователь, генератор тактовых импульсов, формирователь наборов синусных и косинусных весовых множителей, квадратурные каналы,, включающие фазовый детектор, преобразователь аналог-код, N-1 блок памяти, где N - число обрабатываемых импульсов, набор допплеровских частотных фильтров, каждый из которых состоит из четырех каналов, включающих цифровые перемножители, выходы каналов соединены со входами цифрового функционального формирователя огибающей допплеровского частотного фильтра. Для когерентной фильтрации сигналов с конкретной допплеровской частотой цифровые сигналы с выходов преобразователей аналог-код и с выходов блоков памяти умножаются в цифровых перемножителях на синусные и косинусные весовые множители.

Таким образом, в каждом допплеровском частотном фильтре имеются четыре канала по N перемножителей в каждом.

Выходные сигналы цифровых перемножителей каждого канала суммируются в своем N-входовом сумматоре, выходные сигналы сумматоров подают на цифровой функциональный формирователь огибающей, выход которого является выходом цифрового когерентного фильтра на данной допплеровской частоте.

При таком построении цифрового когерентного фильтра на каждый фильтр допплеровской частоты требуется 4 N цифровых перемножающих устройств. Кроме того, N-входовые сумматоры, на каждый из N входов которых поступают многоразрядные двоичные числа, требуют значительных аппаратурных затрат. Аппаратурные затраты и время обработки резко увеличиваются с ростом N. Однако в целом ряде случаев для обнаружения слабых сигналов приходится обрабатывать пачку, состоящую из большого числа импульсов.

Целью настоящего изобретения является повышение быстродействия и уменьшение аппаратурных затрат при большом числе обрабатываемых импульсов.

Поставленная цель достигается тем, что в цифровой когерентный фильтр, содержащий когерентный гетеродин, амплитудный бинарный квантователь, генератор тактовых импульсов, формирователь наборов синусных и косинусных весовых множителей, квадратурные каналы, включающие фазовый детектор, преобразователь аналог-код, N-1 блок памяти, где N - число обрабатываемых импульсов, набор допплеровских частотных фильтров, каждый из которых состоит из четырех каналов, включающих цифровые перемножители, выходы каналов соединены со входами цифрового функционального формирователя огибающей допплеровского частотного фильтра, в каждый квадратурный канал введен блок памяти, вход которого соединен с выходом последнего блока памяти квадратурного канала, в каждый канал допплеровских частотных фильтров введены вычитающее устройство, блок памяти и двухвходовый сумматор, выход цифрового перемножителя, соединенного с выходом преобразователя аналог-код и выход цифрового перемножителя, соединенного с выходом введенного блока памяти квадратурного канала, подключены ко входам вычитающего устройства, выход которого соединен с первым входом сумматора, второй вход сумматора соединен с блоком памяти допплеровского частотного фильтра, выход сумматора соединен со входом блока памяти допплеровского частотного фильтра и входом цифрового функционального формирователя огибающей.

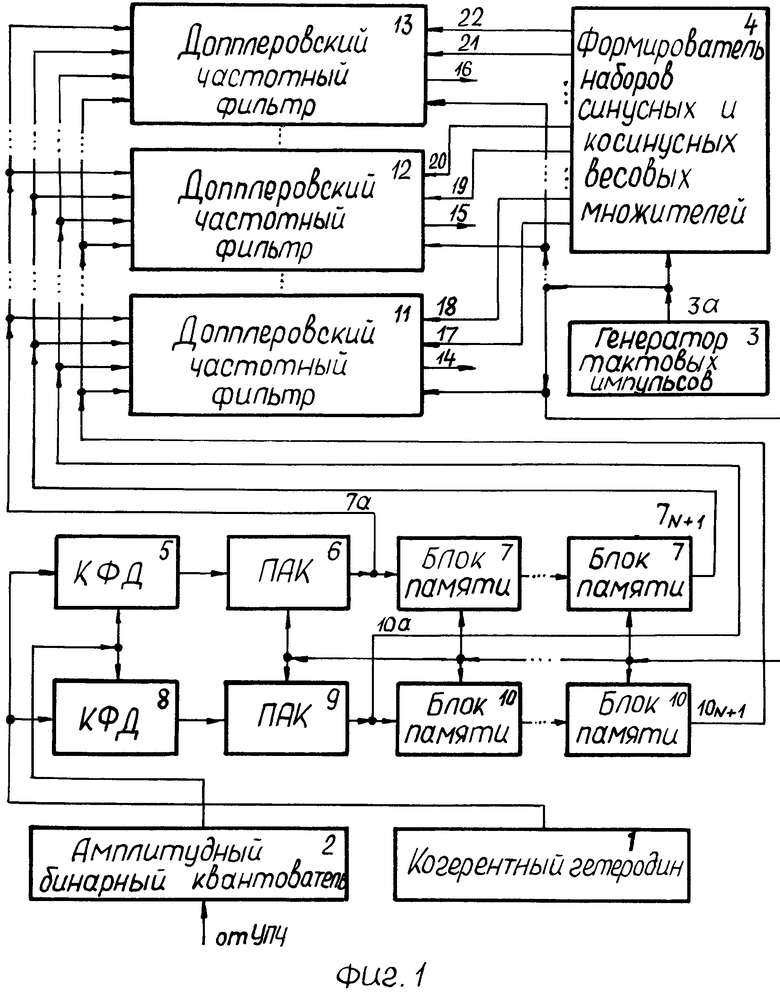

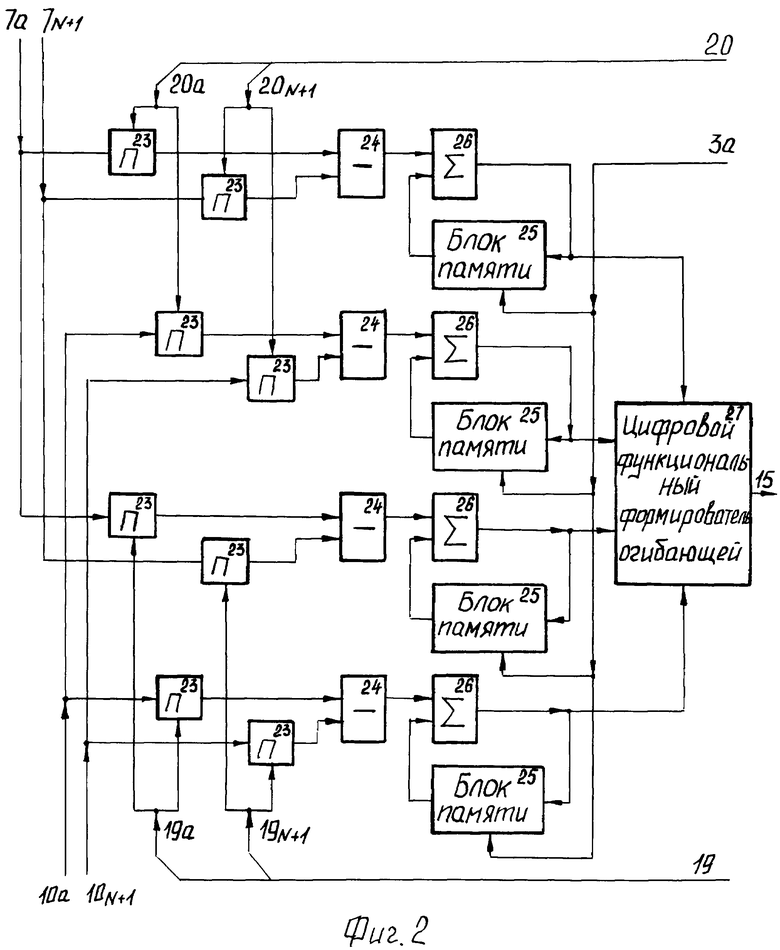

На фиг.1 представлена блок-схема цифрового когерентного фильтра, предлагаемого в качестве изобретения. На фиг.2 показана развернутая блок-схема i-го допплеровского частотного фильтра предлагаемого устройства.

Цифровой когерентный фильтр, блок-схема которого представлена на фиг.1, содержит когерентный гетеродин 1, амплитудный бинарный квантователь 2, генератор тактовых импульсов 3, формирователь наборов синусных и косинусных весовых множителей 4, первый квадратурный канал, состоящий из фазового детектора 5, преобразователя аналог-код 6 и N блоков памяти 7 и второй квадратурный канал, состоящий из фазового детектора 8, преобразователи аналог-код 9 и N блоков памяти 10, набор допплеровских частотных фильтров 11, 12, 13 со своими выходными сигналами 14, 15, 16. На каждый допплеровский частотный фильтр подают два цифровых сигнала 7a, 7N+1 с одного и два цифровых сигнала 10a, 10N+1 с другого квадратурных каналов. Кроме того, на каждый допплеровский частотный фильтр от формирователя наборов синусных и косинусных весовых множителей 4 подают наборы множителей: на первый допплеровский частотный фильтр - набор синусных 17 и косинусных 18 весовых множителей, изменяющихся с частотой настройки первого допплеровского частотного фильтра, на i-й допплеровский частотный фильтр - набор синусных 19 и косинусных 20 весовых множителей, изменяющихся с частотой настройки i-го допплеровского частотного фильтра, на последний допплеровский частотный фильтр - набор синусных 21 и косинусных 22 весовых множителей, изменяющиеся с частотой настройки последнего допплеровского частотного фильтра.

На фиг.2 представлена блок схема i-го допплеровского частотного фильтра. Она содержит четыре канала обработки, состоящих из двух цифровых перемножителей 23, вычитающего устройства 24, блока памяти допплеровского частотного фильтра 25, двухвходового сумматора 26. Выходные сигналы двухвходовых сумматоров 26 являются выходными сигналами каналов допплеровского частотного фильтра и поступают на функциональный формирователь огибающей 27, сигнал 15 с выхода последнего является выходным сигналом i-го допплеровского частотного фильтра. На цифровые перемножители 23 канала допплеровского фильтра подают цифровые сигналы одного из квадратурных каналов и двухэлементный набор синусных 19 или косинусных 20 весовых множителей. Выходные сигналы цифровых перемножителей 23 подают на вычитающее устройство 24, выход которого связан с одним входом двухвходового сумматора 25, другой вход которого соединен с выходом блока памяти 25 допплеровского частотного фильтра. Выход сумматора 26 соединен со входом блока памяти 25. На все блоки памяти цифрового когерентного фильтра и на преобразователи аналог-код подают синхронизирующий сигнал 3a с выхода генератора тактовых импульсов 3.

Предлагаемый цифровой когерентный фильтр работает следующим образом. Выходной сигнал УПЧ обрабатывается амплитудным бинарным квантователем 2 и поступает на сигнальные входы квадратурных фазовых детекторов 5 и 8, на опорные входы которых поступает сигнал когерентного гетеродина 1. Видеосигналы с выходов фазовых детекторов 5 и 8 преобразовываются в двоичнокодированные слова преобразователями аналог-код 6, 9, которые подаются на первые блоки памяти квадратурных каналов. Каждое слово смещается в последующий блок памяти тогда, когда на предыдущей поступает новая информация, слова в последних блоках памяти сбрасываются. Слова с выходов преобразователей аналог-код 6, 9 и с выходов последних блоков памяти квадратурных каналов 7, 10 поступают на цифровые перемножители 23 допплеровских частотных фильтров. На другие входы цифровых перемножителей 23 поступают синусные и косинусные весовые множители 19a, 19N+1 и 20a, 20N+1. Принцип обработки сигналов в каждом канале i-го допплеровского частотного фильтра следующий: в вычитающем устройстве 24 определяется приращение результатов суммирования в сумматоре 26 текущего тактового периода и предыдущего, которое поступает на один вход сумматора 26, на второй вход сумматора 26 поступает результат суммирования предыдущего периода, записанный в блоке памяти 25. Тают образом на входе сумматора 26 получают результат суммирования текущего тактового периода, который подают на цифровой функциональный формирователь огибающей 27.

Таким образом, результат обработки на входе цифрового функционального формирователя огибающей 27 получают за один цикл суммирования в отличие от прототипа, где требуется l=[log2N] циклов суммирования, где квадратные скобки означают округление в сторону большего целого числа, что при большом N не позволит производить обработку в реальном масштабе времени. Как следует из вышеизложенного, в каждом допплеровском частотном фильтре, по сравнению с прототипом, введены дополнительно четыре блока памяти 25 и одна связь 3a, кроме того, два блока памяти 7 и 10 в квадратурных каналах, а в каждом допплеровском частотном фильтре на 4 (N-2) цифровых перемножителя 23, 4 (N-3) двухвходовых сумматора реализующих N-входовые сумматоры, и 4 (N-2) связи с блоками памяти 9, 10 и формирователем наборов синусных и косинусных весовых множителей меньше.

Таким образом, при большом числе обрабатываемых импульсов в предлагаемом устройстве достигается значительное сокращение объема оборудования, уменьшается весогабаритные и стоимостные характеристики устройства, повышается надежность.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ С ЦИФРОВЫМ ФИЛЬТРОМ | 1977 |

|

SU1840897A1 |

| СПОСОБ СОПРОВОЖДЕНИЯ ЦЕЛИ МОНОИМПУЛЬСНОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ | 1997 |

|

RU2117960C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| АВТОКОМПЕНСАТОР ДОПЛЕРОВСКИХ СДВИГОВ ФАЗЫ ПОМЕХ | 2016 |

|

RU2624795C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МОДУЛЯЦИИ, СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ, МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ И ПРИМЕНЕНИЕ СПОСОБА ДЛЯ СИНХРОНИЗАЦИИ ПРИЕМА СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МОДУЛЯЦИИ | 2005 |

|

RU2286025C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

Изобретение относится к области радиолокации. Достигаемый технический результат - повышение быстродействия. Указанный результат достигается за счет того, что фильтр содержит когерентный гетеродин, амплитудный бинарный квантователь, подключенные к квадратурным каналам, включающим в себя фазовый детектор, преобразователь аналог-код, N-1 блоков памяти, где N - число обрабатываемых импульсов, а также содержит генератор тактовых импульсов, формирователь наборов синусных и косинусных весовых множителей и набор допплеровских частотных фильтров, каждый из которых состоит из четырех соединенных с входами цифрового функционального формирователя огибающей допплеровского частотного фильтра каналов, содержащих цифровые перемножители, при этом каждый квадратурный канал также содержит дополнительный блок памяти, вход которого соединен с выходом последнего блока памяти квадратурного канала, а каждый канал допплеровских частотных фильтров содержит вычитающее устройство, блок памяти и двухвходовый сумматор, причем выходы цифровых перемножителей подключены к входам вычитающего устройства, выход которого соединен с первым входом сумматора, второй вход сумматора соединен с блоком памяти допплеровского частотного фильтра, а выход сумматора соединен с входом блока памяти допплеровского частотного фильтра и входом цифрового функционального формирователя огибающей. 2 ил.

Цифровой когерентный фильтр, содержащий когерентный гетеродин и амплитудный бинарный квантователь, подключенные к квадратурным каналам, включающим в себя последовательно соединенные фазовый детектор, преобразователь аналог-код и N-1 блок памяти, где N - число обрабатываемых импульсов, а также генератор тактовых импульсов, формирователь наборов синусных и косинусных весовых множителей и набор допплеровских частотных фильтров, каждый из которых состоит из четырех соединенных со входами цифрового функционального формирователя огибающей допплеровского частотного фильтра каналов, содержащих цифровые перемножители, отличающийся тем, что, с целью повышения быстродействия, в каждый квадратурный канал введен дополнительный блок памяти, вход которого соединен с выходом последнего блока памяти квадратурного канала, а в каждый канал допплеровских частотных фильтров введены вычитающее устройство, блок памяти и двухвходовой сумматор, причем выход цифрового перемножителя, соединенного с выходом преобразователя аналог-код, и выход цифрового перемножителя, соединенного с выходом блока памяти квадратурного канала, подключены к входам вычитающего устройства, выход которого соединен с первым входом сумматора, второй вход сумматора соединен с блоком памяти допплеровского частотного фильтра, а выход сумматора соединен со входом блока памяти допплеровского частотного фильтра и входом цифрового функционального формирователя огибающей.

| "Цифровой когерентный фильтр", книга В.К | |||

| Слока "Вопросы обработки радиолокационных сигналов", Сов | |||

| радио, 1970 г. |

Авторы

Даты

2014-09-27—Публикация

1975-11-13—Подача