I

Изобретение относится к области БЫ- числительной техники и может применять ся в качестве базового элемента операционных узлов автоматизированных систем управления.

Известны К-значные фазоимпульсные сумматоры, содержащие два двоичных динамических триггера, узел запрета, двухтактный кольцевой регистр сдвига и формирюватель фазой мпульсных кодов суммы и переноса. Однако такие сумматоры содержат большое количество элементов разных типов 1|.

Наиболее близким аналогом являегся К-значный фазоимпульсный сумматор, содержащий два динамических триггера, узел запрета, узел формирования суммы, уаеп формирования переноса, двухтактный кольцевой регистр сдвига, выполненные на магнитотранзисторных элементах, причем информационные входы динамических триггеров подключены соответственно к первому и второму информационным входам устройства, а выходы динамических

триггеров объединены и подключены ко входу узла запрета, выход которого через элемент ИЛИ, другой вход которого связан с шиной переноса, подключен ко EOioдам считывания разрядов двухтактного кольцевого регистра сдвига, входы узла формирования суммы подключены к выходам результата операции двухтактного кольцевого |югистра сдвига, вход узла формирования переноса подключен к выходу переполнения двухтактного кольцевого регистра.сдвига 2}.

Недостатком данного сумматора я&ляется низкое быстродействие, которое зависит от числа разрядов, так как передача переноса производятся последовательно,

Целью изобретения является повышение быстродействия.

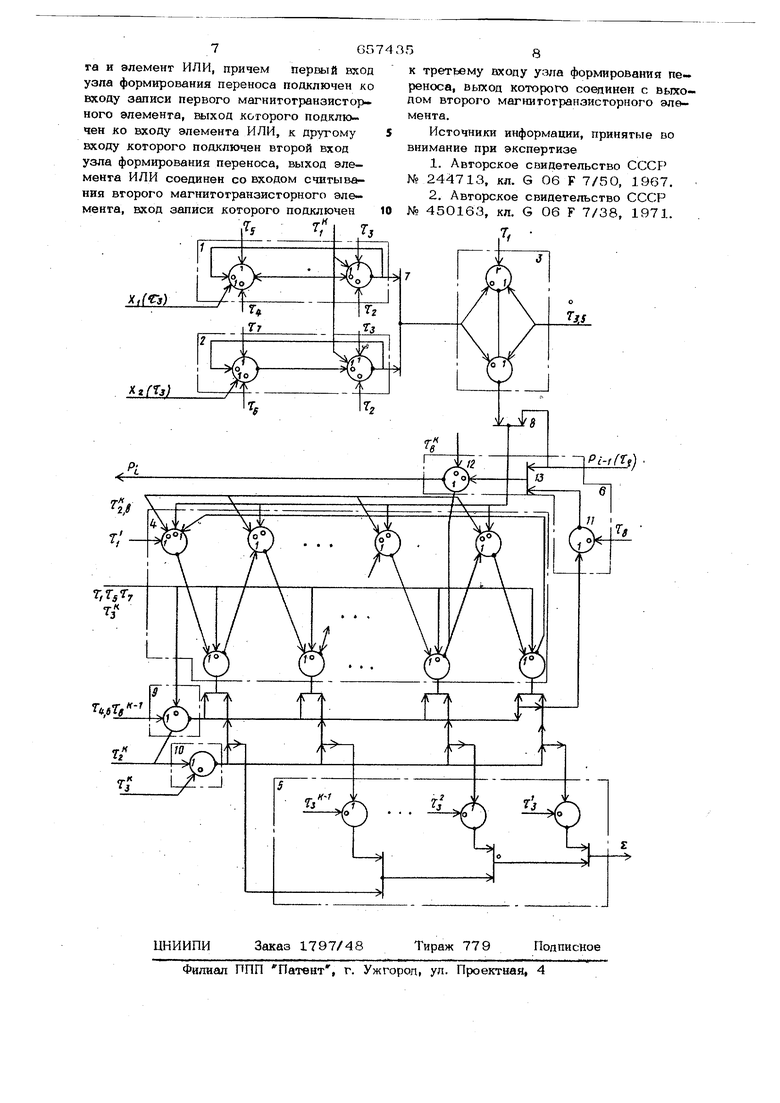

Для достижения этой цели второй вход узла формирования переноса подключен к шине переноса, а третий - к выходу (K-l)-ro разряда двухтактного кольцевого регистра сдвига. Поставленная цель достигается TajoKe тем, что узел формирования переноса содержит два магнитотранзисторных элемеч та и элемент ИЛИ, причеы первый вход узла формирования переноса подключен ко входу записи первого магнитотранзнсторного элемента, выход которого подключен ко входу элемента ИЛИ, к другому входу которого подключен второй вход узла формирования переноса, выход элемента ИЛИ Соединен со входом считывания второго магнитотранзисторного элемента, вход записи которого подключен к третьему входу узла формирования переноса, выход которого соединен с выходом второго магнитотранзисторного элемента. На чертеже изображена функциональная схема К-значнрго фазоимпульсного сумма тора. К-значный фазоимпульсный сумматор содержит два динамических триггера 1 и 2, узел 3 запрета, двухтактный кольцевой регистр 4 сдвига, узел. 5 формировав ния суммы, узел 6 формирования переноса, элементы ИЛИ 7 и 8. Схема сумматора содержит также узел 9 управления сдвигом и узел 10 управления выводом результата. Узел 6 формирования переноса содержит магнитотранзисторные элементы 11 и 12 и элемент ИЛИ 13. Схема сумматора содержит всего (ЗК+9) магнитотранзисторных элементов, Вход первого слагаемого (первый информационный вход устройства) подключен к информационному входу первого динамического триггера 1 (к установочному вхо ду по записи). Вход второго слагаемого (второй информационный вход устройства) подключен к информационному входу второго динамического триггера 2 (к установочному входу по записи). Динамические триггеры имеют общий вход устано&ки в нулевое состояние тактом t Шины постоянных тактов подключены к обмоткам магнитотранзисторных элементов динамических триггеров 1 р 2 таким образом, что в нулевом состоянии динамические триггеры 1 и 2 генерируют импульсы по такту Г, , а в единичном состоянии генерируют импульсы, соответственно, по тактам Т. и С . Выходы динамических триггеров 1 и 2 объединяются элементом ИЛИ 7, выход которог подключен к обмоткам считывания магнитотранзисторных элементов узла 3 запре та, выполняющего функцию запрет по Т, к обмоткам записи этих магнитртранзис торных элементов подключены шины постоянных тактов 1, и Тг , а выход узла 3 запрета объединен с шиной переноса из предыдущего разряда элементом ИЛИ 8. Таким образом, динамические триггеры 1 и 2, узел 3 запрета и элементы ИЛ| 7 и 8 преобразуют информацию входных переменных в число импульсов. Вь1ход элемента ИЛИ 8 подключен к обмоткам считывания магнитотршц ристор. ных элементов верхнего ряда двухтактного кольцевого регистра сдвига 4. Двухтактный кольцевой регистр сдвига 4 содержит 2к магнитотранзисторных элементов, соединенных в кольцо по обмоткам записи. К входу записи первого магнитотранзисторного элемента подключена шина редкого такта начальной установки Т . К нижнему ряду магнитотранзисторных элементов двухтактного кольцевого регистра 4 сдвига через эмиттерные входы подключен узел 9 управления сдвигом информации, реализованный на одном магнитотранзисторном элементе, На обмотки считывания нижнего ряда ма1 нитотранзисторных элементов двухтактного кольцевого регистра 4 сдвига и мат нитотранзисторного элемента узла 9 управпения сдвигом информации подключены шины постоянных тактов С , С- и ТГу и шина редкого такта С . К обмотке записи магнитотранзисторного элемента узла 9 управления сдвигом подключены шины постоянных тактов t и 1Г И шина редкого тактаСд i, а на обмотку гашения - шина редкого такта 11 j, К нижнему ряду магнитотранзисторных элементов двухтактного кольцевого регистра 4 сдвига через эмиттерные юсоды подключен узел 10 управления выводом результата, реализованный на одном магнитотранзисторном элементе, к обмотке записи которого подключена шина редкого такта Т; в к обморке считывания - шина редкого такта ft . Линии связи узла 1О управления выводом результата с эмиттерными входами нижнего ряда магниготранзисторных элементов двухтактного кольцевого реглстра сдвига пЪ тактовому гфинципу подключены к обмоткам записи магнитотранзисторных элементов узла 5 формирования суммы и являются по существу Ы)1ходами результата операции двухтактного кольцевого регистра 4 сдвига. Каждый выход соответствует определенному значению результата. Линия связи узла 56 9 управления сдвигом с последним мапнитотранзисгорным элементом двухтакткого кольцевого регистра 4 сдвига, являющаяся выходом переполнения двухтакт ного кольцевого регистра 4 сдвига,подключена по тактовому принципу к обмотке записи магнитотранзисторного элемента 11 узла 6 формирования переноса. Выход магнитотранзисторного элемента 11 узла 6 формирования переноса подключен ко входу элемента ИЛИ 13, к другому Входу которого подключена ши на переноса из предыдущего разряда. Ко входу считывания и магнитотранзисторного элемента 11 подключена шина постоян ного такта fg . Выход элемента ИЛИ 13 подключен ко входу считывания магнитотранзисторного элемента 12, к другому входу считывания которого пошслючена шина редкого такта to , а к входу записи подключен выход (K-l)-ro разряда двухтактного кольцевого регистра 4 сдвига. Выход магнитотранзисторного эле мента 12 является выходом узла 6 формирования переноса и подключен к шине переноса в последующий разряд. К обмоткам считывания магнитотранзисторных элементов верхнего ряда двухтактного кольцевого регистра 4 сдвига для выполнения операции катода результата и гашения информации подключены шины редких тадтовИ- и . Обмотки считывания магнитотранзисторных элементов узла 5 формирования суммы подключены к шинам редких такTOBtJ Д , 1 , ... ,У . Выходы магнитотранзисторных элементов узла 5 формирования суммь объединены и подключены к выходу узла 5 формирования суммы, который является выходом К-значного фазоимпульсного сумматора. Слагаемые, поступающие на входы К-значного фазоимпульсного сумматора пре ставлены в фазоимпульсной форме, причем каждому из К возможных значений (О, 1, 2 . . . , (K-l)) соответствует наличие импульса тока по соответствующему такту (Г ) такту vLj,tj «-з 3 Для нормального суммирования информации все слагаемые подаются в одном цифровом периоде, а результат операции получается в следующем цифровом периоде, кроме нулевого значения результата (нулевое значение результата выводится в том же цифровом периоде). За цифровой период принимается временной интервал между двумя токовыми импульсами редкого тактаТ в генера56торе такговых импульсов. За тактовый период принимается временной интервал между двумя токовыми импульсами поотоянного тактаГ . Количество тактош тх периодов, необходимых для правильной работы сумматора, равно К ( К - зна ность системы счисления). Количество тактов в тактовом периоде, необходикялх для правильной работы сумматора, равно 8. Такты, повторяемые в каждом тактовом периоде, называются постоянными и обозначаются как Т. , а такты, повторяемые в каждом цифровом периоде только один раз и в определенном тактовом периоде, называются редкими и обозначаются как t . Преимуществом данного сумматора по сравнению с прототипом является то, что без существенного усложнения схемы сумматора быстродействие его повышает- ся в N раз (N - число разрядов сумматора). Формула изобретения 1. К-значный фазоимпульсный суммаг. тор, содержащий два динамических триггера, узел запрета, узел формирования суммы, узел формирования переноса, двухтактный кольцевой регистр сдвига, ы гаолненные на магнитотранзисторных алемен- тах, причем информанионные входы динамических триггеров подключены соотвегственно к первому и второму информационным входам устройства, а выходы динамических триггеров обьединены и подкл чены ко входу узла запрета, выход которого через элемент ИЛИ, другой вход которого связан с шиной переноса, подключен ко входам считывания разрядов двухтактного кольцевого регистра сдвига. входы узла формирования суммы подклк чены к вь1хогам результата операции двухтактного кольцевого регистра сдвига, первый вход узла формирования переноса подключен к выходу переполнения двухтактного кольцевого регистра сдвига, о i личающийся тем, что, с целью повышения быстродействия, второй вход узла формирования переноса подключен к, шине переноса, а третий - к выходу (K-l)-ro разряда двухтактного кольцевого регистра сдвига, 2. К-значный фазоимпульсный сумматор по п. 1, отличающийся тем, что узел формирования переноса соДержит два магнитотранзисторных элемен

| название | год | авторы | номер документа |

|---|---|---|---|

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ К | 1972 |

|

SU341034A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| С-СТАБИЛЬНЫЙ ДИНАМИЧЕСКИЙ ТРИГГЕР | 1971 |

|

SU319055A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

Авторы

Даты

1979-04-15—Публикация

1977-03-29—Подача